#### ADAPTIVE DATA-TRANSITION DECISION FEEDBACK EQUALIZERS FOR HIGH-SPEED SERIAL LINKS

by

#### Yue Li

Master of Science, University of Macau, Macau, China, 2015 Bachelor of Science, University of Macau, Macau, China, 2012

> A dissertation presented to Ryerson University in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2020 ©Yue Li, 2020

# AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A DISSERTATION

I hereby declare that I am the sole author of this dissertation. This is a true copy of the dissertation, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the public.

#### Abstract

Yue Li

Adaptive Data-Transition Decision Feedback Equalizers for High-Speed Serial Links Doctor of Philosophy, Electrical and Computer Engineering Ryerson University, 2020

This dissertation investigates adaptive decision feedback equalizers for high-speed serial data links.

An adaptive data-transition decision feedback equalizer (DT-DFE) was developed. The DT-DFE boosts the eye-opening of the high-frequency components of data without attenuating their low-frequency counterparts. Reference voltages were obtained by transmitting consecutive 1s and 0s and measuring the output of the continuous-time linear equalizer using a pair of successive approximation register analog-to-digital converters in a training phase. It uses loop unrolling to detect data transitions, activate tap-tuning, launch DFE, and combat timing constraints. The performance of the DT-DFE and its advantages over commonly used data-state DFE were validated using the schematic-level simulation results of 5 Gbps backplane links.

A new adaptive DT-DFE with edge-emphasis (EE) taps and raised references was developed. Loop-unrolling was further developed for DT-DFE with EE-taps. The reference voltages were raised beyond that set by the low-frequency components of data to increase vertical eye-opening. Clock and data recovery was performed using 4x oversampling. The DT-DFE was validated using the schematiclevel simulation results of 10 Gbps backplane links.

A pre-skewed bi-directional gated delay line (BDGDL) bang-bang frequency difference-to-digital converter and a BDGDL integrating frequency difference-todigital converter (iFDDC) were proposed for clock and data recovery. Both frequency difference detectors feature all-digital realization, low power consumption, and high-speed operation. The built-in integration of iFDDC results in a zero static frequency error and the first-order noise-shaping of the quantization errors of the BDGDL and digitally-controlled oscillators. Their effectiveness was validated using schematic-level simulation results of 5-GHz frequency-locked loops.

All systems validating the proposed adaptive DFE and frequency-difference detectors were designed in TSMC's 65 nm CMOS technology and analyzed using Spectre from Cadence Design Systems.

## Acknowledgements

I would first express my deepest gratitude to my supervisor Professor Fei Yuan for his guidance, support and kindness through every stages of my doctoral study. I have been extremely lucky to have the opportunity to be his student and assistant. I remember the countless hour we spent in his office discussing when I first started this work. With all kinds of questions and requests, he showed nothing but technical expertise and great personality. I have learned numerous things from Fei and without his help this work would not be possible.

I would also like to thank Professor Andy G. Ye, Professor Gul N. Khan and Professor Vadim Geurkov for being the committee members of my candidacy exam and thesis defense. I would like to thank Professor Guangjun Liu from Aerospace Engineering, Ryerson University and Professor Wai Tung Ng from University of Toronto for kindly joining the defense committee. Thanks to all the committee members for reviewing my thesis and providing constructive comments.

I would like to thank all my colleagues also friends Young Jun Park, Durand Jarrett-Amor, Matthew Dolan, Jean-Claude Clarke, Parth Patel and Rashed Siddiqui from the Integrated Circuits and Systems (ICS) Group for their kind help and wonderful friendship. I would like to thank Ryerson University and the department of Electrical, Computer and Biomedical Engineering for funding my research and study. I also want to thank all the lovely students in the courses I assisted teaching for their cooperation and appreciation. Thanks to them for making conducting the lab session pleasant and rewarding.

I would especially like to thank my parents for encouraging and supporting me to pursue doctoral studies overseas. I thank them for their unconditional love and belief in me. Finally, I would like to thank my wife Xiaoshi Zhang. I did not feel any frustration or disappointment in the last four years with the support of my motivated and brilliant partner. I thank her for bringing delight to every single second of my life and I want dedicate this thesis to her.

# **Table of Contents**

| Ał                       | Abstract iii |                                                                                                                                               |  |  |

|--------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Li                       | st of        | Figures xii                                                                                                                                   |  |  |

| Li                       | st of        | Tables xiii                                                                                                                                   |  |  |

| List of Abbreviations xi |              |                                                                                                                                               |  |  |

| 1                        | Intr         | oduction 1                                                                                                                                    |  |  |

|                          | 1.1          | Serial Links                                                                                                                                  |  |  |

|                          | 1.2          | Wire Channels                                                                                                                                 |  |  |

|                          | 1.3          | Channel Equalization                                                                                                                          |  |  |

|                          | 1.4          | Motivation $\ldots \ldots 12$ |  |  |

|                          | 1.5          | Objectives                                                                                                                                    |  |  |

|                          | 1.6          | Thesis Organization                                                                                                                           |  |  |

|                          | 1.7          | Contributions $\ldots \ldots 15$                   |  |  |

|                          | 1.8          | Summary                                                                                                                                       |  |  |

| <b>2</b>                 | Dat          | -Transition DFE 19                                                                                                                            |  |  |

|                          | 2.1          | DS-DFE Limitations                                                                                                                            |  |  |

|                          | 2.2          | DT-DFE                                                                                                                                        |  |  |

|                          |              | 2.2.1 Architecture                                                                                                                            |  |  |

|                          |              | 2.2.2 Data-Transition Unit                                                                                                                    |  |  |

|                          |              | 2.2.3 Max/Min Vertical Eye-Openings                                                                                                           |  |  |

|                 |      | 2.2.4                                                                         | $Sign^3$ -LMS                                                                     | 25       |

|-----------------|------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------|

|                 |      | 2.2.5                                                                         | Tap Addition/Subtraction                                                          | 26       |

| 2.3 Discussions |      | sions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 26                                                                                |          |

|                 |      | 2.3.1                                                                         | Tap Tuning                                                                        | 26       |

|                 |      | 2.3.2                                                                         | DFE Activation                                                                    | 27       |

|                 |      | 2.3.3                                                                         | DS-DFE versus DT-DFE                                                              | 28       |

|                 |      | 2.3.4                                                                         | Error Propagation                                                                 | 33       |

|                 |      | 2.3.5                                                                         | Loop-Unrolling                                                                    | 35       |

|                 |      | 2.3.6                                                                         | Hardware Cost                                                                     | 35       |

|                 | 2.4  | Simula                                                                        | ations Results                                                                    | 36       |

|                 | 2.5  | Summ                                                                          | ary                                                                               | 37       |

|                 |      |                                                                               |                                                                                   | _        |

| 3               |      |                                                                               | Edge-Emphasis Data-Transition DFE with Raised                                     |          |

|                 |      |                                                                               | s in Oversampling CDR                                                             | 40       |

|                 | 3.1  |                                                                               | non drawbacks of DS-DFE and DT-DFE                                                | 41       |

|                 | 3.2  | Edge-1                                                                        | Emphasis Taps                                                                     | 42       |

|                 | 3.3  | DT-D                                                                          | FE with EE-taps $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$             | 46       |

|                 |      | 3.3.1                                                                         | Architecture                                                                      | 46       |

|                 |      | 3.3.2                                                                         | Loop unrolling for $S_n$                                                          | 47       |

|                 |      | 3.3.3                                                                         | Loop unrolling for DT-DFE with EE-tap                                             | 51       |

|                 |      | 3.3.4                                                                         | Raised reference voltages                                                         | 53       |

|                 |      | 3.3.5                                                                         | Determination of EE-tap                                                           | 55       |

|                 | 3.4  | Clock                                                                         | and Data Recovery $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$       | 57       |

|                 | 3.5  | Simula                                                                        | ation Results                                                                     | 60       |

|                 |      | 3.5.1                                                                         | 5 Gbps Serial Link $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 60       |

|                 |      | 3.5.2                                                                         | 10 Gbps Serial Link with 4x-oversampling CDR $\ .$                                | 64       |

|                 | 3.6  | Summ                                                                          | ary                                                                               | 70       |

| 4               | Δ11_ | Digita                                                                        | l Frequency-Locking using Bi-Directional Gated De                                 | <b>_</b> |

| I               |      | 0                                                                             | requency Difference-to-Digital Converters                                         | 71       |

|                 | 4.1  |                                                                               | ency Difference Detection                                                         | 72       |

|                 | 4.2  | -                                                                             | DL Bang-Bang Frequency Difference Detector                                        |          |

|                 |      |                                                                               |                                                                                   |          |

| Bi       | Bibliography 97 |        |                                                 |      |

|----------|-----------------|--------|-------------------------------------------------|------|

|          | 5.2             | Future | e Work                                          | . 96 |

|          | 5.1             | Conclu | usions                                          | . 94 |

| <b>5</b> | Cor             | clusio | ns and Future Work                              | 94   |

|          | 4.4             | Summ   | nary                                            | . 93 |

|          |                 | 4.3.3  | Simulation Results                              | . 90 |

|          |                 | 4.3.2  | All-Digital FLL with iFDDC                      | . 87 |

|          |                 | 4.3.1  | iFDDC                                           | . 83 |

|          | 4.3             | Integr | ating Frequency Difference-to-Digital Converter | . 83 |

|          |                 | 4.2.5  | Simulation Results                              | . 81 |

|          |                 | 4.2.4  | Frequency Error                                 | . 79 |

|          |                 | 4.2.3  | Frequency Detection                             | . 74 |

|          |                 | 4.2.2  | Pre-Skewed BDGDL                                | . 73 |

|          |                 | 4.2.1  | BDGDL                                           | . 73 |

# List of Figures

| 1.1  | Dependence of data rate on the minimum channel length of         |    |

|------|------------------------------------------------------------------|----|

|      | MOS transistors.                                                 | 2  |

| 1.2  | A typical structure of serial links                              | 3  |

| 1.3  | A backplane example.                                             | 4  |

| 1.4  | Skin Effect.                                                     | 4  |

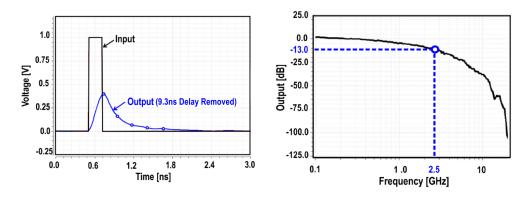

| 1.5  | Channel loss. Left: time domain response Right: frequency        |    |

|      | domain response                                                  | 5  |

| 1.6  | Feed-forward equalizer. Top: Block diagram. Bottom: Spec-        |    |

|      | tral behavior ( $f_{DR}$ : Data rate frequency)                  | 7  |

| 1.7  | CTLE. Left: Schematic. Right: Spectral behavior                  | 8  |

| 1.8  | DFE block diagrams. Top: Regular. Bottom: Loop-unrolling.        | 9  |

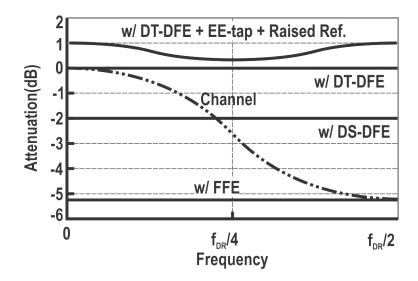

| 1.9  | Comparison between FEE and DFE                                   | 10 |

| 1.10 | DFE with $L$ taps. Left: Conventional DS-DFE. Right: IIR-        |    |

|      | DFE                                                              | 11 |

| 1.11 | Equalization with different types of DFEs. Left: Conventional    |    |

|      | DS-DFE. Right: IIR-DFE                                           | 11 |

| 2.1  | Data-state DFE.                                                  | 20 |

| 2.2  | Architecture of sign <sup>3</sup> -LMS DT-DFE (highlighted part) | 21 |

| 2.3  | Data transition unit.                                            | 23 |

| 2.4  | Data transition signal $s_n$ . If data=0, since the tap increases                                    |      |

|------|------------------------------------------------------------------------------------------------------|------|

|      | $v_A$ in path A and decreases $v_B$ in path B, the output of slicer                                  |      |

|      | A is selected while that of slicer B is discarded. If data=1,                                        |      |

|      | since the tap decreases $v_A$ in path A and increases $v_B$ in path                                  |      |

|      | B, the output of slicer A is discarded while that of slicer B is                                     |      |

|      | selected.                                                                                            | 24   |

| 2.5  | DT-DFE with sign <sup>3</sup> -LMS. The output of the charge pumps is                                |      |

|      | fed to a loop filter to smooth tap tuning                                                            | 25   |

| 2.6  | Tap addition/subtraction.                                                                            | 27   |

| 2.7  | DFE activation schemes                                                                               | 28   |

| 2.8  | Simulated eye diagram equalized using DS-DFE with one tap. The                                       |      |

|      | strength of the tap : 0.7 mA, 1.0 mA, and 2.0 mA . Data rate : 5 $$                                  |      |

|      | Gbps. Channel characteristics : Depicted in Fig. 1.5                                                 | 29   |

| 2.9  | Simulated eye diagram equalized using DT-DFE with one constant                                       |      |

|      | tap. The strength of the tap : $0.7~\mathrm{mA},1.0~\mathrm{mA},\mathrm{and}~2.0~\mathrm{mA}$ . Data |      |

|      | rate : 5 Gbps. Channel characteristics : Depicted in Fig. 1.5                                        | 30   |

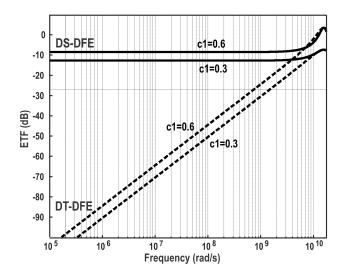

| 2.10 | STF of both DFEs with different normalized taps                                                      | 32   |

| 2.11 | ETF of both DFEs with different normalized taps                                                      | 33   |

| 2.12 | Error propagation. (a) Tap tuning perspective. (b) DFE per-                                          |      |

|      | spective. Error bits are highlighted                                                                 | 35   |

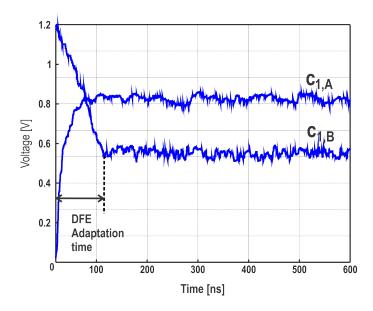

| 2.13 | Adaptation process of taps $v_A^+$ and $v_B^+$ of proposed DT-DFE.                                   | 37   |

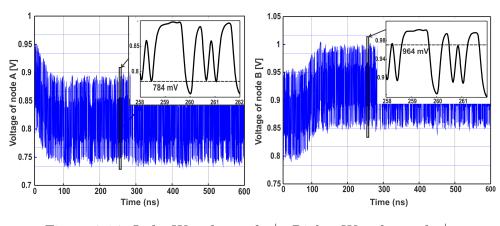

| 2.14 | Left: Waveform of $v_A^+$ . Right: Waveform of $v_B^+$                                               | 38   |

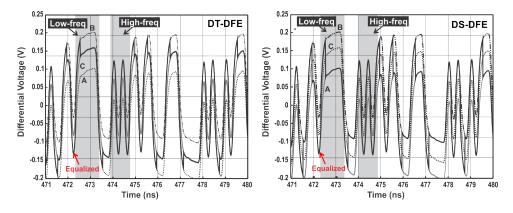

| 2.15 | Voltages of paths A, B, C, and equalized data (solid line)                                           | 38   |

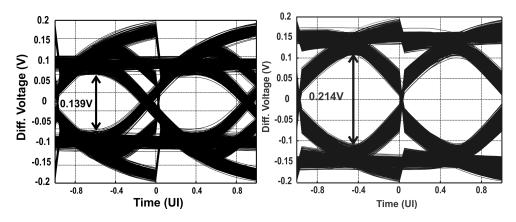

| 2.16 | Eye diagrams. Left: DS-DFE. Right: DT-DFE                                                            | 39   |

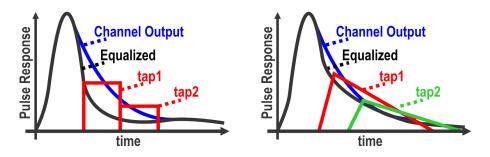

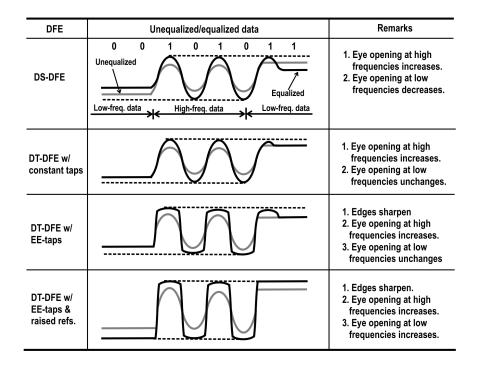

| 3.1  | Comparison of DS-DFE, DT-DFE with constant taps, DT-DFE                                              |      |

| 0.1  | with EE taps, and DT-DFE with EE-taps and raised references.                                         | 41   |

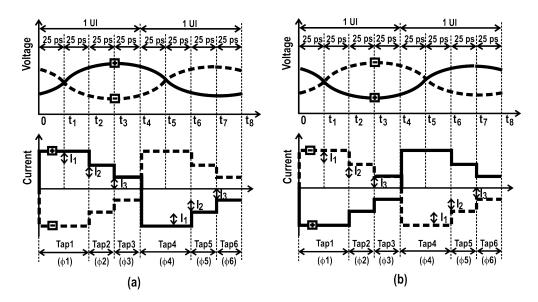

| 3.2  | Top : Voltages of unequalized data. Bottom : Currents of EE-taps.                                    | 11   |

| 0.2  | (a) EE-taps for 010 transitions. (b) EE-taps for 101 transitions                                     | 42   |

| 3.3  | Schematic of edge-emphasis taps for 010 transitions. The polarity                                    | 14   |

| 0.0  | in each tap indicates the polarity of the tap                                                        | 43   |

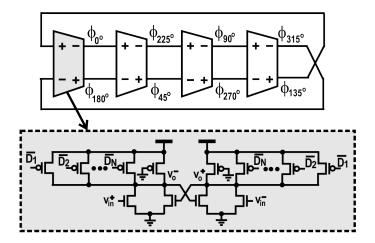

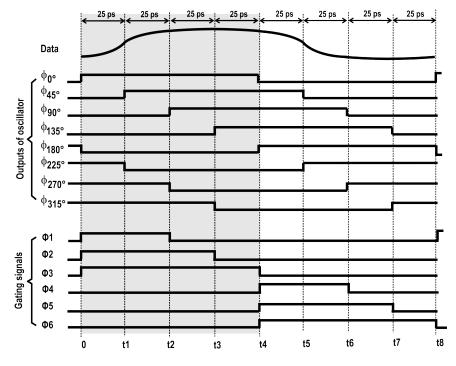

| 3.4  | 4-stage digitally controlled differential ring oscillator.                                           | 44   |

| 0.4  | T-suage dignamy controlled differential tilly oscillator                                             | -1-1 |

| 3.5  | Gating signals for edge-emphasis taps                                                                                                                     | • | 45 |

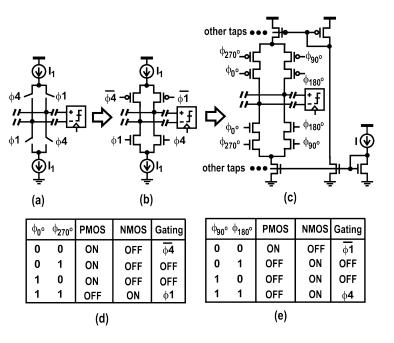

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|

| 3.6  | Implementation of tap $1. \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                 |   | 46 |

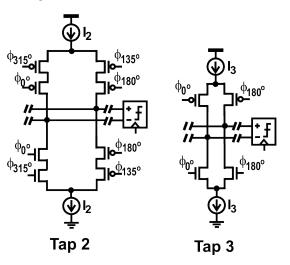

| 3.7  | Implementation of taps 2 and 3. The implementation of the current                                                                                         |   |    |

|      | sources is detailed in Fig. 3.6                                                                                                                           | • | 46 |

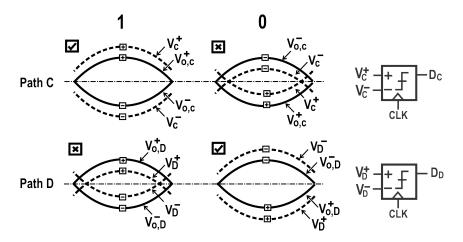

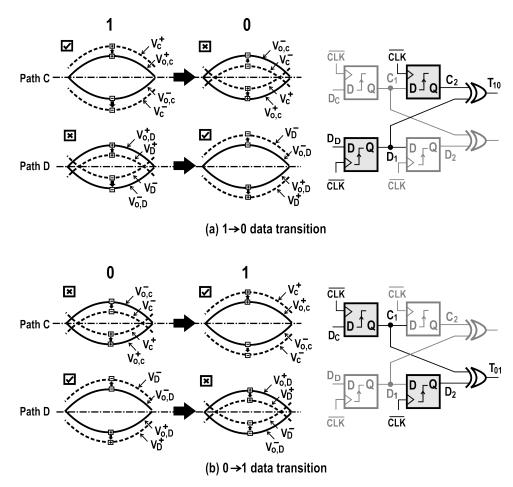

| 3.8  | DT-DFE with an EE-tap when a data transition is present. When                                                                                             |   |    |

|      | no data transition is present, DT-DFE with a constant tap is per-                                                                                         |   |    |

|      | formed                                                                                                                                                    | • | 48 |

| 3.9  | Selection of equalized data. The polarity box on the waveform                                                                                             |   |    |

|      | indicates the polarity of the signal. The check box at the top-left                                                                                       |   |    |

|      | corner of each sub-figure indicates whether the output of the slicer                                                                                      |   |    |

|      | is selected ( $\checkmark$ ) or discarded ( $\times$ )                                                                                                    | • | 49 |

| 3.10 | Detection of the occurrence of $1{\rightarrow}0$ and $0{\rightarrow}1$ data transitions.                                                                  | • | 50 |

| 3.11 | Determination of reference voltages $V_{ref+}$ and $V_{ref-}$ using 8-bit                                                                                 |   |    |

|      | SAR ADCs                                                                                                                                                  | • | 53 |

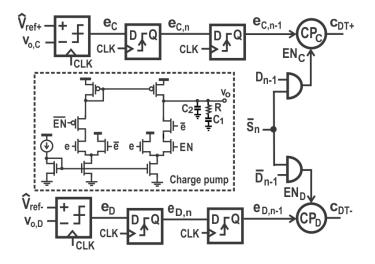

| 3.12 | Circuit that implements S <sup>3</sup> -LMS algorithms to obtain $c_{DT+}$ and                                                                            |   |    |

|      | $c_{DT-}\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ | • | 55 |

| 3.13 | Circuit that implements S <sup>4</sup> -LMS algorithms to obtain $c_{EE}$                                                                                 | • | 57 |

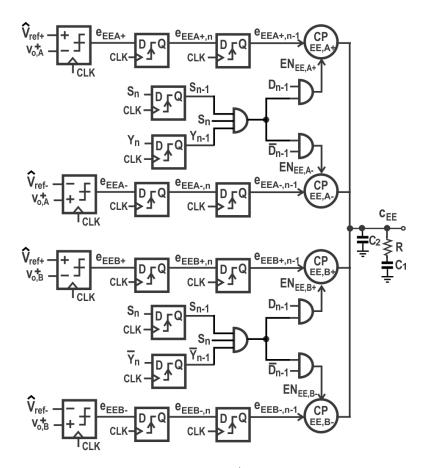

| 3.14 | Top-left : Edge generator. Top-right : Edge accumulator. Bottom                                                                                           |   |    |

|      | : Phase mapping between the phase of incoming data and that                                                                                               |   |    |

|      | of EE-tap gating signals. Legends : $0^\circ, \ 45^\circ, \ldots$ : The phase of                                                                          |   |    |

|      | incoming data. $\hat{0}^{\circ},\hat{45}^{\circ},\!$ : The phase of EE-tap gating signals                                                                 | • | 58 |

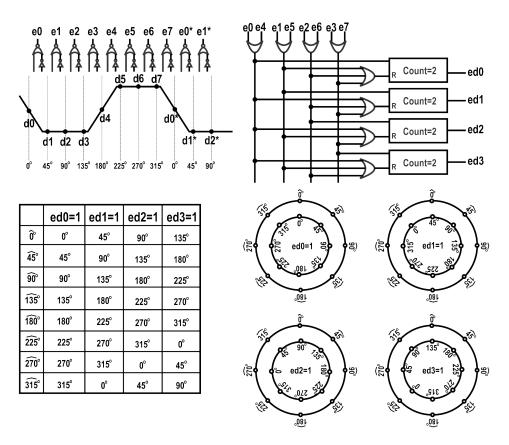

| 3.15 | Time and frequency responses of the backplane channel. The input                                                                                          |   |    |

|      | for the time-domain response is a 200 mV pulse of 100 ps pulse                                                                                            |   |    |

|      | width measured at the near end of the channel. $\ldots$ $\ldots$ $\ldots$                                                                                 | • | 60 |

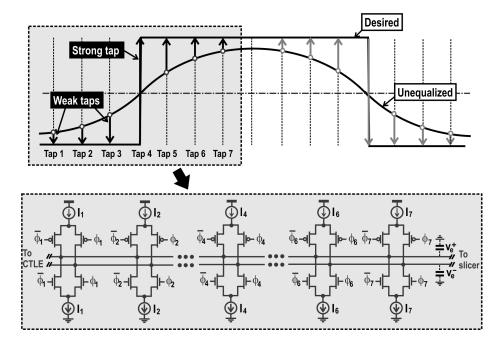

| 3.16 | DT-DFE with an EE-tap. The EE-tap consists of 7 taps of different                                                                                         |   |    |

|      | strength.                                                                                                                                                 | • | 61 |

| 3.17 | Comparison of DS-DFE, DT-DFE with a constant tap, and DT-                                                                                                 |   |    |

|      | DFE with an EE-tap. The light-color traces in (a,b,c) are unequal-                                                                                        |   |    |

|      | ized data                                                                                                                                                 | • | 62 |

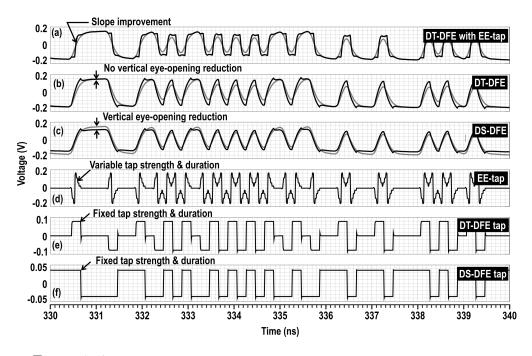

| 3.18 | Eye diagrams of unequalized and equalized data with DS-DFE,                                                                                               |   |    |

|      | DT-DFE with a constant tap, and DT-DFE with an EE-tap                                                                                                     |   | 63 |

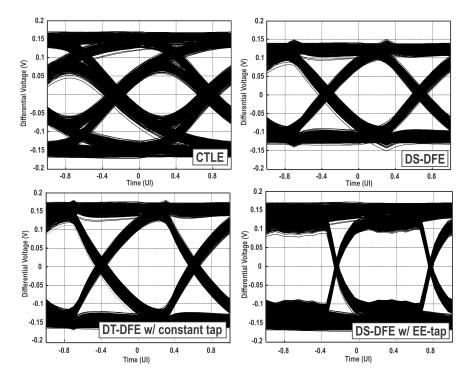

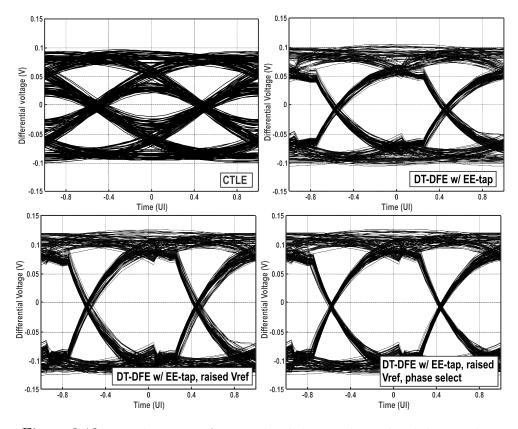

| 3.19 | Eye diagrams of unequalized data and equalized data with 3 dif-                  |    |

|------|----------------------------------------------------------------------------------|----|

|      | ferent settings                                                                  | 65 |

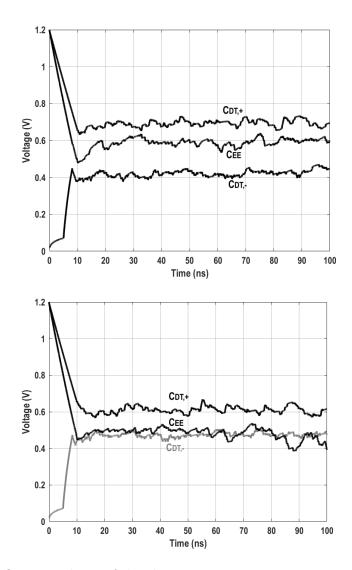

| 3.20 | Output voltage of the charge pumps tuning $c_{DT+}$ , $c_{DT-}$ , and $c_{EE}$ . |    |

|      | Top : Adaptation without raised references. Bottom : Adaptation                  |    |

|      | with $20 \text{mV}$ raised references                                            | 67 |

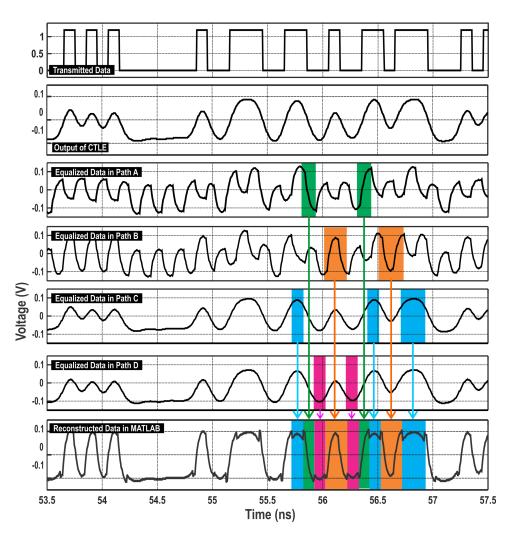

| 3.21 | Waveforms of transmitted, received, and equalized data                           | 68 |

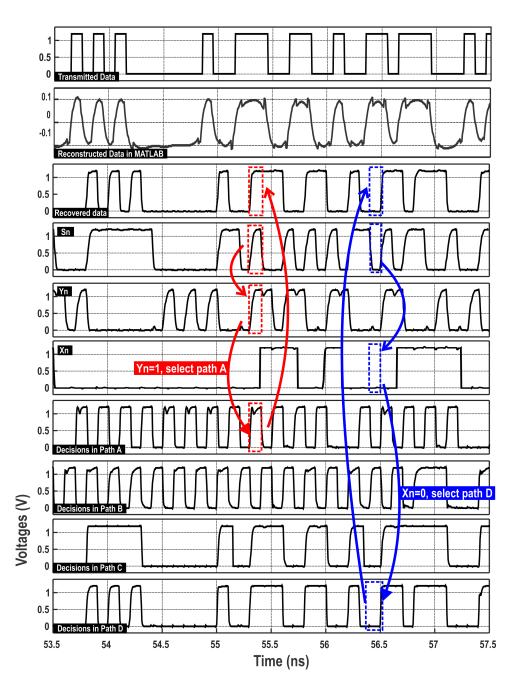

| 3.22 | Waveforms of transmitted, received, and recovered data. $\ldots$ .               | 69 |

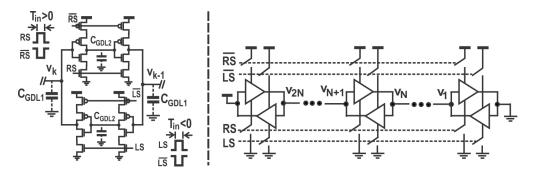

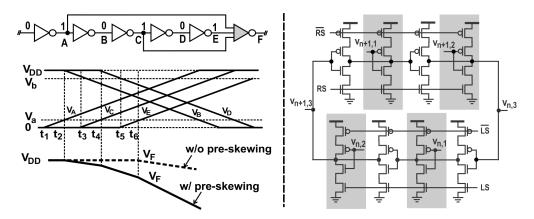

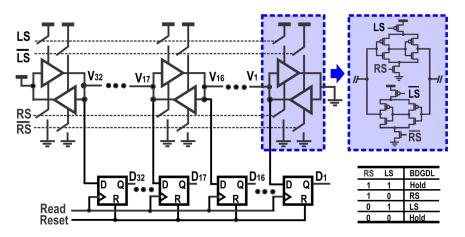

| 4.1  | Left: bi-directional gated delay cell (BDGDC). Right: bi-directional             |    |

|      | gated delay line. Legends : RS - Right-shift. LS - left-shift                    | 73 |

| 4.2  | Left: pre-skewing in a delay line. Right: pre-skewed BDGDL.                      |    |

|      | Pre-skewed inverters are highlighted                                             | 74 |

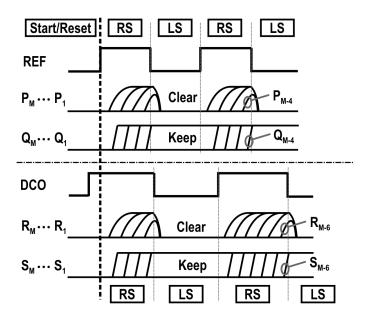

| 4.3  | Dependence of per-stage-delay (left) and power (right) on the                    |    |

|      | number of pre-skewed inverters                                                   | 75 |

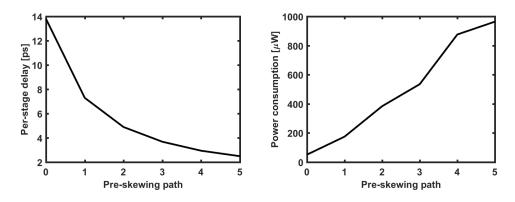

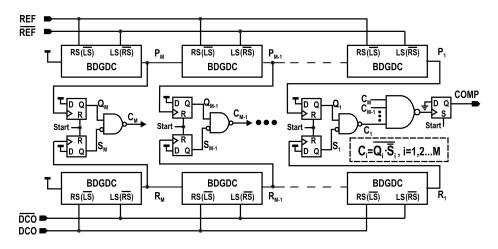

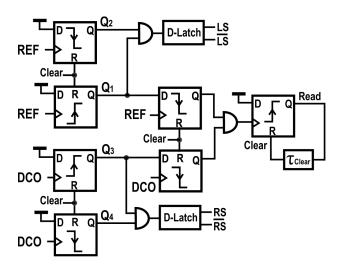

| 4.4  | Schematic of BDGDL frequency detector                                            | 75 |

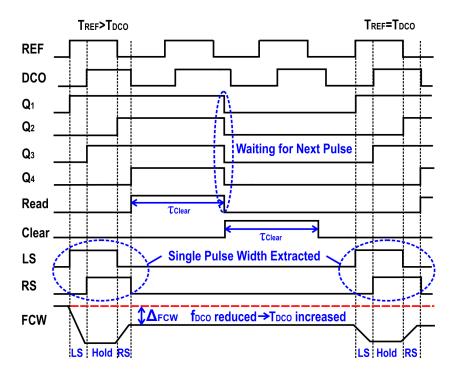

| 4.5  | Timing diagram of BDGDL frequency detector                                       | 76 |

| 4.6  | Frequency relationship implied by per-stage pulse width de-                      |    |

|      | tection results.                                                                 | 77 |

| 4.7  | schematic of a K-bit redundant successive approximation reg-                     |    |

|      | ister                                                                            | 78 |

| 4.8  | schematic of the DCO and varactor                                                | 78 |

| 4.9  | Block diagram of proposed FLL                                                    | 79 |

| 4.10 | Frequency detector dead zone reflects on FD and DCO transfer                     |    |

|      | characteristics, and the maximum locking error under different                   |    |

|      | circumstances                                                                    | 80 |

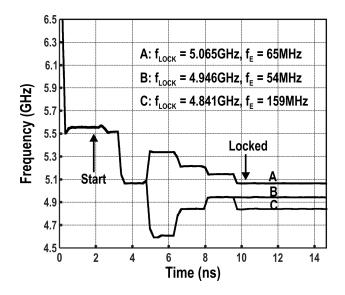

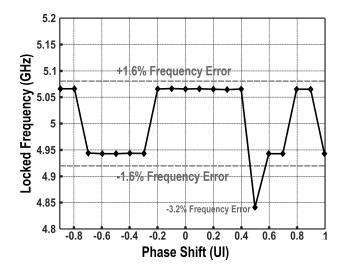

| 4.11 | Simulation results of frequency locking process                                  | 82 |

| 4.12 | Locked frequency with intentionally added phase shift                            | 82 |

| 4.13 | Breakdown of power consumption by key blocks                                     | 83 |

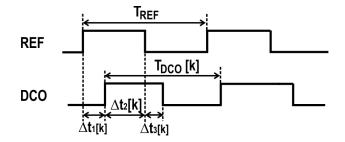

| 4.14 | Timing diagram of REF and DCO.                                                   | 84 |

| 4.15 | Schematic of pulse width extractor.                                              | 85 |

| 4.16 | Timing diagram of gating signal generation and FCW adaptation.                   | 86 |

| 4.17 | Bi-directional gated delay line with read-out DFFs                               | 86 |

|      |                                                                                  |    |

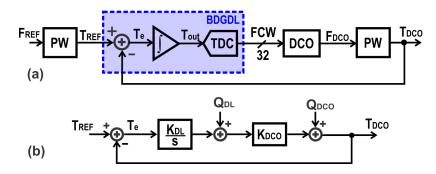

| 4.18 | (a) Frequency-locked loop with an iFDDC. (b) Block diagram of     |    |

|------|-------------------------------------------------------------------|----|

|      | the core of frequency-locked loop with an iFDDC                   | 88 |

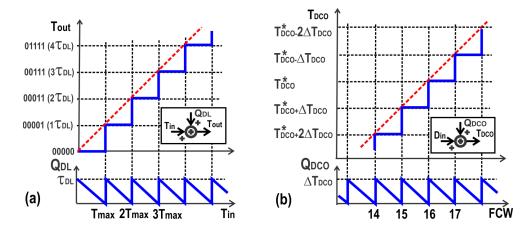

| 4.19 | Quantization error of BDGDL (a) and DCO (b). The center fre-      |    |

|      | quency of the DCO is set to $f^* = 1/T^*$ at which FCW=0011       |    |

|      | with 16 0s and 16 1s                                              | 89 |

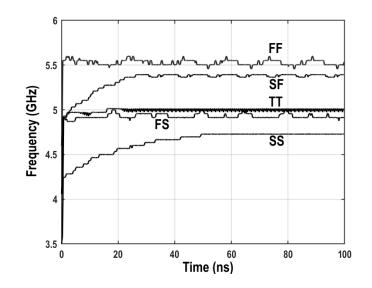

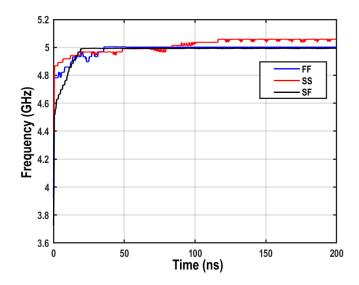

| 4.20 | Locking process of ADFLL in nominal process conditions $(TT)$ and |    |

|      | process corners (FF, FS, SF, and SS)                              | 91 |

| 4.21 | Locking process of ADFLL at process corners with tuned DCO        | 91 |

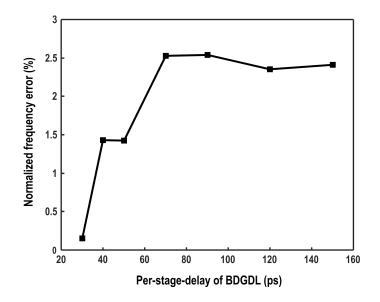

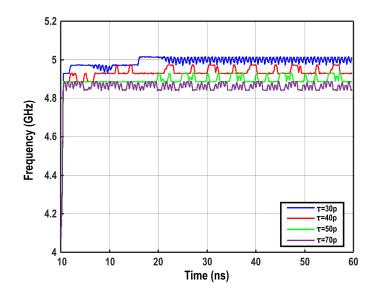

| 4.22 | Impact of per-stage-delay of BDGDL on normalized steady state     |    |

|      | frequency error of ADFLL                                          | 92 |

| 4.23 | Impact of per-stage-delay of BDGDL on locking process of ADFLL.   | 92 |

|      |                                                                   |    |

# List of Tables

| 2.1 | Data transition                                        | 32 |

|-----|--------------------------------------------------------|----|

| 2.2 | Hardware comparison of DS-DFE and DT-DFE               | 36 |

| 3.1 | Performance comparison of DFEs with different Settings | 63 |

| 3.2 | Performance comparison normalized to CTLE output       | 64 |

| 3.3 | Performance comparison of DT-DFE with EE-tap           | 66 |

| 3.4 | Performance comparison normalized to CTLE output       | 66 |

# List of Abbreviations

| ADC           | Analog-to-digital converter       |

|---------------|-----------------------------------|

| ADFLL         | All-digital frequency-locked-loop |

| BDGDL         | Bi-directional gated delay line   |

| BOS           | Blind oversampling                |

| CDR           | Clock and data recovery           |

| CP            | Charge pump                       |

| CTLE          | Continuous-time linear equalizer  |

| DAC           | Digital-to-analog converter       |

| DCO           | Digitally controlled oscillator   |

| DFE           | Decision feedback equalizer       |

| <b>DS-DFE</b> | Data-state DFE                    |

| DRV           | Driver                            |

| DT-DFE        | Data-transition DFE               |

| DTU           | Data-transition unit              |

| $\mathbf{EE}$ | Edge emphasis                     |

| FCW           | Frequency control word            |

| FFE           | Feedforward equalizer             |

| FIR                    | Finite impulse response                               |

|------------------------|-------------------------------------------------------|

| FVC                    | Frequency-to-voltage-converters                       |

| IC                     | Integrated chip                                       |

| iFDDC                  | Integrating frequency difference-to-digital converter |

| IIR                    | Infinite impulse response                             |

| ISI                    | Inter-symbol interference                             |

| $\mathbf{LMS}$         | Least mean square                                     |

| PCB                    | Printed circuit boards                                |

| PLL                    | Phase-locked loop                                     |

| PRBS                   | Pseudo-random bit sequence                            |

| $\mathbf{R}\mathbf{X}$ | Receiver                                              |

| SAR                    | Successive approximation register                     |

| SBR                    | Single bit response                                   |

| TDC                    | Time-to-digital converter                             |

| $\mathbf{T}\mathbf{X}$ | Transmitter                                           |

| UI                     | Unit interval                                         |

### Chapter 1

### Introduction

This chapter examines the characteristics of wire channels and existing equalization techniques. An overview of Gb/s serial links and challenges encountered in design of Gb/s serial links are given in Section 1.1. The characteristics of wire channels are studied briefly in Section 1.2. Three most widely used channel equalization techniques to combat the imperfections of wire channels are introduced in Section 1.3 with an emphasis on decision feedback equalization. Section 1.4 presents the motivation of this research and outlines the reasons why the research focused on DFE. The following Section 1.5 highlights the objective of the the research work. The organization of this thesis is detailed in Section 1.6. Research publications originated from this research are given in Section 1.7. The chapter is concluded in Section 1.8.

#### 1.1 Serial Links

The explosive growth of data processed by integrated circuits (ICs) demands that data be transmitted over wire channels (interconnects, vias, connectors, package pins, printed circuit boards PCBs, and coaxial cables) at multiple giga-bit-per-second (Gbps). Although increasing the number of wire channels directly improves the total data bandwidth, a large number of parallel

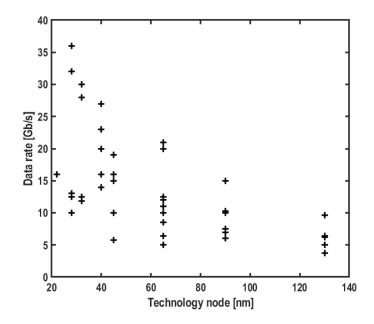

Figure 1.1: Dependence of data rate on the minimum channel length of MOS transistors.

channels not only increase the cost of routing, the overall data rate is also affected by clock and data skews caused by the mismatch of the channels. As a result, parallel links are only attractive for short-range data communications such as multi-processor systems, processor-to-memory interfaces, and network switches. Unlike parallel links, serial links transmit data and clock using a single wire channel, typically a pair of differential wires to minimize electromagnetic interference with neighboring devices. The elimination of a dedicated channel for clock transmission removes the difficulties associated with clock skew. The use of only a single wire channel also eliminates the bottle neck associated with data skew. Moreover, it greatly reduces the cost associated with routing. As a result, serial links are attractive in applications such as block-to-block (on-chip), chip-to-chip, chassis-to-chassis, and computer-to-computer links where the distance over which data are transmitted is large and the number of channels available is small. Although the maximum transit frequency of MOS transistors has well exceeded 100 GHz, the data rate of serial links is much lower, as evident in Fig. 1.1. The low data rate is mainly due to inter-symbol interference (ISI) arising from channel imperfections. In wire channels, ISI is mainly caused by skin-effect and dielectric loss that leads to frequency dependent attenuation, or dispersion. Pulse widening caused by reflections and interference from cross-talks also bring additional ISI [1, 2, 3, 4, 5]. ISI manifests itself as pre-cursors and post-cursors with the latter dominate typically [6, 7].

#### 1.2 Wire Channels

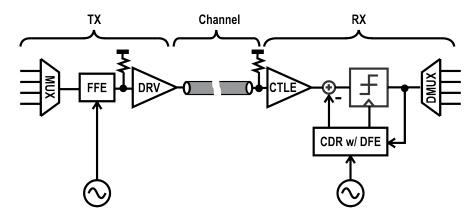

Figure 1.2: A typical structure of serial links.

Fig. 1.2 shows the structure of a typical serial link, which consists of a transmitter (TX), a wire channel, a receiver (RX). A feed-forward equalizer (FFE) also known as pre-emphasis resides in the transmitter while a continuous-time linear equalizer (CTLE) and a decision feedback equalizer (DFE) reside in the receiver. The multiplexer (MUX) in the TX multiplexes low-rate data in the parallel buses into a high-rate data stream and feeds it forward to the channel. The RX recovers the digital bits from the received data stream with a clock and data recovery (CDR) block and a slicer. The demultiplexer (DMUX) converts the received serial data stream back to

low-speed parallel data. The equalizers combat the impact of channel imperfections while the CDR block adjusts RX clock frequency and phase to guarantee the correct sampling of the slicer.

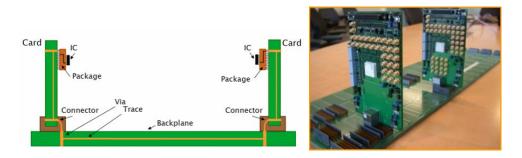

Figure 1.3: A backplane example.

Fig. 1.3 is a typical example of a backplane data communication environment. Data and clock are transmitted simultaneously via the same wire channel with timing information embedded in data as transitions. At Gb/s data rates, channels suffer from two major frequency-dependent losses.

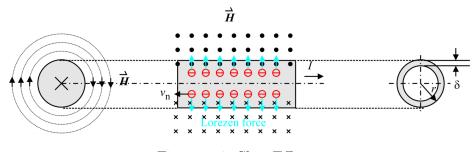

Figure 1.4: Skin Effect.

The first loss mechanism is resistive loss which is induced by conductor's skin effect. At low frequencies, the current flows evenly through the cross section of the conductor. At high frequencies, due to either the rapid current direction alteration inside the wire or outside in another adjacent wire, the current tends to follow only near the conductor surface due the induced magnetic field as illustrated in Fig. 1.4.

Skin depth, which is the depth at which the current density decays to electrons of that at the surface, is given by

$$\delta = \sqrt{\frac{1}{\sigma \pi f \mu}},\tag{1.1}$$

where  $\delta$  is the skin depth, f is frequency,  $\mu$  is permeability, and  $\sigma$  is the material conductivity. Since the skin depth is inversely proportional to  $\sqrt{f}$ , the resistive channel loss increases proportionally with  $\sqrt{f}$ .

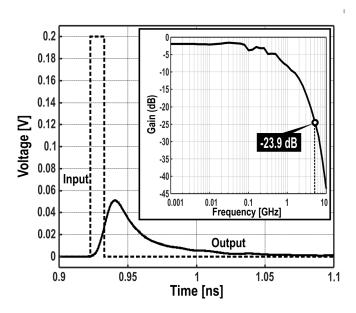

Figure 1.5: Channel loss. Left: time domain response Right: frequency domain response

The second channel loss mechanism is dielectric loss. Dielectric dissipation is induced by the polarization of the molecules in dielectric materials and is illustrated in Fig. 1.4. When an alternating electric field is applied, molecules in the dielectric material rotate so as to align with the either external or internal electric field. The molecules rubs against each other during movements and covert some of the electric energy into heat. The loss is directly related to the speed of field direction rotation. Dielectric loss  $L_D$  can be expressed as

$$L_D = \frac{4.34}{c} 2\pi f \cdot tan(\sigma) \sqrt{\varepsilon_{r,eff}},$$

(1.2)

where  $tan(\sigma)$  is the loss tangent of the dielectric material. It shows  $L_D \propto f$ and dielectric loss surpasses resistive loss at high frequencies. Both of these channel losses increase with frequency. Channel loss normally falls from 20 to 30dB for baud-rate of 10+ Gbps serial links [8, 9, 10]. Fig. 1.5 shows the response of a lossy channel in both time and frequency domains. In time domain, received data lose more energy at high frequencies and leak energy to adjacent symbols, giving rise to ISI. Among all the channel impairments, bandwidth limitation caused ISI dominants in high data-rate applications. Therefore, limited bandwidth is the main impairment that channel equalization techniques are developed to combat.

#### **1.3** Channel Equalization

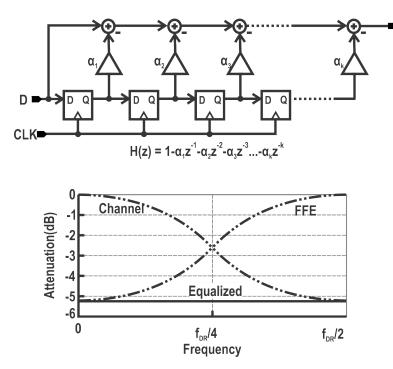

ISI manifests itself as pre-cursors and post-cursors and can be minimized via channel equalization at either the near and far ends of channels. Pre-cursors and post-cursors can be removed by either boosting the high-frequency components [6, 7] or attenuating the low-frequency components of data symbols prior to their transmission [11, 12]. This is known as pre-emphasis. The former increases cross-talk as crosstalk intensifies at high frequencies whereas the latter reduces the power of the transmitted symbols as the power of non-return-to-zero data is largely concentrated at half baud-rate frequency. Near-end channel equalization is often implemented using finite impulse response (FIR) filters that introduce zeros to offset the effect of the poles of the channels, as shown in Fig. 1.6 [13, 6, 7]. By adjusting the tap wights, a relatively flat equalized channel response can be obtained. Since the characteristics of the channel are not known prior to data transmission, the optimal tap coefficients of pre-emphasis FIR filters can only be obtained if a back channel exists. This constraint severely undermines the robustness of preemphasis channel equalization. Another limitation of FFE is the equalizer attenuates low-frequency components of data to achieve channel equalization instead of amplifying high-frequency components. The purpose is to minimize crosstalk. Data equalized with FFE will experience signal power loss due to this. The last limitation of pre-emphasis channel equalization is its inability to remove ISI caused by reflection and crosstalk as these ISI manifest themselves as crests and troughs rather than uniformly sloped attenuation. ISI caused by reflection and crosstalk is typically significant when channels contain multiple vias, connectors, and branches (highly reflective channels).

Figure 1.6: Feed-forward equalizer. Top: Block diagram. Bottom: Spectral behavior ( $f_{DR}$ : Data rate frequency).

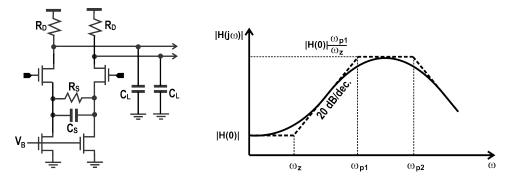

Far-end channel equalization also known as post-equalization combats ISI by either amplifying the high-frequency components of received data symbols in the analog domain or removing post-cursors in the digital domain prior to clock and data recovery (CDR). As compared with near-end equalization, post-equalization offers the ability to combat ISI caused by reflection and crosstalk, and is therefore the most widely used and effective channel equalization techniques. Post channel equalization can be performed using either a linear equalizer or a nonlinear equalizer, or both. Linear post-equalization boosts the high-frequency components of received symbols with a continuoustime linear equalizer (CTLE), as shown in Fig. 1.7 [12, 14]. CTLE provides zeros to cancel out the poles of the channels so that the equalized channel exhibits an all-pass transfer characteristic. The RC load and source degeneration circuit provides one zero and two poles, which are given by

$$\omega_z = \frac{1}{R_S C_S},\tag{1.3a}$$

$$\omega_{p1} = \frac{1}{R_L C_L},\tag{1.3b}$$

$$\omega_{p2} = \frac{1 + 0.5(g_m + g_{mb})R_S}{R_S C_S}.$$

(1.3c)

Figure 1.7: CTLE. Left: Schematic. Right: Spectral behavior

Since the maximum rising slope of this single-zero CTLE is +20dB/dec, the product of the peaking gain and the second pole (bandwidth), which denotes the peaking factor satisfies

$$A_0 \frac{\omega_{p1}}{\omega_z} \omega_{p2} \approx \frac{g_m}{C_L}.$$

(1.4)

This means that the performance of CTLE in terms of peaking gain and bandwidth is limited by the cut-off frequency of the technology. Also, due to the high bandwidth and linearity requirements, CTLE tends to be power hungry. On top of this, the difficulty of designing a CTLE with higher order of zero peaking also limits its development. In current high speed serial links, CTLE serves as an standard front-end of RX just to guarantee the minimal vertical eye-opening of received data and leaves the rest of the calibration work to decision feedback equalization (DFE).

Figure 1.8: DFE block diagrams. Top: Regular. Bottom: Loop-unrolling.

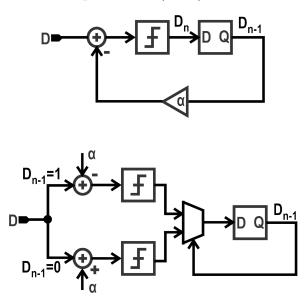

Unlike CTLE, nonlinear post-equalization mitigates the effect of channel loss, reflection, and crosstalk by removing the post-cursors of the received symbol in the digital domain. The most widely used nonlinear equalization is DFE. A single tap DFE is shown in Fig. 1.8. It directly remove post-cursor ISI of the previous symbol from the current symbol. Another point of view it is that the DFE adjusts the slicer threshold depending on the previous data state. Since DFE does not amplify received data symbols, it does not deteriorate crosstalk with neighboring devices. Moreover, since the number, the weight, and the order of the taps of DFE can be adjusted in accordance with the characteristics of the channel to be equalized, DFE is not only most effective in eliminating ISI caused by the finite bandwidth of the channel, it is also most effective in eliminating ISI caused by reflection and crosstalk. Since DFE only utilizes the past decisions, it has no effect on pre-cursors.

In a regular DFE, the multiplication and addition/subtraction need to be

Figure 1.9: Comparison between FEE and DFE.

completed in one UI, which is a significant challenge at high data rate. To relax this time constraint, DFE with loop-unrolling structure is developed by moving the multiplication and addition/subtraction out of the feedback loop [15, 16]. The final decision is selected from two slicer according to previous recovered data [17, 18, 19, 20]. By using loop-unrolling technique in DFE, the one-UI time constraint is only applied to the slicer. The complexity of the loop-unrolling DFE increases exponentially with the number of loop-unrolled taps. Loop-unrolling has been used for the first 2 taps in [21] to cope with 28 Gbps data rate and first 3 taps in [22, 23] to cope with 30 Gbps data rate. Fig. 1.9 plots the transfer characteristics of FFE and DFE. It shows DFE boosts the high frequency components to achieve channel equalization while the method of FFE is attenuating the low frequency components. To sum up, DFE has more potential on performance improvements due to its post-channel digital equalizer nature.

DFE using infinite impulse response (IIR) filtered feedback signal are also widely adopted to combat the long ISI induced by severe channel loss [8, 24, 25, 26, 27]. Channel has loss dominated by skin effect will have longer tail of a impulse response compared to channel has loss dominated by

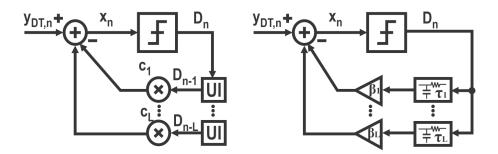

Figure 1.10: DFE with L taps. Left: Conventional DS-DFE. Right: IIR-DFE.

Figure 1.11: Equalization with different types of DFEs. Left: Conventional DS-DFE. Right: IIR-DFE.

dielectric loss even with the same baud-rate channel loss. Fig. 1.10 shows the block diagram of conventional DS-DFE and IIR-DFE. It is seen the key difference between two DFEs is the generation of feedback signal. DS-DFE multiplies the delayed slicer output with tap coefficient to construct a series of discrete time feedback signal to cancel ISI. IIR-DFE feed the slicer output to RC networks with different time constant to construct a series of continuous time feedback signal to cancel ISI. Fig. 1.11 shows the time domain behavior with a 2-tap example of both DFEs. The advantages and limitations of each DFE are evident: conventional DS-DFE has strong feedback signal can improve equalized data slope effectively. Since active duration of each DS-DFE tap is constant of one unit interval (UI), DS-DFE taps with programmable delays have been used to remove reflections in the channel [1, 2, 3], called floating or roving tap DFE. However its complexity and power consumption increase significantly for equalizing channel with a long tail of ISI. On the other hand, IIR-DFE is much more suitable for equalizing channel with long tail of ISI, however as seen in Fig. 1.11 (right), it is less effective on improve data edges due to the tap slope lost on the RC network. To solve this trade-off, hybrid DS- and IIR- DFE are developed to improve the data slope on the main post-cursor with a single DS-DFE tap and use IIR-DFE taps for the long tail of other post cursors [28, 29].

DFE in this dissertation will be based on the conventional discrete time feedback tap since we consider not all the post-cursor ISI is undesired. Only the post-cursor appears near data transitions will reduce the vertical eye opening therefore need to be removed. Post-cursors applied on consecutive data will improve vertical eye opening and should not be removed. Corresponding details will be addressed in the following Chapter.

#### 1.4 Motivation

Most reported DFE falls into the category of data-state (DS) DFE where taps are chosen to maximize the vertical eye opening of equalized data. DS-DFE searches for optimal taps using a sign<sup>2</sup> LMS algorithm that minimizes the error between the vertical eye-opening of desired and equalized data adaptively. DFE that either adds taps to or subtracts taps from incoming data, depending upon the decision of the slicer, is performed on every data. When consecutive 1s are present, DS-DFE will successively subtract taps from the incoming data, reducing vertical eye-opening. Similarly, when consecutive 0s are present, DS-DFE will add taps to the incoming data successively, resulting in reduced vertical eye-opening as well. The successive addition of taps to or subtraction of taps from incoming data not only reduces vertical eye-opening, it also alters the maximum and minimum eye-open boundaries. The eye-open boundaries are also used as the references with respect to which the equalized data are compared. As a result, the references of DS-DFE is tap-dependent and are not known a priori. They need to be obtained iteratively using DFE-like algorithms [30]. To overcome the aforementioned drawbacks of DS-DFE, DFE should not be performed when consecutive 1s or 0s are encountered in order to retain obtained vertical eye-opening. The reference voltages with respect to which the error between the references and the equalized data to be minimized should also be independent of taps such that they can be obtained in a preprocessing phase prior to DFE.

The effectiveness of DS-DFE is increasingly challenged by a shrinking aperture window at high data rates, arising from data-dependent and dataindependent data jitter with the former typically dominant. Data-edge (DE) DFE where taps are chosen to minimize data jitter so as to maximize the aperture window becomes increasingly attractive at high data rates [31, 32]. DE-DFE possesses a number of intrinsic characteristics including the reduced lock time of the receiver phase-locked loop (PLL) and relaxed constraints on the slew rate of the CTLE. Most reported DE-DFE trades performance for design simplicity by only utilizing the sign rather than value of data jitter. The absence of a constraint on vertical eye-opening in DE-DFE results in reduced vertical eye-opening. To overcome this, DS-DFE and DE-DFE are often deployed simultaneously [33, 34].

A common drawback of reported DS-DFE, DE-DFE, and DT-DFE is that tap strength remains constant over the entire data eye. The fact is that the impact of channel imperfection is most severe at the edges of the data eye where the high-frequency components of data concentrate. And channel imperfection is least severe at the center of data eyes where the low-frequency components of data reside. As a result, although equalized eyes have good vertical eye-opening at the center of data eyes, eye-opening drops rapidly when moving away from the center of data eyes, undermining the reduction of data jitter from channel equalization. As a consequence, stringent constraints must be imposed on both the slew rate of the output of the CTLE and the jitter of the receiver PLL.

#### 1.5 Objectives

The objectives of this research were to develop and implement novel adaptive DT-DFEs capable of overcoming the intrinsic drawbacks of DS-DFE. The DT-DFEs should be able to maximize the eye-opening, both vertically and horizontally, of the high-frequency components of received data without attenuating the low-frequency components of the data when consecutive 1s and 0s are encountered so as to retain obtained eye-opening. The performance of the DT-DFEs need to be validated quantitatively by comparing with the performance of the same data links equalized using conventional DS-DFE.

#### **1.6** Thesis Organization

Chapter 1 provides an overview of Gb/s serial links and challenges encountered. It briefly examines various channel equalization techniques with an emphasis on DFE, which is the core of the dissertation. The chapter also highlights the motivation of this study. Chapter 2 examines the intrinsic drawbacks of conventional data-state DFE. It introduces data-transition DFE that overcomes the drawbacks of DS-DFE. The characteristics of DT-DFE are studied in both time and frequency domains. To sharpen transition edges so as to maximize sampling window, DT-DFE with edge-emphasis taps is developed. The effectiveness of the proposed DT-DFE and DT-DFE with edge-emphasis taps is validated using simulation results. Chapter 3 introduces a DT-DFE with EE-taps and raised reference voltages capable of both sharpening the transition edges and enlarging the vertical eye-opening of equalized data. The effectiveness of the proposed DFE is assessed using simulation results. Chapter 4 introduces two power-efficient all-digital frequency difference-to-digital converters and their applications in Gb/s clock and data recovery. The first utilizes two bi-directional gated delay lines (BDGDLs) to perform bang-bang frequency difference detection while the second uses

a single BDGDL to perform integrating frequency difference-to-digital conversion. Finally, the dissertation is summarized in Chapter 5 with a look at future work that is built upon the dissertation.

#### 1.7 Contributions

This dissertation makes the following original contributions :

• An adaptive DT-DFE with a sign<sup>3</sup> least-mean-square (LMS) algorithm is developed. The proposed DT-DFE boosts the high-frequency components of data without attenuating their low-frequency components, overcoming the intrinsic drawbacks of DS-DFE that achieves the same level of eye-opening at the expense of the attenuated low-frequency components of data. The maximum and minimum vertical eye-opening of DS-DFE is tap-dependent whereas that of DT-DFE are tap -independent and can be obtained by conveying consecutive 1s and 0s to the channel in a training phase prior to DFE and measuring the resultant output of the CTLE using successive approximation register analog-todigital converters (SAR ADCs). The proposed DT-DFE utilizes a loopunrolling approach to both detect the occurrence of data transition so as to activate tap tuning and DFE, and combat timing constraints. The effectiveness of the proposed DFE has been validated using simulation results.

#### **Publication**:

- Y. Li and F. Yuan, "Sign3-LMS data-transition decision feedback equalizer," IET Circuits Devices Systems, vol.13, no. 7, pp. 998-1006, Nov. 2019.

- Y. Li and F. Yuan, "Data-transition decision feedback equalizer with S3-LMS adaptation algorithm," Proc. IEEE Int'l NEWCAS Conf., pp.221-224, Montreal, Que., Canada, June 2018.

- Y. Li and F. Yuan, "Adaptive data-transition decision feedback equalizer for serial links," Proc. IEEE Mid-West Symp. Circuits and Systems, pp. 1609-1612, Boston, USA, 2017.

- Y. Li and F. Yuan, "Data-transition adaptive decision feedback equalizer for 2/4 PAM serial links," Proc. IEEE Mid-West Symp. Circuits and Systems, pp. 531-534, Boston, USA, 2017.

- An adaptive DT-DFE with edge-emphasis taps and raised references was developed. The proposed DT-DFT improves both transition edge slopes and vertical eye-opening simultaneously. Loop-unrolling normally used to combat the timing constraints of data-state DFE is further developed for DT-DFE with EE-taps. The reference voltages with respect to which the error signals of DFE are defined are raised beyond that set by the low-frequency components of data to increase vertical eye-opening. Clock and data recovery is performed using blind 4x oversampling and phase-picking. The effectiveness of the proposed DFE has been validated using simulation results of a 10 Gb/s serial link.

#### **Publication**:

- Y. Li and F. Yuan, "Adaptive edge-emphasis data-transition DFE with raised references in oversampling CDR," IEEE Trans. Circuits and Systems I - Regular Papers. Submitted in August 2019 (invited).

- Y. Li and F. Yuan, "Data-transition decision feedback equalizer with edge-emphasis taps and raised references," IEEE NEWCAS, Munich, Germany, June 2019.

- Y. Li and F. Yuan, "Data-transition decision feedback equalizer with edge-emphasis taps," presented at IEEE Int'l Symp. on Circuits and Systems, Florance, Italy, as a "breaking news" paper, May 2018.

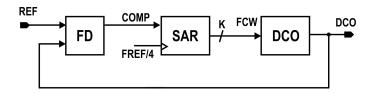

• A pre-skewed BDGDL bang-bang frequency detector (BBFD) is developed and applied to frequency-locking of 10 Gb/s serial links. Bangbang frequency detection is performed using a pair of BDGDLs that digitize the logic-1 pulse of receiver oscillator and a reference clock. A redundant successive approximation register (SAR) driven by the output of the BBFD is used to generate the frequency control word (FCW) of the digitally controlled oscillator (DCO) of the receiver. A frequency detection decision can be made in only 4 cycles of the reference clock. The effectiveness of the proposed DFE has been validated using simulation results of a 5 GHz frequency-locked loop.

<u>Publication</u>: Y. Li and F. Yuan, "A pre-skewed bi-directional gated delay line bang-bang frequency detector with applications in 10 Gbps serial link frequency-locking," IEEE Mid-West Symp. Circuis Syst., pp. 263-266, Dallas, TX, Aug. 2019.

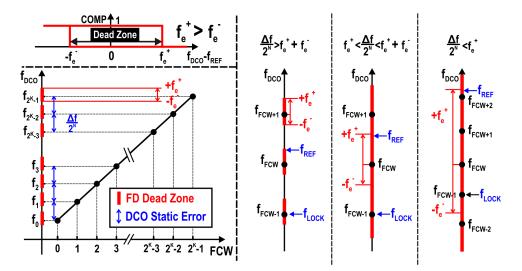

• An all-digital low-power high-speed integrating frequency difference-todigital converter (iFDDC) is proposed. The iFDDC utilizes a BDGDL to detect the difference between the frequencies of two 50% duty-cycle square waves. The iFDDC possesses attractive characteristics including all-digital, low power consumption, high-speed operation, and built-in integration. The built-in integration of the iFDDC results in zero static frequency error and first-order noise-shaping when the iFDDC resides in a frequency-locked loop. When the quantization errors of BDGDL and DCO are accounted for, the static frequency error of the FLL is proportional to the quantization errors of the BDGDL and DCO. The effectiveness of the iFDDC has been validated in a 5-GHz frequencylocked loop designed in a TSMC 65 nm 1.2V CMOS.

#### 1.8 Summary

An overview of Gb/s serial links was presented and challenges encountered in design of Gb/s serial links were examined. The characteristics of wire channels were studied briefly with an emphasis on the loss of wire channels at high data rates. Various channel equalization techniques were briefly examined with an emphasis on DFE. The motivations of this study were provided. The organization of the dissertation was detailed and the original contributions of the dissertation including research publications were provided.

## Chapter 2

### **Data-Transition DFE**

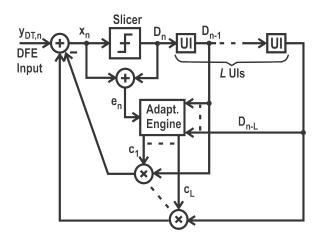

Data-state (DS) DFE widely used to combat the impact of the imperfections of wire channels in serial links suffers from an intrinsic drawback of shrunk vertical eye-opening when consecutive 1s or 0s are encountered in data to be equalized. To overcome this fundamental drawback of DS-DFE, in this chapter, we propose a new adaptive data-transition (DT) DFE that performs DFE only when a data transition is present in data to be equalized as to retain vertical eye-opening. Section 2.1 examines the fundamental limitations of DS-DFE. Section 2.2 presents the architecture, algorithm, and implementation of the proposed DT-DFE. Section 2.3 investigates the intrinsic differences between DS-DFE and DT-DFE, error propagation in DS-DFE and DT-DFE, loop-unrolling, and the hardware cost of DS-DFE and DT-DFE. In Section 2.4, the effectiveness of the proposed DT-DFE is compared with that of DS-DFE with the aid of two 5 Gbps backplane serial links. The chapter is concluded in Section 2.5.

#### 2.1 DS-DFE Limitations

Fig. 2.1 shows the configuration of a conventional DS-DFE with 2PAM signaling. The difference between equalized data symbols  $y_{DT,n}$  and desired data symbols  $D_n$ , denoted by  $e_n$ , is used to guide the search for optimal tap coeffi-

Figure 2.1: Data-state DFE.

cients  $c_l$ , l = 1, 2, ..., L, from which the post-cursors of the data are estimated. The estimated post-cursors of past data are then subtracted from the current data symbol to remove their impact. Optimal tap coefficients are obtained iteratively by minimizing the power of  $e_n$  using the following sign-sign(SS)-LMS algorithm

$$c_{l,n+1} = c_{l,n} + h \operatorname{sgn}[e_n] \operatorname{sgn}[D_{n-1}], \qquad (2.1)$$

where h is the step size used to adjust  $c_1$ ,  $e_n$  is the difference between the equalized and desired data symbols at current sample n,  $D_n$  is the output of the slicer. The sign function is defined as sgn[x] = 1 if  $x \ge 0$  and -1 otherwise. Since the output of the slicer, which is the logic state of the equalized data, is used in (2.1). Therefore, the equalized data with DS-DFE is given by

$$y_{DT,n} = x_n - \sum_{l=1}^{L} c_l D_{n-l}.$$

(2.2)

Existing SS-LMS data-state DFE suffers from the following fundamental drawback: If the output of the slice is logic-1, i.e, data[n]=1, data-DFE will subtract DFE taps from the current data symbol so as to remove the post-cursors. This is desirable only if the next data is 0. If the next data

is also 1, the result of data-DFE operation will actually reduce rather than increase vertical eye-opening. To address this issue, we propose the DT-DFE algorithm uses a S<sup>3</sup>-LMS algorithm to search for optimal tap coefficients utilizing the state transition rather than the state of data. No DFE operation will take place if data transition is absent.

#### **2.2 DT-DFE**

#### 2.2.1 Architecture

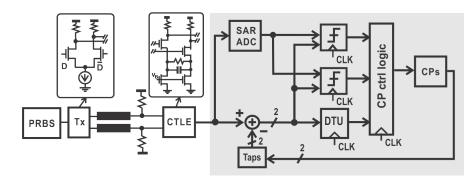

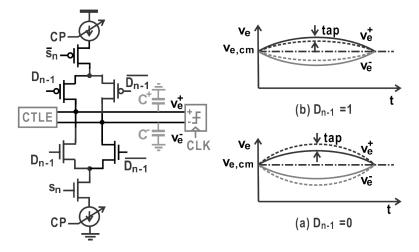

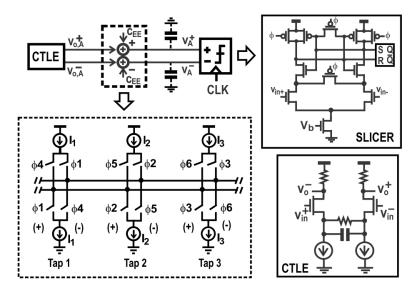

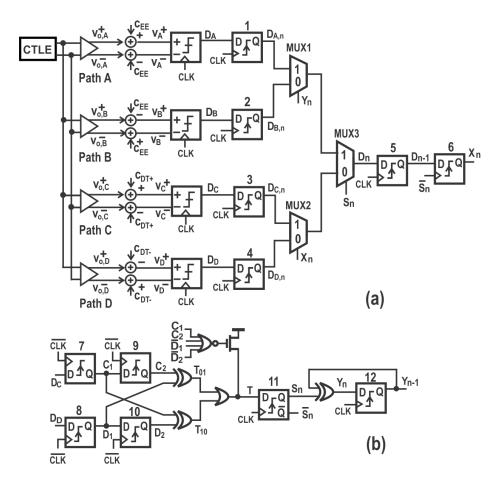

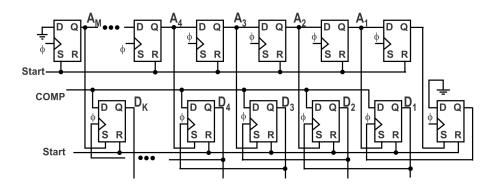

Figure 2.2: Architecture of sign<sup>3</sup>-LMS DT-DFE (highlighted part).

Fig. 2.2 shows the architecture of the proposed sign<sup>3</sup>-LMS DT-DFE. The output of the PRBS generator is fed to a current-mode transmitter that conveys a constant current to the channel. The channel is terminated at both ends to minimize reflection. The output of the CTLE is fed to SAR-ADCs where the maximum and minimum vertical eye-openings, denoted by  $V_{max}$  and  $V_{min}$ , respectively, are obtained in a 11-cycle training phase preceding DFE. Two slicers are employed to compare the equalized data with  $V_{max}$  and  $V_{min}$  so as to determine the sign of the difference (error) between the vertical eye-opening of desired and equalized data. The equalized data is also fed to a DTU where the occurrence of two consecutive data transitions of opposite polarities is detected. The output of the DTU is fed to the control logic block of the CPs that tune taps. The CP control logic determines whether

the charge pumps should be activated or not and the direction of the tuning of the charge pumps. Optimal taps are obtained by using a sign<sup>3</sup> LMS algorithm evolved from conventional sign<sup>2</sup> LMS algorithms. In the example presented, although only one tap is used, it is readily extended to multiple taps. Data equalized with proposed DT-DFE can be written as

$$y_{DT,n} = x_n - \sum_{l=1}^{L} c_l D_{n-l} s_n, \qquad (2.3)$$

where  $s_n$  is the data transition signal.  $s_n = 1$  denotes data transition presents from time instance n-1 to n.  $s_n = 0$  means no data transition occurs. Therefore, data is only equalized when  $s_n = 1$  which means DFE only activates when data transition presents.

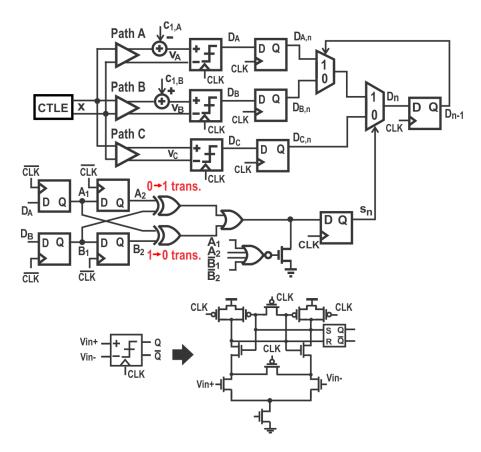

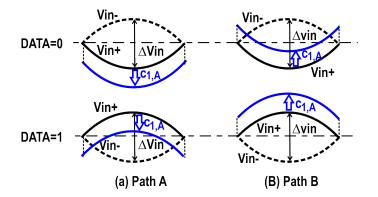

### 2.2.2 Data-Transition Unit

In order to determine whether a data transition occurs or not in *n*th cycle, both  $D_{n-1}$  and  $D_n$ , the previous and current decisions of the slicer, respectively, are needed. The former is readily available while the latter is not at the time of equalization. This difficulty can be overcome using the loop-unrolling approach commonly used to combat timing constraints of DFE [15]. Fig. 2.3 shows the simplified schematic of the DTU that utilizes loop-unrolling. It has three paths, namely paths A, B, and C. Path A performs DFE with the assumption  $D_{n-1} = +1$  and  $s_n = 1$ . Tap  $c_{1,A}$  implemented using a current source drains a current from the non-inverting terminal of the comparator such that  $v_A$  decreases. This is equivalent to subtracting the tap from the incoming data. Path B performs DFE with the assumption  $D_{n-1} = -1$  and  $s_n = 1$ . Tap  $c_{1,B}$  injects the constant current to the non-inverting terminal of the comparator such that  $v_B$  increases. This is equivalent to adding the tap to the incoming data. Path C performs no DFE and is selected only when no data transition is detected  $(s_n = 0)$ . The outputs of slides A and B are also sampled by DFFs at the falling edge of CLK to generate data transition signal  $s_n$ . To illustrate how  $s_n$  is generated, we consider two cases : (i) Case

Figure 2.3: Data transition unit.

1 (data=0) : In path A, since  $v_A$  decreases and data=0, the decision of slicer A is selected. In Path B, since  $v_A$  decreases and data=0, the decision of slicer B is discarded. Fig. 2.4 provides a graphical explanation on why the decision of slicer A should be kept while that of slicer B should be discarded. (ii) Case 2 (data=1) : In path A, since  $v_A$  decreases and data=1, the decision of slicer A is discarded. In Path B, since  $v_B$  increases and data=1, the decision of slicer B is selected. The preceding analysis shows that in order to detect  $0\rightarrow 1$  transitions,  $A_2 \oplus B_1$  should be used. Similarly, to detect  $1\rightarrow 0$  transitions,  $A_1 \oplus B_2$  should be used. We therefore have  $s_n = A_2 \oplus B_1 + A_1 \oplus B_2$ . The pull-down NMOS transistor gated by  $\overline{A_1 + A_2 + \overline{B_1} + \overline{B_2}}$  is needed to discard data transition indication when there is a definitive data sampling er-

Figure 2.4: Data transition signal  $s_n$ . If data=0, since the tap increases  $v_A$

in path A and decreases  $v_B$  in path B, the output of slicer A is selected while that of slicer B is discarded. If data=1, since the tap decreases  $v_A$  in path A and increases  $v_B$  in path B, the output of slicer A is discarded while that of slicer B is selected.

ror. The generation of  $s_n$  during CLK=0 allows the multiplexing operations of loop-unrolling to be performed during CLK=1.

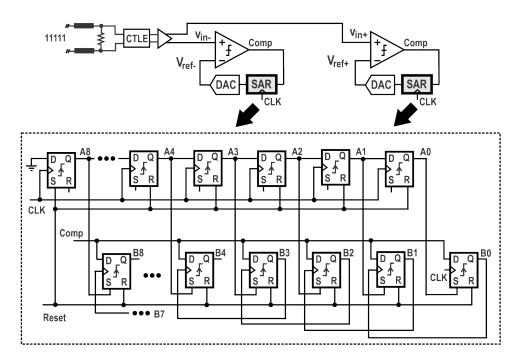

### 2.2.3 Max/Min Vertical Eye-Openings

When consecutive 1s or 0s are encountered, DT-DFE disables DFE to retain obtained vertical eye-opening, revealing that the maximum and minimum vertical eye-opening can be obtained by conveying a train of 1s and 0s to the channel and measuring the corresponding output voltage of the CTLE. Since for a given channel, the maximum and minimum voltages of the output of the CTLE are constant in this case, they can be obtained using SAR ADCs with  $V_{max}$  and  $V_{min}$  the output voltage of the digital-to-time converter (DAC) of the ADCs. Once  $V_{max}$  and  $V_{min}$  are obtained, the SAR ADCs are disabled thereby retaining the content of the SARs. In this work, two 8-bit chargeredistribution SAR ADCs with redundant SARs are used to find  $V_{max}$  and  $V_{min}$  in a 11 cycle training phase preceding DFE. Although redundant SARs are used [35], one can also use a non-redundant SAR to lower cost [36].

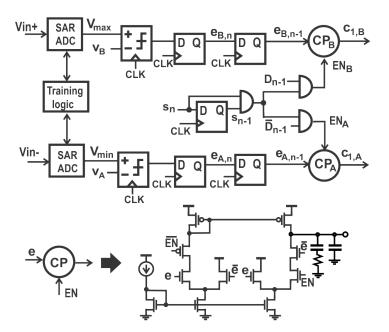

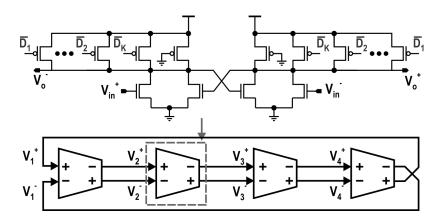

### 2.2.4 Sign<sup>3</sup>-LMS

Considering single tap for simplicity, conventional DS-DFE uses the sign<sup>2</sup>-LMS algorithm given in (2.4) to search for the optimal tap

$$c_{1,n} = c_{1,n-1} + h \operatorname{sgn}[e_n] \operatorname{sgn}[D_{n-1}], \qquad (2.4)$$

where h is the step size used to adjust  $c_1$ , e is the error between the desired and equalized data,  $s_n$  is data transition,  $D_{n-1}$  is the past decision of the slicer, and n indicates nth iteration cycle. To eliminate the intrinsic drawback of DS-DFE detailed earlier, the proposed DT-DFE uses the sign<sup>3</sup>-LMS algorithm given in (2.5) to tune the tap

$$c_{1,n+1} = c_{1,n} + h \operatorname{sgn}[e_n] \operatorname{sgn}[D_{n-1}] \operatorname{sgn}[s_n s_{n-1}].$$

(2.5)

Figure 2.5: DT-DFE with sign<sup>3</sup>-LMS. The output of the charge pumps is fed to a loop filter to smooth tap tuning.

The difference between the tap adaptation of DT-DFE and DS-DFE is the addition of  $sign[s_n s_{n-1}]$ . The tap is updated only when two consecutive state

transitions of opposite polarities are detected. Fig. 2.5 shows the simplified schematic of the adaptation scheme of DT-DFE. Equalized data in paths A and B are compared with  $V_{min}$  and  $V_{max}$ , respectively. As the output voltage of the slicers is not full swing, DFFs are employed at the output of the slicers to restore voltage swing. In order to synchronize with  $s_n s_{n-1}$ , additional DFFs are used to generate  $e_{A,n-1}$  and  $e_{B,n-1}$ . The signals that activate the charge pumps are given by  $\text{En}_A = s_n s_{n-1} \overline{D}_{n-1}$  and  $\text{En}_B = s_n s_{n-1} D_{n-1}$ . The charge pumps are activated only when two consecutive data transitions of opposite polarities are encountered, i.e.  $s_n s_{n-1}=1$ . The sign of  $D_{n-1}$ determines either tap  $c_{1,A}$  or  $c_{1,B}$  needs to be updated. The direction of the tuning of the charge pumps is set by the polarity of the error signal.

### 2.2.5 Tap Addition/Subtraction

The simplified schematic of the tap generator that performs the addition /subtraction of the tap to/from the output of the CTLE is shown in Fig. 2.6. Since both CTLE and slicer are differential, the tap generator is also differentially configured. It is seen that the tap generator is activated only when  $s_n = 1$ . Further when  $D_{n-1} = 1$ , C+ will be charged by the head current while C- will be discharged by the tail current, resulting in a smaller equalized signal  $v_e = v_e^+ - v_c^-$ . This is equivalent to subtracting the tap from the incoming data. Similarly when  $D_{n-1} = 0$ ,  $v_e$  will increase.

# 2.3 Discussions

### 2.3.1 Tap Tuning

The tap will be tuned when two consecutive data transitions of opposite polarities occur e.g.  $s_n s_{n-1} = 1$ . DFE operation e.g. the addition/subtraction of the tap to/from the output of CTLE will be performed when a data transition is detected e.g.  $s_n = 1$ . Since data with two consecutive transitions contain more high-frequency components compared with those with single

Figure 2.6: Tap addition/subtraction.

data transitions, tap adjustment that is dictated by the high-frequency components of data allows the tap to be optimized to better accommodate the more stringent equalization constraints of the high-frequency components of data so as to get better eye-opening. Since the tap is optimized for the high-frequency components of data, it exceeds the necessary strength for dealing with the low-frequency components of data. As a result, the channel is equalized for the high-frequency components of data but attenuated for the low-frequency components of data.

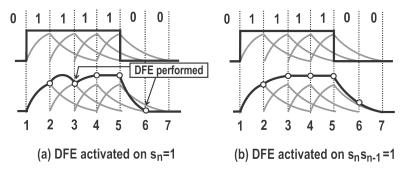

### 2.3.2 DFE Activation

Two options to determine when to activate DFE are available : Activate DFE when a single data transition is detected or when two consecutive data transitions of opposite polarities are present. Let us examine them in detail : (i) Option 1 (Active DFE on a data transition) : Consider the data sequence in Fig. 2.7(a). One post-cursor needs to be removed. At t=2,  $0\rightarrow 1$  transition at t=1 has been detected and DFE is activated at t=3. It removes the post-cursor at t=3. Similarly, at t=6,  $0\rightarrow 1$  transition at t=5 has been detected and DFE is activated at t=6. DFE operation

performed at t=3 lowers vertical eye-opening while that performed at t=6 sharpens the falling edge of the eye, improving data jitter. (ii) Option 2 (DFE is activated on two consecutive data transitions of opposite polarities) : Consider the same data sequence shown in Fig. 2.7(b). Since two consecutive data transitions of opposite polarities do not exist, no DFE is performed. As a result, the vertical eye-opening is larger as compared with that of Option 1 but the falling edge has a smaller slope, worsening data jitter. It is evident that both options have their pros and cons. In this work, option 1 is used.

Figure 2.7: DFE activation schemes.

### 2.3.3 DS-DFE versus DT-DFE

In this section, we analyze the intrinsic differences between DS-DFE and DT-DFE. Let x(t) be the output of the CTLE. The equalized data of DS-DFE and that of DT-DFE in *n*th cycle, denoted by  $y_{DS,n}$  and  $y_{DT,n}$ , respectively, are given by

$$y_{DS,n} = x_n - c_1 D_{n-1}, (2.6a)$$

$$y_{DT,n} = x_n - c_1 D_{n-1} s_n, (2.6b)$$

where  $0 < c_1 < 1$  is the tap. It is seen from (2.6a) that when consecutive 1s are present in data, DS-DFE will successively subtract the tap from data even though no DFE is preferred as ISI in this case actually increases rather than reduces vertical eye-opening. Similarly, when consecutive 0s

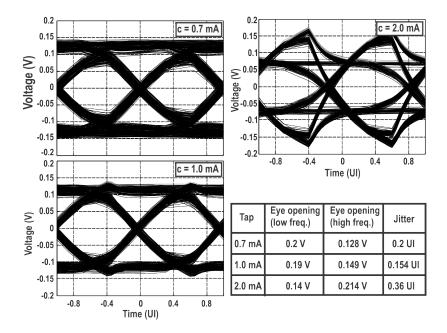

Figure 2.8: Simulated eye diagram equalized using DS-DFE with one tap. The strength of the tap : 0.7 mA, 1.0 mA, and 2.0 mA . Data rate : 5 Gbps. Channel characteristics : Depicted in Fig. 1.5.

are present, DS-DFE will successively add the tap to data even though no DFE is also preferred in this case as well. Therefore, DS-DFE increases the vertical eye-opening of the high-frequency components of data at the expense of the reduced vertical eye-opening of the low-frequency components of data . Increasing tap strength, though improving the vertical eye-opening of the high-frequency components of data, lowers the vertical eye-opening of the low-frequency components of data, as evidenced in Fig. 2.8. The vertical eye-opening that DS-DFE can achieve is upper-bounded by the low-frequency component rather than the high-frequency components of data as the tap strength increases. Although modulation is typically performed on data prior to their transmission to allow modulated data to possess a DC-balanced characteristic critical so as to prevent the drift of the DC operating point of the CTLE, consecutive 1s and 0s still exist in data and the vertical eye-opening of equalized data is data-dependent. As a result, the reference

voltages of DS-DFE are data-dependent, unknown a priori, and can only be obtained using a DFE-like algorithm [30].

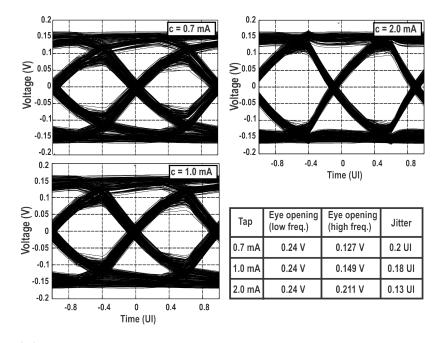

Figure 2.9: Simulated eye diagram equalized using DT-DFE with one constant tap. The strength of the tap : 0.7 mA, 1.0 mA, and 2.0 mA . Data rate : 5 Gbps. Channel characteristics : Depicted in Fig. 1.5.