### MODELLING, SIMULATION, CONTROL, AND ENHANCED TOPOLOGIES FOR THE MODULAR MULTILEVEL CONVERTER FOR HIGH-VOLTAGE DC (HVDC) APPLICATIONS

by

Rafael Oliveira

Master of Science, PUCRS, 2005

Bachelor of Engineering, PUCRS, 2003

A dissertation

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

in the Program of

Electrical and Computer Engineering Ryerson University Toronto, Ontario, Canada

© Rafael Oliveira 2016

### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A DISSERTATION

I hereby declare that I am the sole author of this dissertation. This is a true copy of the dissertation, including any required final revisions, as accepted by my examiners. I authorize Ryerson University to lend this dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the public.

#### Modelling, Simulation, Control, and Enhanced Topologies for the Modular Multilevel Converter for High-Voltage DC (HVDC) Applications

2016

**Rafael Oliveira**

**Doctor of Philosophy**

#### **Electrical and Computer Engineering**

**Ryerson University**

### Abstract

This thesis is focused on the modular multilevel converter (MMC) for High-Voltage DC (HVDC) systems. It is an attempt to address the issues associated with the modelling, simulation, control, efficiency, and fault-handling capability of the MMC. Thus, to address the modelling of the MMC, a new and more accurate steady-state harmonic model is proposed. The proposed harmonic model is capable of predicting the amplitude of the harmonic components of the MMC arm voltages, submodule capacitor voltages, and arm currents. Further, based on the proposed harmonic model, a capacitor sizing method is proposed to determine the capacitance of the submodule capacitor for a desired level of voltage variation, without a need for numerical algorithms or graphs used by the existing methods. In addition, the proposed capacitor sizing method can accurately determine the required capacitance even if circulating currents are injected to mitigate dc voltage fluctuations. The thesis also proposes a simple equivalent-circuit-based simulation model for MMC-based HVDC systems, which assumes ideal submodule switches to speed up the simulation, but is nonetheless capable of capturing the transients as well as harmonic components of the voltages and currents. Further, the thesis proposes a simple compensation strategy that calculates the magnitude of the second harmonic component of an arm voltage, and uses the calculated value as a feedforward signal to cancel the circulating current of the corresponding MMC leg. The proposed feedforward compensation strategy, if combined with a closed-loop circulating current suppression strategy, greatly mitigates the possibility of control saturation and, also, results in better damped closed-loop dynamics. Finally, the thesis proposes two new MMC topologies for enhanced efficiency and dc-side fault handling capability. In the first proposed topology, that is the lattice modular multilevel converter (LMMC), the entire MMC arm is modified to accommodate *networks* that allow shortcuts between the arm capacitors, thus, reducing conduction power losses of the converter. In the second topology proposed, however, only the submodule is modified. In the proposed submodule topology, referred to as *lattice submodule* (LSM), the conduction power losses are decreased, as it is the case for the LMMC, with the difference that the voltage stress in the switches are also reduced.

**Keywords:** Control, lattice modular multilevel converter, lattice submodule, modelling, modular multilevel converter, simulation model.

### Acknowledgements

I would like to express my gratitude to Dr. Amirnaser Yazdani for his excellent supervision during the course of my research. I enjoyed our conversations and learned a lot from him. He passed not only his technical knowledge, but also friendship.

I would also like to thank my wife Juliana, for being by my side throughout this research and the entire immigration process. It was not easy to ride through the hardships during the past years, but her strength and love helped us overcome the difficulties as a family.

Finally, I wish to thank my parents, Cicero and Maria Elisabeth, and my Grandma Josina, for all the support they have given in my whole life, even from thousands of kilometers away. For them, to stop studying was never an option.

# Contents

| Αι | uthor   | 's Decla | iration                                                  | ii   |

|----|---------|----------|----------------------------------------------------------|------|

| AJ | bstrac  | et       |                                                          | iii  |

| A  | cknov   | vledgen  | nents                                                    | iv   |

| Li | st of ] | Figures  |                                                          | ix   |

| Li | st of ' | Tables   |                                                          | xiv  |

| Li | st of A | Abbrev   | iations                                                  | XV   |

| 1  | Intr    | oductio  | n                                                        | 1    |

|    | 1.1     | Backg    | round and Motivation                                     | . 1  |

|    | 1.2     | Staten   | nent of Problem and Thesis Objectives                    | . 7  |

|    | 1.3     | Literat  | ture Survey Pertinent to the Thesis Objectives           | . 8  |

|    |         | 1.3.1    | Modelling of the MMC and component sizing                |      |

|    |         | 1.3.2    | Control of the MMC                                       |      |

|    |         | 1.3.3    | Simulation of the MMC                                    | . 11 |

|    |         | 1.3.4    | Topologies and their dc-side fault handling capabilities | . 12 |

|    | 1.4     | Thesis   | Outline                                                  | . 13 |

| 2  | Dev     | elopme   | nt of the Steady-State Harmonic Model of the MMC         | 15   |

|    | 2.1     | Found    | lation and assumptions regarding the MMC model           | . 15 |

|    | 2.2     | Model    | lling of the MMC                                         | 16   |

|    |         | 2.2.1    | Fundamental harmonic MMC model                           |      |

|    |         | 2.2.2    | Open-loop MMC model                                      | 21   |

|    | 2.3     | Propos   | sed steady-state harmonic model of the MMC               |      |

|    |         | 2.3.1    | Circulating current amplitude calculation                |      |

|    |         | 2.3.2    | Capacitor voltage harmonic components calculation        | . 33 |

|    |         | 2.3.3    | Arm voltage harmonic components calculation              | 35   |

|    |         | 2.3.4    | Modulating function calculation                          | . 37 |

|    |         |          | Polynomial roots calculation using Newton-Raphson        | 40   |

|    | 2.4     | MMC      | component sizing                                         |      |

|    |         | 2.4.1    | Proposed submodule capacitor sizing method               |      |

|    |         |          | Capacitor Sizing Method for Injected Circulating Current |      |

|    |         | 2.4.2    | Arm inductor sizing based on leg current resonance       | . 49 |

|   | 2.5 | Valida        | tion of the harmonic steady-state model                                                                               | 49       |

|---|-----|---------------|-----------------------------------------------------------------------------------------------------------------------|----------|

|   |     | 2.5.1         | Submodule capacitor voltage variation                                                                                 |          |

|   |     | 2.5.2         | Modulation index                                                                                                      | 53       |

|   |     | 2.5.3         | Circulating current, submodule capacitor voltage, and Arm voltage                                                     | 53       |

|   |     | 2.5.4         | Circulating current series convergence (resonance)                                                                    |          |

|   | 2.6 | Valida        | tion of the capacitor sizing method                                                                                   | 55       |

|   | 2.7 |               | ary and Conclusions                                                                                                   |          |

| 3 | Dev | elopme        | nt of a Simulation Model of the MMC                                                                                   | 58       |

|   | 3.1 | -             | ified Equivalent-Circuit Simulation Model                                                                             |          |

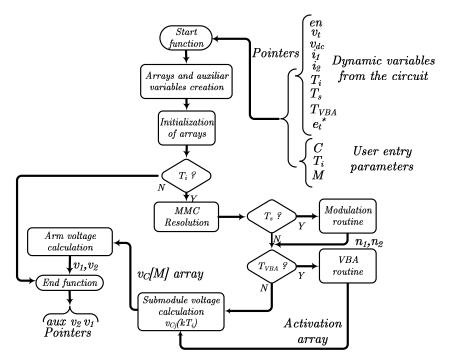

|   | 3.2 | -             | um code for the simplified equivalent-circuit simulation model                                                        |          |

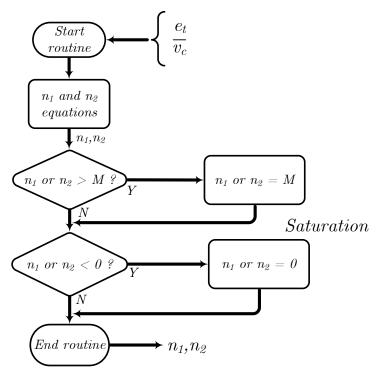

|   |     | 3.2.1         | Modulation routine                                                                                                    |          |

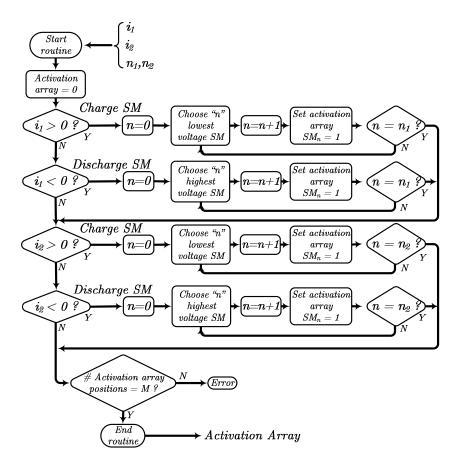

|   |     | 3.2.2         | Voltage balancing algorithm (VBA) routine                                                                             |          |

|   |     | 3.2.3         | Submodule capacitor voltage calculation routine                                                                       |          |

|   |     | 5.2.5         | Capacitor voltage calculation for enabled submodules                                                                  |          |

|   |     |               | Capacitor voltage calculation for disabled submodules                                                                 | 63       |

|   |     | 3.2.4         | Arm voltage calculation routine                                                                                       | 63       |

|   |     | 3.2.7         | Arm voltage calculation for enabled submodules                                                                        | 63       |

|   |     |               | Arm voltage calculation for disabled submodules                                                                       | 64       |

|   | 3.3 | Valida        | tion of the simplified equivalent-circuit simulation model                                                            | 64       |

|   | 5.5 | 3.3.1         | Case I - FBSM-based single-phase MMC inverter for $M = 4$                                                             | 65       |

|   |     | 5.5.1         | Submodule capacitor pre-charge                                                                                        | 66       |

|   |     |               | Simulation of a dc-side fault situation                                                                               | 67       |

|   |     | 3.3.2         | Case II - FBSM-based single-phase MMC rectifier for $M = 4$                                                           | 69       |

|   |     | 5.5.2         | SM capacitor pre-charge $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                | 69       |

|   |     |               | Simulation of a dc-side fault situation                                                                               | 70       |

|   |     | 3.3.3         | Case III - FBSM-based three-phase MMC inverter for $M = 8$                                                            | 70       |

|   |     | 3.3.4         | Case IV - FBSM-based back-to-back three-phase MMC system for                                                          | /1       |

|   |     | 5.5.4         | $M = 400 \dots \dots$ | 72       |

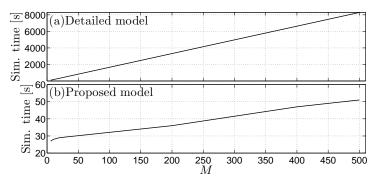

|   |     | 3.3.5         | M = 400                                                                                                               | 72<br>74 |

|   | 3.4 |               |                                                                                                                       |          |

|   | 3.4 | Summ          | ary and Conclusions                                                                                                   | 13       |

| 4 |     | -             | nt of an Enhanced Control Strategy of the MMC                                                                         | 76       |

|   | 4.1 |               | le terminal current compensator strategies                                                                            | 76       |

|   |     | 4.1.1         | PI compensator in $dq$ -frame                                                                                         | 77       |

|   | 4.2 |               | ating current compensator                                                                                             |          |

|   |     | 4.2.1         | Circulating current suppressing compensator in $dq$ -frame                                                            | 81       |

|   |     | 4.2.2         | Resonant compensator                                                                                                  | 82       |

|   | 4.3 | -             | sed feedforward control strategy for circulating current suppressing                                                  |          |

|   | 4.4 |               | prward control strategy validation                                                                                    | 87       |

|   |     | 4.4.1         | Case I - Back-to-back HVDC system with <i>dq</i> -frame PI and feedforward control                                    | 88       |

|   |     | 4.4.2         | Case II - Back-to-back HVDC system with resonant and feedforward                                                      | 00       |

|   |     | <b>⊣.1</b> .∠ | control                                                                                                               | 89       |

|   |     | 4.4.3         | Case III - Back-to-back HVDC system with feedforward control only .                                                   | 91       |

|   | 4.5  | Summa    | ary and Conclusions                                                                       |

|---|------|----------|-------------------------------------------------------------------------------------------|

| 5 | Latt | ice Mod  | Iular Multilevel Converter94                                                              |

|   | 5.1  | Propos   | ed MMC: The LMMC                                                                          |

|   | 5.2  | Princip  | bles of Operation of the LMMC                                                             |

|   |      | 5.2.1    | Normal operation                                                                          |

|   |      | 5.2.2    | Operation under a dc-side fault                                                           |

|   | 5.3  | Switch   | ing Scheme of the LMMC                                                                    |

|   |      | 5.3.1    | Capacitor connected to <i>positive half-bridge</i> : $j = 1$ corresponding to $C_1$ . 101 |

|   |      | 5.3.2    | First Capacitor and Intermediate Capacitors: $1 \le j \le (M - 3)$ corre-                 |

|   |      |          | sponding to $C_1, C_2,, C_{(M-3)}$                                                        |

|   |      | 5.3.3    | Capacitor connected to the last <i>high-efficiency link</i> : $j = (M - 2)$ corre-        |

|   |      |          | sponding to $C_{(M-2)}$                                                                   |

|   |      | 5.3.4    | Capacitor before the last: $j = (M - 1)$ corresponding to $C_{(M-1)}$ 102                 |

|   |      | 5.3.5    | Capacitor connected to <i>negative half-bridge</i> : $j = M$ corresponding to $C_M 102$   |

|   | 5.4  | -        | rrison with the conventional MMC                                                          |

|   |      | 5.4.1    | Comparison between LMMC and MMC building blocks 105                                       |

|   |      | 5.4.2    | Comparison between LMMC and MMC interconnections 106                                      |

|   | 5.5  | •        | is of power losses                                                                        |

|   |      | 5.5.1    | Number of series-connected switches in an arm                                             |

|   |      | 5.5.2    | Power losses                                                                              |

|   | 5.6  | •        | is of Voltage Stress                                                                      |

|   |      | 5.6.1    | Switch $S_{u1}$                                                                           |

|   |      | 5.6.2    | Switch $S_{c1}$                                                                           |

|   |      | 5.6.3    | Switch $S_{d1}$                                                                           |

|   | 5.7  |          | tion results for the LMMC                                                                 |

|   |      | 5.7.1    | Case I - Single-phase LMMC inverter for $M = 4$                                           |

|   |      | 5.7.2    | Case II - Single-phase LMMC inverter for $M = 9$                                          |

|   |      | 5.7.3    | Case III - Three-phase LMMC inverter for $M = 8$                                          |

|   | - 0  | 5.7.4    | Validation of the model for power losses                                                  |

|   | 5.8  | Summa    | ary and Conclusions                                                                       |

| 6 | Latt | ice Subi | module 118                                                                                |

|   | 6.1  | Propos   | ed submodule topology: The LSM                                                            |

|   | 6.2  | Princip  | bles of Operation of the LSM                                                              |

|   |      | 6.2.1    | Normal operation                                                                          |

|   |      | 6.2.2    | Operation under a dc-side fault                                                           |

|   | 6.3  | Switch   | ing Scheme of the LSM                                                                     |

|   | 6.4  | Power    | loss analysis                                                                             |

|   | 6.5  |          | e stress analysis                                                                         |

|   | 6.6  | Advant   | tages of the proposed topology                                                            |

|   | 6.7  |          | tion results for the LSM                                                                  |

|   |      | 6.7.1    | Case I - Single-phase LSM inverter for $M = 4$                                            |

|   |      | 6.7.2    | Case II - Three-phase LSM inverter for $M = 8 \dots 128$                                  |

|   |      | 6.7.3    | Validation of the model for power losses                                                  |

|    | 6.8    | Summary and Conclusions                                               | 131 |

|----|--------|-----------------------------------------------------------------------|-----|

| 7  | Con    | clusions, Contributions, and Future Work                              | 133 |

|    | 7.1    | Conclusions                                                           | 133 |

|    | 7.2    | Contributions                                                         | 134 |

|    | 7.3    | Future Work                                                           | 135 |

| A  | Exa    | mple of program code for the SEC Simulation Model                     | 136 |

|    | A.1    | Function calling and variables initialization                         | 136 |

|    | A.2    | Modulation routine - controlled by $T_s$                              | 138 |

|    | A.3    | VBA routine - controlled by $T_{VBA}$                                 | 138 |

|    | A.4    | Submodule Capacitor Voltage Calculation Routine - controlled by $T_i$ | 140 |

|    | A.5    | Arm Voltage Calculation Routine                                       | 142 |

| Bi | bliogi | raphy                                                                 | 136 |

# **List of Figures**

| 1.1  | Critical distance when HVDC transmission becomes more cost effective in re-<br>lation to HVAC.                                                                                                                                              | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Illustration of the location of the first HVDC transmission system, Gotland, Sweden [3].                                                                                                                                                    | 2  |

| 1.3  | Schematic diagram of the VSC-based HVDC transmission system in Gotland,<br>Sweden [11].                                                                                                                                                     | 3  |

| 1.4  | Conceptual schematic diagram for one leg of an MMC.                                                                                                                                                                                         | 5  |

| 1.5  | AC-side terminal voltage and its fundamental component for an MMC with 50 voltage sources per arm.                                                                                                                                          | 5  |

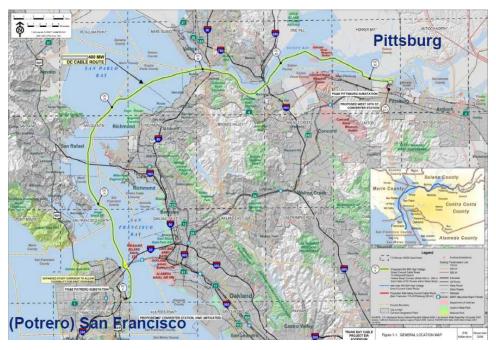

| 1.6  | Transbay HVDC transmission system, connecting Pittsburgh, CA to San Fran-<br>cisco, CA [17].                                                                                                                                                | 6  |

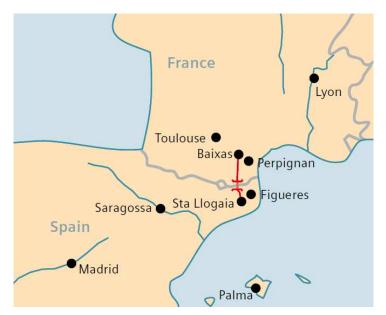

| 1.7  | Location of the Inelfe HVDC transmission system, connecting Sta Llogaia,<br>Spain to Baixas, France [21].                                                                                                                                   | 6  |

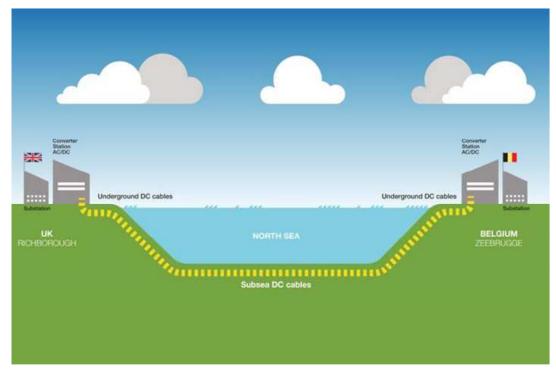

| 1.8  | Illustration of the Nemo HVDC transmission system, connecting Richborough,<br>UK to Zeebrugge, Belgium [24].                                                                                                                                | 7  |

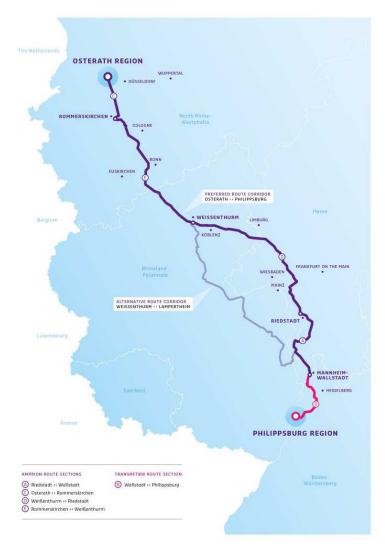

| 1.9  | Future site of the Ultranet HVDC transmission system, connecting Osterath to Philippsburg, Germany [25].                                                                                                                                    | 8  |

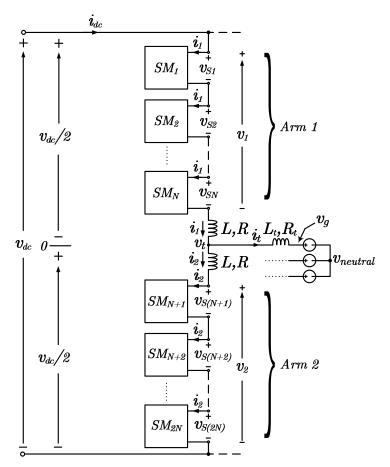

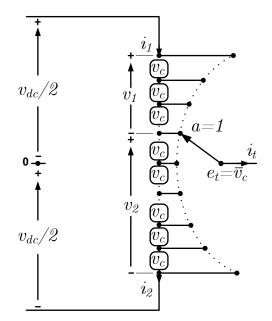

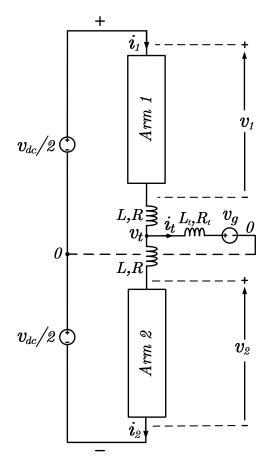

| 2.1  | Schematic diagram for one leg of a three-phase MMC.                                                                                                                                                                                         | 17 |

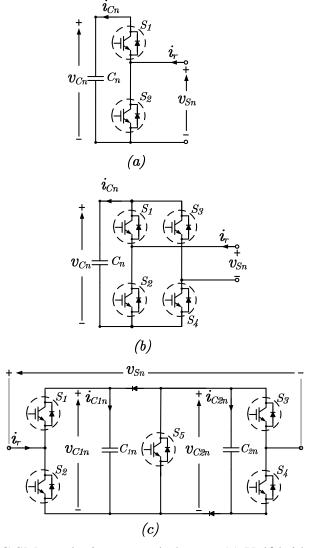

| 2.2  | Main MMC SM topologies currently known:(a) Half-bridge submodule - HBSM;                                                                                                                                                                    |    |

|      | (b) Clamp-doubled submodule - CDSM; (c) Full-bridge submodule - FBSM                                                                                                                                                                        | 18 |

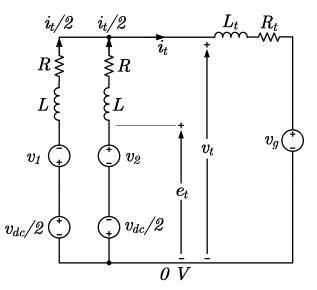

| 2.3  | MMC equivalent circuit from the point of view of the ac grid                                                                                                                                                                                | 19 |

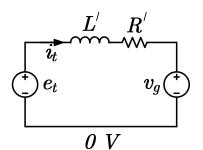

| 2.4  | Simplified MMC equivalent circuit from the point of view of the ac grid                                                                                                                                                                     | 19 |

| 2.5  | Asymmetry dynamic example for $a = 1$                                                                                                                                                                                                       | 20 |

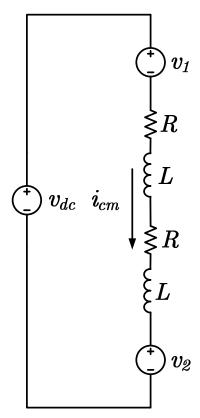

| 2.6  | Simplified MMC equivalent circuit from the point of view of the dc grid                                                                                                                                                                     | 23 |

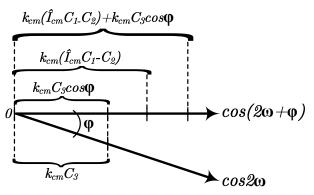

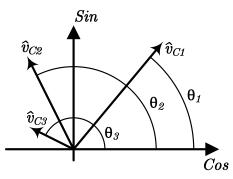

| 2.7  | Grouping of the terms in (2.86) in the same axis                                                                                                                                                                                            | 32 |

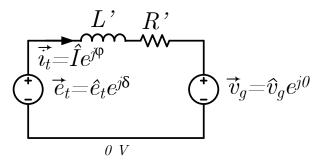

| 2.8  | Simplified circuit representing the inner voltage phasor $\vec{e}_t$                                                                                                                                                                        | 38 |

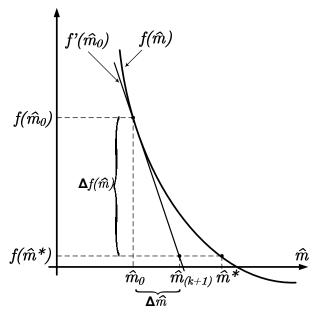

| 2.9  | Newton-Raphson method illustration, first iteration.                                                                                                                                                                                        | 41 |

| 2.10 | Newton-Raphson method illustration.                                                                                                                                                                                                         | 42 |

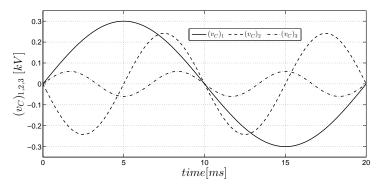

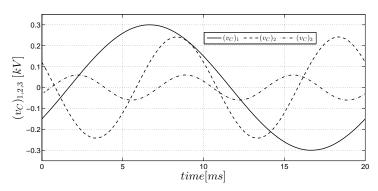

| 2.11 | First, second, and third harmonic components in the submodule capacitor voltage for $\varphi = 0$ .                                                                                                                                         | 42 |

| 2.12 | First, second, and third harmonic components in the submodule capacitor volt-<br>age for $\varphi = -30$ degrees.                                                                                                                           | 43 |

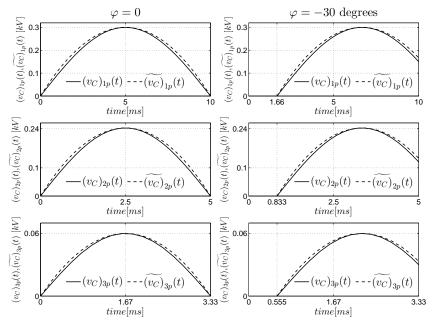

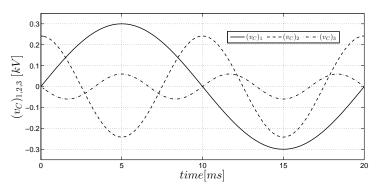

| 2.13 | Approximate quadratic functions $(\tilde{v}_C)_{1p}(t)$ , $(\tilde{v}_C)_{2p}(t)$ , and $(\tilde{v}_C)_{3p}(t)$ , in contrast with $(v_C)_{1p}(t)$ , $(v_C)_{2p}(t)$ , and $(v_C)_{3p}(t)$ , for $\varphi = 0$ and $\varphi = -30$ degrees. | 44 |

| 2.14       | Submodule capacitor voltage harmonic components representation in the trigono-                                                                                                                                                                   |    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | metric plane at $t = t_p$                                                                                                                                                                                                                        | 46 |

| 2.15       | First, second, and third harmonics in the submodule capacitor voltage, for $\varphi =$                                                                                                                                                           |    |

|            | 0, assuming an injected $i_{cm}$ .                                                                                                                                                                                                               | 48 |

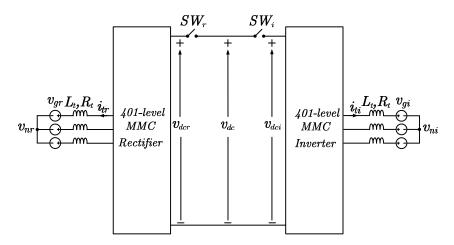

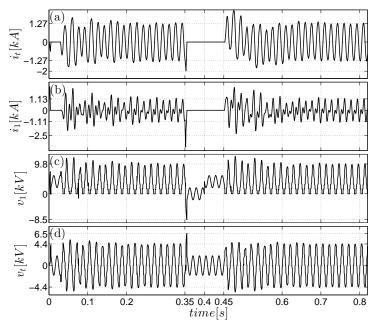

|            | Schematic diagram of the back-to-back MMC HVDC system simulated                                                                                                                                                                                  | 50 |

| 2.17       | Voltages and currents for the back-to-back system illustrated in Fig. 2.16 sub-                                                                                                                                                                  |    |

|            | mitted to different disturbances                                                                                                                                                                                                                 | 51 |

| 2.18       | Circulating current, submodule capacitor voltage, and ac-side terminal current for the back-to-back system illustrated in Fig. (2.16) submitted to different                                                                                     |    |

|            | disturbances                                                                                                                                                                                                                                     | 52 |

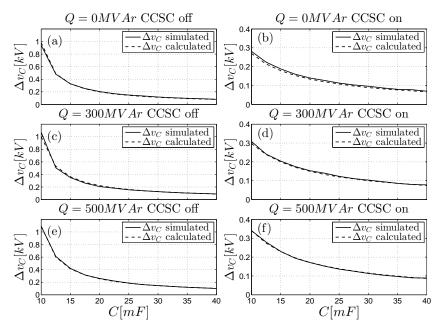

| 2.19       | Comparison between the proposed steady-state model and the simulation results for $\Delta v_C$ . (a) No reactive power and CCSC off; (b) No reactive power and CCSC on; (c) 300 <i>MVAr</i> reactive power and CCSC off; (d) 300 <i>MVAr</i> re- |    |

|            | active power and CCSC on; (e) 500MVAr reactive power and CCSC off; (f)                                                                                                                                                                           |    |

|            | 300 <i>MVAr</i> reactive power and CCSC on                                                                                                                                                                                                       | 52 |

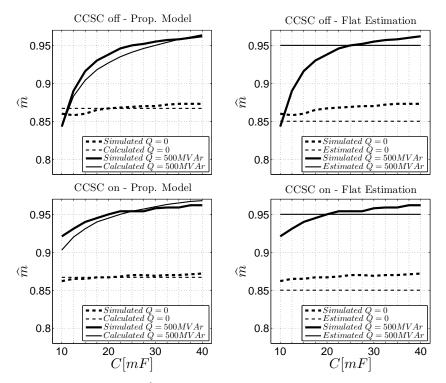

| 2.20       | Comparison between $\widehat{m}$ calculated by the proposed model and estimated by                                                                                                                                                               |    |

|            | (2.24).                                                                                                                                                                                                                                          | 53 |

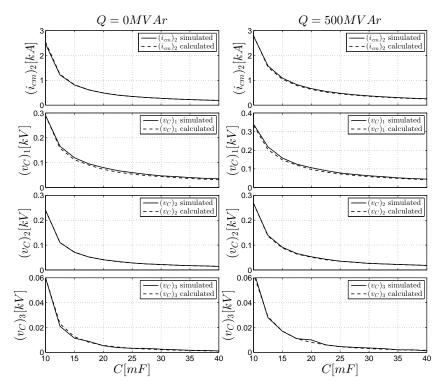

| 2.21       | Comparison between the proposed steady-state harmonic model and the simu-                                                                                                                                                                        |    |

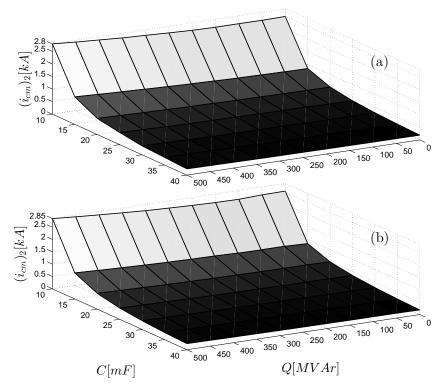

|            | lation results for $(i_{cm})_2$ , $(v_C)_1$ , $(v_C)_2$ and $(v_C)_3$ .                                                                                                                                                                          | 54 |

| 2.22       | Comparison between the simulation, (a), and the proposed steady-state har-                                                                                                                                                                       |    |

|            | monic model results, (b), for $(i_{cm})_2$ amplitude with Q changing from 0–500MVAr.                                                                                                                                                             | 55 |

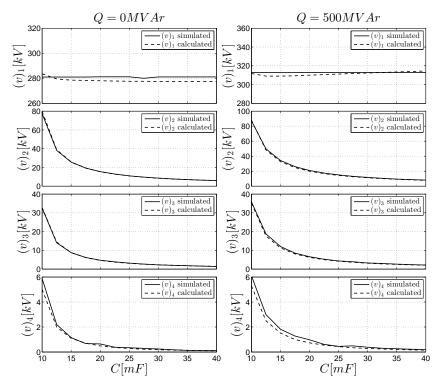

| 2.23       | Comparison between the proposed steady-state harmonic model and the simu-                                                                                                                                                                        |    |

|            | lation results for $(v)_1, (v)_2, (v)_3$ , and $(v)_4, \ldots, \ldots, \ldots, \ldots, \ldots$                                                                                                                                                   | 56 |

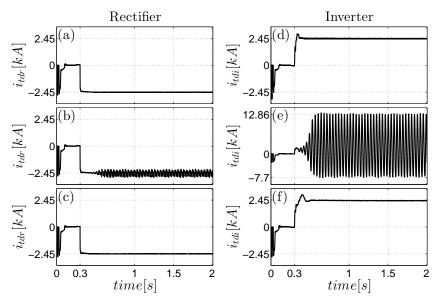

| 2.24       | d component of the ac-side terminal current, in the rectifier and the inverter, for                                                                                                                                                              |    |

|            | an arm inductance of $25 \ mH$ (a) and (d), $45 \ mH$ (b) and (e), and $50 \ mH$ (c) and                                                                                                                                                         |    |

|            | (f)                                                                                                                                                                                                                                              | 56 |

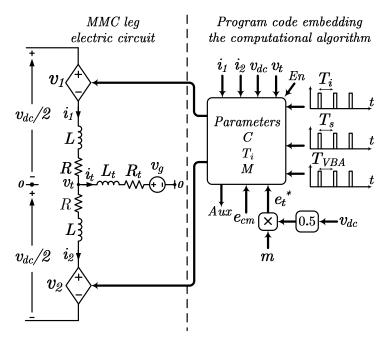

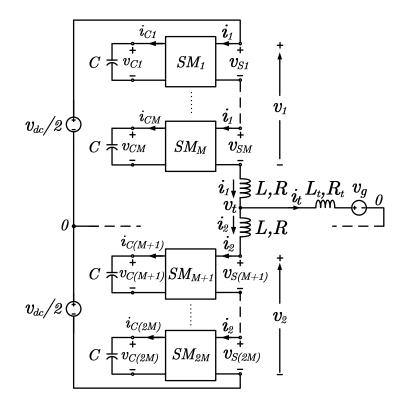

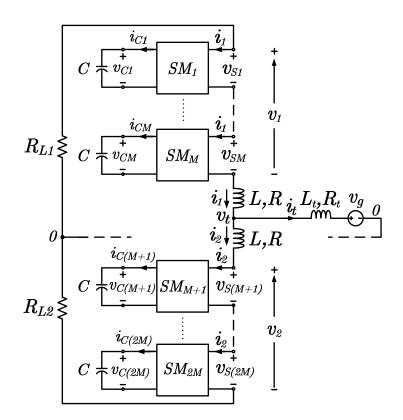

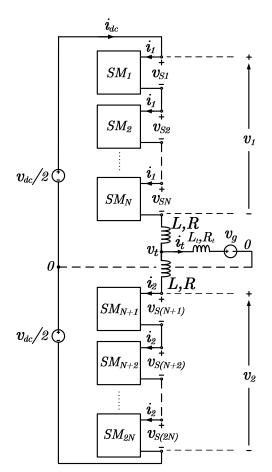

| 3.1        | Schematic diagram of the proposed SEC simulation model for one leg of an                                                                                                                                                                         |    |

| 5.1        | MMC.                                                                                                                                                                                                                                             | 59 |

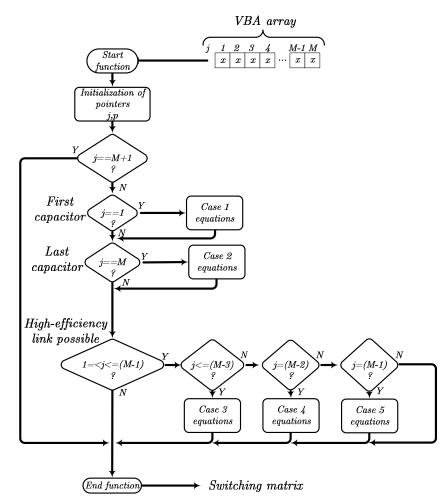

| 3.2        | Flowchart of the program code of the proposed simulation model.                                                                                                                                                                                  | 61 |

| 3.3        | Flowchart of the modulation routine.                                                                                                                                                                                                             | 61 |

| 3.4        | Flowchart of the VBA routine.                                                                                                                                                                                                                    | 62 |

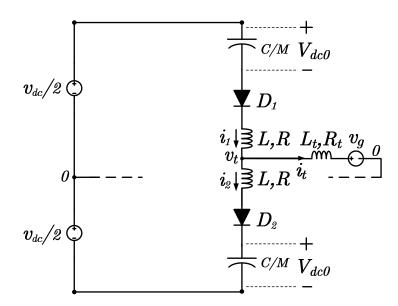

| 3.5        | Schematic diagram of a single-phase MMC inverter system.                                                                                                                                                                                         | 65 |

| 3.6        | Equivalent circuit for the MMC arm during pre-charge.                                                                                                                                                                                            | 66 |

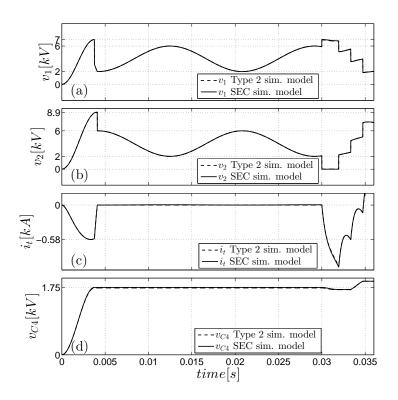

| 3.7        | Case I system during pre-charge. (a) Upper arm voltage. (b) Lower arm volt-                                                                                                                                                                      | 00 |

| 5.7        | age. (c) Ac-side terminal current. (d) Capacitor 4 voltage                                                                                                                                                                                       | 67 |

| 3.8        | Equivalent circuit for the MMC arm during a dc-side fault.                                                                                                                                                                                       | 68 |

| 3.8<br>3.9 | Case I system during a dc-side fault. (a) Upper arm voltage. (b) Lower arm                                                                                                                                                                       | 08 |

| 5.9        | voltage. (c) Ac-side terminal current. (d) Dc-side voltage                                                                                                                                                                                       | 68 |

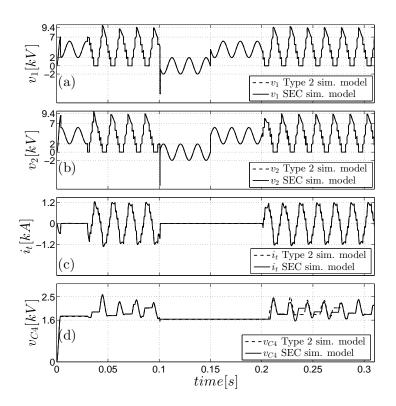

| 3.10       | Case I system full simulated range. (a) Upper arm voltage. (b) Lower arm                                                                                                                                                                         |    |

|            | voltage. (c) Ac-side terminal current. (d) Capacitor 4 voltage                                                                                                                                                                                   | 69 |

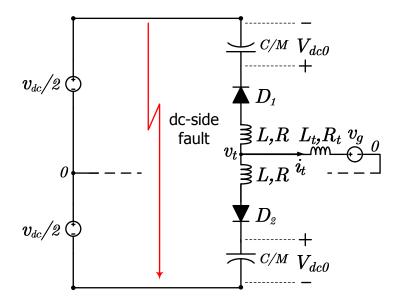

| 3.11       | Schematic diagram of a single-phase MMC rectifier system.                                                                                                                                                                                        | 70 |

|            | Case II system during pre-charge. (a) Upper arm voltage. (b) Lower arm volt-                                                                                                                                                                     |    |

|            | age. (c) Ac-side terminal current. (d) Dc-side voltage                                                                                                                                                                                           | 71 |

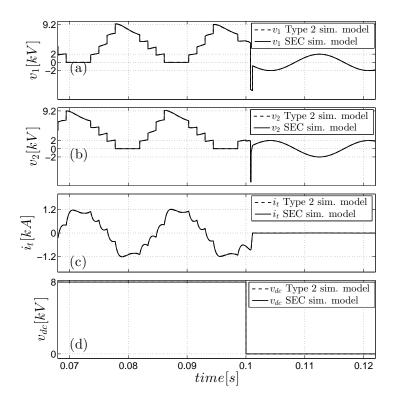

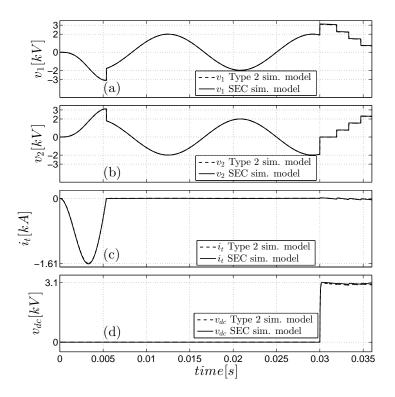

| 3.13          | Case II system during a dc-side fault. (a) Upper arm voltage. (b) Lower arm voltage. (c) Ac-side terminal current. (d) Dc-side voltage                  | 72       |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.14          | Waveforms of selected variables in a closed-loop controlled three-phase 9-level                                                                         | 70       |

| 3 1 5         | MMC, to various disturbances; Case III                                                                                                                  | 73       |

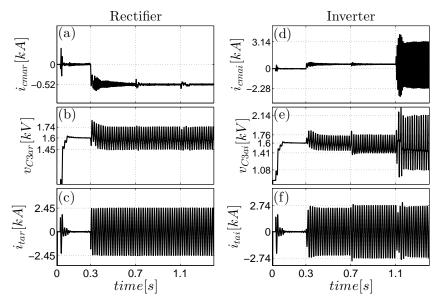

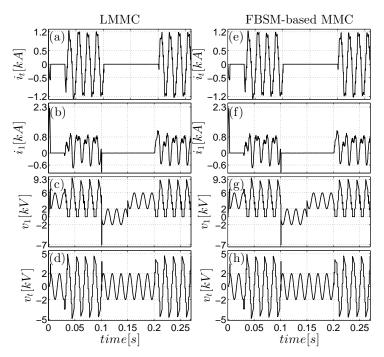

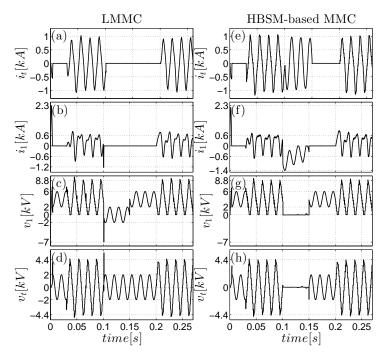

| 5.15          | MMC (right column); Case IV.                                                                                                                            | 74       |

| 3.16          | Simulation runtime versus number of SMs per arm                                                                                                         | 75       |

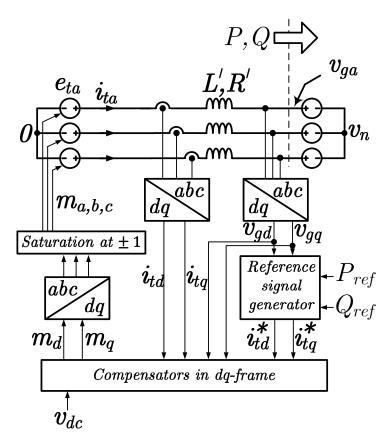

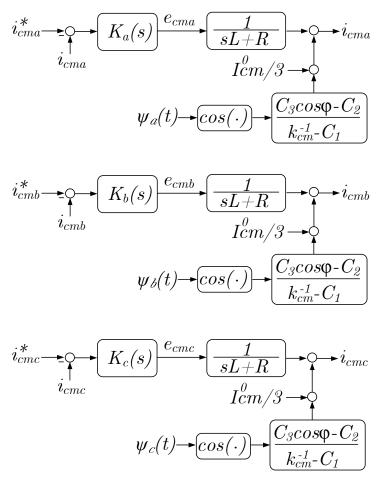

| 4.1           | Block diagram for $i_{ta}$ , $i_{tb}$ , and $i_{tc}$ .                                                                                                  | 77       |

| 4.2           | Schematic diagram of the ac-side terminal current compensator.                                                                                          | 78       |

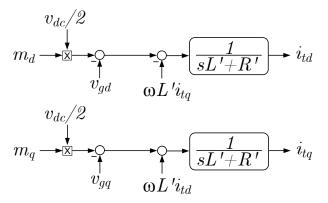

| 4.3           | Block diagram for $i_{td}$ , and $i_{tq}$ .                                                                                                             | 79<br>70 |

| 4.4           | Complete block diagram of the ac-side terminal current control in $dq$ -frame                                                                           | 79       |

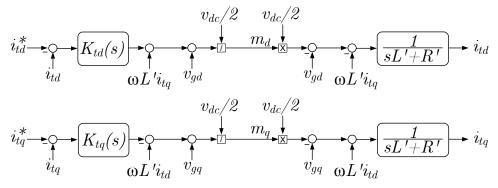

| 4.5<br>4.6    | Simplified block diagram for the ac-side terminal current control in $dq$ -frame.                                                                       | 80<br>81 |

| 4.0<br>4.7    | Block diagram for $i_{cm}$ in phase $a$                                                                                                                 | 01       |

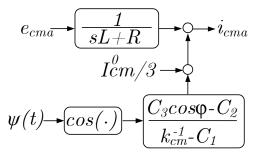

| 4.7           | as a disturbance. $\ldots$                                             | 81       |

| 4.8           | Block diagram for $i_{cm}$ control loop.                                                                                                                | 82       |

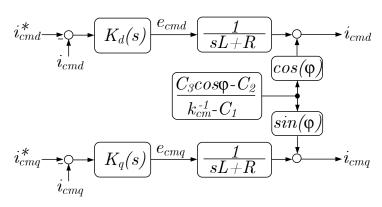

| 4.9           | Block diagram for $i_{cm}$ three-phase control loop.                                                                                                    | 83       |

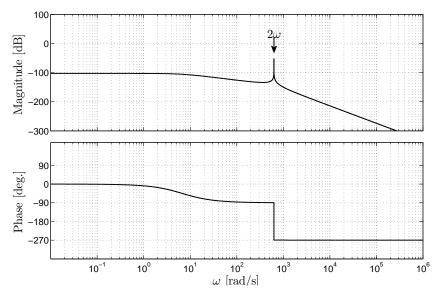

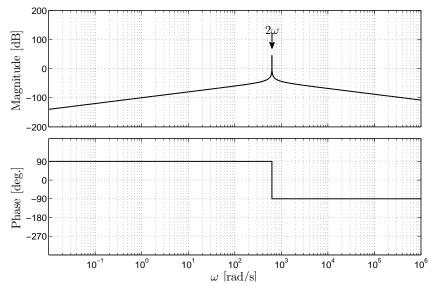

| 4.10          | Bode diagram for the open-loop transfer function $\ell(s)$ without cancellation of                                                                      |          |

|               | the low frequency MMC leg pole.                                                                                                                         | 84       |

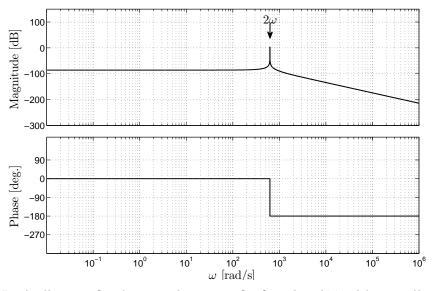

| 4.11          | Bode diagram for the open-loop transfer function $\ell(s)$ with cancellation of the                                                                     |          |

|               | low frequency MMC leg pole.                                                                                                                             | 84       |

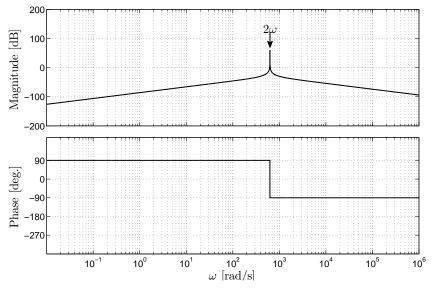

| 4.12          | Bode diagram for the open-loop transfer function $\ell(s)$ with pole cancellation                                                                       |          |

|               | and a zero at the origin.                                                                                                                               | 85       |

| 4.13          | Bode diagram for the open-loop transfer function $\ell(s)$ with pole cancellation                                                                       | 0.0      |

| 1 1 1         | and a zero at the origin for $h = 0.2$                                                                                                                  | 86       |

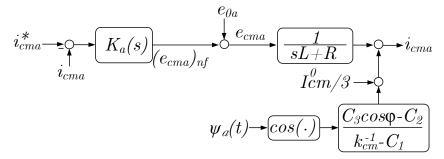

| 4.14          | Block diagram for the $i_{cm}$ control loop of phase $a$ , with feedforward control strategy action.                                                    | 87       |

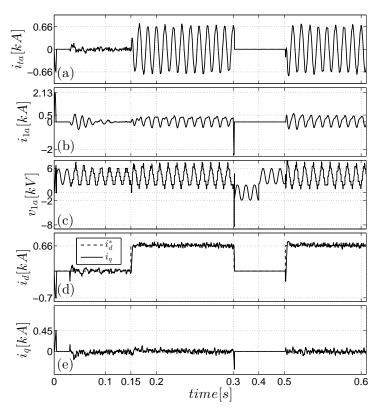

| 1 15          | Circulating current, CCSC action, submodule capacitor voltage, and ac-side                                                                              | 07       |

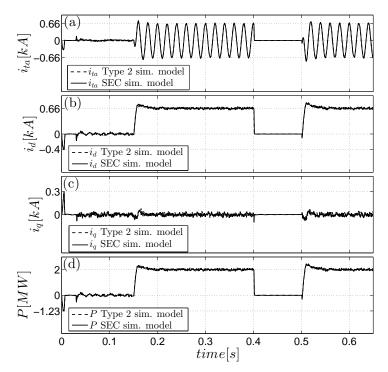

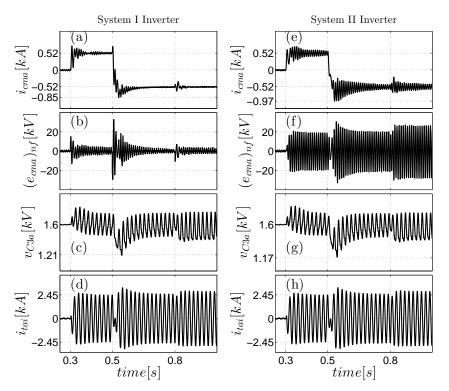

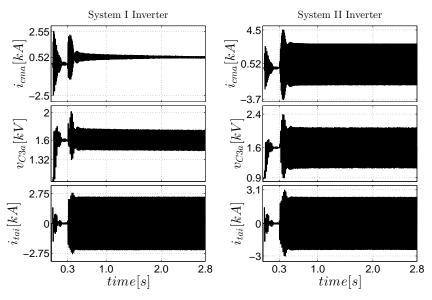

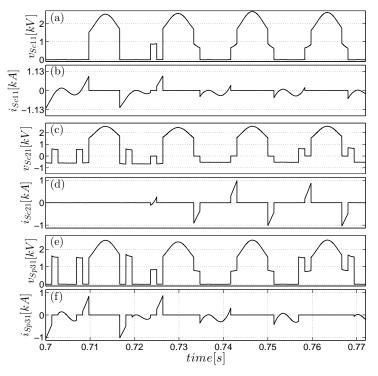

| 4.15          | terminal current for phase $a$ of the inverter station of systems I and II for Case I.                                                                  | 88       |

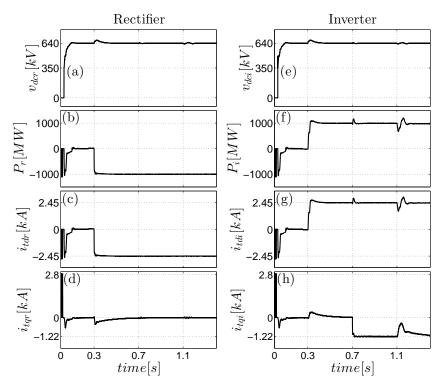

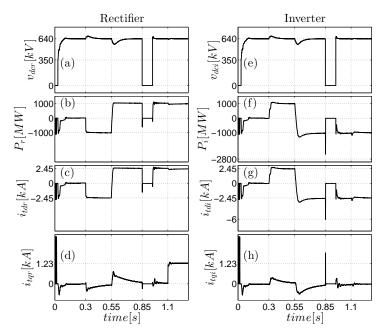

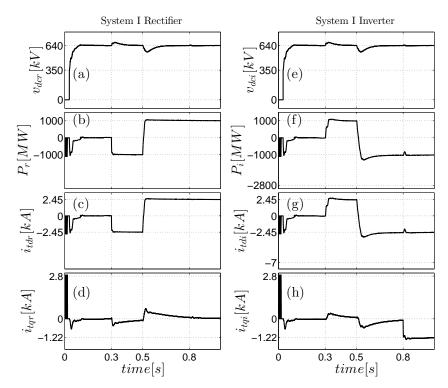

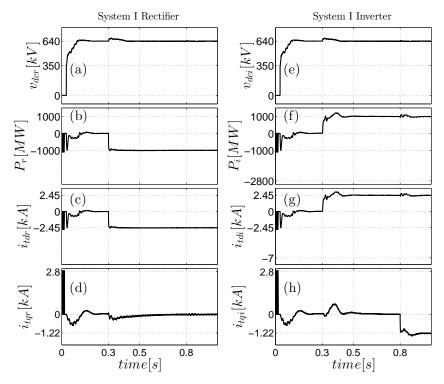

| 4.16          | dc-side voltage, active power, and the $dq$ components of the ac-side terminal                                                                          |          |

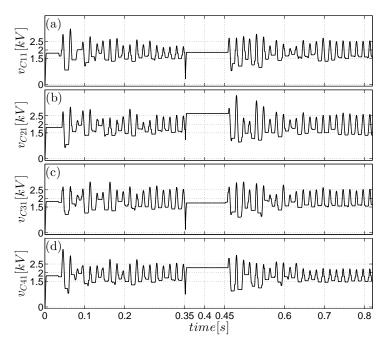

|               | current for both the rectifier and the inverter of System I for Case I                                                                                  | 89       |

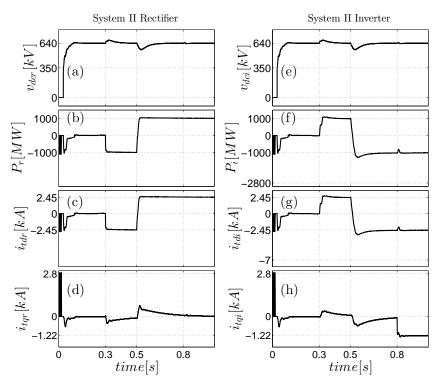

| 4.17          | dc-side voltage, active power, and the $dq$ components of the ac-side terminal                                                                          |          |

|               | current for both the rectifier and the inverter of System II for Case I                                                                                 | 90       |

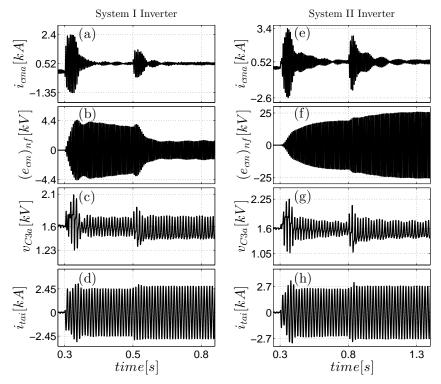

| 4.18          | Circulating current, CCSC action, submodule capacitor voltage, and ac-side                                                                              |          |

|               | terminal current for phase <i>a</i> of the inverter station of systems I and II for Case II.                                                            | 90       |

| 4.19          | dc-side voltage, active power, and the $dq$ components of the ac-side terminal                                                                          | 0.1      |

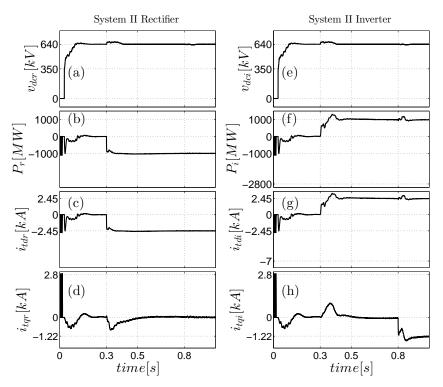

| 4.00          | current for both the rectifier and the inverter of System I for Case II.                                                                                | 91       |

| 4.20          | dc-side voltage, active power, and the $dq$ components of the ac-side terminal                                                                          | 02       |

| 4 21          | current for both the rectifier and the inverter of System II for Case II Circulating current, submodule capacitor voltage, and ac-side terminal current | 92       |

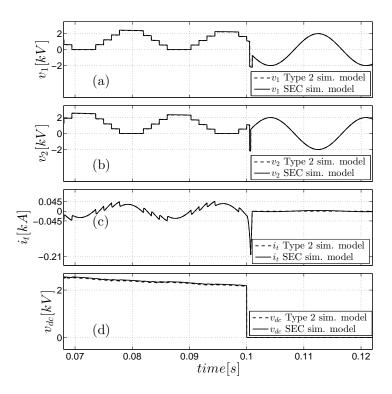

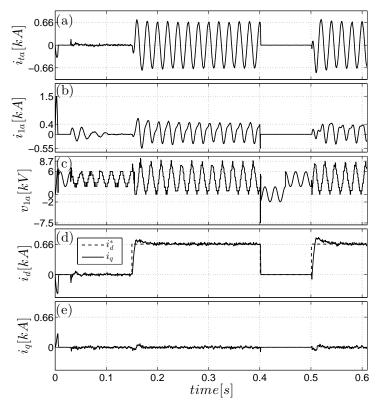

| т. <i>2</i> 1 | for phase <i>a</i> of the inverter station of systems I and II for Case III                                                                             | 92       |

| 4.22          | Circulating current, submodule capacitor voltage, and ac-side terminal current                                                                          | / 1      |

|               | for phase <i>a</i> of the inverter station of systems I and II for Case III, zoomed view.                                                               | 93       |

|               |                                                                                                                                                         |          |

xi

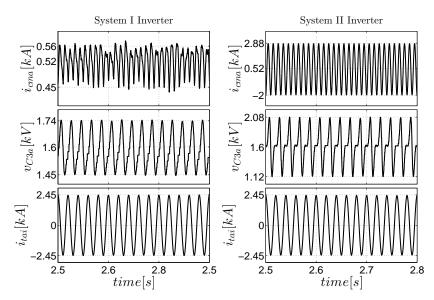

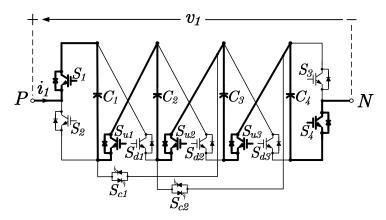

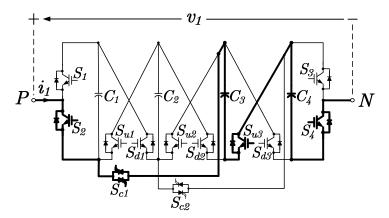

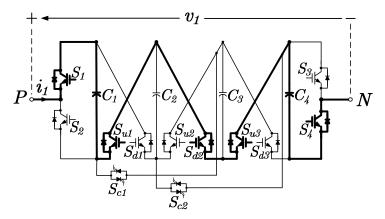

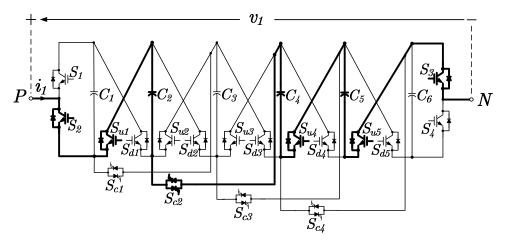

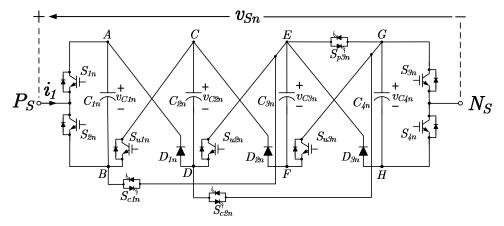

| 5.1          | Schematic diagram for one leg of the proposed MMC, the <i>LMMC</i>                                                           | 96  |

|--------------|------------------------------------------------------------------------------------------------------------------------------|-----|

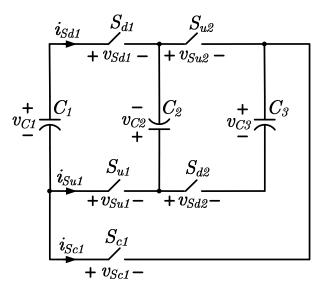

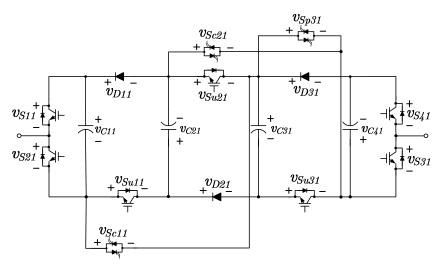

| 5.2          | Circuit of the <i>network</i> , the building block of the LMMC ( $n = 1, 2,, M - 1$ ).                                       | 97  |

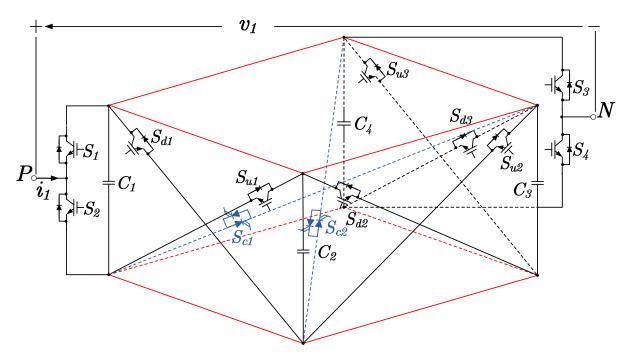

| 5.3          | Schematic diagram of the upper arm circuit of a 5-level LMMC.                                                                | 97  |

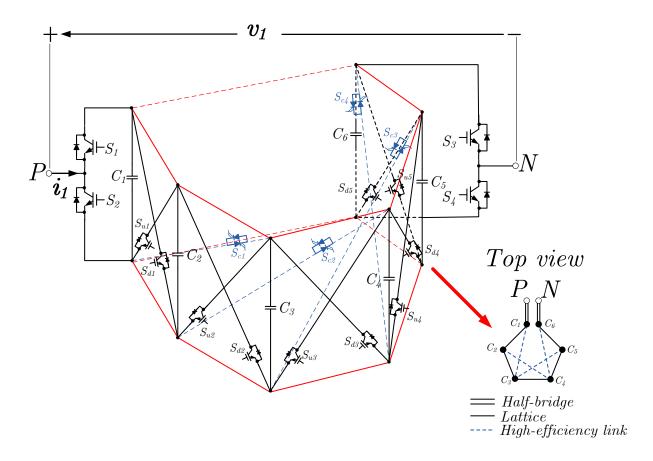

| 5.4          | Schematic diagram of the upper arm circuit of a 7-level LMMC and its top view.                                               | 98  |

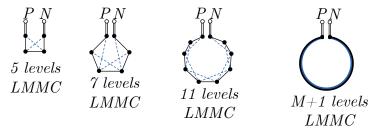

| 5.5          | Top view of an LMMC arm for different values of <i>M</i>                                                                     | 98  |

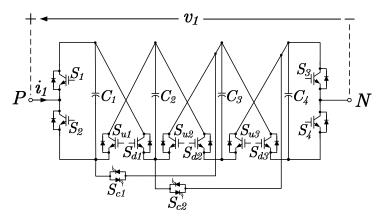

| 5.6          | Schematic diagram of the upper arm circuit of a 5-level LMMC, two-dimensional                                                |     |

|              | view                                                                                                                         | 99  |

| 5.7          | The current path for the upper arm of the 5-level LMMC of Fig. 5.6 if all                                                    |     |

|              | capacitors must be inserted.                                                                                                 | 99  |

| 5.8          | The current path for the upper arm of the 5-level LMMC of Fig. 5.6 if only                                                   |     |

|              | capacitors $C_3$ and $C_4$ must be inserted.                                                                                 | 99  |

| 5.9          | The current path for the upper arm of the 5-level LMMC of Fig. 5.6 if only                                                   |     |

|              | capacitors $C_1$ and $C_4$ must be inserted.                                                                                 | 100 |

| 5.10         | Schematic diagram of the upper arm circuit of the 5-level LMMC of Fig. 5.6                                                   |     |

|              | when the switches are <i>off</i> , e.g., subsequent to a dc-side fault.                                                      | 101 |

| 5.11         | Arm current path and <i>on</i> switches in the upper arm of a 7-level LMMC, if                                               |     |

|              | $\mathbf{x} = [0, 1, 0, 1, 1, 0].$                                                                                           |     |

|              | Fluxogram for the LMMC switching function matrix creation.                                                                   | 105 |

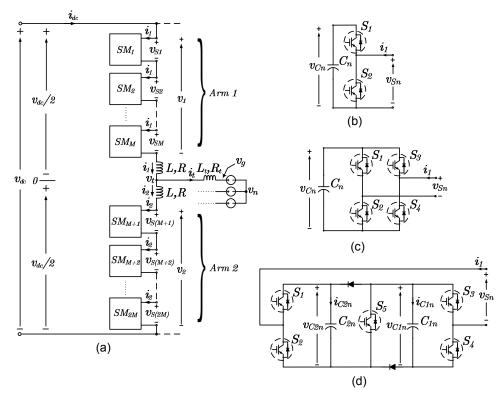

| 5.13         | Schematic diagrams of (a) one leg of a conventional three-phase MMC, (b) an                                                  |     |

|              | HBSM in the upper arm, (b) a FBSM in the upper arm, and (c) a CDSM in the                                                    | 100 |

| <b>5</b> 1 4 | upper arm.                                                                                                                   | 106 |

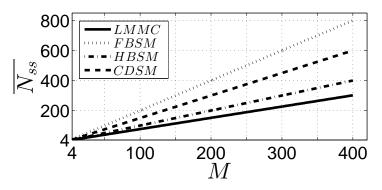

| 5.14         | The average number of series-connected switches per arm versus the number                                                    | 100 |

| 5 15         | of capacitors, for different MMC technologies                                                                                |     |

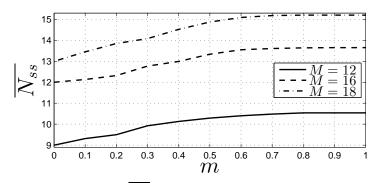

|              | Variation of $\overline{N_{ss}}$ with the modulation index, in the LMMC                                                      | 108 |

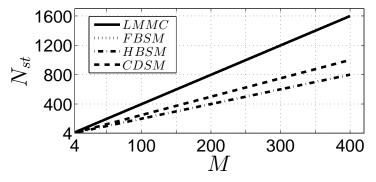

| 5.10         | Comparison of the total number of switches for the HBSM, the FBSM, the                                                       | 100 |

| 5 17         | CDSM, and the LMMC.                                                                                                          | 109 |

| 3.17         | Rearranged partial circuit for the voltage stress analysis in the switches con-<br>necting three capacitors in the LMMC arm. | 110 |

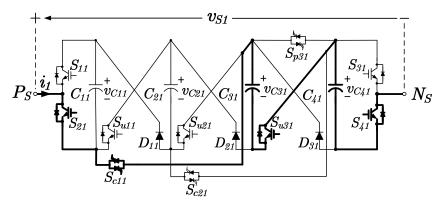

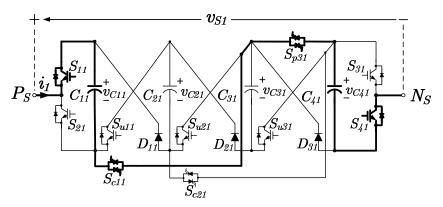

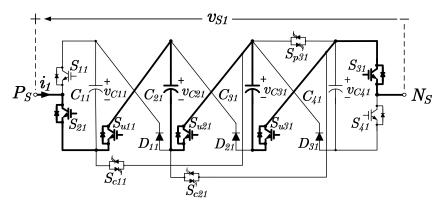

| 5 1 9        | Schematic diagram of the single-phase LMMC system for Case I                                                                 |     |

|              | Waveforms of selected variables in an open-loop controlled single-phase 5-                                                   | 112 |

| 5.19         | level LMMC (left column) and an equivalent FBSM-based MMC (right col-                                                        |     |

|              | umn), to various disturbances; Case I.                                                                                       | 113 |

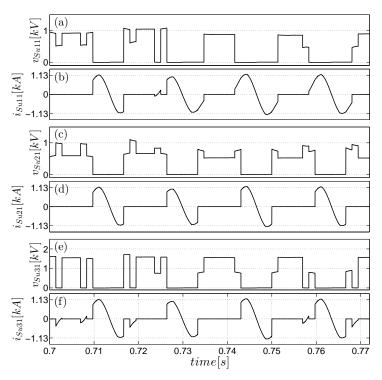

| 5 20         | Voltage and current waveforms for the switches of the second network of the                                                  | 115 |

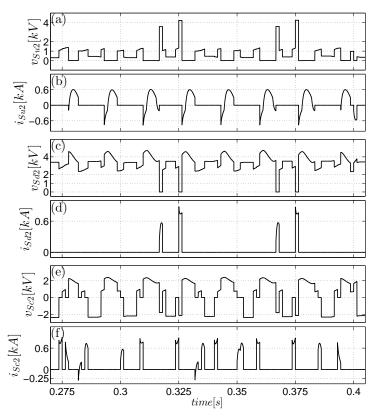

| 5.20         | upper arm; Case I                                                                                                            | 114 |

| 5 21         | Gating pulses for the switches of the second network in the upper arm of the                                                 |     |

| 5.21         | LMMC, and for $S_3$ of the first submodule in the upper arm of the FBSM-based                                                |     |

|              | MMC; Case I.                                                                                                                 | 115 |

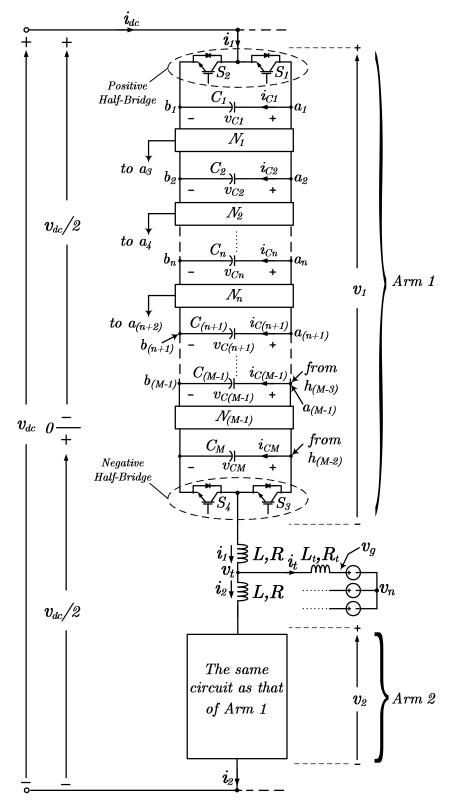

| 5.22         | Waveforms of selected variables in an open-loop controlled single-phase 9-                                                   | -   |

|              | level LMMC (left column) and an equivalent HBSM-based MMC (right col-                                                        |     |

|              | umn), to various disturbances; Case II.                                                                                      | 115 |

| 5.23         | Waveforms of selected variables in a closed-loop controlled three-phase 9-level                                              | -   |

|              | LMMC, to various disturbances; Case III.                                                                                     | 116 |

|              |                                                                                                                              |     |

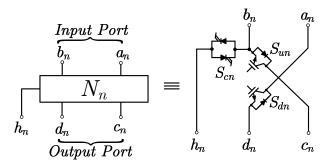

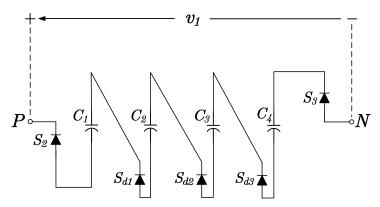

| 6.1          | Schematic diagram for the LSM.                                                                                               |     |

| 6.2          | Current path in the LSM with $C_{31}$ and $C_{41}$ inserted for $n = 1. \dots \dots \dots$                                   | 120 |

| 6.3  | Current path in the LSM with $C_{11}$ and $C_{41}$ inserted for $n = 1, \dots, \dots$                                                                        | . 120 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 6.4  | Current path in the LSM with $C_{21}$ and $C_{31}$ inserted, for $n = 1, \ldots, \ldots$                                                                     | . 120 |

| 6.5  | Rearranged LSM circuit, for $n = 1$                                                                                                                          | . 123 |

| 6.6  | Schematic diagram of the single-phase LSM-based MMC system for Case I                                                                                        | . 127 |

| 6.7  | Waveforms of selected variables in an open-loop controlled single-phase 5-                                                                                   |       |

|      | level LSM-based MMC, to various disturbances; Case I                                                                                                         | . 128 |

| 6.8  | Voltage and current waveforms for the switches of the positive regular links for                                                                             |       |

|      | n = 1; Case I                                                                                                                                                | . 129 |

| 6.9  | Voltage and current waveforms for the switches of the high-efficiency links and                                                                              |       |

|      | parallel link for $n = 1$ ; Case I                                                                                                                           | . 129 |

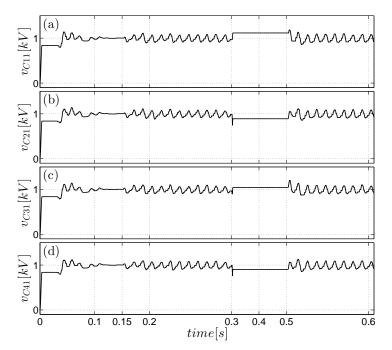

| 6.10 | Waveforms of the capacitor voltages in the phase a of a open-loop single-phase                                                                               |       |

|      | 5-level LSM-based MMC, for $n = 1$ , to various disturbances; Case I                                                                                         | . 130 |

| 6.11 | Waveforms of selected variables in a closed-loop controlled three-phase 9-level                                                                              |       |

|      | LSM-based MMC, to various disturbances; Case II                                                                                                              | . 131 |

| 6.12 | Waveforms of the capacitor voltages in the phase a of a closed-loop controlled                                                                               |       |

|      | three-phase 9-level LSM-based MMC, for $n = 1$ , to various disturbances; Case                                                                               |       |

|      | II                                                                                                                                                           | . 132 |

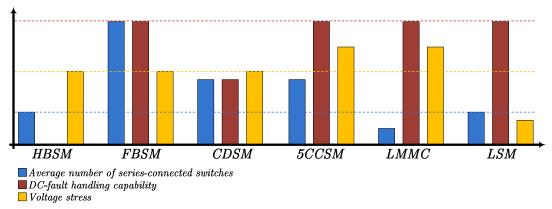

| 7.1  | Illustrated comparison between the helf bridge submedule, the full bridge sub-                                                                               |       |

| /.1  | Illustrated comparison between the half-bridge submodule, the full-bridge sub-<br>module, the clamp-double submodule, the 5-level cross-connected submodule, |       |

|      | the lattice modular multilevel converter, and the lattice submodule, regarding                                                                               |       |

|      |                                                                                                                                                              |       |

|      | dc-side fault handling capability, average number of series-connected switches,                                                                              | 124   |

|      | and voltage stress                                                                                                                                           | . 134 |

# **List of Tables**

| 2.1 | Circulating current, submodule capacitor voltage, and arm voltage harmonic   |

|-----|------------------------------------------------------------------------------|

|     | components amplitudes                                                        |

| 2.2 | Modulation index calculation                                                 |

| 2.3 | Comparison between different methods for capacitor sizing assuming circulat- |

|     | ing current control on                                                       |

| 2.4 | Comparison between the proposed capacitor sizing method and experimental     |

|     | set-ups                                                                      |

| 4.1 | Classification of cases and systems simulated                                |

| 5.1 | Average number of series-connected switches per arm                          |

| 5.2 | Total number of switches for different topologies                            |

| 5.3 | Power loss expressions for large M                                           |

| 5.4 | Voltage across the switches in the LMMC arm                                  |

| 5.5 | Simulated power losses for Cases I and II                                    |

| 6.1 | Switch States in Terms of VBA Array Elements for an LSM                      |

| 6.2 | Boolean Logic for the Switch States in Terms of VBA Array Elements 122       |

| 6.3 | Simulated power losses and <i>H</i>                                          |

# **List of Abbreviations**

| HVDC | High-voltage direct current          |

|------|--------------------------------------|

| VSC  | Voltage-sourced converter            |

| LCC  | Line-commutated converter            |

| MMC  | Modular multilevel converter         |

| LMMC | Lattice modular multilevel converter |

| LSM  | Lattice submodule                    |

| HBSM | Half-bridge submodule                |

| FBSM | Full-bridge submodule                |

| CDSM | Clamp-double submodule               |

| SEC  | Simplified equivalent-circuit        |

|      |                                      |

- $v_{dc}$  DC voltage

- $v_g$  Grid voltage

- $v_{ga}$  Grid voltage phase a

- $v_{gb}$  Grid voltage phase b

- $v_{gc}$  Grid voltage phase c

- $v_{gLL}$  Grid line-to-line voltage

- $i_t$  Ac-side terminal current

- $\widehat{I}$  Ac-side terminal current peak

- $\varphi$  Ac-side terminal current angle

- $i_{ta}$  Ac-side terminal current of phase a

- $i_{tb}$  Ac-side terminal current of phase b

- $i_{tc}$  Ac-side terminal current of phase c

- $i_{td}$  Ac-side terminal current *d* component in *dq*-frame

- $i_{tq}$  Ac-side terminal current q component in dq-frame

- $i_r$  Current in the arm r (r = 1 for the upper arm and r = 2 for the lower arm)

- *i*<sub>cm</sub> Circulating current

- $i'_{cm}$  Circulating current dependent on itself

- $i_{cma}$  Circulating current phase a

- $i_{cmb}$  Circulating current phase b

- $i_{cmc}$  Circulating current phase c

- $v_{Cj}$  Submodule capacitor voltage in capacitor j

- $\overline{v}_C$  Submodule capacitor average voltage (MMC resolution)

- $v_{Sn}$  Ac voltage of submodule n

- $v_1$  Upper arm voltage

- $v_2$  Lower arm voltage

- $e_t$  Inner voltage

- *M* Number of capacitor per arm

- *N* Number of submodules per arm

- $n_1$  Number of capacitors inserted in the upper arm

- $n_2$  Number of capacitors inserted in the lower arm

- *L* Arm inductance

- *C* Submodule capacitance

- *R* Arm resistance

- $R_t$  Terminal resistance

- *L<sub>t</sub>* Terminal inductance

- L' Equivalent inductance from the ac side

- R' Equivalent resistance from the ac side

- *m* Modulating function

- $\widehat{m}$  Modulation index

- $\theta$  Modulating function angle

- *a* MMC assymetry

- $T_s$  MMC sample time

- $f_g$  Grid frequency

- $\omega$  Grid angular frequency

| $C_{eqr}$                | Equivalent capacitance of arm r           |

|--------------------------|-------------------------------------------|

| v <sub>ir</sub>          | Integrated voltage in arm r               |

| $v_1^{i_t}$              | upper arm voltage created by $i_t$        |

| $v_1^{i_{cm}}$           | upper arm voltage created by $i_{cm}$     |

| $I_{cm}^0$               | Circulating current dc component          |

| $(i_{cm})_2$             | Circulating current second harmonic       |

| $(i_{cm})_4$             | Circulating current fourth harmonic       |

| $\widehat{I}_{cm}$       | Circulating current second harmonic peak  |

| $\widehat{I}_{cm4}$      | Circulating current fourth harmonic peak  |

| $arphi_2$                | Circulating current angle                 |

| Р                        | Active power exchanged with the ac grid   |

| Q                        | Reactive power exchanged with the ac grid |

| $P_{loss}$               | Power loss in the MMC arm                 |

| <i>i<sub>trms</sub></i>  | Ac-side terminal current rms value        |

| <i>i<sub>cmrms</sub></i> | Circulating current rms value             |

| $\widehat{e}_t$          | Inner voltage peak                        |

| δ                        | Inner voltage angle                       |

| $(v_{C})_{1}$            | Submodule capacitor voltage fundamental   |

| (1, 1)                   | Submodule consister voltage accord harmo  |

- $(v_C)_2$  Submodule capacitor voltage second harmonic

- $(v_C)_3$  Submodule capacitor voltage third harmonic

- $\tilde{v}_{Cn}$  Submodule capacitor approximate voltage, negative half-cycle

- $\tilde{v}_{Cp}$  Submodule capacitor approximate voltage, positive half-cycle

- $(\tilde{v}_C)_{1n}$  Fundamental of the submodule capacitor approximate voltage, negative half-cycle

- $(\tilde{v}_C)_{2n}$  Second harmonic of the submodule capacitor approximate voltage, negative half-cycle

- $(\tilde{v}_C)_{3n}$  Third harmonic of the submodule capacitor approximate voltage, negative half-cycle

- $(\tilde{v}_C)_{1p}$  Fundamental of the submodule capacitor approximate voltage, positive half-cycle

- $(\tilde{v}_C)_{2p}$  Second harmonic of the submodule capacitor approximate voltage, positive half-cycle

- $(\tilde{v}_C)_{3p}$  Third harmonic of the submodule capacitor approximate voltage, positive half-cycle

- $\Delta v_C$  Submodule capacitor voltage variation

- $\Delta \tilde{v}_C$  Submodule capacitor approximate voltage variation

- $(\Delta \tilde{v}_C)_p$  Submodule capacitor approximate voltage variation, positive half-cycle

- $(\Delta \tilde{v}_C)_n$  Submodule capacitor approximate voltage variation, negative half-cycle

- $t_p$  Instant where  $\tilde{v}_{Cp}$  reaches its peak

- $t_n$  Instant where  $\tilde{v}_{Cn}$  reaches its peak

- $r_{n1}$  Angle in radians for the peak of the fundamental of the submodule capacitor voltage, negative half-cycle

- $r_{n2}$  Angle in radians for the peak of the second harmonic of the submodule capacitor voltage, negative half-cycle

- $r_{n3}$  Angle in radians for the peak of the third harmonic of the submodule capacitor voltage, negative half-cycle

- $N_{ss}$  Number of series connected switches in an arm

- $\overline{N}_{ss}$  Average number of series connected switches in an arm

# Chapter 1

### Introduction

### **1.1 Background and Motivation**

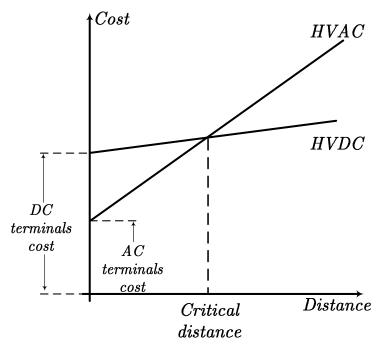

A high-voltage dc (HVDC) system for bulk transmission of electric energy over large distances is more efficient and economical than an ac counterpart, especially if undersea cables are involved, although HVDC transmission systems are on occasions the only choice, e.g., for interconnecting power systems of different frequencies, or for other strategic purposes. Therefore, for most applications choice of using whether a high-voltage ac (HVAC) transmission system or a HVDC transmission system depends primarily on the distance of the transmission, as illustrated in Fig. 1.1. As the figure shows, the initial cost of an HVDC system is higher than that of an HVAC counterpart. However, the overall cost of the HVAC system rises more rapidly with the distance of transmission, mainly due to the cost of the transmission lines. Therefore, there is a distance, marked on Figure 1.1 as the critical distance, at which HVDC transmission becomes more attractive economically. For underground transmission, this critical distance is in the range 500 km to 800 km [1], whereas it is in the range 700 km to 900 km for overhead transmission [2].

The first HVDC transmission system was commissioned in 1954 and connected Gotland in the island of Ygne, Sweden, with the main land, as Figure 1.2 illustrates. The Gotland HVDC system was designed to process 20 MW at a dc voltage of 100 kV, through 96 km of undersea cables. At that time, mercury-arc valves were used for the rectifier and inverter terminals of the HVDC system. In 1970, the Gotland HVDC system became the first to use the thyristor as the electronic switch for its rectifier and inverter stations; this allowed the rated transmitted power to be raised to 30 MW at 150 kV [4], [5]. Since the Gotland project, the thyristor has served as the switch of choice in HVDC systems. Thyristor-based HVDC systems, using the so-called line-commutated converters (LCCs), can process up to 7600 MW of power, at voltages up to 800 kV, and over distances up to 2090 km, as it is the case for the Jinping-Sunan ultra high voltage direct current (UHVDC) system in China, commissioned in 2013 [6].

The thyristor can only be turned on at will; it turns off only if its current crosses zero. Therefore, the LCC must be interfaced with an adequately stiff ac grid. This, in turn, means that the LCC cannot be used to energize passive islands, not does it offer blackstart capability. In addition, it pulsates with three times the ac grid frequency, requiring costly ac- and dc-side filters. Further, it demands a substantial amount of reactive power, again, requiring a stiff ac

Figure 1.1: Critical distance when HVDC transmission becomes more cost effective in relation to HVAC.

Figure 1.2: Illustration of the location of the first HVDC transmission system, Gotland, Sweden [3].

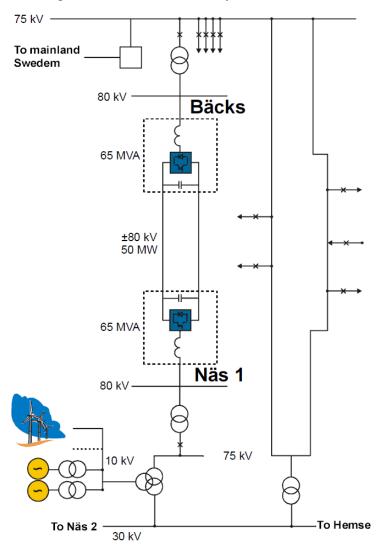

grid or compensation. Furthermore, due to its unidirectional dc current, it requires reversal of its dc voltage polarity if the power flow is to be reversed [7]-[9]. For these reasons, the LCC is being replaced by the voltage-sourced converters (VSCs) which use electronic switches with gate turn-off capabilities such as the insolated-gate bipolar transistor (IGBT) [10]. The VSC can pulsate at much higher frequencies and, therefore, requires smaller filters. Moreover, it can operate at any power factor and with weak ac grids, it offers blackstart capability, and it allows for a bidirectional power flow while the polarity of its dc voltage remains unchanged [10]. The first VSC-based HVDC system was installed in Sweden (again in Gotland), in 1997 [11], to process 50 MW at a voltage of 80 kV, through 70 km of underground cables; Fig. 1.3

illustrates a schematic diagram of the transmission system.

Figure 1.3: Schematic diagram of the VSC-based HVDC transmission system in Gotland, Sweden [11].

In the recent past, the interest in VSC-based HVDC systems has become stronger due to the notion of multi-terminal direct current (MTDC) grids [5]. The idea is to enable mass integration of renewable energy resources scattered over large geographical spans [12], and to offer various energy trade scenarios in a multi-country/multi-continent power system. This would require the co-existence of overhead, underground, and undersea high-voltage transmission lines. However, the conventional technologies for the VSC are limited in terms of voltage and power handling capabilities, relative to the LCC, and, consequently, are deemed unsuitable for MTDCs. Therefore, a new breed of the VSC, known as the modular multilevel converter (MMC) [13], is being seriously considered for HVDC systems. The MMC permits the dc voltage to be divided over multiple modules hosting switches and capacitors. Therefore, the voltage rating of each module can be small, thus allowing for the use of fully-controllable semiconductor switches such as the IGBT [14]-[16]. Further, the modular nature of the MMC enhances its fault tolerance and reliability.

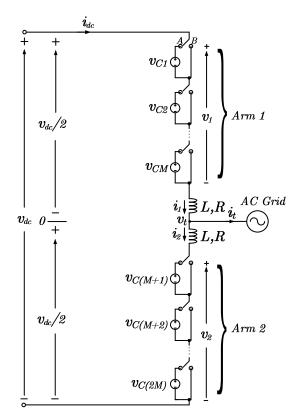

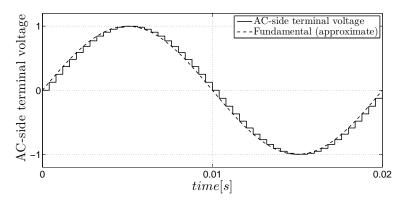

Figure 1.4 shows a conceptual schematic diagram for one leg of the MMC. The MMC basic mechanism is to connect (insert) or disconnect (bypass) voltage sources (denoted by  $v_{Cj}$  (j = 1, 2, ..., M in the upper arm, and j = M + 1, M + 2, ..., 2M in the lower arm) in series in an arm, through fully controllable switches, represented in Fig. 1.4 as ideal switches. The voltage sources are inserted in the MMC arm when the switches are in the position A, and are bypassed when the switches are in the position B. Further, the insertion of voltage sources in both MMC arms generates an *ac-side terminal voltage*,  $v_t$ , that controls the power exchange with the ac grid. Each voltage source inserted in an arm, together with another voltage source with equal average magnitude bypassed in the opposite arm, creates a voltage step in the ac-side terminal voltage. If the number of steps is large enough, the ac-side terminal voltage features a very low harmonic distortion, even without the use of filters. As an example, Fig. 1.5 shows the ac-side terminal voltage and its fundamental component of an MMC with 50 voltage sources per arm.

The voltage sources are arranged in "cells", referred to as *submodules*. Each submodule is formed by one or more voltage sources, together with a number of semiconductor switches, represented in Fig. 1.4 by ideal switches. The voltage sources in the MMC leg have the same voltage, regulated to be 1/M times the dc-side voltage,  $v_{dc}$ , where M is the number of voltage sources in an arm. Moreover, the submodules are arranged in such a way that the voltage across the switches has an average value equal to 0.5, 1, or 2 times the source voltage, depending on the topology of the submodules. In practice, a capacitor plays the role of a voltage source. Therefore, the control of the MMC must regulate the voltage of the capacitors. A detailed description of the MMC and its modelling, is presented in Chapter 2. Finally, the different topologies used for the submodules are discussed in Section 1.3.4, and further in Chapters 5 and 6.

Four projects are cited here as examples of MMC-based HVDC systems: the Transbay Project, the Inelfe Project, the Ultranet Project, and the Nemo Project. The Transbay transmission system connects Pittsburgh, CA to San Francisco, CA, through 88-km undersea cables and can transmit 400 MW at a voltage of  $\pm 220 kV$ ; its MMC has more than 200 SMs per arm in each terminal [17]. Figure 1.6 illustrates the Transbay marine HVDC transmission system. The Inelfe transmission system connects Baixas in France to Santa Llogaia in Spain, through 65 km long underground cables. The system can process 2000 MW through two subsystems, each rated 1000 MW/±320 kV. Each station employs a three-phase MMC with 400 SMs per arm [18]-[22]. Figure 1.7 illustrates the location of the Inelfe HVDC transmission system. The Nemo transmission system, scheduled to be commissioned in 2019, will transmit 1000 MW at a voltage of  $\pm 400 \, kV$ , through undersea cables [23]. Figure 1.8 illustrates the Nemo transmission system. The fourth example is the Ultranet transmission system, which is still in the planning phase. The Ultranet transmission system is expected to process 2000 MW at a transmission voltage of  $\pm 380 \, kV$ , through overhead lines [25]. Transmission of energy through overhead lines, requires a submodule technology that is robust to dc-side faults that strike overhead lines. Therefore, in contrast to the three aforementioned projects, the full-bridge submodule (FBSM) is considered for the Ultranet system. Fig. 1.9 shows the future site of the Ultranet transmission system.

Figure 1.4: Conceptual schematic diagram for one leg of an MMC.

Figure 1.5: AC-side terminal voltage and its fundamental component for an MMC with 50 voltage sources per arm.

Figure 1.6: Transbay HVDC transmission system, connecting Pittsburgh, CA to San Francisco, CA [17].

Figure 1.7: Location of the Inelfe HVDC transmission system, connecting Sta Llogaia, Spain to Baixas, France [21].

Figure 1.8: Illustration of the Nemo HVDC transmission system, connecting Richborough, UK to Zeebrugge, Belgium [24].

### **1.2** Statement of Problem and Thesis Objectives

The MMC is a promising technology, but it is still in its infancy. Therefore, there are multiple issues associated with its component sizing, effective control, efficient simulation, and fault handling capability. Thus, this thesis is focused on the development of analytical and simulation models, effective control strategies, and enhanced topologies, for the MMC. The more specific objectives of this thesis are described below.

- 1. To develop an adequately general, yet, accurate model for the purpose of component sizing and controller design;

- 2. To develop a simplified and easy-to-implement simulation model for the MMC;

- 3. To develop a control strategy to efficiently suppress the circulating current in the MMC; and

- 4. To propose topologies for the MMC that offer higher efficiencies and more economical dc-side fault handling capabilities.

Figure 1.9: Future site of the Ultranet HVDC transmission system, connecting Osterath to Philippsburg, Germany [25].

### **1.3** Literature Survey Pertinent to the Thesis Objectives

### 1.3.1 Modelling of the MMC and component sizing

The MMC modelling represents a very important step for understanding the steady-state and the dynamic behavior in different situations. Also, the correct control and component sizing rely heavily in the MMC modeling. Several works have been published on the MMC modelling [26]-[38], and component sizing [39]-[46], but still some gaps remain to be filled, as described below.

In [26], the MMC has been modeled from the point of view of the ac side, considering each submodule (SM) as a constant voltage source, disregarding the submodule capacitor dynamics in the ac-side terminal current controller, and taking into account only the fundamental component of the MMC voltages and currents. This approach is enough for designing the compensator responsible for controlling the power exchanged between the MMC and the ac grid. However, the submodule capacitor voltage variation and the harmonic components in the arm current are not considered. In [27] the MMC has been modeled in open-loop state and with the submodule capacitive dynamics taken into account, which yields non-linear and time-varying differential equations. The MMC non-linear time-varying model was developed further in [28] and [29]. The proposed model in [28] and [29] considers the ac-side terminal current compensator and the circulating current suppression compensator, following the control strategy described in [30]. Even though the model presented in [29] is adequate, for the control strategies employed, a steady-state model is nonetheless needed for predicting the steady-state magnitude of the MMC quantities, and, in turn, permitting the sizing of the components of the MMC. Thus, in [31], a parametric model for the steady-state magnitude of the circulating current is developed. The described model presents a relative high error, in comparison to the simulation results, and, if applied to HVDC systems, such as described in [18], [22], and [20], the error becomes even higher. Another, more detailed steady-state model is developed in [32]. The presented model correctly predicts the amplitude of the circulating current and, also, predicts the condition for arm current resonance that can destabilize the converter. Then, in [33], a different steady-state model is described, using a different mechanism than [32], and providing simpler equations. The predictions in [33], were shown to be also accurate. However, the models presented in [32] and [33] are still incomplete, in the sense that they do not predict the amplitudes of all harmonic components of the currents and voltages of the MMC. Other dynamic models are described in [34], [35], [36], and another steady-state model is presented in [37], with no advantages added in comparison to the previously commented models, from the point of view of the author. In [38] a new dynamic model is developed in dq-frame, facilitating the designing of the MMC compensators. However, the dq-frame model proposed in [38], is not suitable for deriving equations for the amplitude of the harmonic components of the voltages and currents of the MMC.