#### Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2013

# A Cost Efficiency Analysis and Mechanism for Dynamic Partially Reconfigurable Computing Systems

David Diaz Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Systems Architecture Commons</u>

#### **Recommended** Citation

Diaz, David, "A Cost Efficiency Analysis and Mechanism for Dynamic Partially Reconfigurable Computing Systems" (2013). *Theses and dissertations*. Paper 2068.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

# A COST EFFICIENCY ANALYSIS AND MECHANISM FOR DYNAMIC PARTIALLY RECONFIGURABLE COMPUTING SYSTEMS

by

David Diaz

Bachelor of Engineering, Ryerson, 2009

A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Applied Science

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2013

©David Diaz 2013

## Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions of individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopy or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public.

# A COST EFFICIENCY ANALYSIS AND MECHANISM FOR DYNAMIC PARTIALLY RECONFIGURABLE COMPUTING SYSTEMS

Master of Applied Science 2013

David Diaz

Electrical and Computer Engineering

Ryerson University

#### Abstract

Dynamic Partially Reconfigurable Computing Systems have proven to be useful in environments where a multiplicity of tasks is required. These systems used Dynamic Virtual Components (DVCs) for reconfiguration. However, the computing architecture (dedicated, software, hybrid) of the DVC must be selected during the design stage. In this thesis, a mechanism in which we evaluate and analyze the cost efficiency of a DVC based on a cost efficiency factor (CEF) is proposed. Data centric and stream centric experimental tests were performed and the CEF of a 3D stereo-panoramic augmented reality hybrid DVC was determined. The results show that development costs and number of units to be produced influence the cost efficiency of a DVC. From the results it is concluded that the CEF can be a useful tool for selecting the computing architecture of a DVC, particularly when only a few units are to be deployed.

### Acknowledgements

Completing my Master of Applied Science studies would never have been possible without the guidance of my professors, help from friends, and support from my family.

I would like to express my deepest gratitude to Dr. Lev Kirischian, my supervisor, for his guidance, patience, motivation, enthusiasm and immense knowledge. I could have not chosen a better supervisor for my thesis and I am glad to have chosen his lab for my graduate studies in pursue of my graduate degree.

I would also like to give my sincere thanks to my fellow colleagues Victor Dumitriu and Artur Saakov for their help in the lab. Their advice and sharing of their knowledge throughout my graduate studies is greatly appreciated.

I also would like to thank the Department of Electrical and Computer Engineering at Ryerson University for giving me this educational opportunity.

And lastly, I would like to thank my parents and my brother who have given me their support in pursuing my educational goals.

## Dedication

This thesis is dedicated to my mother Gilda, my father Roberto, and my brother Roberto J. for their love throughout my life and their never ending support and encouragement in achieving my education goals in life.

# Contents

| 1        | The            | esis Introduction                                          | 1  |

|----------|----------------|------------------------------------------------------------|----|

|          | 1.1            | Motivation Statement                                       | 1  |

|          | 1.2            | Objectives                                                 | 3  |

|          | 1.3            | Original Contributions                                     | 4  |

|          | 1.4            | Thesis Organization                                        | 4  |

| <b>2</b> | $\mathbf{Rel}$ | ated Works                                                 | 6  |

|          | 2.1            | Introduction                                               | 6  |

|          | 2.2            | Related Work Observation & Analysis                        | 6  |

|          | 2.3            | Summary                                                    | 12 |

| 3        | Pro            | posed Approach to Evaluate the Cost Effectiveness of a DVC | 13 |

|          | 3.1            | Introduction                                               | 13 |

|          | 3.2            | Concepts and Theory Analysis                               | 13 |

|          |                | 3.2.1 Summary                                              | 26 |

| 4        | Арј            | proach Using Experimental Applications                     | 27 |

|          | 4.1            | Introduction                                               | 27 |

|          | 4.2            | DPRS Experimental Setup                                    | 28 |

|          | 4.3            | Data Centric Experiment Test                               | 29 |

|          |                | 4.3.1 Sobel Mask Computation Description                   | 29 |

|          |                | 4.3.2 Sobel Mask Computation Principles                    | 29 |

|     | 4.3.3  | Sobel Mask Experimental Implementation                            | 30 |

|-----|--------|-------------------------------------------------------------------|----|

|     | 4.3.4  | Sobel Mask DVC Symbol                                             | 33 |

|     | 4.3.5  | Sobel Mask DVC I/O Signals                                        | 33 |

|     | 4.3.6  | Sobel Mask DVC Organization                                       | 35 |

|     | 4.3.7  | Collected Experimental Data From Sobel Mask DVCs                  | 36 |

| 4.4 | Stream | n Based Experiment Test                                           | 37 |

|     | 4.4.1  | RGB to $YC_BC_R$ Conversion Description                           | 37 |

|     | 4.4.2  | RGB to $YC_BC_R$ Principles                                       | 37 |

|     | 4.4.3  | RGB to $YC_BC_R$ Experimental Implementation                      | 38 |

|     | 4.4.4  | RGB to $YC_BC_R$ DVC Symbol                                       | 38 |

|     | 4.4.5  | RGB to $YC_BC_R$ DVC I/O Signals                                  | 38 |

|     | 4.4.6  | RGB to $YC_BC_R$ DVC Organization                                 | 40 |

|     | 4.4.7  | Collected Experimental Data from RGB to $YC_BC_R$ DVCs $\ldots$ . | 40 |

| 4.5 | Data   | and Stream Based Experiment                                       | 41 |

|     | 4.5.1  | NUI-ARDS DVC                                                      | 41 |

|     | 4.5.2  | NUI-ARDS DVC Description                                          | 41 |

|     | 4.5.3  | NUI-ARDS DVC Principles                                           | 44 |

|     | 4.5.4  | NUI-ARDS DVC Implementation                                       | 50 |

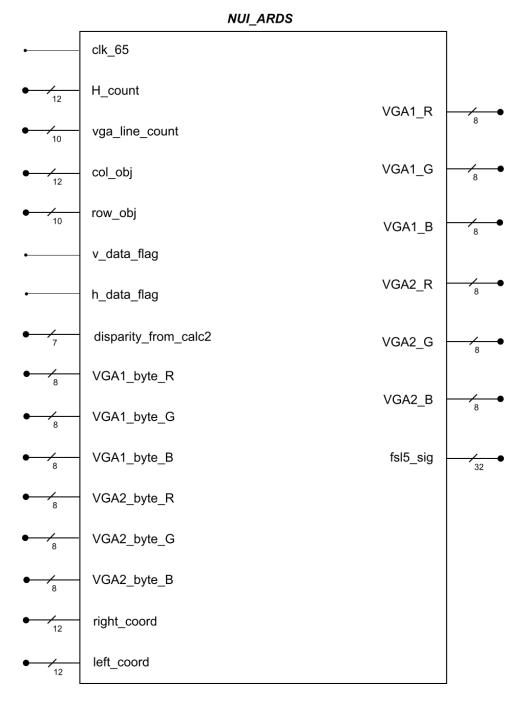

|     | 4.5.5  | NUI-ARDS DVC Symbol                                               | 53 |

|     | 4.5.6  | NUI-ARDS DVC I/O Signals                                          | 54 |

|     | 4.5.7  | NUI-ARDS DVC Organization                                         | 54 |

| 4.6 | Summ   | nary                                                              | 57 |

| <b>5</b>                  | CE   | F Analysis and Discussion                            | 58 |

|---------------------------|------|------------------------------------------------------|----|

|                           | 5.1  | Introduction                                         | 58 |

|                           | 5.2  | CEF Analysis Explanation                             | 58 |

|                           | 5.3  | Analysis of Data Centric Experiment Test             | 59 |

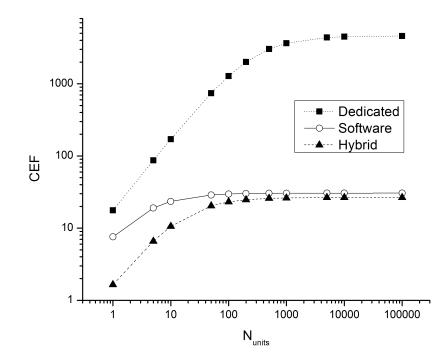

|                           |      | 5.3.1 Sobel Mask Experiment Analysis                 | 59 |

|                           |      | 5.3.2 Sobel Mask Experiment Discussion               | 61 |

|                           | 5.4  | Analysis of Stream Centric Experiment Test           | 62 |

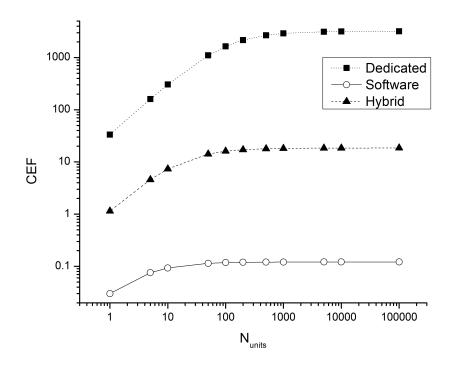

|                           |      | 5.4.1 Y $C_B C_R$ Converter Experiment Analysis      | 62 |

|                           |      | 5.4.2 Y $C_B C_R$ Experiment Discussion              | 63 |

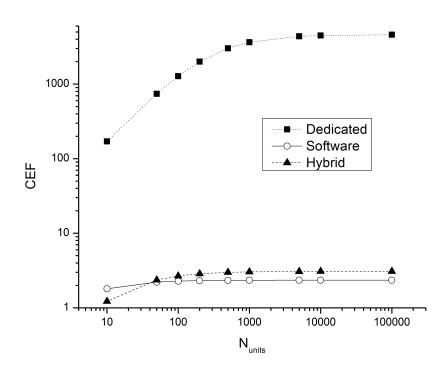

|                           | 5.5  | Hybrid Software Code Optimization CEF                | 64 |

|                           | 5.6  | NULARDS CEF Vs. CPR Analysis                         | 68 |

|                           | 5.7  | Summary                                              | 69 |

| 6                         | Cor  | nclusion and Future Work                             | 71 |

| $\mathbf{A}_{\mathbf{j}}$ | ppen | dices                                                | 74 |

| $\mathbf{A}_{]}$          | ppen | dix A Microblaze mb2 Component Internal Organization | 74 |

| $\mathbf{A}_{\mathbf{j}}$ | ppen | dix B NUI-ARDS Component I/O Signals                 | 76 |

| $\mathbf{A}$              | ppen | dix C CEF Calculations                               | 79 |

|                           | C.1  | Optimized Code                                       | 80 |

|                           | C.2  | Non-Optimized Code                                   | 83 |

|                           | C.3  | NUI-ARDS CEF                                         | 86 |

## Bibliography

# List of Tables

| 3.1 | Engineering Avg. Wage per Hour (Toronto)                  | 19 |

|-----|-----------------------------------------------------------|----|

| 4.1 | Sobel DVC input signals                                   | 34 |

| 4.2 | Sobel DVC output signals                                  | 34 |

| 4.3 | MAC_hwacc input signals                                   | 35 |

| 4.4 | MAC_hwacc output signals                                  | 35 |

| 4.5 | Sobel mask experimental data                              | 37 |

| 4.6 | Input Signals                                             | 39 |

| 4.7 | Output Signals                                            | 39 |

| 4.8 | RGB to $YC_BC_R$ Experimental Data                        | 40 |

| 5.1 | Selected UC equivalent resource Spartan FPGA chip cost    | 59 |

| 5.2 | Sobel mask DVC development cost                           | 60 |

| 5.3 | RGB to $YC_BC_R$ DVC Development Cost                     | 62 |

| 5.4 | Un-Optimized code execution time for Sobel mask DVC       | 65 |

| 5.5 | Un-Optimized code execution time for RGB to $YC_BC_R$ DVC | 65 |

| B.1 | Input signals required by NUI-ARDS                        | 77 |

| B.2 | Output signals produced by NUI-ARDS                       | 78 |

| C.1 | Sobel Dedicated DVC CEF Calculations                      | 80 |

| C.2 | Sobel Software DVC CEF Calculations                       | 80 |

| C.3 | Sobel Hybrid DVC CEF Calculations                         | 81 |

| C.4  | $YC_BC_R$ Dedicated DVC CEF Calculations                                   | 81 |

|------|----------------------------------------------------------------------------|----|

| C.5  | $YC_BC_R$ Software DVC CEF Calculations                                    | 81 |

| С.6  | $YC_BC_R$ Hybrid DVC CEF Calculations                                      | 82 |

| C.7  | Sobel dedicated DVC CEF calculations (Non-Optimized Code)                  | 83 |

| C.8  | Sobel Software DVC CEF Calculations (Non-Optimized Code) $\ . \ . \ . \ .$ | 83 |

| С.9  | Sobel Hybrid DVC CEF Calculations (Non-Optimized Code)                     | 84 |

| C.10 | $YC_BC_R$ Dedicated DVC CEF Calculations (Non-Optimized Code)              | 84 |

| C.11 | $YC_BC_R$ Software DVC CEF Calculations (Non-Optimized Code)               | 84 |

| C.12 | $YC_BC_R$ Hybrid DVC CEF Calculations (Non-Optimized Code)                 | 85 |

| C.13 | NUI-ARDS Hybrid DVC CEF Calculations                                       | 86 |

# List of Figures

| 2.1  | Diagram of a general dedicated computing architecture                 | 7  |

|------|-----------------------------------------------------------------------|----|

| 2.2  | Diagram of a general software computing architecture                  | 7  |

| 2.3  | Diagram of a general hybrid computing architecture                    | 8  |

| 2.4  | Diagram of a DRCA                                                     | 9  |

| 2.5  | General diagram of a DPRCA                                            | 9  |

| 3.1  | Direct and indirect computing device component costs                  | 16 |

| 3.2  | DPRCS with different sized slots and DVC                              | 17 |

| 3.3  | FPGA Vs. ASIC Startups                                                | 20 |

| 4.1  | MARS Experimental Embedded Platform On-Chip Architecture Organization | 28 |

| 4.2  | General and Sobel mask structure                                      | 31 |

| 4.3  | Sobel mask implementation images                                      | 32 |

| 4.4  | Measurement of task execution                                         | 33 |

| 4.5  | Sobel mask DVC symbol                                                 | 34 |

| 4.6  | Dedicated circuit accelerator for Sobel and $YC_BC_R$ computation     | 35 |

| 4.7  | Sobel mask hybrid DVC internal organization                           | 36 |

| 4.8  | Sobel mask software DVC internal organization                         | 36 |

| 4.9  | Sobel Mask DVC symbol                                                 | 39 |

| 4.10 | Example of NUI_ARDS visual display capability                         | 42 |

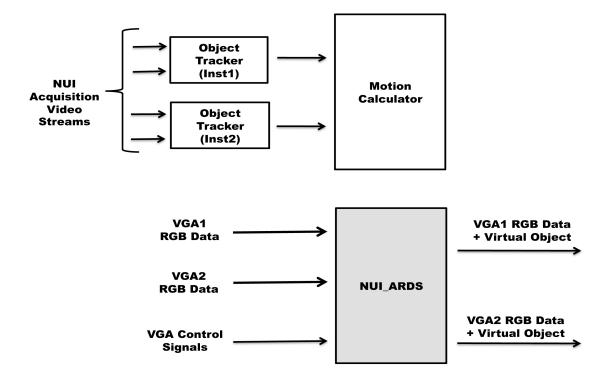

| 4.11 | Controller interface motion capture design                            | 43 |

| 4.12 | Visual display divided into grid_blocks                               | 45 |

| 4.13 | Six bit encoding scheme for (8 bit) red channel                                               | 45 |

|------|-----------------------------------------------------------------------------------------------|----|

| 4.14 | Six bit encoding scheme for (8 bit) green channel $\ldots \ldots \ldots \ldots \ldots \ldots$ | 46 |

| 4.15 | Six bit encoding scheme for (8 bit) blue channel                                              | 46 |

| 4.16 | Six bit encoding scheme for pixel transparency                                                | 47 |

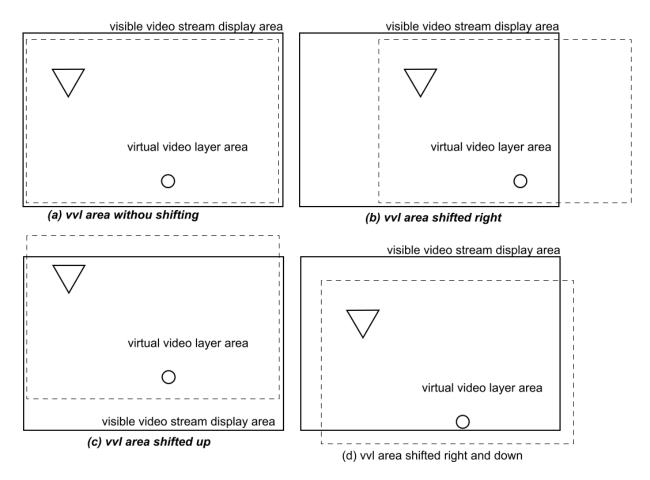

| 4.17 | Virtual video layer (vvl) shifting                                                            | 48 |

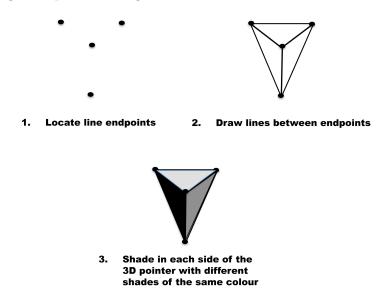

| 4.18 | Construction of virtual 3D pointer                                                            | 49 |

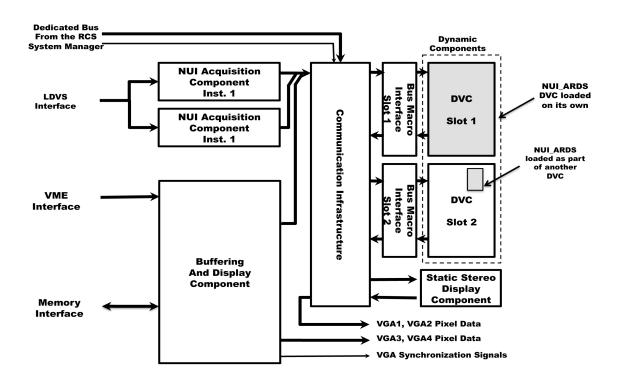

| 4.19 | MARS Platform with NUI-ARDS and RCS PRocessor                                                 | 51 |

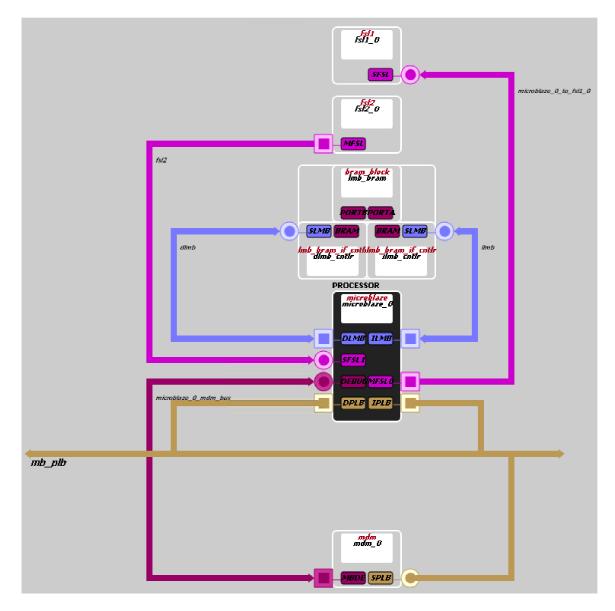

| 4.20 | NUI-ARDS as part of the RCS Processor Internal Components                                     | 52 |

| 4.21 | The NUI-ARDS DVC                                                                              | 53 |

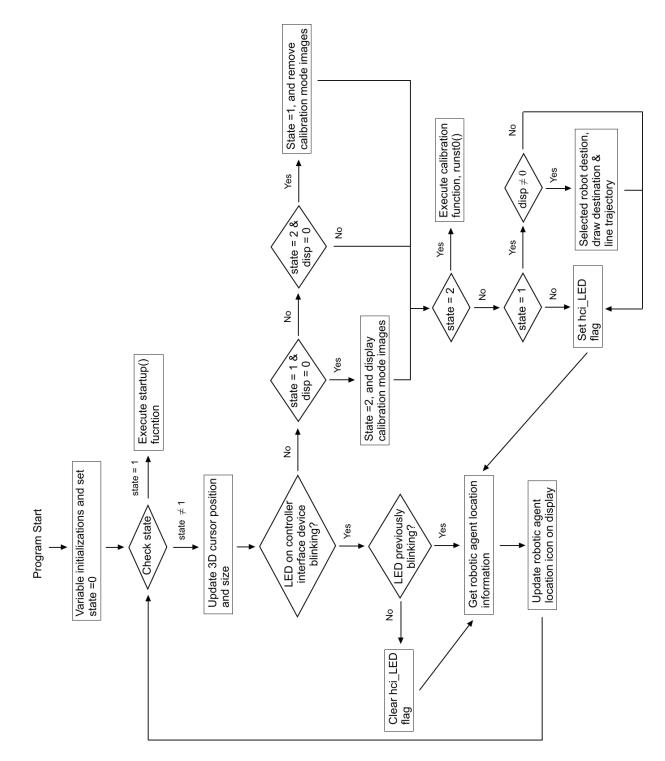

| 4.22 | Software execution flow chart for the mb1 Microblaze component $\ldots \ldots$                | 56 |

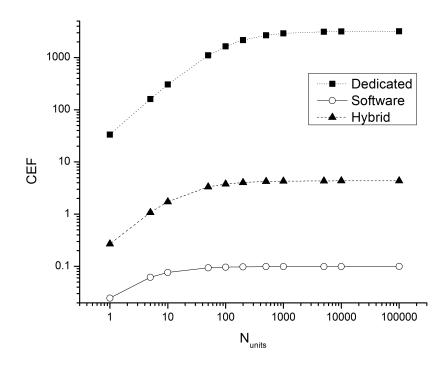

| 5.1  | CEF for Sobel mask DVCs                                                                       | 60 |

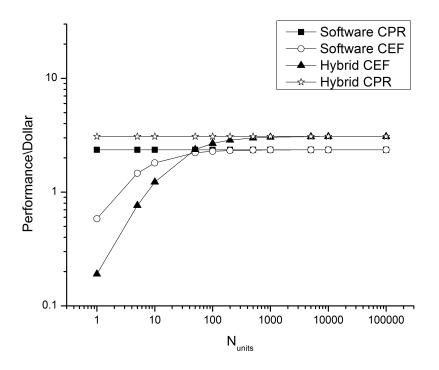

| 5.2  | CEF for $YC_BC_R$ DVCs                                                                        | 63 |

| 5.3  | CEF for $YC_BC_R$ DVCs                                                                        | 66 |

| 5.4  | CEF for $YC_BC_R$ DVCs                                                                        | 67 |

| 5.5  | A CEF and CPR comparison of Sobel DVCs                                                        | 68 |

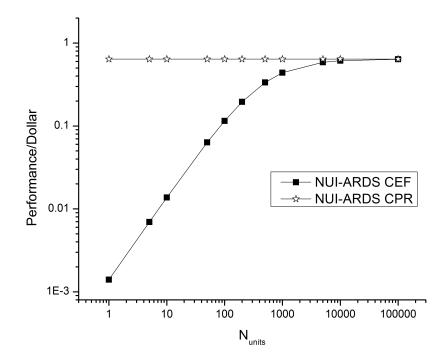

| 5.6  | A CEF and CPR comparison of a Hybrid NUI-ARDS DVC                                             | 69 |

| A.1  | Microblaze mb2 internal component organization for for Sobel mask and                         |    |

|      | $YC_BC_R$ Hybrid DVC Experiments                                                              | 74 |

| A.2  | mb2 Microblaze mb2 internal component organization for Sobel mask and                         |    |

|      | $YC_BC_R$ Software DVC Experiments                                                            | 75 |

## List of Abbreviations

**3D-SPADS** 3D Stereo-Panoramic Acquisition and Display System

ASIC Application Specific Integrated Circuit

**BRAM** Block RAM (Xilinx)

FPGA Field Programble Gate Array

${\bf CPR}\,$  Cost-Performance Ratio

**CEF** Cost Efficiency Factor

${\bf CLB}\,$  Configurable logic block

${\bf CPU}$  Central processing unit

**DPRCS** Dynamic Partially Reconfigurable Computing System

DRCA Dynamic reconfigurable Computing system

**DVC** Dynamic Virtual Component

${\bf FPS}\,$  Frames per second

HW Hardware

$\mathbf{I/O} ~ \mathrm{Input/Output}$

**LED** Light Emitting Diode

LUT Look-up table

${f MB}$  Megabyte

**NUI-ARDS** Natural User Interface Augmented Reality Display System

${\bf SoC}\,$  System on chip

**VHDL** Very-high-Speed-integrated-circuit hardware description language

$\mathbf{VVL}$  virtual video layers

**XVGA** Extended Video Graphics Array

## **1** Thesis Introduction

#### **1.1** Motivation Statement

The motivation behind this thesis is to provide the embedded reconfigurable engineering community with an approach that will help guide hardware design engineers in determining the correct and most appropriate computing architecture design for a particular reconfigurable region allocated for a specific application in a Dynamic Partially Reconfigurable Computing System(DPRCS). Currently the most widely explored approaches involve the use of performance [1], power [2], area [3], and resources [4] for analysis of various computing systems. These types of analyses are useful when trying to develop a computing system that has strict performance requirements, low power, less chip space allocation and use particular resources more than others on chip. These constraint based analyses are useful when a computing system is being designed to meet particular constraint needs. However, in practice, during the design stage there are other factors such as number of units to be deployed and development costs. In the early years of FPGAs reconfigurable resources available on chip for a particular design may have been limited and, therefore, resource constraint analyses were useful to fit the design on the chip. Today, FPGA chips such as Xilinx's Virtex 7 are huge in terms of configurable resources [5]; therefore, the limitation of not having enough resources or space is less of an issue. Also, the same VHDL architecture design on a newer FPGA may take up less power due to advancements in manufacturing technology that reduces static and dynamic power and increases performance [6]. These constraints become less critical as new design factors appear. Also, there are situations where the constraint variable is not strict and instead of having a specific constraint value there is a range for the constraint. Let's assume we are to design a computing architecture for a configurable region on an FPGA. Now let us suppose there are three types of architectures considered for production. Each of the three designs have varying degree of performance, power, resources, and area but all of them are within the specified constraint range. Presented with this situation how does a design engineer select the most appropriate architecture for the given task? The design engineer may use his previous experience or intuition regarding each computing architecture option (qualitative analysis) and select one for production. However, this approach has a few drawbacks. It assumes the engineer has lots of experience behind him but he would not have the quantitative analysis to support his decision. To avoid this situation and provide a quantitative analysis to support more subjective qualitative analysis, some form of analytic mechanism needs to be introduced. A quantitative analysis previously introduced as a solution to this problem is the cost performance ratio (CPR). This CPR analysis takes into consideration the performance and cost of the system and is currently used to arrive at a decision. However, this earlier CPR analysis is based on the assumption that development costs are relatively small because large numbers of units will be produced. This assumption does limit its use for the design of Dynamic Virctual Components (DVCs) for partially reconfigurable systems because only a few DVCs may be deployed and more of the resources are directed to the development cost of a DVC; therefore, a design engineer should also take into account development cost and the number of units to be produced. For this reason a more refined version of the CPR is proposed to address the quantity and development costs in the cost efficiency analysis of a DVC.

### 1.2 Objectives

In order to address our motivation and achieve the goal of proposing a valid mechanism to determine the cost efficiency of a DVC the following steps need to be taken:

- 1. Research & analyze currently available methods that may be applicable for the efficiency analysis of partial reconfigurable systems.

- 2. Propose an alternative approach based on the concept of a Cost-Efficiency Factor (CEF).

- 3. Test the proposed approach by implementation of dedicated hardware components, hybrid components and software based components.

- 4. Analyze the results from the two test experiments.

- 5. Implement the proposed approach during the computing architecture design phase of an industry specific application involving live 3D stereo panoramic video streaming with a remote robotic control system.

- 6. Identify any foreseeable limitations or future improvements to the proposed approach as observed during test experiments and specific industry application implementation.

### **1.3** Original Contributions

The contributed research work to the objectives stated previously are:

- 1. Analysis of currently available methods.

- 2. Concept and approach of using a CEF as the mechanism of determining the correct computing architecture design for a particular application for dynamic partially reconfigurable computing systems.

- 3. Software and Hybrid computing architecture implementation for two test applications.

- 4. Computing Architecture design and Implementation of the Natural User Interface Augmented Reality Display System (NUI-ARDS).

- 5. Experimental results and discussion of computing architecture design using a CEF approach.

#### 1.4 Thesis Organization

The remaining organization of this thesis is as follows:

- 1. Chapter 2 is dedicated to the collection and analysis of current related work in the field and to highlight the need for the proposed approach.

- 2. Chapter 3 proposes the concept of using a Cost-Efficiency Factor (CEF). It will discuss how this CEF can be used in determining the correct computing architecture design of a given programmable logic given that a dynamic partially reconfigurable computing system is to be used.

- 3. In chapter 4, two experimental test will be examined and the results presented. The CEF for a complex design and implementation of an industrial application involving 3D stereo panoramic video streaming with augmented reality and remote robotic agent control system is determined.

- 4. Chapter 5 discusses the results and the implications CEF can have in the design of dynamic partially reconfigurable computing systems.

## 2 Related Works

#### 2.1 Introduction

Over the years embedded digital systems development has become more prominent as devices become smaller in size and specialized in function. To date embedded systems have become an integral part of every computer systems; however, the engineering design aspect of computer systems still remains to be fully explored. This chapter will overview the current available approaches for the design of embedded partially reconfigurable systems.

#### 2.2 Related Work Observation & Analysis

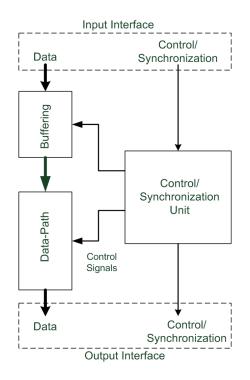

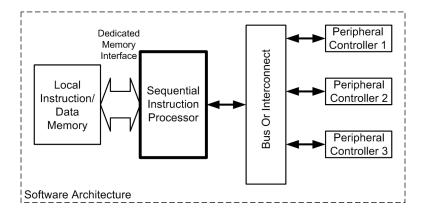

Computer systems are commonly categorized into one of the following three main computing architecture: Dedicated, Software, or Hybrid computing systems. Dedicated computing architectures generally consists of dedicated hardware that is specifically designed for a particular task and does not contain any sequential processing elements such as a microprocessor. A diagram for the general organization of a dedicated computing architecture is depicted in Figure 2.1. In this type of computing architecture there exists only inputs and outputs, data paths, and control units for data synchronization. Dedicated computer architectures are usually suited for computational intensive tasks. On the other hand, a CPU-based computing architecture, the cheapest and most general purpose architecture to utilize, may not be optimized for the intended task. This type of computing architecture, depicted in Figure 2.2, contains a sequential processing element such as a microprocessor and no dedicated hardware components. This CPU-based computing architectures are suitable

Figure 2.1: Diagram of a general dedicated computing architecture [7]

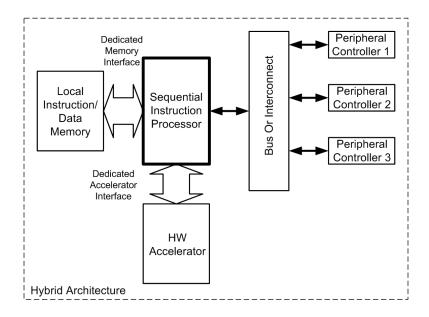

for algorithmic intensive or are very sequential by nature tasks. A hybrid computing architecture, depicted in Figure 2.3, tries to take advantage of both worlds by containing both a sequential processing element (sequential instruction processor) and a dedicated hardware (HW accelerator). A communication infrastructure is then used to exchange data between both systems. In order to take advantage of all three computing architectures one can use

Figure 2.2: Diagram of a general software computing architecture [7]

Figure 2.3: Diagram of a general hybrid computing architecture [7]

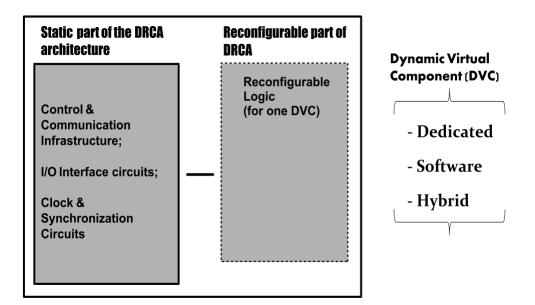

a dynamic reconfigurable computing architecture (DRCA) depicted in Figure 2.4. This type of computing architecture usually consists of two sections: a static section and a dynamic (Reconfigurable) section. The static section usually consists of a microprocessor and the dynamic section consists of reconfigurable logic which can be reconfigured by the microprocessor whenever a different architecture(dedicated, software or hybrid) is needed for a given task. For example, this approach is effective for small dynamic sections in which the time in between tasks is greater than the reconfiguration time. The reconfiguration time is the time it takes for the programmable logic area to be reconfigured with another computing architecture.

Figure 2.4: Diagram of a DRCA

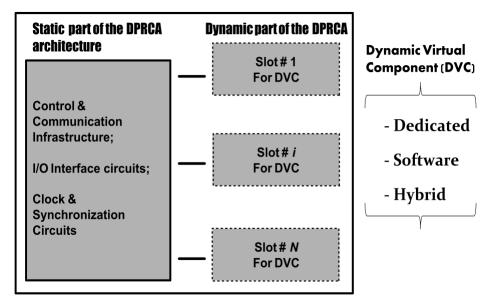

A potential problem may arise when other tasks are required to continue executing while at the same time another programmable computing architecture is needed for a new task execution. In this situation a Dynamic Partially Reconfigurable Computing Architecture(DPRCA), depicted in Figure 2.5, has been proposed as a possible solution. A DPRCA

Figure 2.5: General diagram of a DPRCA

[8, 9] is similar to a DRCA except that the programmable logic section of DPRCA consists of

multiple slots. Each slot can be reconfigured with any Dynamic Virtual Component(DVC) which can be either a Dedicated, Software, or Hybrid computing architecture design. One advantage of a DPRCA is that the hardware can adapt depending on the task at hand. Traditionally, a task is usually constructed or adapted to fit a particular computing architecture but in a DPRCA one can think of adapting the computing architecture to fit the task instead, which is achieved by loading reconfigurable slots with a specific DVC depending on the task that needs to be performed. However, in order to adapt the computing architecture to the given task one must have a way to determine which computing architecture type is to be implemented in a DVC for a particular task, the main focus of this thesis. Previous related work done in this area revolves around the idea of simulating computer architecture performance, effectively mapping a given task onto whatever processing elements are available or how to create effective architectures for a particular task. In [10] and [11] the emphasis is on computer architecture modeling of hybrid architectures so that one can determine if a hybrid architecture is suitable for the task. However, the results are very related to how well the simulators are built. Even well built simulators have flaws, such as the inability to consider new technology resources, the assumption that all resources available are the same and unlimited, and that all solutions are possible to develop in terms of cost. To build a simulator one must have a particular method to solve the problem, however, to our knowledge, there is no method or simulators capable of making the decision as to which computing architecture should be implemented in a DVC given a particular task. Much work has also been done in using algorithms for finding optimum hardware software partitioning methods to address constraints such as configuration area, configuration blocks (CLBs), available resources, and power consumption. In [12] a Particle Swarm Optimization inspired approach is used to find a range of valid hardware-software partitioning solutions. However, a method for selecting which of the implementations should actually be used in a DVC design for a particular task is not provided. Other works such as [13] try to find ways in which to effectively schedule tasks between dedicated hardware and software architectures in order to improve efficiency in terms of performance and area. This would result in having many possible solutions but not in providing a quantitative analysis to help decide as to which computing architecture should be implemented into the DVC. From a hardware computing architecture point of view there has been work done such as [14] and [15] that show the benefits and limitations of both heterogeneous and homogeneous computing systems. In [14] the system cost is discussed in terms of the cost of the processors selected and the links between them but a DVC could also potentially be a dedicated or hybrid architecture. [15] Looks at how heterogeneous architectures can provide a more linear performance increase when compared to homogeneous architectures under certain task conditions by having more optimized processing components (such as multipliers, LUTs, Dividers, etc) catered towards specific functions. This however would also lead to multiple architecture solutions for a DVC but without being able to know which of them should actually be implemented as a DVC. However, all the preceding approaches are constraint driven. On the other hand there is a need to have an evaluation based on a cost-efficiency of the system. There are few works [16, 17, 18, 19] which consider ratio between performance and cost; however, these works focused on mass production, thus the number of units as well as the cost of research and development plus the cost of design were implicitly embedded in the cost of each unit, and this is not explicitly analyzed.

### 2.3 Summary

In summary, there has been much work done as to how to design proper dedicated, software and hybrid architectures. Many techniques have been developed to properly construct computing architectures and the advantages and disadvantages of each architecture has been explored. However, there has not been any method or technique, to our knowledge, that will aid in the selection of the correct computing architecture to be implemented into a DVC given multiple possible solutions which meet all task requirements.

# 3 Proposed Approach to Evaluate the Cost Effectiveness of a DVC

#### 3.1 Introduction

Given all the previous research work done into how to design proper dedicated, software, and hybrid computing architectures our approach will focus on how to determine the correct computing architecture implementation for a DVC given a particular task to perform. This decision will require certain efficiency measurement mechanism and in this work the use of a CEF is proposed as such mechanism. It will be explained in detail in this chapter and used as a mean to arrive at a decision for a FPGA-based computer architecture. Before proposing our approach, we first analyze and discuss the various factors that affect the cost of a given on-chip computing architecture.

#### **3.2** Concepts and Theory Analysis

When hardware design engineers build computing architectures many factors that affect the cost of a computing architecture are considered. In most published literature in the field, the term "cost" for the FPGA-based SoC usually refers to how many configurable logic blocks or how much area, power, or memory is required for a particular computing architecture [20]. For the purpose of this thesis the cost of a particular DVC architecture will refer to the monetary quantity required to produce the DVC.

In general, determining the cost of an entire computing architecture can be very complex and may change over time. However, as we will show in this study, it is a critical aspect to consider when designing a DVC. There are many trends and factors that are well known to affect the design of a computing architecture and they may be associated with manufacturing technology, quantity of production, market target and development costs [21]. The manufacturing of a specific computing architecture (e.g. ASIC) decreases as time passes because the manufacturing techniques improve over time which leads to a higher yield. Yield is the number of computing architecture components that pass the testing stage. For integrated circuits, the manufacturing cost consists of many variable costs such as the cost of die, testing die, die yield, cost of packaging, etc. Without going into copious details regarding integrated circuit costs, it is important to note that die size and yield have an important effect on its cost. The more die area required by the computing architecture leads to an increase in the cost of the integrated circuit. This is important to take into account if there are various DVC candidates that require different die areas. Manufacturing affects cost because it is always evolving over time. Improvements in the manufacturing process over the years contributes to cost reduction as die yield improves and contributes to the reduction of die cost which designers don't have control over. Both of these cost reductions translate into a reduced integrate circuit cost which is important, particularly if there are multiple competitors.

When manufacturing any type of integrated chip there is usually the question of quantity. Determining how many chips are to be manufactured with a given computing architecture is important when considering costs. The three major common computing design markets are: low cost design, cost-performance design and high-performance design market areas [21]. In each design area the design objective is different. In a low cost design market the goal of the computing architecture design is to arrive at the least cost solution for the computing architecture with performance being acceptable and not a priority in the decision process. Usually, in a low cost design market the demand for the computing architecture is high hence large quantity orders are expected. In a cost-performance computing architecture market the goal is to design a computing architecture which is neither cheap nor expensive but rather has the best performance for its cost. For the high-performance design market the computing architecture goal is purely performance driven and the cost is not a primary concern, usually these types of computing architectures are not produced in large numbers due to the large cost associated with them. The key concept to understand here is that the relationship between price and quantity can get intricate.

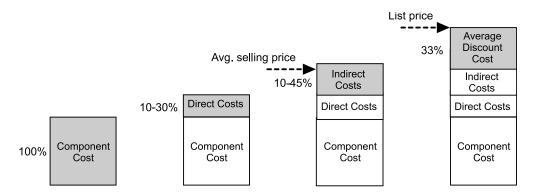

We will now discuss some important cost implications for a product containing an onchip computing architecture design. Two main cost categories that affect the development of a computing architecture product are direct and indirect costs. Direct costs are directly associated with the making of a product and are usually 10% to 30% of component costs [21]. Direct component cost refers to the raw components available for production which do not need to be acquired externally from the company through purchase. Some examples of direct costs are: purchasing of components(which are not internally available), labour, and warranty. Indirect costs result from the architecture design and cannot be associated to the production of a single product. Examples of indirect costs are: research and development (R&D), manufacturing equipment maintenance, marketing, building rental, cost of financing and sales. Figure 3.1 shows how the cost of a product evolves in each step of its production. Indirect costs range usually from 10% to 45% of the average selling price [21]. The average selling price of the product is defined as the summation of components costs, direct costs and indirect costs. On top of all these costs it is possible to add an additional average discount cost resulting in the list price of the product. The list price is the price most likely seen by consumers and includes costs if the product is to be sold at a discount price. In markets where there is high competition the list price may not exist and to further compete companies have the option of reducing direct, indirect and component costs. Since at every production stage the preceding cost affects the subsequent costs it is very crucial to select the appropriate computing architecture in order to gain a cost advantage over a rival competitor in a costperformance or low-performance design market. These cost implications also highlight the need of having some form of quantitative mechanism that will help design engineers to determine the correct computing architecture approach with some form of computational or logical analysis to support their decision instead of relying solely on past experiences and intuition (qualitative analysis).

Figure 3.1: The cost component of a computing device as the price evolves with the addition of direct and indirect cost [21].

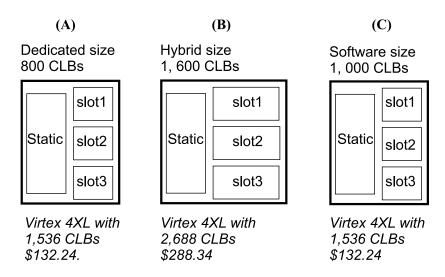

After discussing the many factors that may affect the production of computing architecture we will specifically identify and discuss those factors that are applicable in the decision process for the development of a DVC. Firstly, since a DVC is to be loaded into a slot located in a DPRCS the cost of the integrated circuit for a particular DVC can be considered as part of the overall cost (both static and dynamic sections of the DPRCS) of the integrated circuit that would house the entire DPRCS. This means that the integrated circuit design cost may be affected by the DVC architecture. If a DPRCS is to be used for a particular application with three possible DVC variations (Dedicated, software, or hybrid) and each requiring a different size of integrated circuit area resulting in three DPRCS variations with different integrated circuit area needs. Figure 3.2 illustrates such a situation when a Field-Programmable Gate Array (FPGA) logic device is used for implementation. In Figure 3.2B the Hybrid variant of the DPRCS requires 1600 configurable logic blocks(CLBs) which requires a larger and more costly FPGA chip than the dedicated and software DVC architectures in Figure 3.2A and Figure 3.2C, both of which can fit on a smaller sized FPGA chip.

Figure 3.2: DPRCS with different sized slots and DVC

This observation suggests that any method used in determining the nature of a DVC must take into account the integrated circuit cost of the static and dynamic area of the DPRCS in which the DVC will be placed in. When dealing with FPGA's as the reconfigurable platform the integrated circuit cost of the DPRCS can be considered as the cost incurred by the resources required by the static and dynamic area. The incurred resources can be viewed as fine grain such as LUTs, flip flops, and gates or viewed as course grain such as divider, adders, and multipliers. For the purpose of this study we will simplify the resources to the amount of CLBs required by both the static and the dynamic sections. The cost of each section is proportional to the platform cost (an FPGA in this case) where the fraction is the percentage of CLB's used by each section. In equation 3.1, SSC represents the cost of the static section of the DPRCS,  $SS_R$  represents the resource count (CLB count) required by the dynamic section. The term  $T_R$  represents the total resource count available in the reconfigurable platform and RPC refers to the reconfigurable platform cost which is the cost of the FPGA chip in this case. In equation 3.2, DSC refers to the cost of the dynamic section of the DPRCS and  $DS_R$  refers to the resource count required by the dynamic section which in our case is the resource count required by the DVC.

$$SSC = \frac{SS_R}{T_R} \times RPC \tag{3.1}$$

$$DSC = \frac{DS_R}{T_R} \times RPC \tag{3.2}$$

The second direct cost required by DVC are its labour development cost. Depending on which architecture is deployed different knowledge and expertise with different cost values is required. For example, if the choice was made that a particular DVC is to be deployed using a dedicated hardware then one must employ skilled labour with hardware knowledge. However, if the DVC is to be deployed on a software based DVC then one can simply acquire skilled labour with software programming knowledge. Table 3.1 shows how different engineering skill set levels may vary in cost, having an effect on labour cost which is an important factor in the development of a computing architectures. Table 3.1 is the average Canadian labour cost for electrical, computer, and software engineers for 2010 obtained from Living In Canada [7] data. Since these labour skills have different labour cost any methodology that will help determine the nature of the DVC to be produced should probably take into consideration this variable.

| Table 3.1: Engineering Avg. Wage per Hour (Toronto) |                   |                   |  |

|-----------------------------------------------------|-------------------|-------------------|--|

| Electrical Engineer                                 | Software Engineer | Computer Engineer |  |

| \$34.53                                             | \$36.60           | \$31.78           |  |

A third factor that may influence the nature of the DVC is its market area. If the DVC is to be used in thousands of units rather than just tens of units then perhaps a higher DVC cost may or may not be worth it in some cases. Therefore the number of units to be produced will have to be considered in some way as well.

After discussing some costs related to embedded digital systems we will look at how these costs influence architecture design decisions. Currently when designing reconfigurable systems designers have three main general architecture design approaches to choose from. One design approach may consist of using an Application Specific Integrated Chip (ASIC), another option is to use a Field programmable Gate Array (FPGA), and lastly a Microprocessor could be used as well. In order to compare the three types of implementation solutions and select the most appropriate one, development designers commonly use a cost-performance ratio (CPR) for comparison. This CPR is calculated using Equation 3.3.

Cost-Performance Ratio (CPR) =

$$\frac{\text{Performance}}{\text{Cost}}$$

(3.3)

Where CPR is equal to the performance metric of the computing architecture divided by

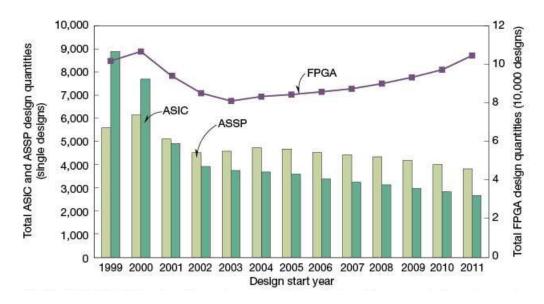

its price [22]. Simply using the CPR computing systems with an FPGA approach can be seen as inefficient. ASIC based computing systems give higher performance over FPGAs, have lower power consumption, and are less expensive compared to FPGA chips that can cost more than \$1,000. Therefore when the performance of a microprocessor architecture is not enough the CPR clearly indicates that an ASIC design is a better design solution because of its superior performance gains and price per chip compared to its FPGA counterpart. However, in reality this appears not to be the case and the industry shows quite a different picture. FPGAs architecture designs today are vast and FPGA manufacturers like Xilix and Altera continue to produce and sell millions of FPGAs chips yearly. Figure 3.3 shows how FPGA designs over the resent years and into the future will continue to rise while ASIC designs continue to fall. If the CPR as it is used currently is correct then there should have been an increase in ASIC designs and a steady fall in FPGA instead. This contradiction implies we must take a look and reassess the way in which the CPR is used for the design of computing architectures.

Figure 3.3: FPGA Vs. ASIC Startups [23]

Today, embedded systems can be found in many markets such as consumer electronics, aviation and aerospace, medicine, machinery and other custom electronics. Furthermore, the computing designs in these areas are multi-functional. In the past, it was fairly common to find an electronic device designed for a single function. Today, electronic devices are increasingly becoming multi-functional and at the same time they must continue to be reliable, low power, low cost and fast enough to perform all the functions required. One example of such a device is mobile phones. They are not just used to make phone calls but also for taking pictures, editing documents, listening to music, watching video, and sending or receiving data using multiple wireless standards. Cell phones are a good example of a consumer market electronic where the production of units is very large. However, the design market for consumer electronics is just a small part of the overall embedded systems market and the number of units produced or manufactured in other sectors range from a hundred units to just tens of unit only. This means that systems are now being designed to be multi-functional and limited units being produced. For this reason many designs requiring multiple functions and limit units to be produced have turned to FPGAs. FPGAs provide the reconfigurable ability to allow the computing architecture to be multi-functional without the need to have large ASIC development costs or long development cycles for limited production.

Over the last few years, FPGA configurable logic gates have gone from a few millions to hundreds of million. The large size FPGAs allows embedded reconfigurable design engineers to develop a System on Chip (SoC) on a single FPGA. Although larger FPGAs provide the ability to have a SoC on a large FPGA changes or modifications to the design result in large compilation times and larger configuration bit streams. For this reason partial reconfigurable systems have become a viable solution to this problem. This is because the particular component (which we address in this study as a DVC) of the design that needs to be changed or modified can be recompiled with the three common architectures discussed earlier. Although this solution leads to lower compilation times and smaller bit streams it presents a question as to how a designer would now select the proper computing architecture for a particular DVC given that they have three main options to choose from. At first glance it appears that the CPR could help in this decision making. However, the current CPR already fails in explaining why configurable computing systems have become more abundant in the industry and perhaps the CPR should be modified in order to more accurately address and explain the current architectural design issue faced by engineers when determining the computing architecture of a DVC in partially reconfigurable computing systems. The biggest disconnect between how the CPR is obtained and the development of DVC is that CPR does not explicitly take into account the number of units to be produced. When designers use CPR most inherently assume that the number of units to be produced is extremely high; however, as we explained before, that is only the case for the consumer market but not for the entire engineering marker as a whole. Therefore, by using the CPR as it is currently used for partially reconfigurable computing systems we are incorrectly assuming that the DVC to be designed will be deployed in thousands of units when in reality the DVC might only be deployed in tens of custom units. We also have to acknowledge that since the quantity of computing architectures can be few, we must take into account the development cost portion of direct cost which can substantially affect the final cost of a computing system. Unfortunately the CPR fails to address the development cost because of its inherit assumption that development cost becomes insignificant by the fact that millions of units are to be produced. To address these two main issues, we propose a modification to the way the CPR is calculated by making sure that development cost and quantity of computing units to be sold are taken into consideration when determining the correct computing architecture of a DVC. Lastly the design of a DVC must also take into consideration the cost of reconfigurable resources required by the DVC since the price of an FPGA chip increases with size.

Taking into consideration all the aspects that affect the cost of a computing architecture and examining how the design of DPRCS has evolved we propose the use of a Cost-Efficiency Factor (CEF), Equation 3.4, to help guide the decision process as to whether a particular DVC should be implemented as a dedicated , software, or hybrid computing architecture. As one can see in Equation 3.4 the CEF, unlike the CPR, takes into account the number of DVC units to be produced and their development cost. The cost of the reconfigurable resources required, and the performance obtained from the computing architecture solution are the same as in Equation 3.

$$CEF(A_i) = \frac{P(A_i)}{UC + \frac{DC(A_i)}{N_{units}}}$$

(3.4)

Where:

$A_i =$ Architecture  $A_i$

$CEF(A_i) =$ Cost Efficiency Factor of Architecture  $A_i$

$P(A_i) =$ Performance of Architecture  $A_i$

$DC(A_i) = DT(A_i) \times AC(A_i)$  = Development cost of Architecture  $A_i$

$DT(A_i)$  = Development Time for Architecture  $A_i$

$AC(A_i) =$  Average Development Cost for Architecture  $A_i$

$N_{units} =$  Number of units to be produced

UC =Unit Cost: SSC + DSC +manufacturing + etc

The Unit Cost term, UC, consists of the platform cost (static + dynamic) and indirect costs such as manufacturing, packaging, etc. The  $P(A_i)$  term is the desired performance metric result for the proposed DVC architecture. For example, in a video application the  $P(A_i)$  variable can be frames per second(fps) or bits per second(bps) in a data execution. The Development Cost term,  $DC(A_i)$ , is calculated based on the number of hours needed to develop the architecture ( $DT(A_i)$ ) and the average national wage for such particular work  $AC(A_i)$ . The average national wage may or may not be the same for all possible architecture solutions and varies depending on location. Lastly the  $N_{units}$  term represents the total number of computing units anticipated for production. This term is important because it is important to notice that a particular DVC may or may not be used in millions of of DPRCS instead it may just be used in tens of units. Since the quantity of DPRCS with the specified DVC unit to be produced has an effect on costs and varies depending on application one cannot eliminate the  $N_{units}$  term. Assuming the DVC will be used in millions of units would be incorrect since it is not always the case, especially in areas concerning R&D or specialized custom systems where production is few.

The units for the CEF factor is always performance metric per dollar. Therefore, if we are designing a system for video processing then one performance metric could be frames per second (FPS), then the CEF would be FPS per dollar. With this information the designer can see how much performance metric is attained per every dollar that is put into developing the architecture. The higher the CEF value the more cost effective the design is since one is getting a higher performance value per every dollar spent on developing the

design. This type of computing architecture analysis can be beneficial in the design of a DVC architecture tailored towards the cost-efficiency computing market or application such as multitasking smart-phones, and high performance video streaming. It is important to note that performance metric calculations and analysis for a given computing architecture may differ from one application to another application; therefore, during the CEF analysis one must decide on one particular performance metric. For example, if the performance metric for the dedicated DVC is FPS then the performance metric for the software and hybrid DVCs should also be FPS.

Although there may be many ways to analyze and measure performance there are two widely used performance metrics which are execution time and throughput. Execution time is the time elapsed from the start of the task to the end of the task. Execution time includes everything the computing system needs to do to accomplish the task such as memory access, I/O bus service routines and Operating System (OS) overheads. Throughput is the amount of work done within a specified time. One way to increase throughput is to reduce the task execution time but one can also take advantage of parallelism in tasks as well. For the purpose of determining the CEF in this study, we analyze performance in terms of execution time.

In order to determine what kind of an impact our proposed CEF approach may have on the architecture design decision of a DVC we need to consider multiple experiments that: 1) Contain commonly used architecture features such as architectures that are mostly stream based where data is mostly coming in, processed and sent out quickly without the need to store large amounts of data; and, 2) Architectures that are memory centric in which data that is being processed and its results need to be stored in memory. For this reason we designed three experiments that will help us to see how useful the CEF can be in the design of DVC architectures.

The first experiment involves RGB to  $YC_BC_R$  colour conversion which is a more of a streaming application since the RGB colours are convert to  $YC_BC_R$  colours and do not have to be necessarily stored. The second experiment deals with Sobel mask computation for the purpose edge detection techniques. This experiment is more memory centric because the inputs and outputs to the Sobel mask calculations need to be stored so that they can be further processed. The third experiment is more complex and incorporates both streaming and memory centric features of the first two experiments.

#### 3.2.1 Summary

By using equation 3.4 along with performance requirements and costs we will demonstrate how a CEF value can be used to correctly select the proper DVC computing architecture for a particular application for development in situations where cost-performance is of importance without ignoring the development costs and without the assumption that production will always be extremely high. In this study, we evaluate the use of a CEF on three experimental implementations: RGB to YCBCR colour conversion, Sobel Mask computations and a natural user interface with augmented reality display system(NUI-ARDS). The detailed experimental procedure and observations for these experiments are described in the following chapter 4.

# 4 Approach Using Experimental Applications

## 4.1 Introduction

In this thesis we use three video processing applications as mentioned in chapter 3 to demonstrate how the CEF can help guide a design engineer or an automatic tool select the most appropriate computing architectural structure of a DVC to be developed. The applications used for this study are in the area of edge detection, colour conversions, and augmented reality. We will look at all three applications and evaluate the usefulness of a CEF when designing a DVC for a DPRCS hardware platform. The following is a list of experiments selected to examine our proposed use of a CEF for determining the architectural nature of a DVC which were introduced in chapter 3:

- 1. Sobel Mask Computation

- 2. RGB to YCBCR Colour Conversion

- 3. Natural User Interface with Augmented Reality (NUI-ARDS)

The reason these three experiments were chosen was that they deal with streaming and memory centric architecture applications which are very commonly found in computing designs and, therefore, will give us a good measure as to how this CEF can address the design concern of DVC in partially reconfigurable computing systems.

# 4.2 DPRS Experimental Setup

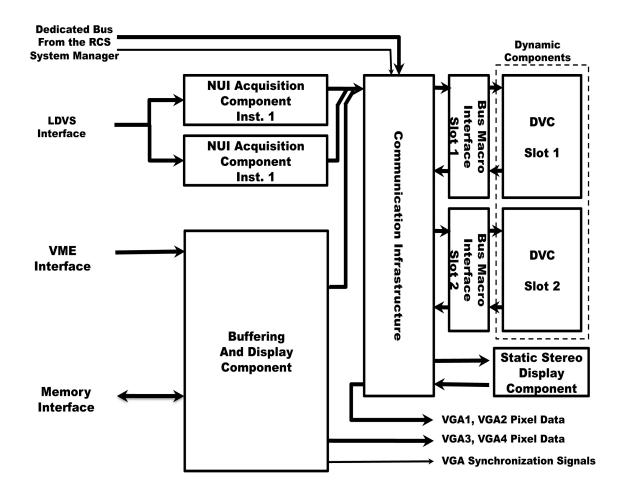

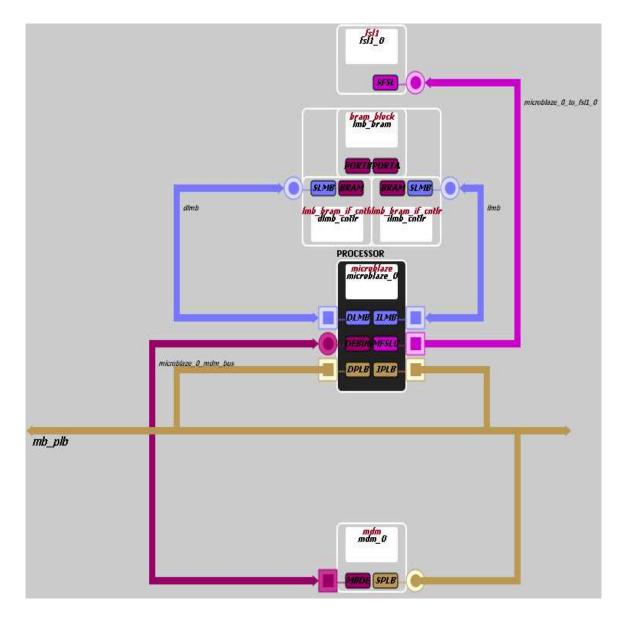

In order to perform the three listed experiments, an appropriate platform is required. For the purpose of this thesis an existing Multi-Application Reconfigurable System (MARS) platform was selected. MARS is a custom platform consisting of a Virtex 4 FPGA with a 1024 x 768 projector display, 3D stereo panoramic capture, memory for video buffering, and a stereo camera for motion tracking. The embedded DPRS inside the Virtex 4 FPGA in which the DVC would be placed is depicted in Figure 4.1.

Figure 4.1: MARS Experimental Embedded Platform On-Chip Architecture Organization

### 4.3 Data Centric Experiment Test

#### 4.3.1 Sobel Mask Computation Description

In image processing a common task performed that is computationally intensive and requires memory storage for the inputs and output results is edge detection. There are many edge detection methods and algorithms but in this particular experiment we specifically implement Sobel mask computation DVC for the purpose of an Edge detection application.

#### 4.3.2 Sobel Mask Computation Principles

Edge detection is defined as an approach for segmenting an image based on abrupt local changes and this process is explained in [24]. When performing edge detection on an image there are three main tasks to perform:

- 1. Take the image and apply some method or process to reduce noise. One example of image noise reduction is image smoothing.

- 2. Extract all possible edge points from the given image using local operations such as various masks (for example a Sobel mask).

- 3. Select and determine the true edge points from the set of points obtained in step 2.

To extract all possible edge points in an image one can take advantage of the image gradient. The strength and direction of the gradient at each pixel of an image can be determined using equation 4.1 where the gradient is denoted by  $\nabla f$ . The original image is denoted as f. The term  $g_x$  is the gradient vector component in the x-direction and the term  $g_y$  is the component of the gradient vector in the y-direction.

$$\nabla \equiv grad(f) \equiv \begin{bmatrix} g_x \\ g_y \end{bmatrix} = \begin{bmatrix} \frac{\partial f}{\partial x} \\ \frac{\partial f}{\partial y} \end{bmatrix}$$

(4.1)

In order to calculate the partial derivatives to obtain the gradient of an image one can use Sobel partial derivatives using Equations 4.2 and 4.3. Where the variables  $Z_1$  to  $Z_9$ represent the colour(red, blue, or green) values for the image pixels under the Sobel mask as depicted in figure 4.3.

$$g_x = \frac{\partial f}{\partial x} = (z_7 + 2z_8 + z_9) - (z_1 + 2z_2 + z_3)$$

(4.2)

(4.3)

#### 4.3.3 Sobel Mask Experimental Implementation

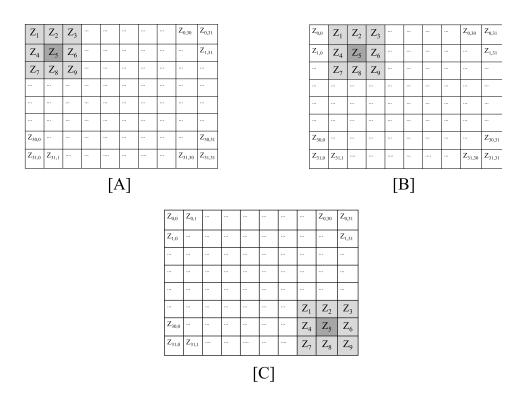

In our experimental setup, we use a Sobel mask to obtain the partial derivatives of an image that is of 32x32 pixels in size. The Sobel equations 4.2 and 4.3 used for partial derivatives are implemented using a mask as depicted in Figure 4.2(A). The variables  $M_{0,0}$  to  $M_{2,2}$  represent the value for each element in a mask, thus different masks have different element values.

The Sobel mask in Figure 4.2(B) was applied on the image to get the gradient in the x-direction,  $g_x$ . The mask is implemented by aligning the mask starting at the top left corner of the image and sliding it along the image with each pixel of the image centred under the mask centre element. At each pixel the partial derivative is calculated using the mask. since the image pixel has to be centred under the mask the gradient for the first and last row, and the first and last columns cannot be calculated. Figure 4.3 illustrates how this calculation process was performed. In Figure 4.3, (A) shows the starting pixel position in the image, (B) shows how the mask is shifted and centered for the next pixel in the image and (C) shows the last pixel position in the image from which the gradient can be calculated using the Sobel mask.

| M <sub>0,0</sub> | <b>M</b> <sub>0,1</sub> | $\mathbf{M}_{0,2}$ | -1    | -2  | -1 |

|------------------|-------------------------|--------------------|-------|-----|----|

| M <sub>1,0</sub> | M <sub>1,1</sub>        | M <sub>1,2</sub>   | <br>0 | 0   | 0  |

| M <sub>2,0</sub> | M <sub>2,1</sub>        | M <sub>2,2</sub>   | 1     | 2   | 1  |

| [A]              |                         |                    |       | [B] |    |

Figure 4.2: [A]General 3x3 mask structure [B]Sobel Mask

The gradient for pixels along the first and last rows, and for pixels along the first and last columns can not be computed because the mask cannot be centred on these pixels which results in the final image being two rows and two columns smaller than the original image. For the purpose of this experiment a random set of values were used for pixel image values.

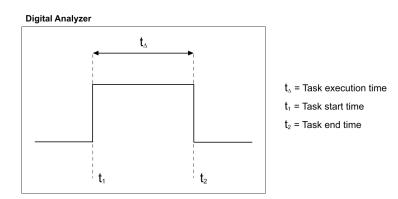

In order to determine performance we used a system cpu time approach because it pro-

Figure 4.3: Sequence of images depicting implementation of Sobel mask on a 32x332 pixel image

vided the best comparable measurements between the three types of systems. Each DVC asserts a signal to indicate the start of the gradient computation and deasserts the signal when the gradient computation has been completed. The start and end signal of the gradient task were captured using a digital analyzer connected to an output pin on the MARS platform. The execution time for the task was taken to be the time between the rise and fall of the signal as depicted in Figure 4.4. The hybrid and software DVC have no operating system overhead and all low level software is written in C to ensure that the execution time measured consisted only of system CPU time.

Figure 4.4: Measurement of task execution

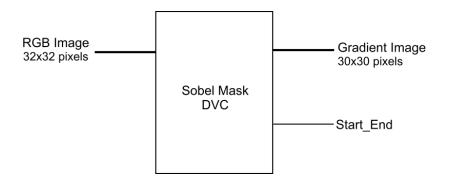

### 4.3.4 Sobel Mask DVC Symbol

Figure 4.5 show a block diagram of the Sobel Mask DVC.

### 4.3.5 Sobel Mask DVC I/O Signals

Table 4.1 explains the input and output signals of the Sobel Mask DVC.

Figure 4.5: Sobel mask DVC symbol

| Table $4.1$ : | Sobel | DVC | input | signals |

|---------------|-------|-----|-------|---------|

|---------------|-------|-----|-------|---------|

| Name      | Size         | Description          |

|-----------|--------------|----------------------|

| RGB Image | 32x32 pixels | 32x32 pixel image to |

|           |              | which the Sobel Mask |

|           |              | will be applied to.  |

Table 4.2: Sobel DVC output signals

| Name      | Size         | Description                   |

|-----------|--------------|-------------------------------|

| RGB Image | 30x30 pixels | This is a 30x30 pixel image   |

|           |              | resulting from the applied    |

|           |              | Sobel Mask computation        |

| Star_End  | 1 bit        | This signal is used to deter- |

|           |              | mine the start and end of     |

|           |              | the Sobel Mask Computa-       |

|           |              | tion on a 32x32 image         |

### 4.3.6 Sobel Mask DVC Organization

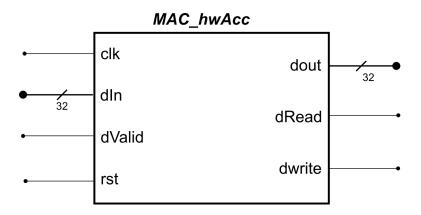

The organization of components within the dedicated Sobel Mask DVC were treated as a black box hardware accelerator. Figure 4.6 shows the dedicated computing accelerator and its interface signals. The input and output signals for the dedicated DVC are defined in tables 4.3 and 4.4.

Figure 4.6: Dedicated circuit accelerator for Sobel and  $YC_BC_R$  computation

| Name   | Size    | Description                 |

|--------|---------|-----------------------------|

| clk    | 1 bit   | Clock input signal          |

| dIn    | 32 bits | Input data for computation  |

| dValid | 1 bit   | Signals if data on dIn is   |

|        |         | valid (active high)         |

| rst    | 1 bit   | Component reset signal (ac- |

|        |         | tive high)                  |

Table 4.3: MAC\_hwacc input signals

| Table $4.4$ : | MAC_hwacc | output | signals |

|---------------|-----------|--------|---------|

|---------------|-----------|--------|---------|

| Name   | Size    | Description                                         |

|--------|---------|-----------------------------------------------------|

| dout   | 32 bits | Output data signal of com-<br>puted results         |

| dRead  | 1 bit   | Determines if dIn has be<br>latched (active high)   |

| dwrite | 1 bit   | Determines if data on dout<br>is valid (ative high) |

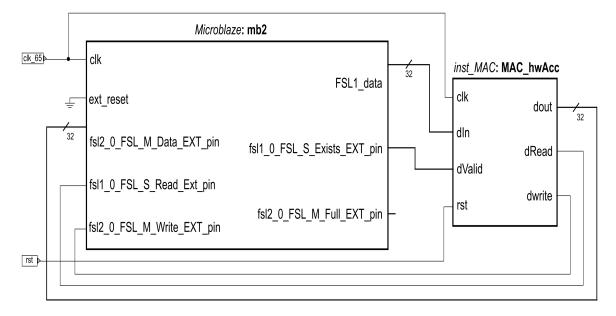

The organization of internal components for the hybrid Sobel mask DVC is depicted in Figure 4.7 and a more detailed Microblaze structure is found in appendix A.

Figure 4.7: Sobel mask hybrid DVC internal organization

The organization of internal components for the Software Sobel mask DVC is depicted in Figure 4.8 and a more detailed Microblaze structure is found in appendix A.

Figure 4.8: Sobel mask software DVC internal organization

### 4.3.7 Collected Experimental Data From Sobel Mask DVCs

Table 4.5 shows the observed experimental execution times and CEF calculation for the three types of DVC considered.

| DVC Type  | Execution Time  | Development Time | Development Cost |

|-----------|-----------------|------------------|------------------|

| Dedicated | $20.67 \ \mu s$ | 80 hr            | \$2762.40        |

| Hybrid    | $556 \ \mu s$   | 30 hr            | \$1045.32        |

| Software  | $484 \ \mu s$   | 6 hr             | \$216.60         |

Table 4.5: Sobel mask experimental data

### 4.4 Stream Based Experiment Test

### 4.4.1 RGB to $\mathbf{Y}C_BC_R$ Conversion Description

In image processing there are many colour schemes to work with and many times it is necessary to convert from one colour scheme to another depending on the application. In this experiment our goal was to determine the proper computing architecture for an RGB to  $YC_BC_R$  converter DVC.

### 4.4.2 RGB to $YC_BC_R$ Principles

Today, there are many hardware and software colour imaging systems and there are millions of colours to manage and organize in some way so that systems can exchange image data correctly. Colour images are made up of colour pixels where each pixel colour is determined by the system using a particular colour model such as the RGB(Red, Green, Blue) colour model [24]. The RGB colour model assumes that an image is composed of three distinct images; one red, one green and one blue image. When combined these three images produce the resulting RGB colour image.

In the  $YC_BC_R$  encoding model the colour image is composed of three image components: the luma, blue-difference and red difference components. The luma component, Y', carries the (Achromatic) brightness information of the image. The blue difference ( $C_B$ ) and red difference  $(C_R)$  components carry the colour information of the image. To convert an RGB image into its Y $C_BC_R$  components Equations 4.4, 4.5, and 4.6 [25] can be used for an 8 bit pixel depth digital image.

$$Y' = 16 + \frac{65.738 \times R'_D}{256} + \frac{129.057 \times G'_D}{256} + \frac{129.057 \times B'_D}{256}$$

(4.4)

$$C_B = 128 + \frac{37.945 \times R'_D}{256} - \frac{74.494 \times G'_D}{256} + \frac{112.439 * B'_D}{256}$$

(4.5)

$$C_R = 128 + \frac{112.439 \times R'_D}{256} - \frac{94.154 \times G'_D}{256} + \frac{18.285 \times B'_D}{256}$$

(4.6)

The terms  $R'_D$ ,  $G'_D$  and  $B'_D$  refer to the red, green, and blue pixel values of the image respectively.

#### 4.4.3 RGB to $YC_BC_R$ Experimental Implementation

A randomly generated 32x32 RGB matrix was initially generated. Then the matrix was converted to its  $YC_BC_R$  component values using equations 4.4, 4.5, 4.6. The execution time is taken as system time and obtained in the same manner as in section 4.3.3.

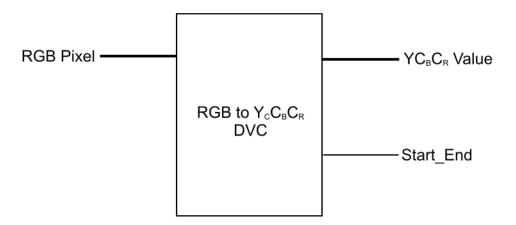

### 4.4.4 RGB to $\mathbf{Y}C_BC_R$ DVC Symbol

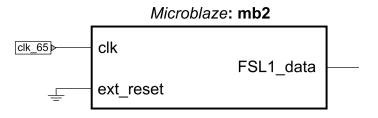

Figure 4.9 shows a block diagram of the RGB to  $YC_BC_R$  DVC.

### 4.4.5 RGB to $YC_BC_R$ DVC I/O Signals

Tables 4.6 and 4.7 explains the input and output signals of the Sobel Mask DVC.

Figure 4.9: Sobel Mask DVC symbol

### Table 4.6: Input Signals

| Name      | Size         | Description                    |

|-----------|--------------|--------------------------------|

| RGB Image | 32x32 pixels | 32x32 pixel RGB image to       |

|           |              | be convert into $YC_BC_R$ val- |

|           |              | ues                            |

Table 4.7: Output Signals

| Name            | Size         | Description                   |

|-----------------|--------------|-------------------------------|

| $YC_BC_R$ Image | 32x32 pixels | The converted 32x32 pixel     |

|                 |              | $YC_BC_R$ image.              |

| Start_End       | 1 bit        | This signal is used to deter- |

|                 |              | mine the start and end of     |

|                 |              | the RGB to $YC_BC_R$ conver-  |

|                 |              | sion task on a $32x32$ pixel  |

|                 |              | image                         |

### 4.4.6 RGB to $YC_BC_R$ DVC Organization

The organization of components within the RGB to  $YC_BC_R$  dedicated DVC was previously designed in the lab and depicted in Figure 4.6. The  $YC_BC_R$  accelerator is the same component however configured differently before sending the data for computation. For example, the accelerator is configured to expect six or three sets of values depending if the task is a Sobel or  $YC_BC_R$  operation, respectively.

The organization of internal components for the RGB to  $YC_BC_R$  hybrid DVC is depicted in Figure 4.7 with the accelerator component configured for  $YC_BC_R$  operations. Similarly, the organization of internal components for the software RGB to  $YC_BC_R$  DVC is depicted in Figure 4.8 configured for  $YC_BC_R$  operations.

### 4.4.7 Collected Experimental Data from RGB to $YC_BC_R$ DVCs

Table 4.8 shows the observed experimental execution times, development time and development cost for the three types of DVCs considered for the RGB to  $YC_BC_R$  task.

| DVC Type  | Execution Time         | Development Time | Development Cost |

|-----------|------------------------|------------------|------------------|

| Dedicated | $21.66~\mu \mathrm{s}$ | 40 hr            | \$1381.20        |

| Hybrid    | $800 \ \mu s$          | 30 hr            | \$1045.32        |

| Software  | 122 ms                 | 6 hr             | \$216.60         |

Table 4.8: RGB to  $YC_BC_B$  Experimental Data

### 4.5 Data and Stream Based Experiment

#### 4.5.1 NUI-ARDS DVC

In our third experimental test we apply our methodology to a more complex application to determine the CEF of a DVC that would extend the capabilities of an existing 3D stereopanoramic vision system depicted earlier in Figure 4.1.

#### 4.5.2 NUI-ARDS DVC Description

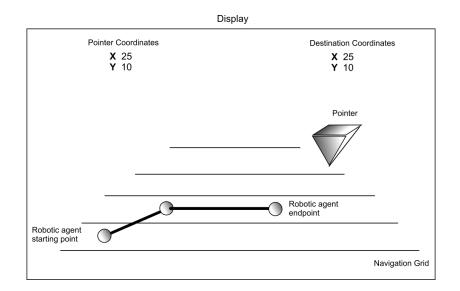

The 3D Stereo-Panoramic Acquisition and Display System (3D-SPADS) [26] developed in the Embedded Reconfigurable Systems Lab at Ryerson University displays captured video on three screens. A portion of the captured video displayed in the center screen can be seen in 3D by the human eye. Our goal is to provide a DVC computing architecture for a Natural User Interface Augmented reality Display System (NUI\_ARDS) which could extend the systems capability by allowing 3D virtual objects to be superimposed on the center screen. Our main objective is to determine the cost effectiveness of the computing architecture using our proposed analysis. The added capability would allow the 3D-SPADS to be used in applications such as telepresence or telemedicine by allowing a human operator to remotely control, plan, and manipulate a robotic agents movement or action. Figure 4.10 illustrates an example of how the NUI\_ARDS could work.

The architecture design selected needs to also meet the following functional and technical specifications.

#### Functional Specifications

Figure 4.10: Example of NULARDS visual display capability

- 1. System should be able to inject virtual objects into the captured video data.

- 2. Virtual objects can be 3D or 2D such as pop-up menus, and 3D pointer.

- 3. Virtual objects follow the movement of the human operators interface device.

- 4. The size and shape of virtual objects should react to movement of the human operator interface device.

- 5. Allow human operator to select robotic agents motion path.

#### **Technical Specifications**

- 1. Virtual objects should be superimposed on captured stereo video data from XVGA camera 1 and VGA camera 2.

- 2. The entire display is divided into 3 screens, left screen, center screen, and right screen. The left screen displays the captured left peripheral video data, the right screen displays the right peripheral video data. The center screen displays both the left and right video

data simultaneously for the left and right eye respectively to provide a stereoscopic display.

- 3. Each virtual object displayed is no more than 64x64 pixels in size.

- 4. System should be a loadable and unloadable DVC on the MARS platform.

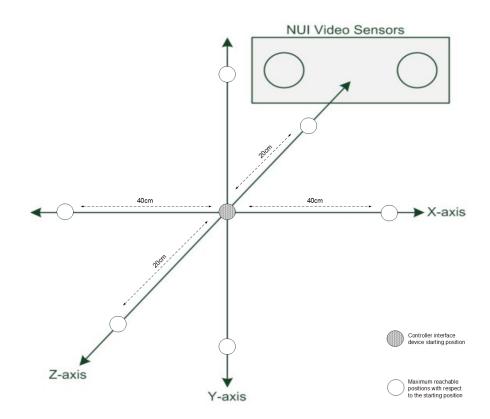

- 5. The position and tracking of the human operator interface device is with respect to the xyz Cartesian co-ordinate system in Figure 4.11:

Figure 4.11: Controller interface motion capture design

In this design situation a dedicated DVC was eliminated from consideration because the human-computer interaction with the system is vastly slower than the processing speed of the 3D-SPADS system. For example, the required 60 FPS with a screen resolution of 1024x768 means that the system has 9.82 frames to process a single character input by a human operator if a keyboard control device was used at a speed of 367 characters per second. With this system the user uses hand motion and selection of points which is even slower. With a user randomly selecting any 10 points at 0.45 point selections per second the system has even more time for processing. However, this system needs to draw 2D and 3D images and then output the appropriate pixel. Adding special dedicated hardware for the drawing of images is possible but can also be done by the processor at a slower rate without affecting the user interaction with the system. In this situation, a hybrid DVC is a good computing architecture candidate.

### 4.5.3 NUI-ARDS DVC Principles

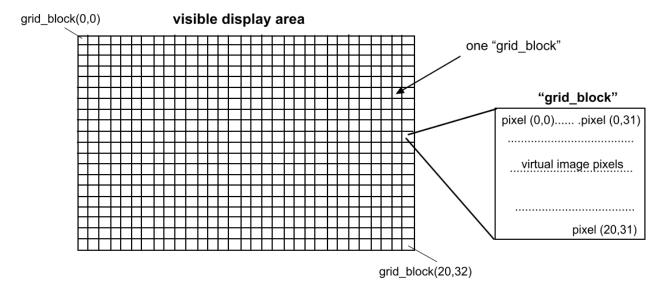

Graphical display systems such as computer graphics cards usually have a large frame buffers to store entire display image where the system can make any change before output to the screen. This type of approach requires large amounts of memory and in our case a 1024x768 display resolution with a 24 bit RGB colour depth would require 2.25 MB of memory. For an embedded system with minimal memory available 2.25 MB would take up almost all the memory available on the Virtex 4 [27] which would also be required by other components. In this case, we developed a different approach for displaying virtual graphical images superimposed on live video stream which lead us to use a bitmap approach. To superimpose virtual objects onto the live video stream the display screen is divided into 32x32 pixel sections which we refer to as grid\_blocks. In each grid\_block a virtual object can be injected into the display. Figure 4.12 depicts how the display screen is divided into grid\_blocks and how the virtual image to be superimposed onto the live video stream is stored in memory.

Figure 4.12: Visual display divided into grid\_blocks

Each virtual image pixel colour information is encoded into six bits. One bit is used for transparency, two bits for red channel, three bits for green channel, and two bits for blue channel. The six bits are decoded using the method in tables 4.13 to 4.16 in order to get the actual eight bit RGB virtual image colour channel data output on the display.

| Bit | Bit | Bit | Bit | Bit | Bit | 8bit Red channel |

|-----|-----|-----|-----|-----|-----|------------------|

| 5   | 4   | 3   | 2   | 1   | 0   | value            |

| 0   | 0   | х   | х   | х   | 0   | 0                |

| 0   | 1   | х   | х   | x   | 0   | 42               |

| 1   | 0   | х   | х   | x   | 0   | 84               |

| 1   | 1   | х   | х   | x   | 0   | 126              |

| 0   | 0   | х   | х   | x   | 1   | 0 (transparency) |

| 0   | 1   | х   | х   | х   | 1   | 171              |