# Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2008

# Co-synthesis of multiple processor embedded systems for real time applications

Anika Awwal Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Awwal, Anika, "Co-synthesis of multiple processor embedded systems for real time applications" (2008). *Theses and dissertations*. Paper 167.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

#### CO-SYNTHESIS OF MULTIPLE PROCESSOR EMBEDDED SYSTEMS FOR REAL TIME APPLICATIONS

Anika Awwal BASc, University of Toronto, 2004

A thesis presented to Ryerson University in partial fulfilment of the requirements for the degree of

Masters of Applied Science

Graduate Program in Electrical and Computer Engineering Toronto, Ontario, Canada, 2008 ©Anika Awwal 2008

> PROPERTY OF RYERSON UNIVERSITY LIBRARY

# Declaration

I hereby declare that I am the sole author of this thesis. I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Anika Awwal

# Abstract

Co-synthesis of Multiple Processor Embedded Systems for Real Time Applications Masters of Applied Science, 2008 Anika Awwal

Electrical and Computer Engineering

**Ryerson University**

This thesis presents the methods for automating the synthesis of multiprocessor realtime embedded systems. It describes an evolutionary technique of finding an affordable architecture for a multi-mode multi-task system while meeting the real-time constraints imposed by designers.

First the synthesis problem is introduced and previous co-synthesis approaches to handle this problem are discussed. Then the description of the proposed co-synthesis framework foe real time systems is presented. The co-synthesis framework consists of four main steps, namely processing element allocation, process assignment, scheduling and evaluation. The method determines a set of feasible solutions with optimized partitioning and real-time schedules for processes and data communication. The framework is capable of producing acceptable solutions for critical systems with hard real-time deadlines by employing process level prioritization and by meeting the process level deadlines. Moreover, the proposed scheduling methodology achieves better PE utilization as compared to the conventional non-preemptive scheduling technique. The co-synthesis method is demonstrated by applying it to examples from the literature and to industrial benchmarks, such as auto industry, telecommunication, networking and office automation.

# Acknowledgements

First, I would like to express my gratitude to my supervisor, Gul N. Khan, for his close supervision on all the work presented in this thesis. He is methodical, imaginative and an excellent research advisor. I would like to thank NSERC and Ryerson University for providing financial support. The equipments provided by the Canadian Micro-electronics Corporation were valuable and important for implementing the proposed algorithm. Finally, I would like to thank Robert P. Dick (Northwestern University) for discussions on E3S benchmarks implementation.

# **Table of Contents**

| De | clara   | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ii  |

|----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| At | ostrac  | sterne state in the second state of the | iii |

| Ac | know    | vledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | v   |

| Ta | ble of  | f Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | vi  |

| Li | st of l | Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | X   |

| 1  | Intr    | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1   |

|    | 1.1     | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1   |

|    | 1.2     | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2   |

|    | 1.3     | Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3   |

|    | 1.4     | Contribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4   |

|    | 1.5     | Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4   |

| 2 | Co-s             | ynthesi | s of Real-time Embedded Systems                            | 6  |

|---|------------------|---------|------------------------------------------------------------|----|

|   | 2.1              | Definit | ions                                                       | 7  |

|   |                  | 2.1.1   | Constraint Specification: Task Set, Tasks and Processes    | 7  |

|   |                  | 2.1.2   | Processing Elements and Communication Resources            | 10 |

|   |                  | 2.1.3   | Utilization, Load and Laxity factor of a Processor         | 11 |

|   |                  | 2.1.4   | Scheduling Algorithms Taxonomy                             | 12 |

|   | 2.2              | Optimi  | zation Techniques for Scheduling and Assignment            |    |

|   |                  | Metho   | ds                                                         | 14 |

|   |                  | 2.2.1   | Optimization Algorithms for Scheduling Methods             | 15 |

|   |                  | 2.2.2   | Optimization Algorithms for Assignment/Allocation          | 19 |

|   | 2.3              | Co-syr  | thesis Approaches                                          | 23 |

|   |                  | 2.3.1   | Pioneering Work in Co-synthesis                            | 23 |

|   |                  | 2.3.2   | Synthesis of Distributed Embedded Systems and Multiproces- |    |

|   |                  |         | sor Systems                                                | 27 |

|   |                  | 2.3.3   | Co-synhesis of Multiprocessor Real- time Embedded Systems  | 30 |

|   |                  | 2.3.4   | Co-synthesis of Multi-mode Embedded Systems                | 33 |

| 3 | Co-s             | ynthesi | s of Heterogeneous Multi-task Embedded Systems with Real   |    |

|   | Time Constraints |         |                                                            | 36 |

|   | 3.1 Introduction |         |                                                            | 36 |

|     | 3.1.1     | System Architecture                                             | 37 |

|-----|-----------|-----------------------------------------------------------------|----|

|     | 3.1.2     | Optimization Algorithm Requirements                             | 38 |

| 3.2 | System    | Specification and Solution Representation                       | 39 |

| 3.3 | Optimi    | zation Algorithm for Proposed Co-synthesis Method               | 42 |

| 3.4 | Initializ | ation of PE and Communication Resource Allocation               | 44 |

| 3.5 | Deadlir   | ne Assignment                                                   | 47 |

| 3.6 | Schedu    | ling                                                            | 48 |

|     | 3.6.1     | Process Prioritization                                          | 49 |

|     | 3.6.2     | Scheduling of Communication Events                              | 55 |

|     | 3.6.3     | Scheduling of Processes                                         | 56 |

|     | 3.6.4     | Verification of Schedule List by Utilization Factor Computation | 58 |

| 3.7 | Solutio   | n Evaluation                                                    | 61 |

| 3.8 | Evolut    | ion of New Solutions by Genetic Algorithm                       | 63 |

|     | 3.8.1     | Solutions Ranking                                               | 64 |

|     | 3.8.2     | Halt                                                            | 64 |

|     | 3.8.3     | Solutions Selection and Reproduction                            | 65 |

|     | 3.8.4     | Crossover and Mutation                                          | 66 |

| Exp | eriment   | al Results                                                      | 69 |

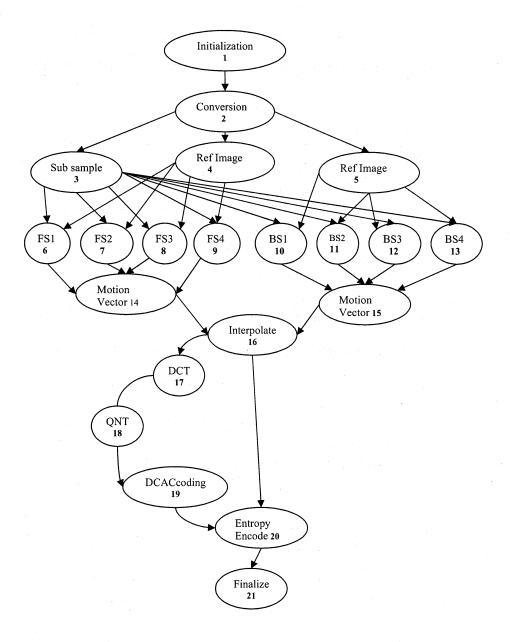

| 4.1 | MPEG      | Encoder                                                         | 69 |

4

| 5 | Con | clusions and Future Work                                            | 97 |

|---|-----|---------------------------------------------------------------------|----|

|   | 4.5 | Multi-mode Applications                                             | 95 |

|   | 4.4 | E3S Benchmarks                                                      | 80 |

|   | 4.3 | Hou and Wolf's Graph                                                | 77 |

|   |     | Systems                                                             | 73 |

|   | 4.2 | SOS: Synthesis of Application-specific Heterogeneous Multiprocessor |    |

# List of Figures

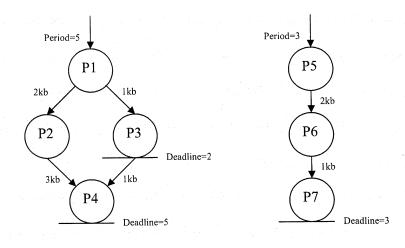

| 2.1  | Tasks Set Representing a System Specification.    | 9  |

|------|---------------------------------------------------|----|

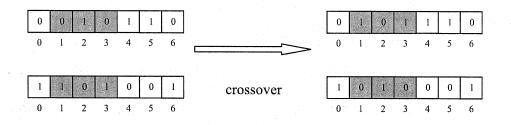

| 2.2  | Crossover for GA.                                 | 22 |

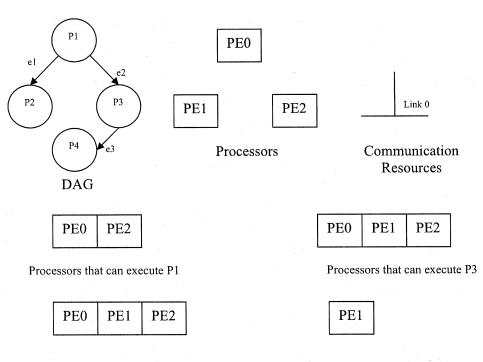

| 3.1  | PE and Communication Resource Allocation.         | 39 |

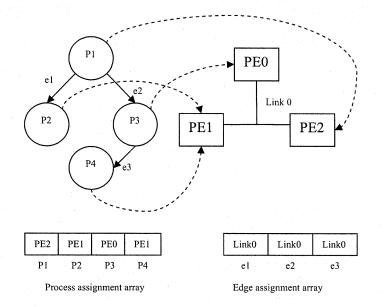

| 3.2  | PE and Communication Resource Assignment.         | 40 |

| 3.3  | Communication Resource Connectivity Array         | 41 |

| 3.4  | The Co-synthesis Framework.                       | 42 |

| 3.5  | Solutions for A Generation                        | 43 |

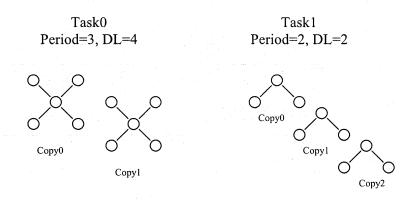

| 3.6  | Deadlines and Periods of the Tasks.               | 48 |

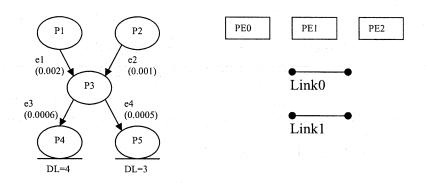

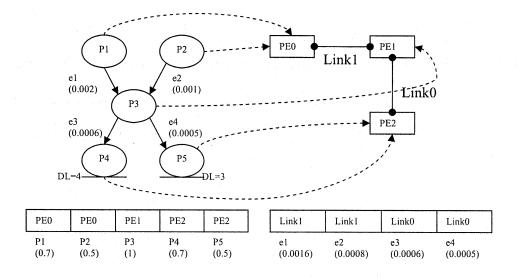

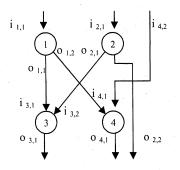

| 3.7  | Task Graph, PEs, Communication Resources.         | 50 |

| 3.8  | Process and Edge Assignment.                      | 52 |

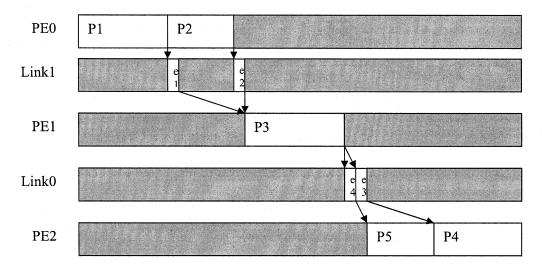

| 3.9  | Example of PE and Communication Resource Schedule | 54 |

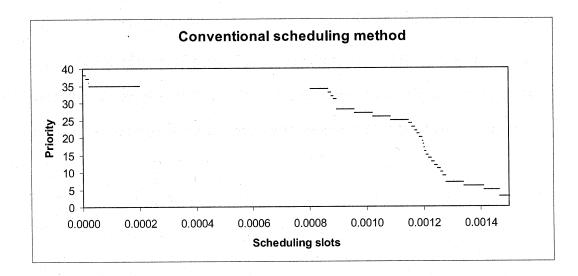

| 3.10 | Schedule for Conventional Non-Preemptive Method   | 61 |

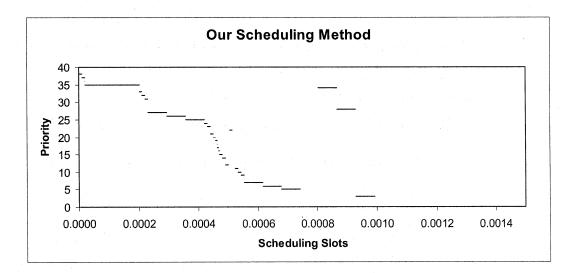

| 3.11 | Schedule for Proposed Method                      | 62 |

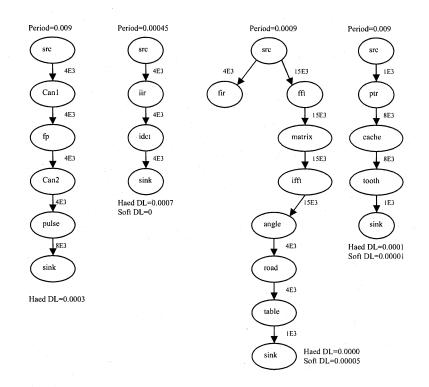

| 4.1  | MPEG Encoder Task Graph.                                  | 70 |

|------|-----------------------------------------------------------|----|

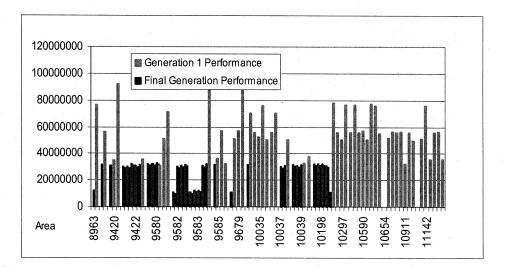

| 4.2  | Initial and Final Generation Solutions for MPEG2 Encoder  | 72 |

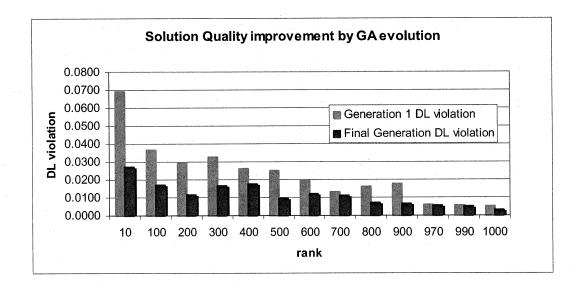

| 4.3  | SOS Example 1 and Example 2                               | 73 |

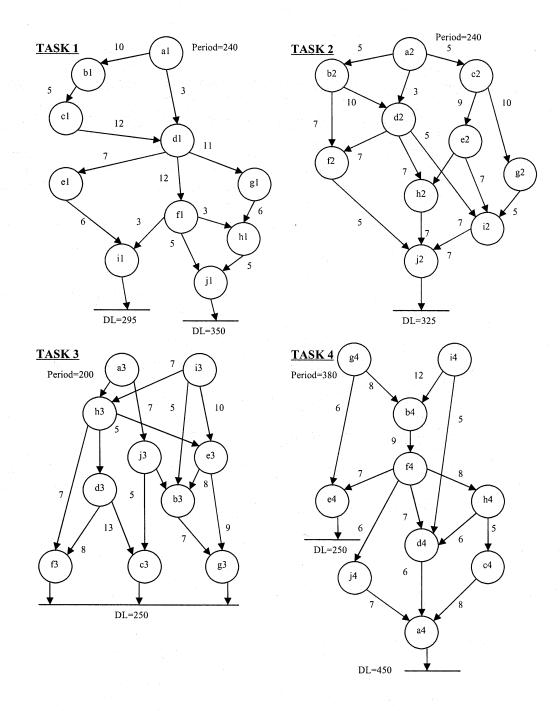

| 4.4  | Hou and Wolf Task Graphs                                  | 78 |

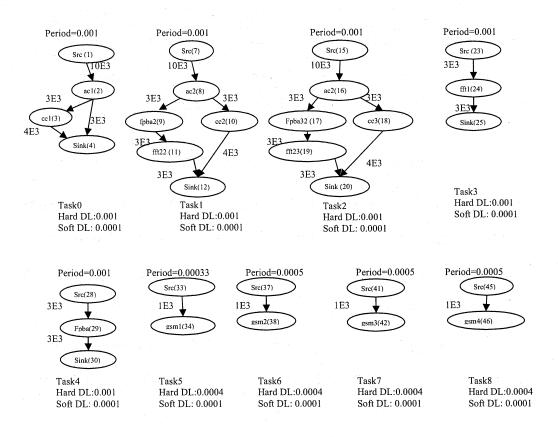

| 4.5  | Telecommunication E3S Benchmark.                          | 81 |

| 4.6  | Generation 1 and Final Generation Soft Deadline Violation | 87 |

| 4.7  | Example of Schedule List.                                 | 89 |

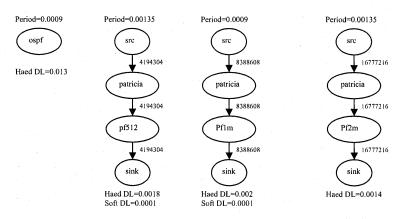

| 4.8  | Networking E3S Benchmark.                                 | 90 |

| 4.9  | Office-Automation E3S Benchmark.                          | 91 |

| 4.10 | Auto-industry E3S Benchmark                               | 92 |

# **Chapter 1**

# Introduction

In this chapter we give an overview of embedded systems and co-synthesis method. Here we state the motivation behind our proposed work. We also state our objective, and we present our contribution in the co-synthesis research field. Finally we discuss the thesis organization.

#### 1.1 Overview

A large number of modern electronic devices around us are embedded systems. Average modern cars consist of 10-20 embedded computer systems and these systems are responsible for a major portion of the cost of a car. The microwave oven we use to warm our food, the cell phone we use to communicate, printers, almost every modern device around us are built around embedded systems. Recent implementations of

1

embedded systems consist of multiple general purpose processors (software processing elements) and dedicated hardware blocks (hardware processing elements), such as Application Specific Integrated Circuit (ASIC) and/or Field Programmable Gate Arrays (FPGAs) [14, 39]. Co-synthesis automates the process of design space exploration for multiple processing element embedded systems.

#### **1.2 Motivation**

Designing an embedded computer system, especially the ones with the real-time constraints, is a challenging job. Hard real-time systems are designed to minimize (if not completely eliminate all) possible errors and to produce results that are on time. Life-supporting medical equipments, nuclear power plants, flight control systems are examples of such embedded systems. Many of these systems have task level, as well as explicit process level deadlines. The designer can ensure real-time deadlines are met by using more expensive faster processors. However, they also have to design and develop affordable low cost systems.

To explore the embedded systems design space, the designer needs to design and prototype numerous different embedded systems. Manual design space exploration for embedded system is time consuming and expensive. Though embedded systems containing multiple processing elements are gaining popularity, design automation of these systems poses a number of challenges. In this thesis, we propose a new design automation method that is capable of producing optimized partitioned solutions for large-scale multiprocessor multi-task embedded systems in finite time.

Initial design automation has been for the low-level stages of design processes and later design automation moved toward the automation of the high-level (architectural) design processes. The problem definition of high level designs is more ambiguous than that of low level ones. As the embedded system synthesis problems become increasingly well defined and solved, embedded system designers will have to spend less time to explore design space.

#### **1.3 Objectives**

We wanted to design a heuristic optimization algorithm for our co-synthesis method that can guarantee sub-optimal solutions. The objective of the co-synthesis method was to determine feasible solutions with optimized partitioning and real-time valid schedules for processes and communication events. These solutions should have low resource cost, and they should meet the real-time deadlines as well as schedulability conditions.

3

#### 1.4 Contribution

The proposed method is fast and efficient to design large scale high performance embedded system . The presented framework is multiobjective: while meeting the realtime constraints it also tries to optimize the resource usage. It supports process level resource sharing, and therefore, it is more flexible than other co-synthesis methods that use task level resource sharing. We consider process level deadline assignment and prioritization method. This prioritization method helps the proposed method to meet the deadlines of critical hard real-time systems.

Unlike many other proposed co-synthesis methods our method does not ignore communication resource allocation and scheduling. It supports both processing elements and communication resource allocation and scheduling. It is also capable of producing efficient solutions for practical modern embedded systems. Moreover, the proposed scheduling methodology achieves better PE utilization as compared to the conventional non-preemptive scheduling technique.

#### **1.5** Thesis Organization

The thesis is organized into five chapters. Chapter 2 provides definitions that are useful when discussing hardware-software co-synthesis, formalizes the basic hardwaresoftware co-synthesis problem, discusses various optimization methods for scheduling and co-synthesis, and finally surveys the work of other co-design and co-synthesis research groups. In chapter 3, we describe all phases of the proposed co-synthesis algorithm. These include algorithms for initialization of processing elements and communication resources allocation, scheduling of the processes on the allocated processing elements, and evolution method for a new generation of solutions. Chapter 4 presents experimental results. The proposed algorithm is tested with different random graphs from the literature and industrial benchmarks. Results for these systems are discussed here. Moreover these results are compared with previous work. We summarize our contributions, present conclusions, and state some directions for future work in chapter 5.

# **Chapter 2**

# **Co-synthesis of Real-time Embedded Systems**

This chapter provides definitions that will be useful when discussing the proposed cosynthesis method. Here we also discuss general optimization algorithms used in the area of scheduling and partitioning. And finally we provide a survey of previous work in the co-synthesis field.

Hardware-software co-synthesis automates the process of design space exploration for multiple processing element embedded systems. The problem of mapping functionalities into one of the available dedicated hardware processing elements (hardware modules) or implement them as processes on one of the available software processing elements (traditional CPUs) can be viewed as an optimization problem. The goal of this problem is to optimize the implementation cost and the performance while meeting the schedulability condition and real-time constraints imposed on the system. There are four main steps that are carried out by a co-synthesis CAD tool, namely allocation, assignment, scheduling and evaluation.

- Allocation selects various types of processing elements (PEs) and communication links that can be used in the system.

- Assignment, determines the mapping of processes to PEs and communication events to links. Binding or mapping has been used as synonyms for assignment.

- Scheduling determines the order in which processes will be executed on the PEs they are assigned to.

- Evaluation determines the cost, performance, and amount of deadline violation of the solution.

To achieve optimal solutions it is important to have feedback from one step of cosynthesis to others, because each of the steps affects others.

#### 2.1 Definitions

#### 2.1.1 Constraint Specification: Task Set, Tasks and Processes

The proposed co-synthesis method is intended to design multi-task embedded systems. A multi-task embedded system supports applications with multiple independent executable tasks. For our co-synthesis method the behavior, functional requirements and constraints of a system are represented by a task set. Each of the tasks of the task set consists of multiple function modules. Fixed Point Bit Allocation (FPBA) and Convolutional Encoder (CE) [43] are examples of function modules of a telecom application. Functional modules for a system are presented as processes in this thesis. A task can have multiple processes of the same functionality and different tasks can have processes of the same functionality. We assume the processes are coarse grained, which means a process may be complicated enough to require numerous microprocessor instructions.

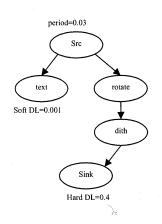

A directed acyclic graph (DAG) represents a task of a system and the nodes of a DAG represent the processes of a task. A simple example of a system with two tasks and the processes is shown in Figure 2.1. The volume of data transferred between a source and a destination node is associated with the edge (arc) between the two nodes. There are two tasks for this system. First task has four processes, and second task has three processes. A dependant process may start executing after all of its data dependencies have been satisfied. Process P4 of first task in figure 2.1, may begin execution after both process P2 and process P3 complete execution and required data to process P4 (3kbits from process P2 and 1kbits from process P3) have been transferred.

Figure 2.1: Tasks Set Representing a System Specification.

The *period* of a task is the time between one copy of task ready time and consecutive copy of the same task ready time. A system with multiple tasks may have different periods for different tasks. The *hyperperiod* of a task set is the least common multiple of the periods of the tasks. A node without any incoming edges is called a *source* node and a node with no outgoing edges is called a *sink* node. The deadline of a process (or task) is the time by when the process (or task) must complete its execution. A deadline can be either soft deadline or hard deadline. If for a synthesis solution, one or more multiple processes violate the hard deadline, then that solution will be an invalid solution. It is not desirable that a process misses its soft deadline, but meeting the soft deadline is not mandatory.

#### 2.1.2 Processing Elements and Communication Resources

A processing element (PE) execute processes. A PE can be a general-purpose processor, an application specific integrated circuits (ASICs), a field programmable gate array (FPGA), or of any other processor type. A PE library is available as an input to our co-synthesis tool. A PE library for a system describes some characteristics of the PEs, such as price, power consumption etc. It also contains information about the relationships between processes and PEs, such as worst-case execution time for each task-PE pair.

If for a particular system architecture solution, dependent and parent processes are assigned to different PEs, the edge connecting these two processes must be assigned to a communication resource. When there is no communication resource connecting the PEs, then the architecture is invalid. The main attributes of a communication resource are communication controller price, transmission time per bit, the number of contacts, power consumption during operation etc. A communication resource can connect a number of PEs that are equal or less than its number of contacts. A point-to-point communication resource has two contacts and a bus can have more than two contacts. The worst-case communication time for an edge can be calculated from various parameters, such as the amount of data need to be transferred for the edge and transmission time per bit for the communication resource.

10

#### 2.1.3 Utilization, Load and Laxity factor of a Processor

The *Utilization* factor of a processor is the fraction of time the processor is busy executing the application processes. Utilization factor, U can be expressed with equation 2.1. Load factor, *CH* of a processor can be calculated with equation (2.2).

$$U = \sum_{i=1}^{n} C_i / T_i$$

(2.1)

$$CH = \sum_{i=1}^{n} C_i / D_i \tag{2.2}$$

wehere,

n is total number of processes,

$C_i$  is the execution time of the processor for a specific process i,

$T_i$  is the period of process i, and

$D_i$  is the deadline of process i.

The laxity factor of a processor at any time t is the maximal time the processor may remain idle after t without causing a process to miss its deadline. The conditional laxity factor,  $LC_i(t)$  can be presented by equation (2.3) where the sum in j presents the pending execution time of all the processes (including process i) that are ready to execute at t and have a higher priority than process i. The laxity factor LP(t) is the smallest value of all  $LC_i(t)$ .

$$LC_{i}(t) = D_{i} - \sum_{j} C_{j}(t)$$

(2.3)

#### 2.1.4 Scheduling Algorithms Taxonomy

Off-Line scheduling algorithms are executed on the processors before the processes are activated. The schedule list is then used by the dispatcher. The run-time overhead of these algorithms is assumed to be low. However, these algorithms are not appropriate for real-time systems, as process activation for real-time systems is difficult to calculate off-line.

On-Line scheduling algorithms are executed online, during the run-time, and scheduling decision are taken every time a process is ready to execute or a process completes its execution. Each process is prioritized based on its temporal parameters. Processes can be assigned to a fixed priority or a dynamic priority. Fixed priority is assigned based on fixed parameters, before a process is activated. Dynamic priority is assigned based on the dynamic parameters that may change during system evolution. Among the basic on-line algorithms with static prioritization methods, *rate monotonic scheduling (RM)* and *deadline monotonic scheduling (DM)* algorithms are the most known ones. For *RM scheduling*, priority is assigned the highest priority. If the condition presented in equation (2.4) is satisfied for a PE, then *n* number of processes are schedulable on that PE using *RM scheduling*. This is a sufficient schedulability condition.

$$U = \sum_{i=1}^{n} C_i / T_i \le n(2^{1/n} - 1)$$

(2.4)

For DM scheduling, priority is assigned based on the deadline of a processes, the shorter the deadline of a process, the higher its priority is. If the condition presented in equation (2.5) is satisfied for a PE, then n number of processes are schedulable on that PE using DM scheduling. This is a sufficient schedulability condition.

$$U = \sum_{i=1}^{n} C_i / D_i \le n(2^{1/n} - 1)$$

(2.5)

*Earliest deadline first (EDF) algorithms* and *least laxity first (LLF) algorithms* are the most important dynamic priority assignment algorithms. For *EDF algorithms*, processes are prioritized based on their absolute deadlines. A process with the earliest deadline will be prioritized the highest. *LLF algorithm* assigns the highest priority to the process with the smallest laxity (difference between deadline and execution time of a process). A necessary and sufficient schedulability condition for *EDF algorithm* and *LLF algorithm* is

$$U = \sum_{i=1}^{n} C_i / D_i \le 1$$

(2.6)

Dynamic prioritization methods can achieve higher PE utilization comparing to static prioritization methods, but they have a higher run-time overhead. Whereas static prioritization methods are more predictable and low priority processes have chances to miss their deadlines, dynamic prioritization methods are unpredictable, and a large number of processes may miss deadlines.

# 2.2 Optimization Techniques for Scheduling and Assignment

#### Methods

Allocation/assignment and scheduling are known to be NP-complete problems [1, 38]. An algorithm that can find guaranteed-optimal solution to an NP-complete problem usually takes an amount of time exponentially dependent on the problem size. Therefore heuristic algorithms have been used in the literature to solve co-synthesis problems for large systems.

Optimization algorithms attempt to minimize a value, the optimized cost of a system. The optimization cost of a system depends on some parameters of a system that are called optimization parameters. The set of solutions around a solution is called the neighborhood of the solution, if they can be reached in one discrete step of the optimization algorithm. A local minima is a solution that has the lowest optimized cost in the neighborhood. A global minima is a solution that has the lowest optimized cost in the whole problem space. In general optimization algorithms try to avoid getting stuck in the local minima, and attempt to find the global minima. Some of the heuristic algorithms are iterative improvement algorithms. For an iterative algorithm, greediness is the tendency or probability to choose a cost-decreasing change over a cost-increasing change. Greedy algorithms are one of the simplest and the most commonly used heuristic approaches. For greedy algorithms, at a given stage, only the best choice at the present stage is considered, without taking into account any previous and later decisions. Greedy algorithms have a tendency to get trapped in local minima or local maxima. In the following sections we discuss some popular optimization algorithms that can be used to solve scheduling and assignment/allocation problems.

#### 2.2.1 Optimization Algorithms for Scheduling Methods

Scheduling is a very important phase of co-synthesis. Scheduling of a system determines the start time and completion time of the processes. As discussed in the previous section, the start time of a process must satisfy the dependencies of the DAG. This dependency constraint limits the amount of process execution parallelism. Scheduling affects the performance (completion time of a task) of a system for a co-synthesis solution, because it determines the order and concurrency of the process execution. There are scheduling methods for systems without resource constraints and there are scheduling methods for systems with resource constraints. Our co-synthesis algorithm focuses on systems with resource constraints. If resource constraints are imposed, the number of processes that can execute in parallel depends on the number of available processors. The solution of scheduling problem under resource constraints provides the trade-off points of the design space.

To achieve exact solutions for resource constrained scheduling problems, Integer Linear Programming (ILP) method can be used. To formulate scheduling problems as linear problems, the objectives and constraints need to be defined as linear equations. The objective is to minimize the schedule length under the imposed resource constraints, and the following additional constraints :

- The start time of each process is unique

- The earliest possible start time for a process is when all its parent processes have finished execution and completed required data transfer

- The number of processes executing in parallel depends on the number of available processors

- Maximum schedule length has to be smaller than a specified upper bound.

The advantage of ILP formulation is that it provides an exact solution to scheduling problems. The disadvantage of this method is that ILP formulation is computationally

complex. For medium scale examples ILP schedulers are efficient, but for large scale examples, when the number of variables or constraints of the linear equations become more than several hundreds, ILP schedulers fail to solve the problems.

To simplify the scheduling problem many researchers have reduced the number of variables and made simplified assumptions of less numbers of constraints. It can be assumed that all the processes can be executed by the same type of processors and it takes one unit execution delay to execute all the processes. Under these assumptions, to find the minimum number of processors required to schedule processes with latency constraint, researchers have used Hu's algorithm [18]. If it is also assumed that the DAG as a tree (single paths from each vertex to sink), the problem can be solved in polynomial time. Hu's algorithm applies greedy strategy. At each scheduling step it schedules as many ready-to-execute processes as possible.

The above simplified assumptions are impractical for real multiprocessor embedded systems. Without making these assumptions, minimum-latency resource-constrained scheduling problems and minimum-resource latency-constrained problems are known to be intractable. Therefore, to solve the scheduling problems heuristic algorithms have gained popularity. Among heuristic algorithms, list scheduling has been widely used [27]. For this algorithm a priority list of the processes (based on some heuristic urgency measure) is used to select among the processes. The priority list can be modified to support the timing constraints, by reflecting the proximity of an unscheduled process to a deadline. Using this technique, it is possible to meet the timing constraints, but due to the heuristic nature of list scheduling, there is no guarantee in finding the optimal solution. The list scheduling method can be applied to find a scheduling solution to minimum resource with latency constrained problems. At the beginning the least numbers of processors are allocated and to meet the latency constraints. If required additional processors are allocated. The processes are prioritized based on a slack based prioritization method [9]. *Slack* for a process is calculated based on the difference between the latest possible start time of the process and the index of the schedule step under consideration. The low computational complexity of the list scheduling method made the algorithm very popular for large systems. For smaller system this method is capable of finding optimal solutions. Among other scheduling algorithms force-directed scheduling [30], trace scheduling [12] and percolation scheduling [32] methods are most well known.

Genetic algorithms, tabu search and dynamic programming algorithms can be used for scheduling methods. We discuss these optimization methods in the following sections, as these methods have been used for assignment/allocation.

#### 2.2.2 Optimization Algorithms for Assignment/Allocation

Different optimal approaches and heuristic approaches have been used to solve assignment/allocation problems. The simplest approach is to try out all possible solutions and then select the best option. However, this approach is not feasible, because design space can be very large. Even for the lowest number of possible PEs (i.e. two PEs) of a system with N processes, there are  $2^N$  number of possible solutions. Hence there is no guarantee to find the best optimal solution manually in a finite amount of time.

Among optimal approaches, integer linear programming (ILP) and dynamic programming have been used widely to solve the partitioning problem [33, 26]. Using ILP for assignment (partitioning) is similar to the use of ILP for scheduling (discussed earlier in this section).

Dynamic Programming approach has also been known as an efficient approach for hardware-software partitioning. In this method, the optimization problem is decomposed into a sequence of stages. The optimal solution to each stage must belong to the optimal solutions of the original problem. The success of this approach depends on how efficiently the problem is divided and complexity to reach an optimal solution at every stage of the problem.

The discussed optimal approaches are suitable for only small assignment problems. For large systems, these methods become computationally too expensive, because of the exact nature of the solutions. Therefore, heuristic approaches, like simulated annealing, genetic algorithms, tabu search techniques have been widely researched to solve the process assignment problem for co-synthesis algorithms (see section 2.3). These heuristic approaches provide good-quality solutions, but they cannot guarantee the optimality of the solution.

Simulated annealing techniques are iterative improvement algorithms. Greediness in simulated annealing increases during the run of the algorithm [8]. During a simulated annealing algorithm run, probability P of a modified solution to get accepted can be represented with the following equation

$$P = 1/(1 + e^{(N-P)/T})$$

(2.7)

where,

T is the global temperature parameter,

P is the cost of the old solution,

N is the cost of the modified solution.

The temperature parameter begins at a high value (infinity) and decreases as the system stabilizes. Beginning of a simulated annealing algorithm run, changes that increase the cost of a solution are selected with the same probability as changes that decrease the cost, and the algorithm can escape local minima. But this stage does not help to reach the goal of reducing optimized cost. Towards the end of the run cost-decreasing changes have higher probability to be preferred comparing to the costincreasing changes and thus the algorithm degrades to a greedy iterative algorithm.

Tabu search algorithms are another type of powerful heuristic algorithms that can be used for efficient hardware-software partitioning. Tabu search uses a local search method to escape a local minima. It maintains a tabu list that keeps track of all the recently visited solutions. The iterative improvement procedure prohibits the solutions on the tabu list to be revisited for the next iteration and thus tries to avoid getting trapped in one neighborhood of the solution space. The tabu condition might be overruled if it results in an overall low cost. After a specified number of iterations, the search is restarted from the initial system state to expand the search of the design space.

Genetic algorithms maintain a set of solutions. During the run of the algorithm, for each generation these solutions evolve in parallel over time. For each generation, solutions from the current generation are improved by randomized local changes performed by genetic operators and exchange of information between solutions. The lowest quality solutions of a generation are then removed from the solutions set by ranking and selection process [13]. In genetic algorithm, the term chromosome typically refers to a candidate solution to a problem. All changes to chromosomes are made with two operators that are mutation and crossover. *Mutation* operation ran-

Figure 2.2: Crossover for GA.

domly picks a location on the solution array and changes the entry of the location with a new value. *crossover* randomly picks two solutions and two locations on these solutions, and swaps portions of solutions between these two location. Figure 2.2 shows an example of crossover. For two randomly chosen solutions presented in the figure, the randomly chosen positions are position 1 and 3. After crossover portions of solutions between position 1 and 3 are swapped and one new pair of solutions are evolved.

Genetic algorithms are capable of handling difficult problems composed of multiple NP-hard problems, even if each of these problems has huge solution spaces. But it is difficult to design and implement genetic algorithms. Genetic algorithms can be claimed to be better heuristic comparing to simulated annealing algorithms and tabu search algorithms based on the argument that only GA has the ability to share information between solutions.

#### **2.3 Co-synthesis Approaches**

In this section we discuss some of the past co-synthesis approaches. A lot of research has been done in the area of hardware-software co-design. Some related research on hardware-software co-synthesis with real time constraints have also been reported. Some recent work on multi-mode multi-task embedded systems has also been reported. Unfortunately, most of the techniques found in the literature suffer from some problems – either they are computationally intensive, or do not account for real-time constraints, process level deadlines, communication link scheduling, etc.

#### 2.3.1 **Pioneering Work in Co-synthesis**

Prakash and Parker used Integer Linear Programming (ILP) for SOS to solve partitioning problems [33]. Input to the algorithm is in the form of data flow graph and the algorithm synthesizes a multiprocessor architecture. The constraints and objective for a heterogeneous multiprocessor system are presented with formal mathematical equations. These equations are then linearized and solved by applying simplex technique with Bozo program [15]. It is possible to find the best optimal solution for systems with a limited number of processes by using Prakash and Parker's method. However as pointed out earlier, the computation time to find the solution using ILP increases exponentially with the system size. Gupta and Micheli presented one of the earlier approaches in the area of optimization for hardware-software co-synthesis [14]. The authors proposed the idea of optimized hardware-software partitioning to meet the constraints imposed by the designer. There are trade-offs between hardware and software implementations while capturing and making use of a partitions effect on system performance. They proposed that a partition cost function should be devised to capture these properties. Then this cost function can be used to direct the partitioning algorithm toward a desired solution, where the optimum solution is defined by the minimum value of the partition cost function. Unlike the previous research done in this area that has only focused on optimizing area and pinout of resulting circuits, the authors emphasized on how capturing the effect of timing behavior in the partition cost function is very crucial. The authors suggested that to find a solution that minimizes this cost function, a large number (exponential to the number of operations under partition) of solutions should be examined.

Ernst et al. developed a co-synthesis system COSYMA [11]. The system specification is represented in  $C^x$ , a superset of C language. A simplified assumption of only one software processor and one hardware block was made. Authors used simulated annealing for the partitioning process. The method starts with infeasible solutions that violate the timing constraints, and then improves the solutions by migrating function-

24

ality from software to hardware. A cost function was used to estimate the cost and also to control partitioning process. Hankel and Ernst proposed a co-synthesis method that dynamically determines the partitioning granularity to achieve better partitioning results [16]. It is assumed that software and hardware parts execute in mutual exclusion. This partitioning process was integrated in COSYMA.

Kalavade and Lee presented a constructive partitioning algorithm [19]. First it is decided whether hardware area is more critical for a system or the time is more critical for the system. This is selected by the threshold based comparison of a global timecriticality measure, called global criticality. In the next phase of the algorithm, named as local phase, each process is mapped to hardware or software based on different criteria of a process. This algorithm works on coarse granularity and partitions a system by traversing a list of processes.

Liu and Wong integrated partitioning with scheduling algorithm for their iterative improvement algorithm [25]. Authors made a simplified assumption of fixed number of PEs for a system, two software PEs and k number of hardware PEs. The algorithm starts with allocating all the processes to the software PEs. Later appropriate processes are migrated to hardware based on the feedback provided by the scheduler, to minimize the completion time and resource cost.

Mooney and Micheli presented a tool that performs real time analysis and priority

assignments [26]. To meet hard real time constraints, authors used dynamic programming algorithms to assign the static priorities to that processes. Proposed real-time scheduler is able to achieve tighter bounds thus squeezing more performance out of the same components as compared to a traditional RTOS. However, as mentioned earlier due to the exact nature of dynamic programming algorithms, they are only suitable for small problems.

Eles et al. presented an approach for system level specification and hardwaresoftware partitioning with VHDL [10]. The authors formulated HW-SW partitioning as a graph partitioning problem and solved it by implementing two iterative improvement heuristics based on simulated annealing and Tabu search. They mainly focused on deriving a perfect cost function that should be optimized. The problem of using a linear weighted sum as the cost function is that the weighing array has to be appropriate for the problem instance, and also for the designer's desired solution [9]. However, since the co-synthesis problem is too complicated without first exploring all the possible solutions, it is hard to find an instance's best weighing array.

Shaha et al. used a genetic algorithm for hardware-software partitioning [36]. Some simplifications are made in their work. For instance, only one software processing element is allowed, and thus it cannot handle multiprocessor distributed systems. Moreover, communication link synthesis is not carried out. The fitness function presented, only considers the violation of constraints, and does not try to find better solutions among the valid solutions.

Areto et al. provided a formal mathematical analysis of the complexity of the partitioning problems. It was proved the partitioning problems are NP - hard in general case, and the authors presented some efficiently solvable special cases of partitioning problem [1]. Only one software processor was considered. The authors in this paper tried to introduce a simplified model for hardware-software partitioning to make algorithms scalable for systems with hundreds or even thousands of components. Prakash et al., Shaha et al. and Areto et al. did not consider real time constraints in their work [1, 33, 36].

## 2.3.2 Synthesis of Distributed Embedded Systems and Multiprocessor Systems

Recently, some researchers conducted research on distributed embedded systems. Axelsson compared three heuristic techniques for hardware software co-synthesis of realtime systems: a tabu search algorithm, a simulated annealing algorithm and a genetic algorithm [3]. Dave et al. developed a constructive co-synthesis algorithm (COHRA) to solve the co-synthesis problem for multi-rate hierarchical distributed embedded systems [6]. COHRA supports pipelining of the task graphs and employs the combination of preemptive and non-preemptive scheduling algorithm. Karkowoski and Corporall presented a design space exploration method for homogeneous processing elements on a single chip [20]. This method employs functional pipelining. Oh and Ha designed an iterative algorithm for the co-synthesis problem targeting system-on-chip [28]. Hou and Wolf presented a process clustering method to achieve better co-synthesis results in lower time [17]. Li and Malik worked on analyzing the extreme (best and worst) case bounds on the running time of a program on a given processor [24].

Some researchers considered real-time constraints for allocation and scheduling problems in distributed multiprocessor systems [31, 34, 41]. Xu presented a scheduling algorithm that solves the problem of finding non-preemptive schedule for system with M identical processors [41]. The simplified assumption of all same type PEs is not realistic for modern multiprocessor systems. Peng et al. also presented a method that finds an optimal solution to the problem of allocating communicating periodic tasks to the heterogeneous processing nodes in a distributed real-time system [31]. The authors assumed that all functional modules (processes) from the same task were assigned to the same PE. Moreover, the presented method does not support systems with deadline greater than the period. Therefore, the method is not efficient for most of the real systems. The method presented by Xu and that presented by Peng. et al. uses a branch-and-bound search algorithm to find the optimal scheduling solutions for a system. The branch-and-bound search method is capable of finding the exact optimal solution. This optimal approach is suitable for small systems with a limited number of tasks and processes. Due to the exact nature of the solutions, in the worst case this algorithm may take exponential amount of time to find the optimal solutions for large systems. Ramamritham presented a static allocation and scheduling algorithm for periodic tasks and distributed systems [34]. Author used latest start time/maximum immediate successors first (LST/MISF) heuristic to search a feasible allocation and schedule. The prioritization method for this algorithm assigns priority of a process based on the latest start time of a process and the number of successor processes. This priority assignment method is not efficient, because it only considers the number of successors and does not consider priority levels of the successors. For the methods discussed above authors considered constant number of PEs for the multiprocessor systems [31, 34, 41]. Therefore, their allocation and scheduling problem has only one objective that is meeting the time constraints and this makes the optimization problem much simpler compared to the multiobjective optimization problem for embedded systems. In the rest of this section, we present the previous research work that is closely related to the work proposed in this thesis.

## 2.3.3 Co-synhesis of Multiprocessor Real- time Embedded Systems

A number of researchers considered hardware-software co-synthesis with real-time constraints [7, 9, 23, 39]. Dave et al. presented a new technique for hardware-software co-synthesis algorithm COSYN, for periodic task graphs with real time constraints [7]. COSYN can produce a feasible distributed embedded architecture for real-time systems. It allows task graphs in which different tasks have different deadlines. Authors presented a co-synthesis method to optimize the resource cost and another co-synthesis method (COSYN-LP) to optimize the power. COSYN is efficient for systems where a large number of processes are executable on the same type of PE, and thus clustering the processes speeds up the process assignment [7]. Systems for which a large number of PEs is available and where tasks are executable on different types of PEs, clustering of tasks becomes less advantageous.

Wolf presented an iterative architectural co-synthesis algorithm for heterogeneous multiprocessor embedded systems [39]. The algorithm starts with assigning each process to one PE where the process can be executed efficiently. To minimize the resource cost, processes are re-assigned based on the PE utilization, i.e. by trying to remove less utilized PE from the architecture. In the next stage of the algorithm, process reassignment is performed to minimize communication cost between PEs. In the final stage of the algorithm, communication channels are allocated between PEs. Depending on

whether the communication allocation on an existing channel is possible, the channel is used or a new channel is added. This heuristic algorithm is fast comparing to other methods.

Among all the co-synthesis algorithms presented in literature, only MOGAC uses multiobjective optimization strategy [8, 9]. Dick and Jha presented a hardware-software co-synthesis method that partitions and schedules embedded specifications consisting of multiple periodic task graphs [9]. MOGAC synthesizes real-time heterogeneous distributed architectures, which meets the hard real time constraints. It used a multiobjective genetic algorithm (GA) to optimize the conflicting features of price and power consumption. The requirements of the embedded system are modeled as DAG. The authors used multiple general-purpose processors and multiple cores as the processing element (PE) for co-synthesis. MOGAC was designed such that it accepts a database, which specifies the performance and power consumption of each task on each available PE type. Each task graph edge is assigned to a communication link for which the power consumption and communication time is considered.

Xie and Wolf presented an allocation and scheduling algorithm for systems with control dependencies among the processes [40]. The proposed method handles conditional execution in multirate embedded systems. The authors proposed a new mutual exclusion technique for the conditional branches of the task graph to exploit the resource sharing. Author used a scheduling method that is similar to Sih and Lee's proposed compile-time scheduling heuristic [37]. Sih and Lee used dynamic level scheduling that accounts for interprocessor communication overhead when mapping processes onto heterogeneous processor architecture. The authors used a simplified non-preemptive scheduling technique in which lower priority processes might hamper a higher priority process execution.

Chakravarty et al. used a stochastic scheduling algorithm to schedule the processes for their co-synthesis method ESCORTS [4]. Using this scheduling method, the authors are able to assign non-preemptive stochastic start and completion time to the processes for a given allocation, with polynomial time complexity. A hierarchical genetic algorithm is used for resource optimization. The GA chromosomes are evaluated using a cost feasibility function. For this method chromosomes with a fitness value below a certain threshold are removed immediately, and these invalid solutions do not get a chance to evolve into better solutions.

Lee and Ha proposed a co-synthesis algorithm applicable for general multiprocessor systems with diverse operating policies [23]. The proposed algorithm separates the partitioning method from schedulability analysis and thus adaptable to various scheduling and operating policies. The proposed method takes into account the effect of partitioning results of higher-priority process when partitioning a lower-priority process. This algorithm also adopts the schedule-based schedulability analysis of timed multiplexing model in the performance evaluation step. The authors proposed a schedulability analysis technique to schedule all tasks until their hyper-period. A preemptive scheduling algorithm is used. If any task cannot meet the real-time constraints, the framework reports an error message. Lee et al.'s algorithm supports only task level deadlines and does not support process level deadlines, which can be critical for hard real-time systems [35]. As explained earlier in section 2.1.1 every task of a system consists of one or multiple processes.

#### 2.3.4 Co-synthesis of Multi-mode Embedded Systems

Only a few recent work were done in the area of multi-mode embedded systems. Oh and Ha proposed techniques for multi-mode, multitask embedded systems with real time constraints [29]. This iterative co-synthesis method has three main steps that solve the sub problems separately. In the first step of the algorithm a set of processing elements are allocated. The next step of the algorithm schedules the acyclic graph of each task to the selected processing elements to minimize the schedule length. In the final stage of the algorithm, evaluation is performed to check if the design constraints are satisfied and to compute the utilization factor. The problem with this algorithm is, each task is scheduled independently and to reduce the schedule length, all tasks use the fastest candidate processor as much as possible. As a result the faster processors tend to be always over utilized and the slower ones always under utilized. Oh and Ha's method assumes that processes in different tasks can not be executed in parallel and consequently the schedule length becomes unnecessarily longer.

Kim and Kim's recent work proposes hardware-software partitioning technique for multi-mode embedded systems [22]. Unlike Oh and Ha, authors considered processlevel resource sharing and parallelism rather than task level resource sharing. Processes are scheduled such that tasks can be executed in fully, partially parallel, or completely nonparallel based on the status of resource sharing between the processes in the tasks. Finally a global optimization method for PE allocation for all the tasks and all modes of a system is proposed. Scheduling method used for the proposed algorithm, schedules processes such that a process starts executing as soon as it is ready to execute. Consequently, a lower priority process may keep executing, while a higher priority process becomes ready, hampering the higher priority process execution. This simple scheduling method is not realistic for critical real-time systems.

Process assignment methods for the multi-mode, multi-task co-synthesis methods discussed above, are not efficient for systems with a large number of candidate PEs [22, 23, 29]. For each process assignment, every PE is considered and for large number of PEs the method of repeated re-assignment and re-scheduling can be laborious, and sometimes not feasible. Some of the proposed co-synthesis algorithms discussed here do not provide allocation or scheduling methods for the communication links [22, 23, 29]. Communication link allocation and scheduling is critical for system optimization, and for accurate evaluation of target system architecture. Most of these co-synthesis methods use conventional task level prioritization method for scheduling, which is not efficient for satisfying real-time process level deadlines [22, 23, 29].

In this chapter we provided some definitions that will be useful when discussing the proposed co-synthesis method. Here we discussed general optimization algorithms used in the area of scheduling and partitioning. This chapter also provides a survey of previous work in the co-synthesis field.

# **Chapter 3**

# Co-synthesis of Heterogeneous Multi-task Embedded Systems with Real Time Constraints

In this chapter we describe our co-synthesis framework, and the software implementation associated with it for hardware software partitioning and process scheduling of a real-time system. First we present the main steps of the proposed method, and then we describe these steps in detail.

## 3.1 Introduction

The co-synthesis problem is formulated to optimize the system cost and performance, while satisfying the schedulability conditions. The proposed co-synthesis algorithm can produce valid system architectures meeting real time deadlines and area constraints. Optimized system partitioning (mapping/assignment) is achieved using a genetic algorithm (GA) that can avoid becoming trapped in the local minima. The proposed co-synthesis method employs a new static priority list scheduling technique to schedule the tasks on their assigned PEs and the data communication on the communication resources [2]. It can handle multi-rate systems containing tasks with hyperperiods that are large relative to their periods. A single co-synthesis run of this algorithm produces multiple designs that present the trade-offs points of a multiple PE architectural design space.

In this chapter we explain how we represent the solutions and system specifications. Here we provide detailed description of our co-synthesis steps, such as allocation, assignment, scheduling, initialization and evolution techniques.

#### 3.1.1 System Architecture

The proposed method does not place any limit on the number of PEs (software or hardware) in the architecture. It supports the use of multiple types of communication resource (bus or point to point) in the target architecture. The following assumptions are made for the target multi-processor embedded architecture:

• The target system can consist of multiple software and hardware PEs that can work in parallel.

37

- A communication resource can support communication for multiple PEs based on the number of contacts available on the link.

- PEs can perform computation concurrently while transferring data to other PEs.

## 3.1.2 **Optimization Algorithm Requirements**

The goal of our co-synthesis algorithm is to produce a sub-optimal embedded realtime architecture by allocating PEs, finding process assignment to the allocated PEs, and by finding a scheduling order for the architecture. This architecture should have low cost and must meet the real time constraints. The algorithm requires the application specifications in the form of DAGs and a PE library describing types of PEs and communication resources (see sections 2.1.1 and 2.1.2). As mentioned in section 2.2, partitioning and scheduling problems are NP-complete, and in the worst case they may optimally require an amount of time exponential in the size of problem instance. Hence we were forced to resort to a heuristic optimization algorithm that can guarantee sub-optimal solutions. This algorithm should be able to avoid becoming trapped in the local minima, and it should assimilate problem-specific heuristic into the optimization framework easily.

Processors that can execute P2

Processors that can execute P4

Figure 3.1: PE and Communication Resource Allocation.

## 3.2 System Specification and Solution Representation

The proposed co-synthesis algorithm accepts a PE library that specifies the execution time of each process on each available PE, a list of processes that are not executable on each PE and cost of each PE. The types of PEs available for a process are represented by an array of integers, and the types of communication resources are represented by another similar array of integers. For example for a system presented in Figure 3.1, three PEs are available, and a communication resource with three contacts is available. There are two PEs, PE0 and PE2 that can execute process 1, three PEs are suitable for process 2 and 3, and process 4 is executable only on PE1.

Figure 3.2: PE and Communication Resource Assignment.

Process assignment is presented with a one dimensional array. The offset in this array corresponds to the process. The integer at each offset represents the PE the process is assigned to. For example, for the DAG and PE allocation presented in Figure 3.1, one possible PE assignment and communication resource assignment solution is presented in Figure 3.2. Every process is assigned to one of the available PEs and Link 0 connects all the three PEs that need to be connected for data transfer.

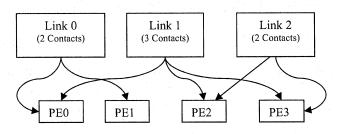

For every communication resource an array of PEs specifies which PEs the communication resource is connected to. In Figure 3.3, Link 0 has two contacts and it connects PE0 and PE1, Link 1 has three contacts and it connects PE0, PE2 and PE3, Link 2 has two contacts that connect PE2 and PE3.

Figure 3.3: Communication Resource Connectivity Array.

For our software implementation of the co-synthesis algorithm, there are four main structures that model the system. The *Node* structure represents processes, the *Edge* structure represents the data communication between processes, the *PE* structure represents processing elements, and the *Link* structure represents communication resources. Some fields of these structures are specified by the user. The user provides the system specification, e.g. available PEs, DAG, and system constraints in the form of cost (hardware area), real-time process deadlines etc.

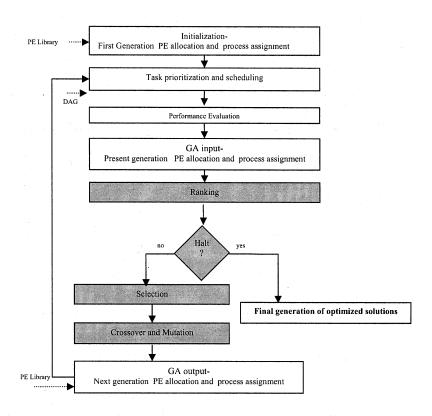

# 3.3 Optimization Algorithm for Proposed Co-synthesis Method

The main steps of our co-synthesis algorithm are given in Figure 3.4. The shaded rectangles and diamonds present the genetic algorithm steps. At the first step of the algorithm, the solution pool for the genetic algorithm is initialized with a randomized solution. After this step the algorithm enters the main loop of the algorithm and the next steps of the algorithm are repeated until the halting condition reaches.

Figure 3.4: The Co-synthesis Framework.

42

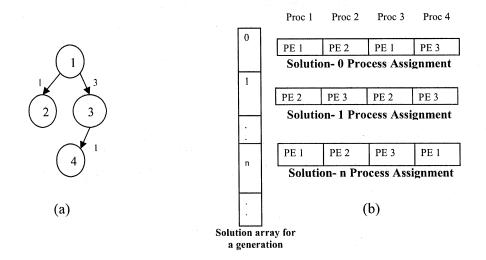

The PE assignment solutions for the generations of the genetic algorithm are presented with a two dimensional array in which the first dimension corresponds to the solution index, and the second dimension corresponds to the process index. For our co-synthesis algorithm the GA chromosome is encoded as an array and the genes in terms of integers (see Figure 3.5). For a specific run of this system, process assignment arrays for the first, second, and nth solution of a generation are presented in Figure 3.5.

Figure 3.5: Solutions for A Generation.

## 3.4 Initialization of PE and Communication Resource Allocation

Initial solutions are generated by the initialization method of PE allocation and communication resource allocation. The initialization method is presented below. The first process of the system is assigned to a PE by a randomized selection mechanism. One of the available PEs, capable of executing the first process is chosen randomly. For other processes, first it is checked if one of the already allocated PEs is capable of executing the process. When none of the allocated PEs is suitable for executing the process, the process is assigned to a new PE by the randomized selection procedure. If already allocated multiple PEs are suitable for executing the process, then a randomized selection method is used to choose one of these PEs to execute the process. This initialization procedure, confirms the assignment of all the processes to valid PEs, for a minimum resource cost.

1 for each process  $P_i$

2 for every allocated PE

3 if the PE is capable of executing  $P_i$

The PE is entered in the suitablePElist

5 endif;

6 endFor;

7 if suitablePElist is not empty

8 Randomly choose one of the PE from suitablePElist

9 else

4

10 randomly choose one of the PE that is capable to execute  $P_i$

11 endIf;

12 endFor;

Every communication event is assigned to a communication resource. A communication resource can support communication between a limited numbers of PEs, depending on the number of the contacts of the communication resource. Communication between any two PEs can use at most two contacts of a resource. The first communication event that need to be assigned to a resource is assigned by a randomized selection method. For other communication event assignments, first already allocated resources are considered. If one (two) of the contacts of one of the available allocated resources has (have) been used for one (or both) of the PEs under consideration, there is no need to allocate a new contact for the PE. Communication event assignment is performed in such a way that the least number of new communication resource contacts are added to the architecture. This assignment technique avoids the addition of extra communication resource contacts to system resource and minimizes the total resource cost. If none of the already used communication resources are economical for the communication event, a new resource is randomly selected to perform the communication event. Communication resource (CR) allocation algorithm is presented below.

1 for each edge  $e_i$

| 2 while number of available allocated CR, that have not been checked yet > |

|----------------------------------------------------------------------------|

| 3 randomly choose one of the allocated communication resource $CR_i$       |

| 4 if the source process of $e_i$ is one of the contacts of $CR_i$          |

| 5 if the sink process of $e_i$ is one of the contacts of $CR_i$            |

| 6 assign $e_i$ to $CR_i$                                                   |

| 7 break                                                                    |

| 8 else                                                                     |

| 9 use one of the available contact of $CR_i$ for $e_i$ sink process        |

| 10 $assign e_i \text{ to } CR_i$                                           |

| 11 endif;                                                                  |

| 12 else                                                                    |

| 13 if the sink process of $e_i$ is one of the contacts of $CR_i$           |

| 14 use one of the available contact of $CR_i$ for $e_i$ source process     |

| 15 $assign e_i \text{ to } CR_i$                                           |

| 16 endif;                                                                  |

| 17 endif;                                                                  |

| 18 if $e_i$ is assigned to $CR_i$                                          |

| 19 break;                                                                  |

| 20 else                                                                    |

| 21 <i>check another randomly chosen already allocated CR</i>               |

| 22 endWhile;                                                               |

| 23 if $e_i$ is not assigned to any one of the allocated CR                 |

| 24 Randomly choose a CR for $e_i$ from PE library                          |

| 25 endIF                                                                   |

| 26 endFor;                                                                 |

# 3.5 Deadline Assignment

The hyperperiod of the system is calculated as the least common multiple (LCM) of the periods of the tasks. Each task has a *hyperperiod/period* number of copies for the duration of the hyperperiod. It is assumed that, for a particular system architecture solution, if all the copies of all the tasks of a system are schedulable within the hyperperiod, then the system is schedulable for the solution [23]. The proposed method supports a deadline longer than the period, which means multiple copies of the same task can be ready to execute simultaneously. Deadlines for the first copy of each task are specified by the user. The proposed method also supports process level deadlines. Deadlines for the copies of a process are calculated as given in equation (3.1):

Deadline of nth copy of a process =  $Process_period * (n-1) + Deadline of the 1st copy$  (3.1)