### Modelling and Current-Mode Control of a Modular Multilevel DC-DC Converter

by

Sandeep Kaler

Bachelor of Engineering, Ryerson University, 2016

A thesis presented to Ryerson University in partial fulfillment of the requirements for the degree of Master of Applied Science in the program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2019

© Sandeep Kaler, 2019

#### Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public.

#### Modelling and Current-Mode Control of a Multilevel Modular DC-DC Converter

2019

Sandeep Kaler Master of Applied Science Electrical and Computer Engineering Ryerson University

#### Abstract

The visions of multi-terminal direct-current (MTDC) grids, DC distribution systems for densely populated urban areas, and DC microgrids for more straightforward integration of distributed energy resources (including renewable energies, electric vehicles, and energy storage devices) have sparked a great deal of research and development in the recent past. An enabling technology towards the fulfilment of these visions is efficient, highly-controllable, and fault-tolerant AC-DC and DC-DC electronic power converters capable of interfacing networks that operate at different voltage levels. This thesis thus presents the results of an in-depth investigation into the operation and control of a particular class of DC-DC converters. The DC-DC converter studied in this thesis is based upon the so-called modular multi-level converter (MMC) configuration, employing halfbridge submodules and with no galvanic isolation. The thesis first presents the governing dynamic and steady-state equations for the converter. Then, based on the developed mathematical model, it identifies suitable variables, strategies, and feedback loops for the regulation of the submodule DC voltages as well as converter power throughput. In particular, two current-control loops are proposed that, in coordination with one another, not only enable the control of the power flow within the converter, but also promise protection against overloads and terminal shorts. The validity of the mathematical model and effectiveness of the proposed control are verified through off-line simulation of a detailed circuit model as well as experiments conducted on a 1-kW experimental setup. The results of this exercise motivate the extension of the proposed control method to more compact designs with galvanic isolation and enhanced power handing capabilities.

### Acknowledgments

I would like to take this opportunity to thank Prof. Amirnaser Yazdani for being the best supervisor, mentor, and friend that I could have ever asked for. The amount of support, knowledge, and the number of opportunities that I have received because of him have truly been a blessing. To my parents

For all that they have done, and all that they still do.

## Contents

| 05010                                   | $\operatorname{ct}$                                                                                                                                                                                                                                                                                                            | iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cknov                                   | wledgments                                                                                                                                                                                                                                                                                                                     | $\mathbf{v}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| edica                                   | tion                                                                                                                                                                                                                                                                                                                           | vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| st of                                   | Tables                                                                                                                                                                                                                                                                                                                         | ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| st of                                   | Appendix Tables                                                                                                                                                                                                                                                                                                                | x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| st of                                   | Figures                                                                                                                                                                                                                                                                                                                        | xi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| st of                                   | Appendix Figures                                                                                                                                                                                                                                                                                                               | xiii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| onvei                                   | ntion for Notations                                                                                                                                                                                                                                                                                                            | xiv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| st of                                   | Abbreviations                                                                                                                                                                                                                                                                                                                  | $\mathbf{x}\mathbf{v}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| omen                                    | aclature                                                                                                                                                                                                                                                                                                                       | xvi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4 | oduction         Background and Motivation         Literature Review Pertinent to Thesis Objectives         Thesis Objectives         Thesis Structure                                                                                                                                                                         | <b>1</b><br>1<br>2<br>4<br>5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| The<br>2.1<br>2.2<br>2.3<br>2.4         | Principles of Operation of the MMC Based DC-DC ConverterPrinciples of Operation2.1.1The Two-Level VSC as a Building Block2.1.2The Modular Multilevel Converter (MMC)Mathematical Modelling of the MMCSteady State Characteristics of the MMCControl2.4.1Output Current Control2.4.2Arm Power Control2.4.3Input Current Control | 6<br>6<br>8<br>12<br>14<br>20<br>21<br>21<br>21<br>23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                         | edica<br>st of<br>st of<br>st of<br>st of<br>onver<br>st of<br>onver<br>1.1<br>1.2<br>1.3<br>1.4<br>The<br>2.1<br>2.2<br>2.3                                                                                                                                                                                                   | In the original sector of the sector of t |

|              |                                | 2.5.1  | Phase-Shifted Pulse Width Modulation (PS-PWM)                                                                                                                             | 25        |

|--------------|--------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|              |                                | 2.5.2  | Capacitor Voltage Balancing                                                                                                                                               | 27        |

|              | 2.6                            | A Nur  | nerical Case Study                                                                                                                                                        | 28        |

|              |                                | 2.6.1  | Output Current Controller Design                                                                                                                                          | 30        |

|              |                                | 2.6.2  | Input Current Controller Design                                                                                                                                           | 31        |

|              |                                | 2.6.3  | Arm Power Control                                                                                                                                                         | 32        |

|              |                                | 2.6.4  | Discretization of Control Parameters                                                                                                                                      | 32        |

| 3            | Soft                           | ware S | Simulation of MMC                                                                                                                                                         | <b>35</b> |

|              | 3.1                            | Case 1 | : Steady state with $i_t = 0$                                                                                                                                             | 36        |

|              | 3.2                            |        | P: Transient with $i_t = 0$ to $i_t = 4 A \dots \dots$                    | 41        |

|              | 3.3                            | Case 3 | B: Steady State with $i_t = 4 A$                                                                                                                                          | 44        |

|              | 3.4                            | Case 4 | $: \text{Transient with } i_t = 4 A \text{ to } i_t = 8.33 A \dots \dots$ | 45        |

|              | 3.5                            |        | 5: Steady State with $i_t = 8.33 A \dots$                                                                                                                                 | 47        |

| <b>4</b>     | 4 Experimental Setup of MMC    |        |                                                                                                                                                                           | 55        |

|              | 4.1                            | Physic | al Implementation                                                                                                                                                         | 55        |

|              | 4.2                            | •      | Level Configuration                                                                                                                                                       | 57        |

|              | 4.3                            |        | evel Configuration                                                                                                                                                        | 59        |

| <b>5</b>     | 5 Conclusion and Future Work 6 |        | 63                                                                                                                                                                        |           |

| $\mathbf{A}$ | Appendices                     |        |                                                                                                                                                                           | 64        |

| Bi           | Bibliography 7                 |        |                                                                                                                                                                           | 71        |

## List of Tables

| 2.1 | Summary of converter parameters used in the PSCAD simulation | 30 |

|-----|--------------------------------------------------------------|----|

| 3.1 | Summary of cases according to operating conditions.          | 36 |

# List of Appendix Tables

| A.1 | NI C-Series module | es used in this system. |  |  | 64 |

|-----|--------------------|-------------------------|--|--|----|

|-----|--------------------|-------------------------|--|--|----|

# List of Figures

| 2.1  | Basic two level voltage-sourced converter.                                                                                                       | $\overline{7}$ |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.2  | Generic MMC circuit configuration considering the two arm voltages to                                                                            |                |

|      | be voltage sources.                                                                                                                              | 9              |

| 2.3  | Half-bridge submodule used in the modular multilevel converter                                                                                   | 10             |

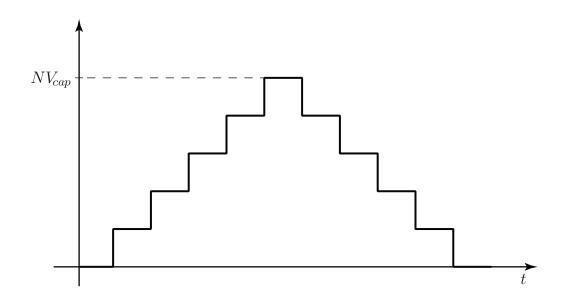

| 2.4  | General arm voltage waveform using half-bridge submodules                                                                                        | 11             |

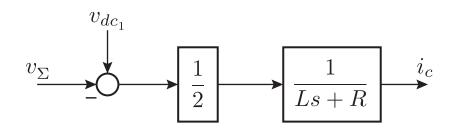

| 2.5  | Block diagram representation of (2.20)                                                                                                           | 14             |

| 2.6  | Block diagram representation of $(2.21)$                                                                                                         | 14             |

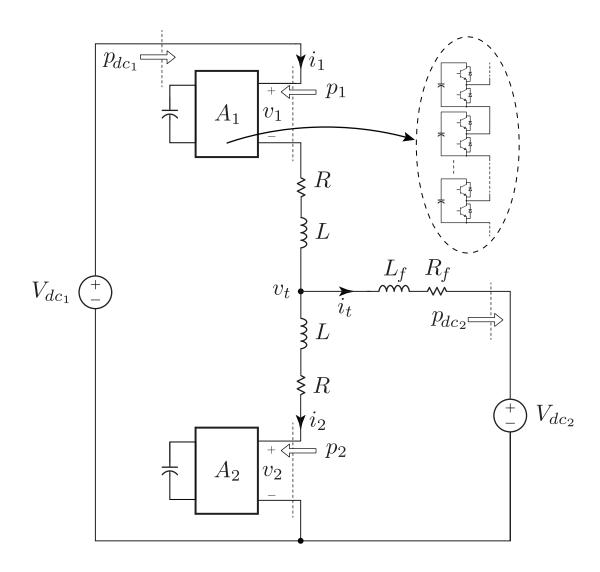

| 2.7  | General MMC circuit considered for the analysis of Section 2.3. Note that                                                                        |                |

|      | $A_1$ and $A_2$ represent the strings of submodules in the upper and lower arm                                                                   |                |

|      | respectively                                                                                                                                     | 15             |

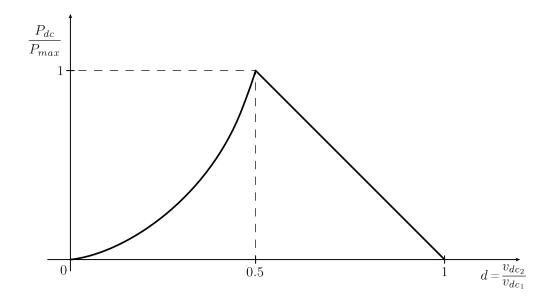

| 2.8  | Variation of maximum achievable output power versus conversion ratio of                                                                          |                |

|      | the MMC                                                                                                                                          | 20             |

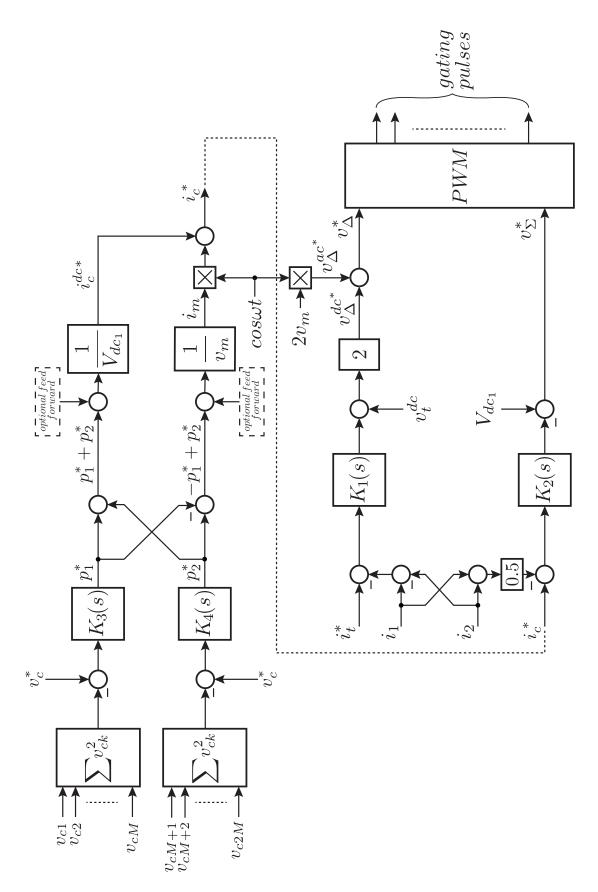

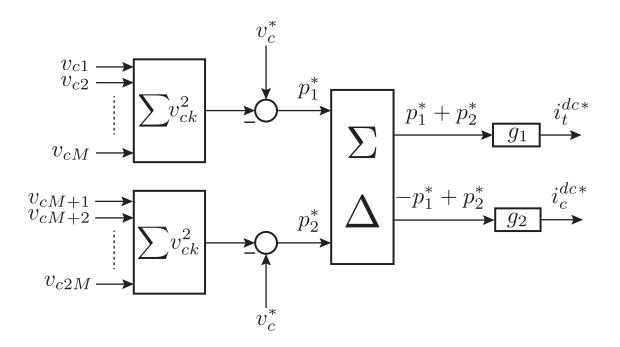

| 2.9  | Complete block diagram of the control flow for the MMC                                                                                           | 22             |

| 2.10 | Block diagram representation of the closed loop system for $i_t$                                                                                 | 23             |

| 2.11 | Block diagram representation of the control path used to regulate the arm                                                                        |                |

|      | powers $p_1$ and $p_2$                                                                                                                           | 24             |

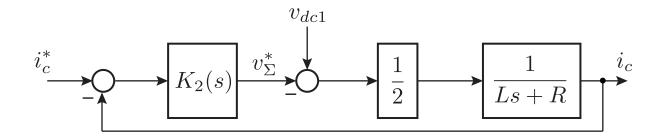

|      | Block diagram representation of the closed loop system for $i_c$                                                                                 | 25             |

| 2.13 | The $k^{th}$ submodule considered for the purpose of submodule capacitor                                                                         |                |

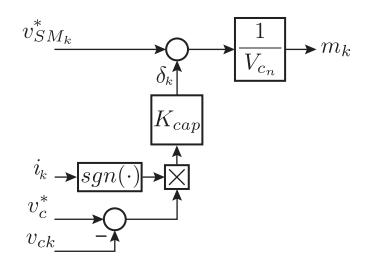

|      | voltage regulation.                                                                                                                              | 28             |

| 2.14 | Block diagram representation of the control path used to regulate the arm                                                                        |                |

|      | powers $p_1$ and $p_2$                                                                                                                           | 29             |

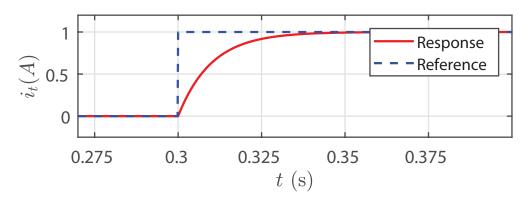

|      | Step response of $i_t$ using the gain parameters $K_p = 8.625$ and $K_i = 6.25$ .                                                                | 31             |

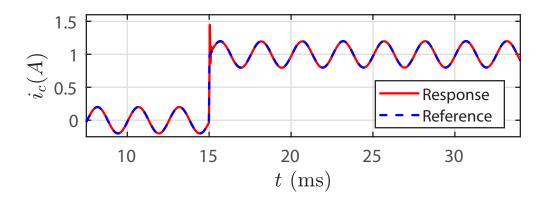

|      | Step response of the compensator expressed by $(2.76)$                                                                                           | 32             |

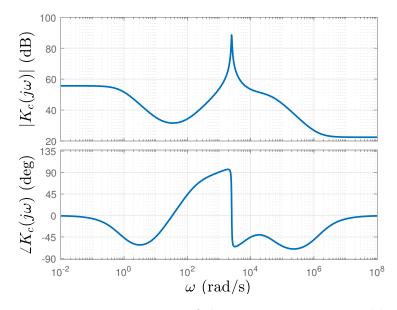

|      | Frequency response of the compensator expressed by $(2.76)$                                                                                      | 34             |

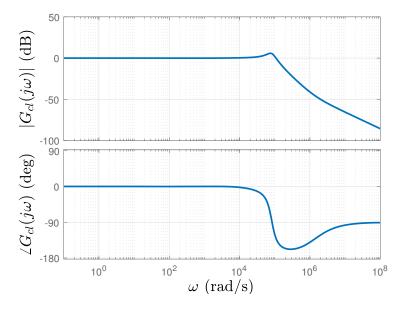

| 2.18 | Frequency response of the closed loop system using the compensator from                                                                          |                |

|      | Figure $(2.17)$                                                                                                                                  | 34             |

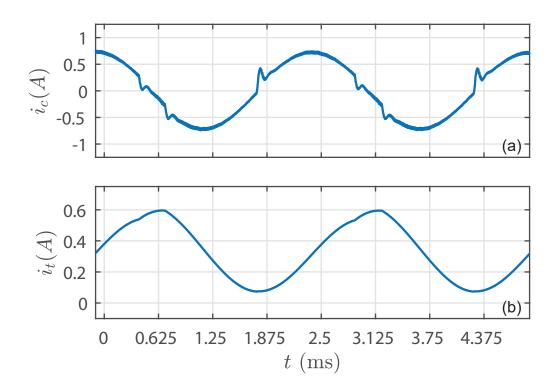

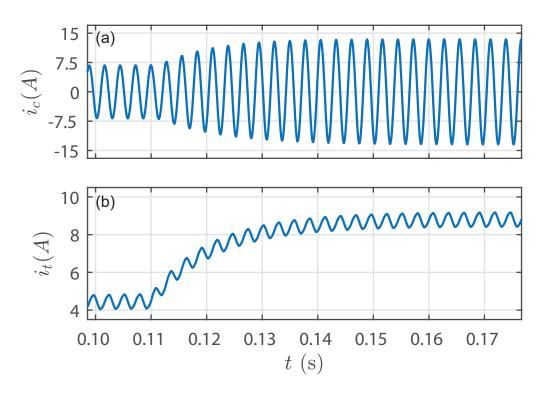

| 3.1  | Steady-state current waveforms: (a) $i_c$ and (b) $i_t$ for Case 1                                                                               | 37             |

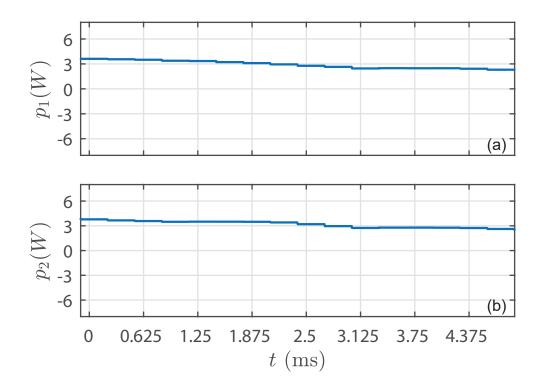

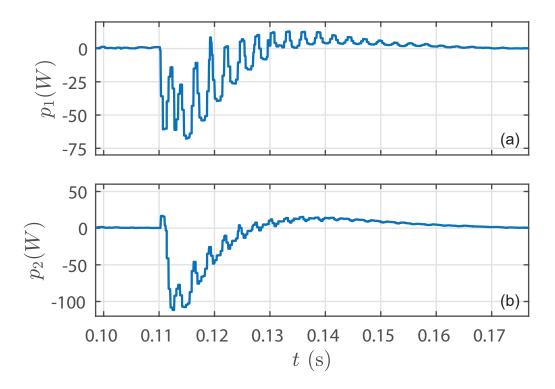

| 3.2  | Steady-state arm power waveforms: (a) $p_1$ and (b) $p_2$ for Case 1                                                                             | 38             |

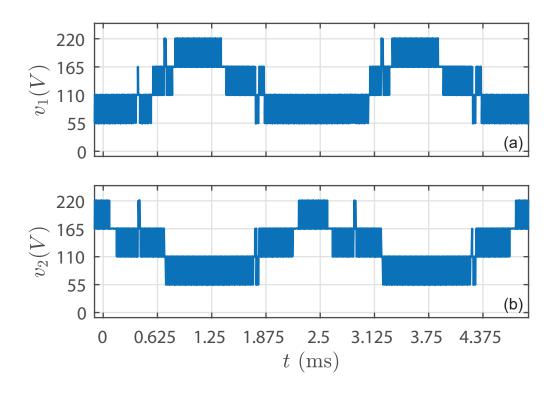

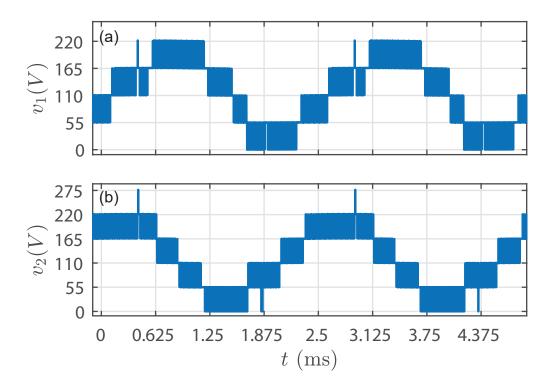

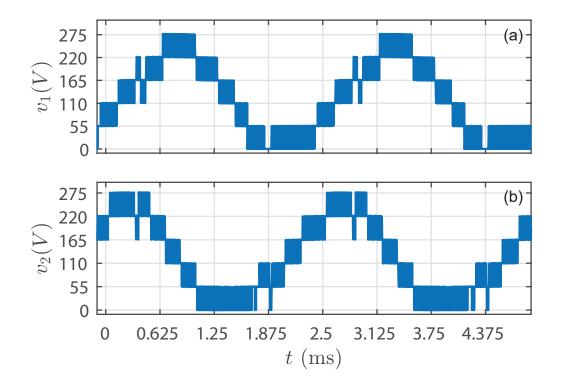

| 3.3  | Steady-state arm voltage waveforms: (a) $v_1$ and (b) $v_2$ for Case 1                                                                           | 39             |

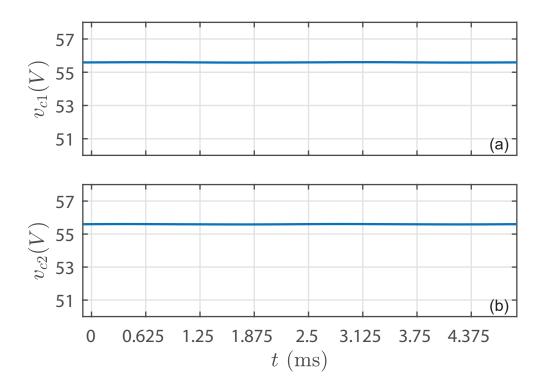

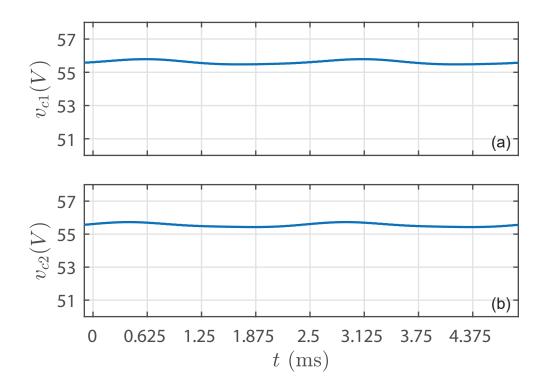

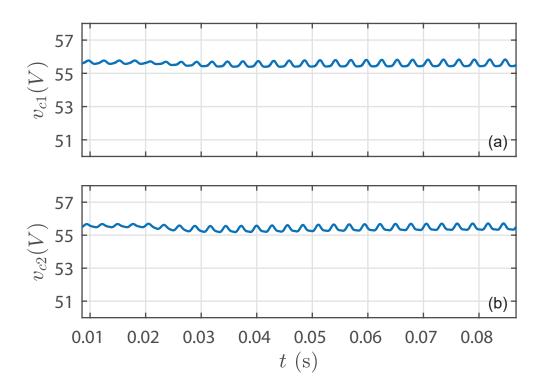

| 3.4  | Steady-state capacitor voltage waveforms: (a) upper arm capacitor voltage                                                                        |                |

| -    | $v_{c_1}$ and (b) lower arm capacitor voltage $v_{c_2}$ for Case 1                                                                               | 40             |

| 3.5  | Transient step response of $i_t$ and $i_c$ for a step change from $i_t = 0$ to $i_t = 4$ A                                                       | 41             |

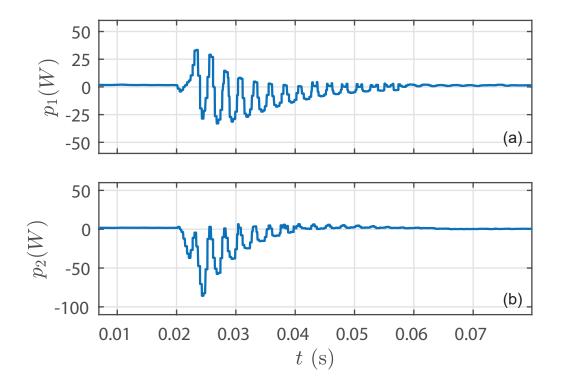

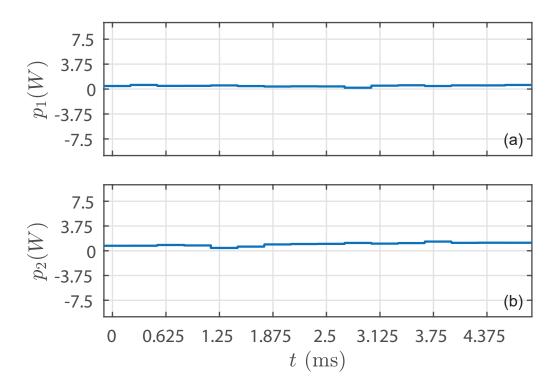

| 3.6  | Transient responses of arm powers: (a) $p_1$ and (b) $p_2$ for Case 2                                                                            | 42             |

| 3.7  | Transient capacitor voltage waveforms for (a) $v_{c_1}$ and (b) $v_{c_2}$ for a step                                                             |                |

|      | change from $i_t = 0$ to $i_t = 4 A \dots \dots$ | 43             |

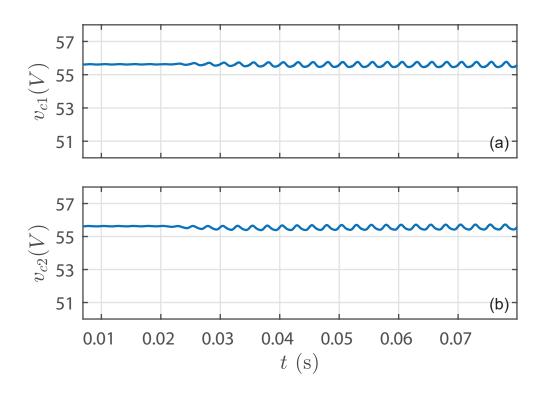

| 3.8  | Steady-state waveforms of arm powers: (a) $p_1$ and (b) $p_2$ in Case 3                  | 44 |

|------|------------------------------------------------------------------------------------------|----|

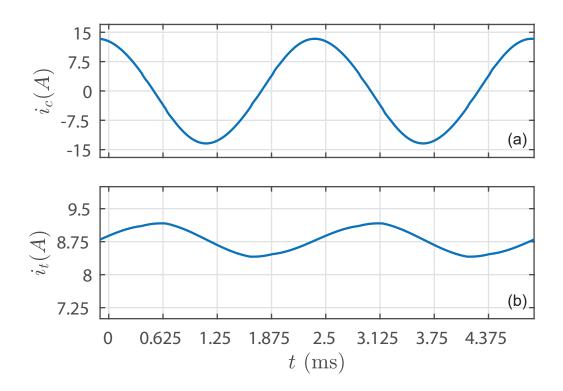

| 3.9  | Steady-state waveforms of currents: (a) $i_t$ and (b) $i_c$ for Case 3                   | 45 |

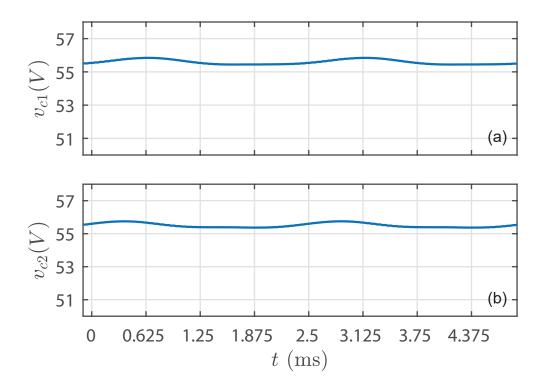

| 3.10 | Steady-state waveforms of capacitor voltages: (a) $v_{c_1}$ and (b) $v_{c_2}$ for Case 3 | 46 |

| 3.11 | Steady-state waveforms of arm voltages: (a) $v_1$ and (b) $v_2$ for Case 3               | 47 |

| 3.12 | Transient responses of currents (a) $i_t$ and (b) $i_c$ for a step change from           |    |

|      | $i_t = 4 A$ to $i_t = 8.33 A$                                                            | 48 |

| 3.13 | Transient response of arm powers (a) $p_1$ and (b) $p_2$ for a step change from          |    |

|      | $i_t = 4$ A to $i_t = 8.33$ A                                                            | 49 |

| 3.14 | Capacitor voltage waveforms (a) $v_{c_1}$ and (b) $v_{c_2}$ during the transient period  |    |

|      | of Case 4                                                                                | 50 |

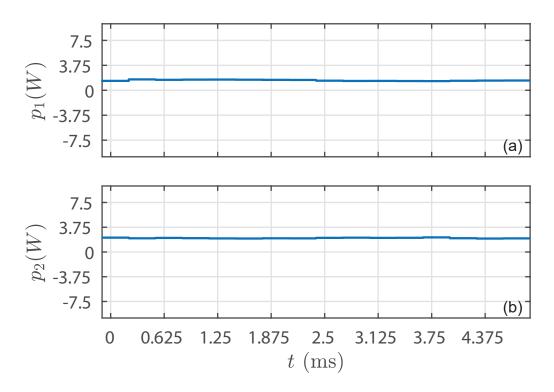

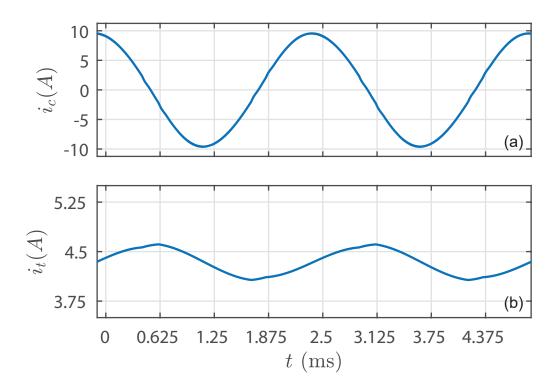

| 3.15 | Steady-state waveforms of the arm powers $p_1$ and $p_2$ for $i_t = 8.33 A$              | 51 |

|      | Steady-state current waveforms for (a) $i_t$ and (b) $i_c$ at $i_t = 8.33 A.$            | 52 |

| 3.17 | Capacitor voltage waveforms (a) $v_{c_1}$ and (b) $v_{c_2}$ in the steady-state condi-   |    |

|      | tion of Case $5$                                                                         | 53 |

| 3.18 | Arm voltages (a) $v_1$ and (b) $v_2$ in the steady-state condition of Case 5.            | 54 |

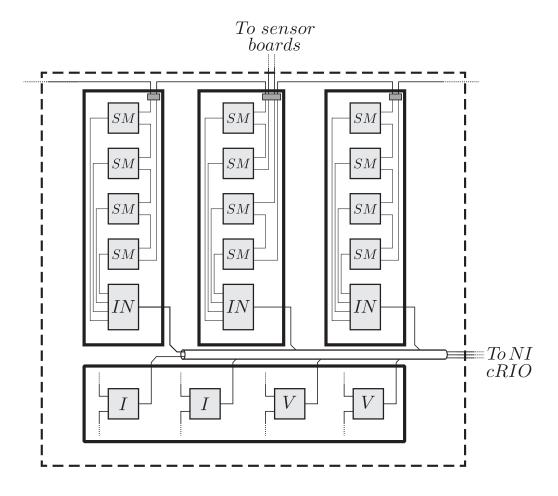

| 4.1  | High-level layout and connection diagram of the MMC assembled in the                     |    |

|      | cabinet. The board labels SM, IN, V, and I, signify the submodule, inter-                |    |

|      | face, voltage sensor, and current sensor boards, respectively                            | 56 |

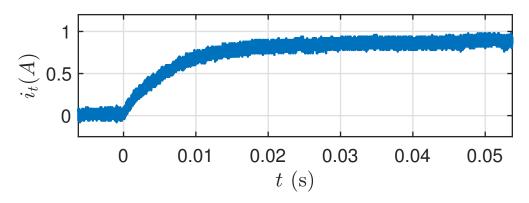

| 4.2  | Step response of $i_t$ to a 1 A reference for the single level configuration.            | 58 |

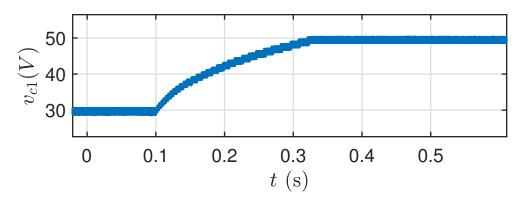

| 4.3  | Response of the capacitor voltage to a step change from $30 V$ to $50 V$ .               | 59 |

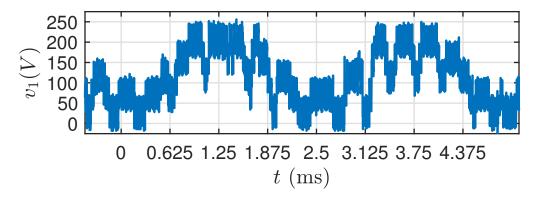

| 4.4  | Voltage waveform for $v_1$ in the five-level configuration.                              | 59 |

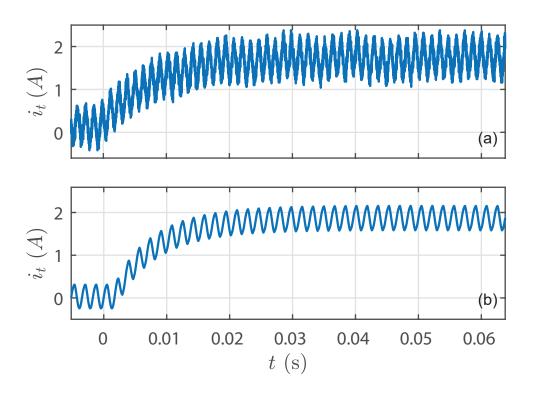

| 4.5  | Step response of $i_t$ for a change in reference from 0 to 2 A: (a) experimental,        |    |

|      | (b) simulation.                                                                          | 60 |

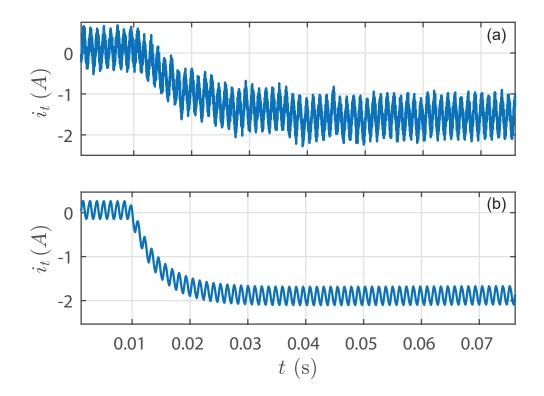

| 4.6  | Step response of $i_t$ for a change in reference from 0 to -2 A: (a) experi-             |    |

|      | mental, (b) simulation                                                                   | 61 |

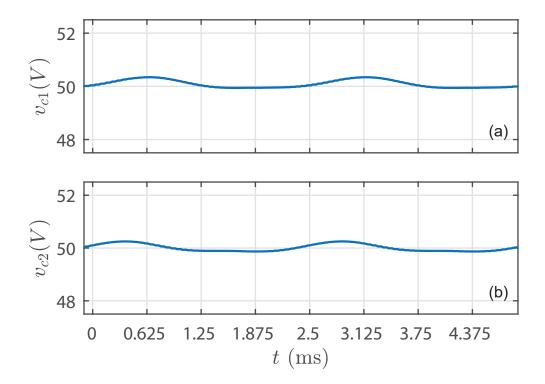

| 4.7  | Steady state voltage waveform of capacitors in the five level configuration.             |    |

|      | $v_{c_1}$ corresponds to the voltage of a capacitor in the upper arm while $v_{c_2}$     |    |

|      | corresponds to the voltage of a capacitor in the lower arm                               | 62 |

# List of Appendix Figures

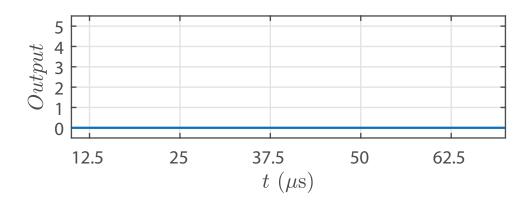

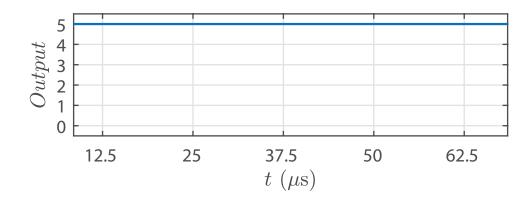

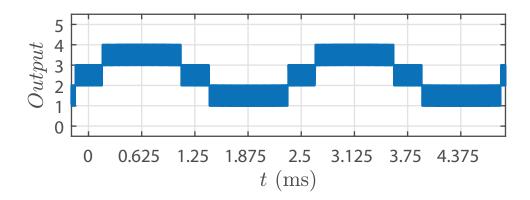

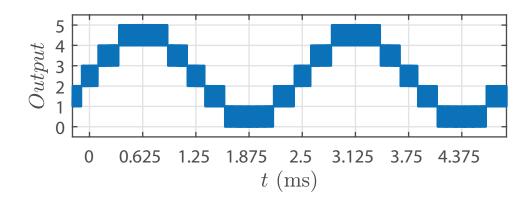

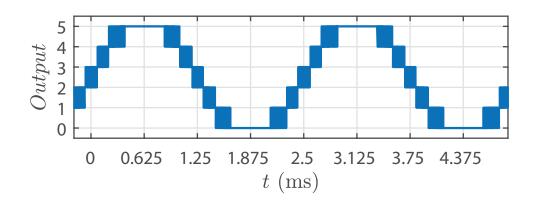

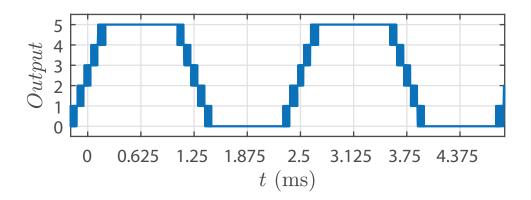

| B.1 | PS-PWM waveform for $m^{dc} = 0$ and $m^{ac} = 0$ .                                 | 68 |

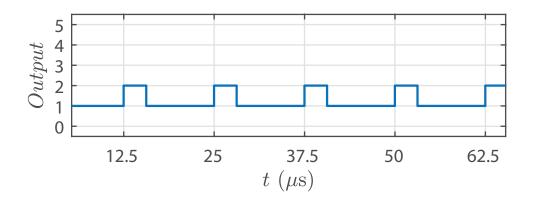

|-----|-------------------------------------------------------------------------------------|----|

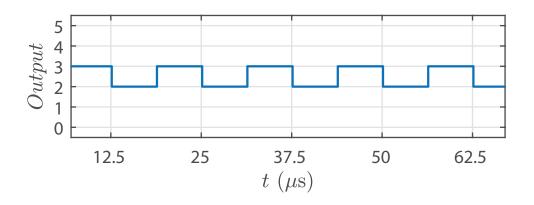

| B.2 | PS-PWM waveform for $m^{dc} = 0.25$ and $m^{ac} = 0. \ldots \ldots \ldots \ldots$   | 68 |

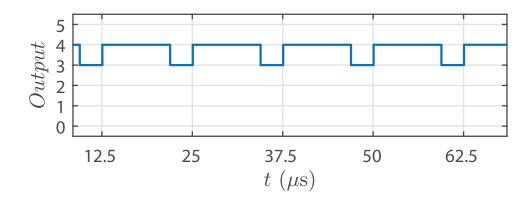

| B.3 | PS-PWM waveform for $m^{dc} = 0.5$ and $m^{ac} = 0.$                                | 68 |

| B.4 | PS-PWM waveform for $m^{dc} = 0.75$ and $m^{ac} = 0. \dots \dots \dots \dots \dots$ | 69 |

| B.5 | PS-PWM waveform for $m^{dc} = 1$ and $m^{ac} = 0$                                   | 69 |

| B.6 | PS-PWM waveform for $m^{dc} = 0.5$ and $m^{ac} = 0.25$                              | 69 |

| B.7 | PS-PWM waveform for $m^{dc} = 0.5$ and $m^{ac} = 0.4$ .                             | 70 |

| B.8 | PS-PWM waveform for $m^{dc} = 0.5$ and $m^{ac} = 0.6$                               | 70 |

| B.9 | PS-PWM waveform for $m^{dc} = 0.5$ and $m^{ac} = 1$                                 | 70 |

| C.1 | Experimental circuit board of the submodule.                                        | 72 |

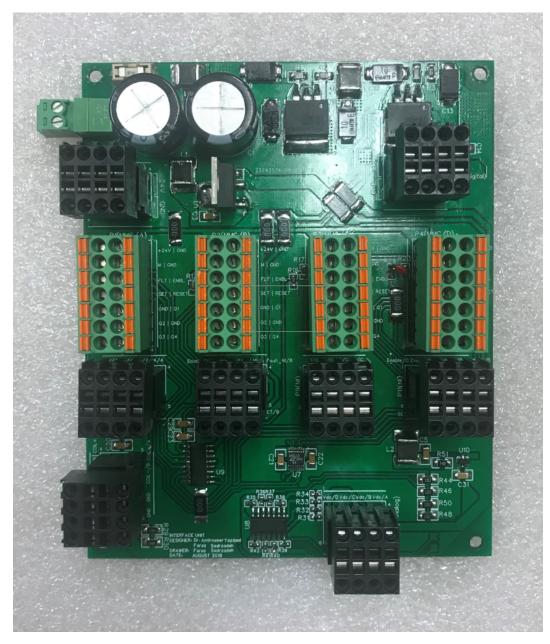

| C.2 | Experimental PCB of the interface board.                                            | 73 |

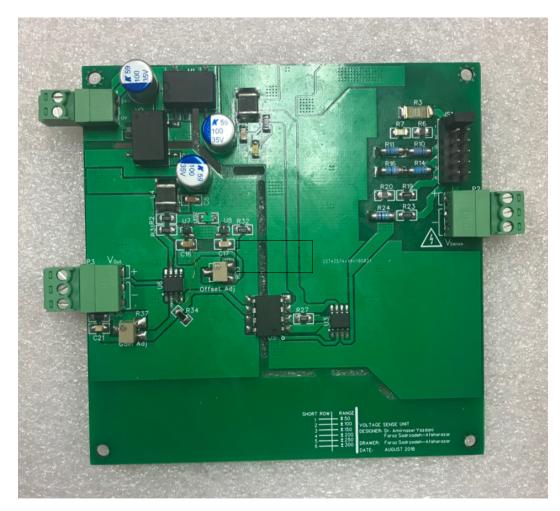

| C.3 | Experimental PCB of the voltage sensor board.                                       | 74 |

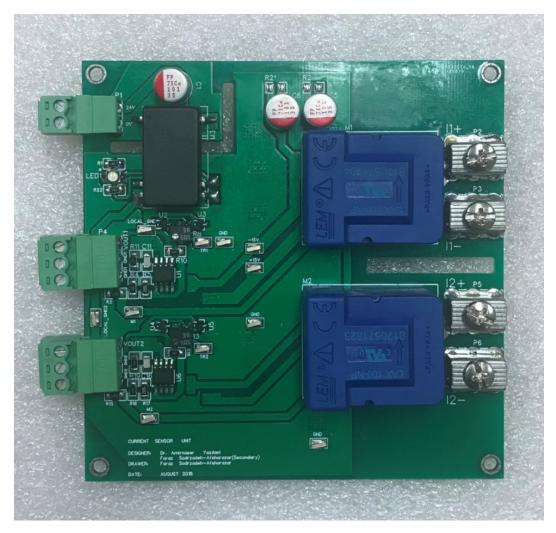

| C.4 | Experimental PCB of the current sensor board.                                       | 75 |

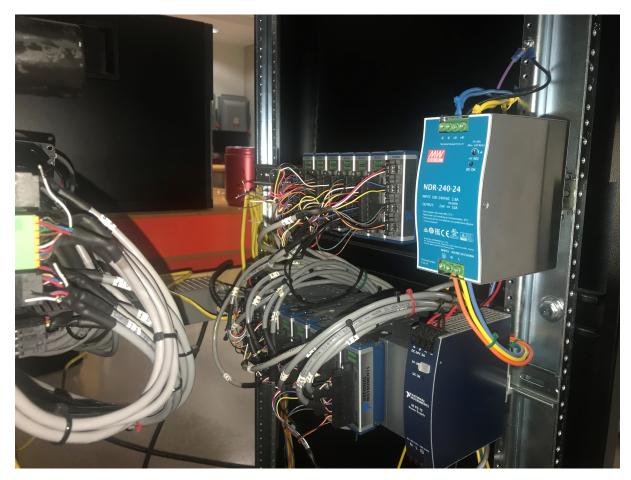

| C.5 | National Instruments CompactRIO-9082 installed inside of the cabinet                |    |

|     | and connected to the converter                                                      | 76 |

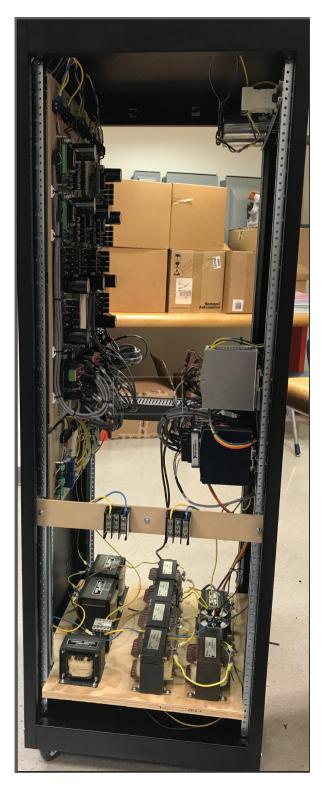

| C.6 | Submodule and interface boards connected and assembled inside the cabinet.          | 77 |

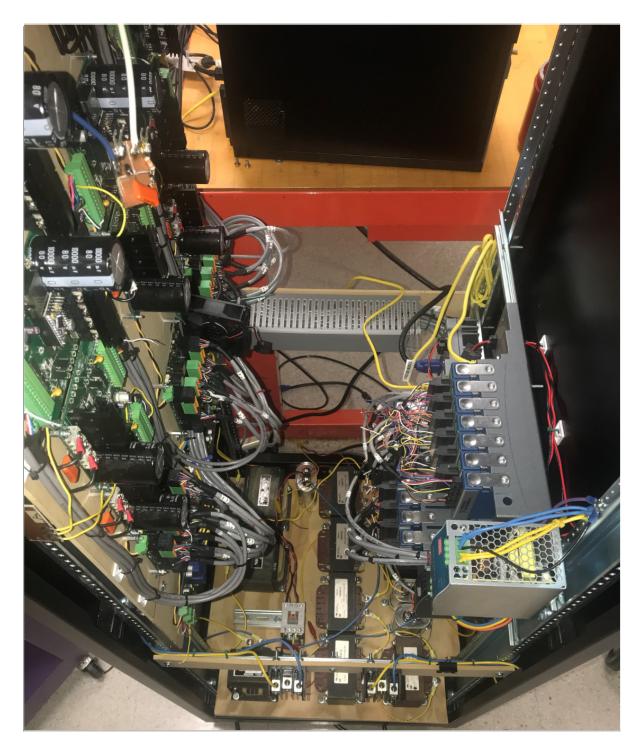

| C.7 | Inductors and contactors used in the converter.                                     | 78 |

| C.8 | A top-down view of the inside of the cabinet                                        | 79 |

| C.9 | The fully assembled cabinet as seen from the outside                                | 80 |

## **Convention for Notations**

For clarity and consistency, the following is used in this thesis.

- Variables that are constant are represented using upper case characters (e.g.,  $P_{max}$  and  $V_{cn}$ .

- Variables that are varying are represented lower upper case characters (e.g.,  $v_1$  and  $i_c$ .

- Constant and time varying components of composite variables are denoted with the superscripts dc and ac respectively (e.g.,  $v_{\Delta}^{ac}$  and  $v_{t}^{ac}$ ).

- The average value of a time varying component is denoted by an overline (e.g.,  $\overline{v_1 i_1}$ ).

# List of Abbreviations

| DIN     | Deutsches Institut fr Normung      |

|---------|------------------------------------|

| EMI     | Electromagnetic Interference       |

| F2F     | Front-to-Front                     |

| HV      | High Voltage                       |

| HVDC    | High Voltage Direct Current        |

| LV      | Low Voltage                        |

| MMC     | Modular Multilevel Converter       |

| MV      | Medium Voltage                     |

| NI-cRIO | National Instruments CompactRIO    |

| PI      | Proportional Integral              |

| PSCAD   | Power System Computer-Aided Design |

| PWM     | Pulse-Width Modulation             |

| SM      | Submodule                          |

| VSC     | Voltage-Sourced Converter          |

## Nomenclature

- $\alpha$  Phase shift between upper and lower arm voltages

- $\delta_k$  Reference offset for local voltage regulation

- $\omega$  Angular frequency of converter AC component

- $\omega_b$  Bandwidth of system

- $\omega_c$  Crossover frequency of compensator

- $\omega_m$  Angular frequency of the modulating waveform

- $\phi$  Phase shift between adjacent PWM carriers

- $\tau_i$  Integral time constant

- d Conversion ratio of the converter

- $e_{ck}$  Error associated with the  $k^{th}$  submodule capacitor voltage

- $f_{sw}$  Switching frequency of submodules

- $i_m$  Amplitude of the AC component of  $i_c$

- $i_1$  Current of the upper arm

- $i_2$  Current of the lower arm

- $i_c$  Common mode current of the converter

- $i_t$  Output current of the converter

- k Index of submodule

- $K_1$  Compensator function for the output current

- $K_2$  Compensator function for the input current

- $K_{cap}$  Proportional gain of local voltage regulation

- $K_i$  Integral gain of compensator function

- $K_p$  Proportional gain of compensator function

- L Arm inductance

- $L_e$  Effective arm inductance seen by the converter output

- $L_f$  Output filter inductor

- M Number of submodules in an arm

- m Modulation index

- $m_k$  Modulation index of the  $k^{th}$  submodule

- $p_1$  Power of the upper arm

- $p_2$  Power of the lower arm

- $P_{dc_1}$  DC power of the high voltage side

- $P_{dc_2}$  DC power of the low voltage side

- $P_{max}$  Maximum power transferable by the converter

- *R* Arm resistance

- $R_e$  Effective arm resistance seen by the converter output

- $R_f$  Output filter resistance

- $v_{\Delta}$  Difference of the arm voltages

- $v_{\Sigma}$  Sum of the arm voltages

- $v_m$  Amplitude of the AC component of  $v_t$

- $v_t$  Output voltage with respect to DC side midpoint

- $v_1$  Voltage of the upper arm

- $v_2$  Voltage of the lower arm

- $v_{c_k}$  Voltage of the  $k^{th}$  submodule capacitor

- $V_{c_n}$  Nominal submodule capacitor voltage

- $v_c$  Voltage of the submodule capacitor

- $v_{dc_1}$  Voltage of the high voltage side

- $v_{dc_2}$  Voltage of the low voltage side

- $v_{dc}$  DC voltage

- $v_{SM_k}$  Output voltage of the  $k^{th}$  submodule

- $v_{SM}$  Output voltage of a submodule

# Chapter 1

## Introduction

### 1.1 Background and Motivation

In recent years, there has been an increased demand for a switch to renewable energy sources from the traditional fossil fuel sources. Moreover, an increase in carbon emissions over the past few decades has resulted in a global effort to curb the impact of fossil fuels on the environment. In 2014, it was estimated that around 77% of the energy used in the world was generated from fossil fuels, a percentage that is too large to sustain in the future [1].

Studies have shown that 30% of the fossil fuels extracted annually around the world are used for electric power generation, and that 40% of all energy related carbon emissions originate from fossil fuels used to generate electricity. Also, considering that 80% of the energy harvested from these fossil fuels is lost in the chain from the energy harvesting stage, to the end consumer use [1] means that there is a need for the harvesting and efficient transmission of cleaner energy sources. The need for higher efficiency in the harvesting and transmission of energy has become a primary focus for scientists and engineers across the world, and as a result the use of renewable energy sources has become a hot topic in recent years. In fact, the US Department of Energy estimates that 35% of the energy generated in the US will be done solely by wind energy in the year 2050 [2].

Still, a shift in the current paradigm is required in order to achieve the aforementioned goals of harvesting and transmission, and thus the state of the art must continue to be pushed forward. In order to do so, changes must be made to the framework that is in place at the moment. One of the main changes is the integration of the renewable energy sources into the already existing power grid. However, such an integration can be made much more effective and efficient if HVDC grids are used rather than the existing AC grids [3], [4], due to the nature of the energy sources such as off-shore wind farms.

In an off-shore wind farm, the wind turbines are set up in large bodies of water, and the energy that is generated by the turbines is transmitted to a power station via cables that are submerged in water. In this case, the use of a DC grid as opposed to an AC one is a much better option, as DC transmission lines are not susceptible to reactive power losses the same way that AC lines are, an effect which is amplified when the wires are submerged in water [1], [2], [5]. Furthermore, when compared to AC transmission lines, DC lines have lower costs and lower power losses when compared to their AC counterparts for a comparable power capacity [5]. Lastly, another great benefit of the DC grid is that the frequencies of the sending and receiving ends are independent of one another which offers a great deal of versatility to the system [2].

Traditionally, HVDC grids have been developed for point-to-point bulk energy transmission. However, as the grids become more and more elaborate, the interconnection of different grids is necessary. There are two prominent cases where the interconnection of DC grids takes place: the interconnection of two HVDC transmission grids are, or the connection of a medium voltage (MV) DC generation system (such as a wind farm) to an HVDC transmission grid [6], [7]. In both cases, one of the biggest challenges is to provide an interface between the two grids, as they will generally be operating at different voltage and/or power levels.

Based on the discussion thus far, it is clear that there is a need to interface either medium voltages to high voltages, or high voltages to other high voltages. To address this need, the DC grids make use of DC-DC converters when converting between different voltage or power levels. However, when operating at medium to high voltages, the conventional two-level voltage-sourced converter (VSC) proves to be insufficient [1], [5], [8]. For efficient operation at MV and HV levels, mulitlevel converters are often used as they offer benefits that the conventional two-level VSC cannot.

One class of mulitlevel converter that is often used for the aforementioned types of HVDC applications is the Modular Multilevel Converter (MMC) [7], [9]–[21]. In essence, the MMC is similar to the two-level VSC, but instead of using a semiconductor switch in each arm, the arms are made up of numerous cells of semiconductor switches. Thus, the MMC allows the larger voltage levels to be divided among multiple smaller switches and capacitors which introduces a number of benefits. First, the requirements of the ratings on all of the components can be relaxed as each submodule will see a reasonably small voltage. Second, the fact that each submodule switches between smaller voltage levels means that the voltages will have much less harmonic distortion, and that the converter will be much less susceptible to stray capacitances and generate less EMI [1]. Next, the fact that the DC storage element is in each individual cell of the MMC, the converter does not require a large DC link capacitor [8]. And finally, the redundancy of the submodules makes the MMC much easier to maintain and makes it more convenient to deal with in the event of a fault, as faulty or damaged submodules can be bypassed as desired [22].

Before getting into the details of this thesis, it is important to understand what the state of the art is in regards to this particular area. Hence, the following section will present a literature review of the concepts and topics that are relevant to this thesis.

### 1.2 Literature Review Pertinent to Thesis Objectives

In this section, a review of the work that has been done thus far in the literature will be presented. The main focus of this review will be the different topologies and control strategies used in MMCs implemented as DC-DC converters. Furthermore, the fault handling capabilities of the DC-MMC is also of interest.

In general, the DC-MMC has been reported in two main configurations: the two stage DC-DC converter, and the direct DC-DC converter. In the conventional two stage DC-DC converter, two DC-AC MMCs are connected in a front-to-front (F2F) configuration through an intermediate transformer [7], [20], [23], [24]. Of course, the introduction of an intermediate stage results in increased weight, cost, and losses in the converter, and so the directly connected DC-DC converter has been discussed in [14], [15], [21], [25]–[28] where the intermediate stage is removed altogether. In order to successfully remove the intermediate stage while retaining the desired DC-DC power conversion, an AC circulating current must be present in the upper and lower arms of every phase in the converter to maintain the necessary energy balance between the arms of the DC-MMC [29]–[33].

To have a feasible and economical converter, the MMC must be able to handle faults and have some fault tolerance. As such, a great deal of work has been done on the fault handling capabilities of the MMC, both from a topological aspect, and through the use of elaborate control strategies. First, in [34] a fault blocking control technique is presented for the F2F topology where the converter continues to operate while connected to the faulty side with reactive current absorption. This technique is reported to achieve a greater DC fault current declining rate, while also ensuring maximum power transfer between the interconnected DC grids. However, as mentioned before the F2F topology includes an intermediate transformer which increases the weight, cost, and most importantly losses in the system. Therefore, the remainder of this review and thesis will focus on the direct DC-DC converter topologies which eliminate the intermediate stage altogether.

In order to eliminate the need for an intermediate transformer, several different converter topologies have been presented. In [27], a transformerless topology is discussed which implements crossly connected upper and lower arms of the MMC using capacitors. The resulting AC and DC power loops formed by the capacitors allow for power balance between the primary and secondary sides. Next, in [35], a topology has been presented which replaces the intermediate transformer using an LCL-based DC-DC converter. Additional converter topologies including the thyristor-based high-ratio converter, rotating capacitor converter, switching-module converter, and resonant step down converter are presented in [36]–[39] which all allow for the elimination of the intermediate transformer. However, as discussed in [27], each topology comes with its own drawbacks. For instance, the rotating capacitor converter and switching-module converter have a discontinuous DC current at the primary and secondary side, while the resonant step-down converter loses its bidirectional power transmission capability when trying to achieve a high voltage ratio between the primary and secondary sides.

From the control point of view, the direct implementation of the DC-DC MMC requires the injection of an AC circulating current in order to implement a closed loop control of the converter. However, the introduction of this circulating current into the converter can result in a degradation of the converter's efficiency [30]. In order to preserve the efficiency of the converter, the AC current needs to be minimized. In [40], a control strategy is presented which regulates the DC-link currents, ensures that the submodule capacitor voltages are balanced, and most importantly that the magnitude of the AC current is minimized. Next, in [41], an enhanced closed-loop control strategy which increases power transfer capabilities while also reducing the ac circulating current of the converter is presented. Furthermore, the harmonic content of the AC circulating current is also of interest, as in [42] where the second harmonic component of the circulating current is controlled in order to reduce power losses and balance the submodule capacitor voltages. Additional control techniques such as in [43] have also been presented, but the approach is more complicated as it makes use of modelling the converter in the d-q frame.

Finally, the topological solutions for increasing the fault handling abilities of the converter have also been a focus in the literature. In [29], a transformer less hybrid MMC is presented which uses a combination of half-bridge and full-bridge submodule arms. The lower and shunt arms of the MMC are made up of half-bridge submodules, whereas the upper arm is made up of full-bridge submodules. By introducing a shunt arm of halfbridge submodules, this configuration is capable of eliminating the output filter entirely. At the same time, this topology provides bidirectional fault ride through capabilities as a result of the full-bridge submodules used in the system, but still uses a lower number of switches than if the system was made up of full-bridge submodules entirely. The concept of bidirectional fault handling is further explored and considered for the application of an HVDC interconnect in [44] where a topology is introduced that features bidirectional power flow, step-up and step-down operation, and most importantly, bidirectional fault blocking similar to that of a dc circuit breaker, without actually using a circuit breaker, using multiple interleaved strings of submodules in order to perform the power conversion. In [45], a fault protection scheme for MMCs using half-bridge submodules is introduced which replaces the typical bypass thyristors found in the submodules with an independent modular rectifier bridge. Then, a switch with negligible losses is introduced to isolate the MMC in the event of a fault while the rectifier bridge suppresses the fault current by introducing a reverse DC voltage. Finally, [46] examines the different DC protection design choices and their impacts on the DC fault recovery of the MMC with half-bridge submodules. Also, a DC circuit breaker controller is developed along with a blocking scheme to limit the DC side fault current.

Having illustrated a clear picture of the work done thus far, the following section will introduce the objectives of this thesis.

### 1.3 Thesis Objectives

Based on a review of the literature, it is clear that there is a need for a DC-DC MMC that can provide DC fault handling capabilities. Thus, the objective of thesis is to present a DC-DC converter that can meet this requirement. In particular, a modular multilevel converter implemented as a DC-DC converter will be explored in detail along with the closed loop control of the converter. The objective of the control technique will be to control the current of the converter such that DC faults on the input or output side can be handled safely by limiting the input or output current. In order for the MMC to operate as intended, the submodule capacitors in the arms of the MMC must act as a string of voltage sources. To ensure that this is indeed the case, there is a need for a closed loop control of the MMC such that it exhibits the desired characteristics. Moreover, since the input and output powers of any converter must also be controllable in some manner, the challenge of controlling the MMC can be broken into three main parts: the capacitor control, input power control, and output power control.

Therefore, the main objective of this thesis can be further broken down to consider control techniques by which all of the powers associated with the MMC can be completely regulated. As such, three main control loops are required which are dedicated to the input power, output power, and capacitor voltages. Moreover, it is expected that the concepts presented in this thesis should be verifiable by a practical system, and so a secondary objective is to present a fully functional converter that operates based on the theory presented in this thesis.

### 1.4 Thesis Structure

This thesis is categorized into five unique chapters, including this one. Here, an introduction of the converter and its relevance to the state of the art were presented along with some objectives for this thesis. In Chapter 2, the theoretical background of the MMC will be presented. First, the principles of operation will be discussed in detail to provide a fundamental understanding of how the MMC operates. Next, the mathematical modelling of the entire converter will be done considering a general system. Then, the steady state characteristics of the converter will be examined followed by a control methodology that can be used to guarantee that the steady state characteristics are realized. Furthermore, the synthesis of the arm voltages in a multilevel topology require some explanation. Finally, a numerical case study will be presented which will serve as a foundation for the simulation and experimental sections.

In the third chapter, the system presented at the end of Chapter 2 will be simulated using the PSCAD software. The simulation will subject the converter to several different cases in order to test and validate the proposed theory of Chapter 2.

Next, Chapter 4 will discuss the details of the physical implementation of the converter, along with experimental results from the hardware setup. The experimental results will be compared directly with the simulation results and the expected theory so as to further validate the theoretical concepts discussed in Chapter 2.

Finally, Chapter 5 will summarize the contributions and findings of the thesis, while also discussing potential future works to elaborate upon in related areas. Furthermore, the main body of the thesis will be followed by some appendices which will present details relating to the experimental setup including the hardware used, and details related to the control platform.

The main body of the thesis will be followed by a series of appendices which contain details related to the physical implementation of the converter.

## Chapter 2

## Theoretical Operation of the MMC Based DC-DC Converter

To fully understand the operation of the MMC, the theoretical basis of the converter must be discussed in detail. In this chapter, the principles of operation of the MMC will be introduced based on the two-level VSC. Then, the mathematical model of the converter along with its steady state characteristics will be presented along with some control techniques for the output and input power. Finally, a numerical case study will be presented in order to set the stage for the following chapters.

### 2.1 Principles of Operation

Before delving into the details of the MMC, a good starting point is the simple twolevel voltage source converter. In this section, the principles of operation of the MMC will be presented based on the simple two-level VSC. Once the operation of the VSC is understood, the discussion will shift to the broader concept of the MMC.

#### 2.1.1 The Two-Level VSC as a Building Block

While the MMC consists of a large number of submodules in general, it is a much simpler task to begin with the fundamental building block of the converter: the two-level voltage source converter. Since the MMC is essentially a number of strings of two level VSCs connected in series, by understanding how the two level VSC operates one can quite easily understand how the MMC operates. The simplest topology of the two level VSC is the half bridge configuration. In this configuration, the two semiconductor devices form a complementary pair, meaning that when one is active or conducting, the other is turned off and not conducting. Like any VSC, there is an energy storage element, which is often referred to as the DC link capacitor. The purpose of this capacitor is to maintain the DC side voltage at a fairly constant level for a reasonable portion of a fundamental cycle. The operation of the two-level VSC requires that the gates of the two semiconductor devices be fed with gating pulses. These gating pulses are used to control when the semiconductor device is in the on state (conducting) or off state (cut

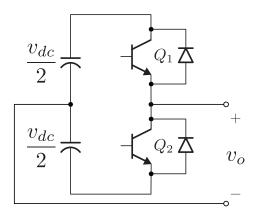

Figure 2.1: Basic two level voltage-sourced converter.

off). When the upper device is fed with a high pulse, the output of the VSC will have a value equal to the positive rail voltage of  $v_{dc}/2$  which is the voltage of the DC side capacitor. Conversely, when the lower device is active, the output of the VSC is  $-v_{dc}/2$ . As such, by generating the desired patterns of the gating pulses, it is possible to control the output voltage of the VSC. To describe the output of a two-level VSC, the variable s, which denotes the state of the devices, can be introduced. Simply put, when s assumes a value of 1, the output is connected to the positive DC rail, and when s is -1, it is connected to the negative DC rail. Mathematically,

$$v_o = s \frac{v_{dc}}{2} \tag{2.1}$$

Having understood how the VSC operates physically, it is important to discuss how the switching instances of the devices can be determined in order to control the output voltage of the converter. The most common way to determine when the devices should be turned on or off is by employing pulse-width modulation (PWM). PWM is an operation in which two waveforms, referred to as the modulating wave and carrier wave are compared to one another, and at the intersection points of these two waveforms the devices switch states. A key quantity that is used in PWM is referred to as the modulation index, m. The modulation index is used to relate the DC side voltage to the fundamental component of the modulated voltage as follows:

$$\hat{v_o} = m \frac{v_{dc}}{2} \tag{2.2}$$

Therefore, the modulated voltage can be expressed as

$$v_s = \frac{mv_{dc}}{2}cos(\omega_m t) \tag{2.3}$$

where  $\omega_m$  is the frequency of the modulating or reference waveform. It should be noted that (2.3) is only the fundamental component of the modulated voltage. In reality, the modulated voltage consists of a large number of harmonics since it is generated by the switching of semiconductor devices. Still, by ensuring that the carrier frequency is much larger than the modulating signal, the modulated voltage will more accurately represent an analog signal instead of a digital signal. Also, while the sharp changes in voltage levels will create higher-order harmonic content, these harmonics do not create significant currents in the system and can therefore be ignored in most cases [1], [8].

In this section, the two-level VSC was introduced in order to serve as a building block for the MMC. In the following section, the general concept of the MMC will be introduced and discussed.

#### 2.1.2 The Modular Multilevel Converter (MMC)

Having explored the basic VSC topology, the discussion can be expanded to consider the MMC. Simply put, the MMC is a multilevel converter that consists of a string of two-level VSCs. In the general case, each VSC is usually referred to as a submodule (or sometimes referred to as a cell or chain link), and a string of submodules is referred to as an arm [9]. Typically, there are two types of submodules; half-bridge submodules, and full-bridge submodules, which as the names suggest, are made up of semiconductor switches configured as a half-bridge and full-bridge, respectively. While there are more sophisticated submodule configurations, the typical MMC makes use of either half or full bridge submodules [30].

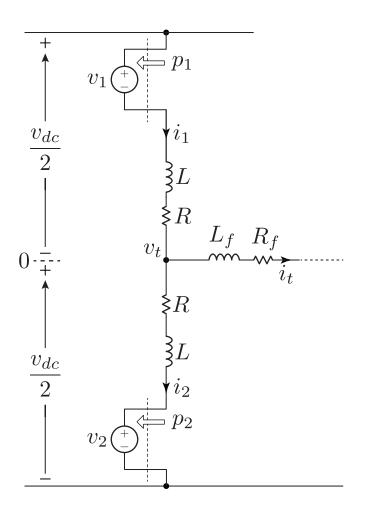

As seen in Fig. 2.2, two arms, two DC terminals (a high voltage and low voltage side), and a relatively small inductor in each arm. In the two-level VSC, the inductors are required to allow fast current changes during the commutation of phase legs. However, in an MMC the inductors serve a different purpose since the commutation takes place in the submodules, meaning that the rapid change which takes place in the two-level VSC does not exist in the MMC arms [1], [8]. Instead, in the MMC the inductors are required to prevent direct parallel connection of voltage sources (which is implemented by the submodule strings). In Fig. 2.2, the arm voltages are represented by two voltage sources. However, in reality these two voltage sources will be replaced with strings of submodules. Later in this section, it will be shown that under certain conditions, the submodules can be simplified to be modelled as voltage sources.

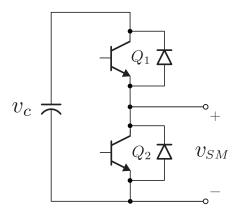

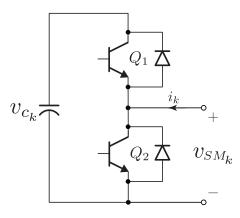

As seen in Fig. 2.3, a half-bridge submodule consists of one two-level VSC, that is, two series connected semiconductor switches connected across a DC capacitor which is used to maintain a constant voltage. In order to create a chain of such submodules, the two external terminals of the submodule (the node labelled  $v_o$  in Fig. 2.3, and one of the DC capacitor terminals) are connected in series with other submodules. Based on the conduction states of  $Q_1$  and  $Q_2$ , there are two possible switching states for the submodule: bypass or insertion. When the submodule is in the bypass state, the  $Q_2$ is active. As a result, the submodule acts as a short circuit and exhibits a negligible voltage drop. On the other hand, when the submodule is inserted,  $Q_1$  is active, meaning the submodule exhibits a voltage equal to the DC capacitor voltage [9]. Thus, the output voltage  $v_o$  of each submodule can be expressed as in terms of a switching function s as seen in (2.4).

$$v_o = sV_c \tag{2.4}$$

where s is 0 for the bypass state, and 1 for the insertion state. Furthermore, using a

Figure 2.2: Generic MMC circuit configuration considering the two arm voltages to be voltage sources.