### Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2011

## Optimization of a compact thermal model for a Ball Grid Array (BGA) package using experimental data

Tayaz Fakhry Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

### **Recommended** Citation

Fakhry, Tayaz, "Optimization of a compact thermal model for a Ball Grid Array (BGA) package using experimental data" (2011). *Theses and dissertations.* Paper 694.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

### OPTIMIZATION OF A COMPACT THERMAL MODEL FOR A BALL GRID ARRAY (BGA) PACKAGE USING EXPERIMENTAL DATA

By

Tayaz Fakhry BASc. University of Tehran Tehran, Iran

September 2008

A thesis

presented to Ryerson University in partial fulfillment of the requirement for the degree of

Master of Applied Science

in the program of

Electrical and Computer Engineering.

Toronto, Ontario, Canada 2011

© Tayaz Fakhry 2011

### **Author's Declaration**

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Signature

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Signature

### **Instruction on Borrowers**

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

### Abstract

Tayaz Fakhry Optimization of a Compact Thermal Model For a Ball Grid Array (BGA) Package Using Experimental Data

Master of Applied Science, Electrical and Computer Engineering Ryerson University, Toronto, 2011

The goal of this research is to optimize a *static & dynamic* compact thermal model for a ball grid array (BGA) package using experimental data. The general objectives of thermal modeling are to increase the accuracy of electrical analysis to enhance the performance of the electronic systems. The project is focused on generating the static and dynamic compact thermal model of a Bipolar Junction Transistor (BJT) and a Ball Grid Array (BGA) based on experimental results of infrared (IR) camera system, so that the steady state and transient thermal behaviors of the package could be predicted fast with required accuracy. The approach proposed by a previous study based on generation of dynamic compact thermal model of a BGA package using simulation tools, is extended in this work to generate the static and dynamic compact model of the same package represented by a RC (thermal) network or admittance matrix based upon a methodology which couples different layers of experimental data to the error minimization notion of the problem. This optimization problem sets the temperature profile experimental data as a standard and compares the compact model's computed temperature and refines itself with a feedback, until reaching a desired point.

### Acknowledgments

First of all, I would like to express my gratitude to my supervisor, Dr. Farah Mohammadi, for accepting me as her MASc. student in Ryerson University. Her expertise, understanding, and patience, added considerably to my graduate experience and without her excellent guidance and encouragement, it would have been so much harder to finish this research.

I would like to thank my committee members Dr. Das, Dr. Rahemifar and Dr. Anpalagan for their great advices and supports.

I would also like to thank my friends and lab mates, Farnoos Farrokhi, Elahe Talebinejad and Shazzat and Mosen Marami for all the wonderful time that we shared and their help during my research.

I would like to thank Ryerson University and Department of Electrical Engineering faculty and staffs for giving me the opportunity to study in such a high reputable institute and also for the research facilities and financial assistance.

I would like to thank my parents, my brother and sister, my girlfriend, my friends and whom I love with all my heart, for all their support and tolerance.

Last but not least, I thank God for whatever I am and have right now.

## **Table of Contents**

| List of Figures                                                                         | viii |

|-----------------------------------------------------------------------------------------|------|

| List of Tables                                                                          | X    |

| CHAPTER 1                                                                               | 1    |

|                                                                                         |      |

| 1. Introduction                                                                         |      |

| 1.1 Introduction                                                                        |      |

| 1.2 Literature Review.                                                                  |      |

| 1.2.1 Thermal Analysis of Electronic Components                                         |      |

| 1.2.2 Detailed Thermal Analysis                                                         |      |

| 1.2.3 Compact Thermal Analysis                                                          |      |

| 1.3 Thesis Objective                                                                    |      |

| 1.4 Thesis Outline                                                                      |      |

| CHAPTER 2                                                                               | 7    |

|                                                                                         | _    |

| 2. Basics of BGA Compact Thermal Modeling                                               |      |

| 2.1 Introduction                                                                        |      |

| <ul><li>2.1.1 BGA Packages</li><li>2.1.2 Governing Heat Transfer Equations</li></ul>    |      |

| 2.1.2 Compact Thermal Modeling                                                          |      |

| 2.1.3 Compact merinal Modeling<br>2.1.4 Infrarered (IR) Camera in Thermal Analysis of E |      |

| 2.1.4 Infrared (in) Camera in Thermal Analysis of L<br>2.1.4.1 Infrared Camera          | -    |

| 2.1.4.2 Data Acquisition System                                                         |      |

| 2.1.4.3 Heat-sink                                                                       |      |

| 2.1.4.4 Oil Pump                                                                        |      |

| 2.1.4.5 Thermocouple and Digital Thermomet                                              |      |

| 2.1.4.6 Emmisivity                                                                      |      |

| 2.2 Summary                                                                             |      |

|                                                                                         |      |

| CHAPTER 3                                                                               |      |

|                                                                                         |      |

| 3. Software and Computing                                                               |      |

| 3.1 Introduction                                                                        |      |

| 3.2 Modelsim & Quartus II                                                               |      |

| 3.3 Infradred (IR) Camera's Dedicated Softwares                                         |      |

| 3.3.1 Researcher Software                                                               |      |

| 3.3.2 Software Development Kit (SDK)                                                    |      |

| 3.4                                    | Visual C++                                                                              |          |

|----------------------------------------|-----------------------------------------------------------------------------------------|----------|

| 3.5                                    | MATLAB                                                                                  |          |

| 3                                      | .5.1 MATLAB as a Mathematical Fitting Toolbox                                           |          |

| 3                                      | .5.2 MATLAB as an Optimization Tool                                                     |          |

| 3.6                                    | Other Software (FPGA and Power-Play Excel                                               |          |

| 3.7                                    | Summary                                                                                 |          |

|                                        |                                                                                         |          |

| CHAP                                   | TER 4                                                                                   | 40       |

| 4. F                                   | easibility Study: Generation of the Compact Thermal Model for a BJT                     | 40       |

|                                        | Introduction                                                                            |          |

| 4.2                                    | Test Setup & Literature Review for BJT 2N39014                                          |          |

| 4.3                                    | Static Compact Thermal Model for the BJT                                                |          |

| 4.4                                    | Dynamic Compact Thermal Model for the BJT                                               |          |

| 4.5                                    | Summary                                                                                 |          |

|                                        |                                                                                         |          |

| СНАР                                   | TER 5                                                                                   | 53       |

|                                        |                                                                                         |          |

|                                        | tatic & Dynamic Compact Thermal Model for BGA Using Infrared Camera                     |          |

|                                        | Introduction                                                                            |          |

| 5.2<br>5.3                             | Test Configuration<br>Parallel Current/ Power Measurements                              |          |

| 5.3<br>5.4                             | Verification of Current/ Power Measurements                                             |          |

| 5.4<br>5.5                             |                                                                                         |          |

| 5.5<br>5.6                             | Static Compact Thermal Model for a BGA                                                  |          |

| 5.0                                    |                                                                                         |          |

| E 7                                    | Dynamic Compact Thermal Model for a BGA                                                 |          |

| 5.7                                    | Effect of Smal Perturbation                                                             | 69       |

|                                        |                                                                                         | 69       |

| 5.8                                    | Effect of Smal Perturbation                                                             | 69<br>70 |

| 5.8<br>CHAP                            | Effect of Smal Perturbationl<br>Summary                                                 |          |

| 5.8<br>CHAP                            | Effect of Smal Perturbation                                                             | 69<br>70 |

| 5.8<br>CHAP<br>6. C                    | Effect of Smal Perturbationl<br>Summary                                                 |          |

| 5.8<br>CHAP<br>6. C<br>Refere          | Effect of Smal Perturbationl<br>Summary<br>TER 6<br>onclusions and Future Work          |          |

| 5.8<br>CHAP<br>6. C<br>Refere<br>Apper | Effect of Smal Perturbationl<br>Summary<br>TER 6<br>onclusions and Future Work<br>ences |          |

| 5.8<br>CHAP<br>6. C<br>Refere<br>Apper | Effect of Smal Perturbationl<br>Summary<br>TER 6<br>onclusions and Future Work          |          |

## List of Figures

| Figure 2.1: Dual Inline Parallel (DIP) Package.                                              | 8  |

|----------------------------------------------------------------------------------------------|----|

| Figure 2.2: PBGA-h and PBGA Ball Grid Arrays                                                 |    |

| Figure 2.3: PBGA-h Layout in the Literature Research (a) Cross Section (b) Bottom View       |    |

| Figure 2.4: (a) Top1, Top2, Side areas, (b) Lead1, Lead2, Bottom areas.                      |    |

| Figure 2.5: Proposed Test Setup for Simple BJT Introducing Different Equipment.              |    |

| Figure 2.6: Infrared (IR) Camera SC4000.                                                     |    |

| Figure 2.7: Thermal Resistance Circuit                                                       | 19 |

| Figure 2.8: Temperature Distribution of the DUT with Air Cooling.                            |    |

| Figure 2.9: Temperature Measurement with Turbulent Oil Flow                                  |    |

| Figure 2.10: Temperature Measurement with Turbulent at Angle of 45°.                         |    |

| Figure 2.11: Temperature Measurement with Laminar Oil Flow                                   |    |

| Figure 2.12: Utility Pump.                                                                   |    |

| Figure 2.13: Emissivity Effect of Temperature Measurement of the DUT.                        | 23 |

| Figure 3.1: Flowchart of Software Application.                                               |    |

| Figure 3.2: Parts of Verilog Code for a Music Synthesizer implemented in the BGA.            |    |

| Figure 3.3: Relatively Complex Block Diagram for a Quartus II Instruction for the FPGA       |    |

| Figure 3.4: Results for the Complex Quartus II Code.                                         |    |

| Figure 3.5: Temperature Profile of the BGA at a Given Time Frame by Showing the Physical     |    |

| BGA under its Screen before Starting the Power.                                              | 29 |

| Figure 3.6: Indicating the Implementation Process while Acquiring Temperature Profile in a   |    |

| Researcher                                                                                   | 30 |

| Figure 3.7: IR Camera's SDK Diagrams as Compomemt Layers                                     | 31 |

| Figure 3.8: First Lines of a Visual C++ Code Indicating the Libraries Maintained and the     |    |

| Command Prompt Environment.                                                                  | 32 |

| Figure 3.9: Temperature (Celsius) Profile of Junction Temperature in a BGA in a Specific     |    |

| Experiment of a Quartus II Instruction Called Load 1 which was Simple Multiplier Vs the Inde | ЭХ |

| of the Frame (× 100)                                                                         | 34 |

| Figure 3.10: Applied MATLAB Toolbox for the Same Quartus II Instruction as Figure 3.9        | 35 |

| Figure 3.11: Junction Temperature Profile for the Same Quartus II Instruction as Figure 3.9  | 35 |

| Figure 3.12: Codes of Dynamic Cost Function and Temperature Computed by the Proposed         |    |

| Mdodel                                                                                       | 37 |

| Figure 3.13: Power-Play Excel-Based Power Estimator Used to Verify the Power Measured fro    |    |

| the Same Instruction Used in Figure 3.9                                                      | 38 |

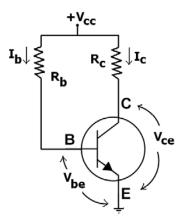

| Figure 4.1: Fixed Biased Activated BJT                                                       | 41 |

| Figure 4.2: Researcher's Focus Structure Modeled for the BJT's area to track some sample     |    |

| temperatures                                                                                 |    |

| Figure 4.3: Measured BJT Temperatures for the Second BJT; Indicating Two Almost Identical    |    |

| Rises for Temperature; Getting Cut-Off4                                                      |    |

| Figure 4.4: Measured BJT Temperatures for the Second BJT; Comparing to the First B.          |    |

| Getting Cut-off4                                                                             |    |

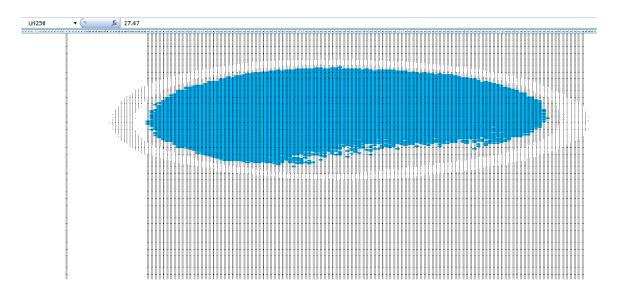

| Figure 4.5: SDK Measured BJT Temperatures for the First BJT Frame 600; Identifying           |    |

| temperature more than 31 <sup>°</sup> on Board4                                              | 14 |

| Figure 4.6: SDK Measured BJT Temperatures for the First BJT Frame 600; Identifying Some     |

|---------------------------------------------------------------------------------------------|

| Sample Cells and Average Temp on Board45                                                    |

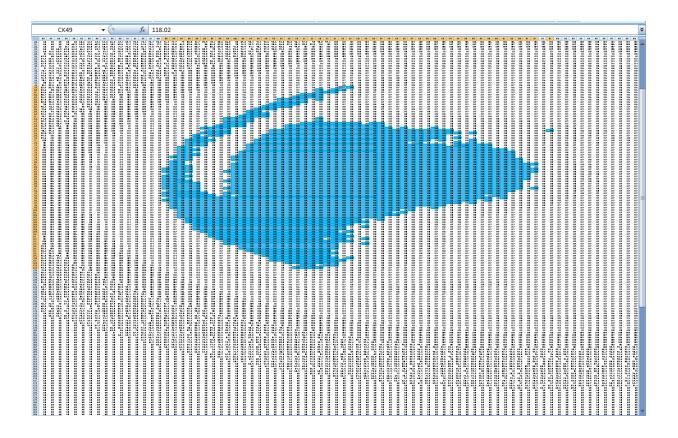

| Figure 4.7: SDK Measured BJT Temperatures for the Third BJT Frame 1200; Identifying         |

| Temperature More than 118 <sup>c</sup> on Board45                                           |

| Figure 4.8: Process of Interpolation of the Temperature Profile to Find the Dynamic Compac  |

| Thermal Model of the BJT                                                                    |

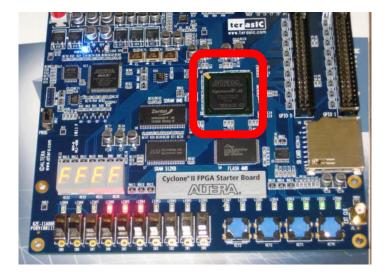

| Figure 5.1: ALTERA FPGA is a BGA Electronic Package and Device Under Test Highlighted54     |

| Figure 5.2: Power-Play Power Estimator different parameters for load 1                      |

| Figure 5.3: Power-Play Power Estimator different parameters for load 3                      |

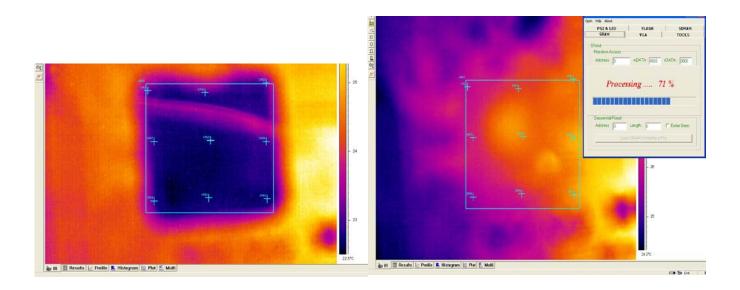

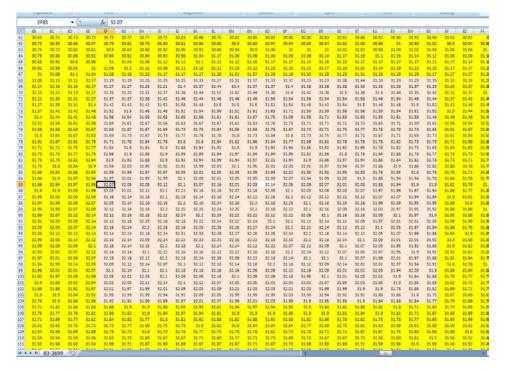

| Figure 5.4: 2700 Frames for the One of the BGA Experiments Processed by the Visual C++59    |

| Figure 5.5: Transient Analysis of the BGA under Researcher; 2D Temperature Profile at t=0S, |

| and as the 71% of the Implementation of the Instruction                                     |

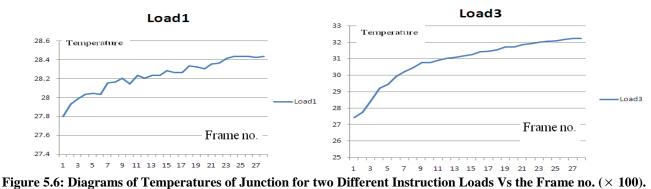

| Figure 5.6: Diagrams of Temperatures of Junction for two Different Instruction Loads Vs the |

| Index of the Frame (× 100)                                                                  |

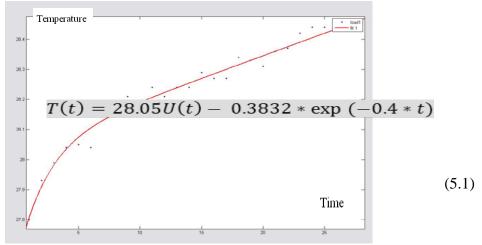

| Figure 5.7: Interpolation of Junction's Temperature Profile for Load 1                      |

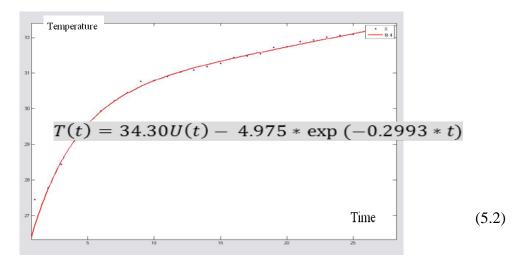

| Figure 5.8: Interpolation of Junction's Temperature Profile for Load 3                      |

| Figure 5.9: Compact Thermal Representation of a BGA                                         |

| Figure 5.10: Applying 58 Boundary conditions to find the Initial H matrix for load 1;       |

| Temperature vs. # Boundary Condition                                                        |

| Figure 5.11: Applying 58 Boundary conditions to find the Initial H matrix for load 3;       |

| Temperature vs. # Boundary Condition                                                        |

| Figure 5.12: Optimization Block and Boundary Condition Refinement Using MATLAB              |

| Optimization Toolbox                                                                        |

## **List of Tables**

| Table 2.1: Different Nodes in the Layout and Their Surface Areas                                                      |

|-----------------------------------------------------------------------------------------------------------------------|

| Table 0.1: Room's Temperature in 10 Consecutive Days before the Experiment                                            |

| Table 4.2: Power Dissipation Computed on Measured Output Current during the Experiments.43                            |

| Table 4.3: Power Dissipation Computed on Measured Output Current during the Experiments.50                            |

| Table 4.4: Static and Compact Thermal Model for a BJT in Two Different Conditions ofDifferent Ambient Temperatures.52 |

| Table 5.1: Parameters for the BGA Test Configuration                                                                  |

| Table 5.2: Maximum Current Generated by the BGA with Different Experiments                                            |

| Table 5.3: Relative Errors of the Powers of BGA with the Estimation of Power-Play Estimator                           |

| File                                                                                                                  |

| Table 5.4: Flowchart of Generating the Compact Thermal Model for a BGA60                                              |

| Table 5.5: Admittance Static Matrix for the Heat Transfer Equation                                                    |

| Table 5.6: Capacitors' value of Dynamic Compact Thermal Model                                                         |

| Table 5.7: Static & Dynamic Compact Thermal Models for a BGA Obtained                                                 |

| Table 5.8: Dynamic Compact Thermal Model Absolute and Relative Errors under SmallPerturbation                         |

# **CHAPTER 1**

### **1.1 Introduction**

More component density in electronic boards, more speed of VLSI circuits and unwillingly more power dissipation of fast electronic devices seem to be bundled together. Dramatic increase of applications of such circuits and devices, urges the *thermal analysis and power management* studies of such systems a vital design requirement. The amount of dissipated power by the chip is directly related to its temperature which is a crucial parameter in electrical behavior of electronic components, circuit performance, and reliability of the electronic system. Thermal analysis is an important part of modern electronic design thus that enables the designer to calculate the critical thermal variables as key factors in electrical analysis: *component, package or system level*. Depending on the level of the design an electronic designer is engaged with, one of these analyzing levels must be chosen that gives out only the sufficient and relevant information about the thermal behavior of the subject of the thermal analysis [1-5].

In many cases of thermal analysis most of the information provided as the detailed model is unnecessary for the consumer because it includes the thermal characteristics of undesired locations. A smaller model that is capable of calculating only the hot spots, the temperatures and heat fluxes at some desired locations can help the designer to perform the thermal analysis much more easily and quickly with the required accuracy. Such model is called Compact Thermal Model (CTM). CTM can be generated from the detailed numerical model or the experimental data. This thesis focuses on generation of CTM at package level using experimental test.

The key to successful experimental test (for the purpose of thermal analysis) is the ability to obtain comprehensive and accurate prediction of temperature gradients influencing the quality of electronic products under near real-time operating conditions. However, the commonly used method of gathering these temperature gradients using thermocouples is limited by the large number of points to be monitored and the small size of the components being measured. Connecting tens to hundreds of thermocouples is very time consuming. In addition, thermocouples can act as heatsinks and conduct away heat, affecting the accuracy of measurements since the action of the heatsink may lower device temperatures.

Infrared (IR) thermal imaging system is a method which addresses the abovementioned issues by providing comprehensive two-dimensional temperatures gradients of components under test [6,7], [46]. This is accomplished without the need to make contact with the components. Therefore, the thesis focuses on generation of CTM at package level using experimental testing data obtained from infrared thermal imaging system.

### **1.2 Literature Review**

#### **1.2.1 Thermal Analysis of Electronic Components**

There are three levels of macroscopic thermal analysis and depending on the level of the design an electronic designer is engaged with, one of these analyzing levels must be chosen that gives out only the sufficient and not unnecessary information about the thermal behavior of the subject of the thermal analysis. These levels are as follows:

#### **1.2.1.1 Component Level of Thermal Analysis**

In component level a single component or some specific components of the electronic circuit are the subjects of thermal analysis. It's desirable for the designer to study the effect of thermal behavior of components on their own electrical behaviors and the mutual effects of the thermal behaviors of components on the electrical behaviors and operating points of their adjacent components. This level of analysis is usually used in electro-thermal analysis of the electronic circuit [6-9]. Electro-thermal analysis of the circuit is necessary, when there are some components which play key roles in the circuit

and it's very important for the designer to predict their electrical and thermal operating points in order to design a stable, predictable, and reliable circuit. Unlike ordinary electrical analysis by which the electrical operating point of the circuit is calculated for a fixed and predetermined temperature (usually room temperature), electro-thermal analysis performs both electrical and thermal analyses concurrently. It is well known that electrical current flowing through the materials causes heat dissipation and temperature elevation. This phenomenon is called Joule heating and in most cases changes the electrical operating point of the component and the circuit in which it is operating. Electrical analysis with fixed temperature thus is not sufficient for an accurate analysis and electro-thermal analysis should be performed so the mutual effects of temperature variation and electrical operating point variation are taken into consideration.

### 1.2.1.2 Package Level of Thermal Analysis

This level of thermal analysis is useful when the electronic designer needs to calculate the temperature profile and inward/outward heat fluxes of an electronic package working as a part of an electronic system. A package can be analyzed thermally using a simulation software or by its compact thermal model as explained later in this chapter and the rest of this work. Detailed analysis of package is expensive in terms of money and simulation time but it gives a relatively accurate temperature profile for every location inside or on the surface of package. Compact thermal model of package on the other hand is fast, almost free, and easy to use but it calculates the average temperature and heat flows for predetermined volumes inside or areas on the surface of the package with acceptable accuracy. The subject of this project is thermal analysis in package level and in future chapters detailed and compact modeling of electronic packages will be explained thoroughly.

#### **1.2.1.3 System Level of Thermal Analysis**

Accurate thermal analysis of a complex electronic system including several packages, discrete elements, printed circuit boards, connectors and mechanical parts, heat sinks and cooling mechanisms, and covering cases is almost impossible with currently available thermal simulation softwares, because of its complexity and the large number of thermal characteristics and the excessive amount of unnecessary information carried in the output of the analysis. The alternative solution is to separately, generate the compact model of packages, boards, and other parts of the system and use them as the building blocks of the thermal model of the system. This system level model is then used to generate the thermal variables at the desired locations within the system.

#### **1.2.2 Detailed Thermal Analysis**

The temperature profile (temperature at any desirable location of a solid object) and inward/outward heat flux from the surfaces of the solid object obey the heat transfer equation by conduction (this will be explained in Chapter 2 in more detail). However, if an object with a complex geometry such as a modern electronic package with several layers of materials is the subject of the thermal analysis problem, it's impossible to find an analytical solution for this equation.

One of the first alternatives to overcome this problem is employing experimental methods developed for generating the heat transfer equation with specified boundary and initial conditions and obtaining the temperature profile and outward/inward heat fluxes as they occur during the experiment. Some other ways, like numerical methods, do exist in the literature where each of these methods have their own privileges and drawbacks; numerical methods such as Boundary Elements Method (BEM), Finite Difference Method (FDM), and Finite Elements Method (FEM). Detail discussion and explanation on these methods are available in [12, 13] and other numerical analysis and heat transfer text books [14]. The first issue that rises immediately is the cost of analysis in terms of tools, time and accessibility. Unless the object has a very simple geometry, a high price software package such as ANSYS© [16] or COMSOL© [18] *Multi-physics* specially designed for numerical calculation of partial differential equations is needed to be

installed and made available on a powerful machine and the computation time is also considerably long. This makes the use of numerical method expensive and inefficient for the customer of the electronic package and makes the experimental method ideal for such a case; the second issue is the confidentiality of the electronic packages. Furthermore, to perform the detailed thermal analysis of an electronic package, exact information about the internal structure of the package, dimensions and physical properties such as thermal conductivities, thermal capacities, and densities of the different layers of the package are necessary in a simulation solution. Package producers, however, usually consider these specifications as classified information and don't publish them in the public domain. This makes the detailed thermal analysis hard for the package customer. The solution to overcome this situation is Compact Thermal Modeling (CTM) of packages using experimental data.

### **1.2.3 Compact Thermal Analysis**

There are two types of CTM: static and dynamic. Static models are capable of calculating the thermal behavior and operating point under steady state conditions [10, 20]. Dynamic models on the other hand are more complex and capable of calculating the temperature profile and heat flows during transition times in which the temperature has not reached to its final value yet or the electrical and environmental conditions are not stable [19, 44, 45, 47]. A detailed description of CTM is presented in Chapter 2, Section 2.1.3.

### **1.3 Thesis Objective**

The goal of this research is to develop an optimized *compact thermal model* of electronic package using experimental data. The objective of the compact thermal modeling process is to create a simplified model that represents the thermal behavior of the package to perform a quick thermal analysis with the required accuracy in system design process. This research project aims to create methodology to enable *rapid, precise* and *inexpensive* assessment of thermal behavior of packages in electronic equipment

under real-time experimental testing. This methodology is applied to predict the thermal behavior of the Ball Grid Array (BGA) package.

*The Static and dynamic compact thermal model* generation methodology based on experimental test data and the resistor/capacitor (RC) network approach for a typical BGA package is discussed. A feasibility study was performed to verify the proposed approach of the CTM development based on thermal measurement data. The CTM is generated and optimized by MATLAB for different work-loads for an FPGA with a PBGA-H technology.

### **1.4 Thesis Outline**

In this research we attempt to provide coverage of a methodology based on experimental test data via infrared camera system required for optimization of static & dynamic compact thermal modeling of an electronic package.

In Chapter 2, the fundamental building blocks to generate a compact thermal model of a Ball Grid Array (BGA) technology and packages were introduced. Heat conduction mechanism was discussed. The infrared (IR) thermography measurement setup and major equipments used in the experiment setup were also presented.

Chapter 3 is allocated to various proposed software blocks used in the research which have an important role on progressing these steps. A variety of experimental, code-based, object-oriented or text-based software were applied and processed sequentially or concurrently to obtain static and dynamic CTM.

Chapter 4 concentrates on the feasibility study to generate the compact thermal model for a BJT device using infrared camera system.

In Chapter 5 a methodology to generate the static & dynamic compact thermal model based on the resistor and capacitor network for a typical BGA package using experimental data are reported.

The conclusion and suggested future works are summarized in Chapter 6.

6

# **CHAPTER 2**

# Basics of BGA Compact Thermal Modeling

### 2.1 Introdution

In this chapter, different *BGA packages* and their manufacturing technology are described. Then, *Governing Heat Transfer Equations* which are the founding infrastructure of the thermal analysis dynamics are stipulated. In addition, CTM for a BGA Package is introduced. Finally, *infrared (IR) camera's application in thermal analysis of electronic package is illustrated*.

### 2.1.1 BGA Packages

There are many types of electronic packages which are divided into several categories based on the material used for fabrication, the method they are mounted on the PCB, pin arrangements, and other characteristics. For example, materials used in packages can be plastic, ceramic, or epoxy. The mounting methods include insertion, surface, chip carrier, socket, and ball grid array (BGA). Before moving to a thorough explanation about BGA packaging technology some of the other types of packages which are popular and produced by manufacturers are introduced in the following section.

**Dual Inline Parallel (DIP) package** which is also called DIL is a rectangular shape package with two parallel rows of electrical connecting pins coming out of the two sides of the package. Material used in this type of packages is either plastic or ceramic. The method of connecting DIP package to the PCB is insertion. It means the metal pins of DIP are inserted from one side of the PCB to the holes already drilled in the board and soldered on the other side of the board. Some of the characteristics of DIP are as follows:

- Lead Pitch (Pin spacing): 2.54 mm or 0.1" and 1.778 mm (0.07").

- Row spacing (the distance between the rows): 7.62 mm (0.3") and 15.24 mm (0.6").

- Pin counts (number of electrical pins): 8, 14, 16, 18, 20, 22, 24, and 28 for 0.3" row spacing and 24, 28, 32, 36, 40, 48, and 52 for 0.6" row spacing.

A typical 18 pins, 0.3" row spacing plastic DIP package [27] is shown in Figure 2.1.

Figure 2.1: Dual Inline Parallel (DIP) Package. Small Outline Integrated Circuit (SOIC), Plastic Leaded Chip Carrier (PLCC), Quad Flat Pack (QFP), Pin Grid Array (PGA) are samples of other types of traditional popular electronic packages [27-29].

The Ball Grid Array or BGA is an advanced packaging technology, which has descended from PGA. Like PGA packages one side of the BGA is fully or partially covered by electrical pins and the other side is exposed to the free or forced convection or in contact with the heat sink. Unlike other types of packages in BGA technology electrical connections between the chip and PCB are established via solder balls instead of metal pins. The process of mounting the BGA package on the PCB involves three steps:

1- BGA is precisely placed and aligned on top of the PCB so the balls are in contact with PCB pads.

2- The contact location is then heated usually by infrared heater so the solder balls start melting.

3- The last step is cooling down so the solder starts to solidify. This process of mounting is considerably more complex than what is needed for other types of packaging.

There are, however, some key advantages that make this technology desirable for microelectronic designers. These advantages are:

1- High connection density: in order to connect other types of package to the PCB, pins must be soldered. This will restrict the proximity of the pins so the danger of unwanted bridging between two adjacent pins is reduced. BGA, however, does not have this problem so the number of pins can be increased up to 1152 leads when the lead pitch is 1.0 mm.

2- Increased heat conduction: the thermal resistance between the BGA package and PCB lower than other packages. The operating temperature is, therefore, lower.

3- Low inductance of connections: the small size of leads in BGA technology compared to the metal pins reduces electrical inductance, switching noise and other distortions.

4- Higher reliability: the short length of balls compared to the pins reduces the danger of failures caused by mechanical tensions and vibrations.

There are several variants of BGA packages and some of them are as follows: Fine Ball Grid Array (FBGA), Ceramic Ball Grid Array (CBGA), Plastic Ball Grid Array (PBGA), Plastic Ball Grid Array - Heat Spreader (PBGA-H), Plastic Ball Grid Array - Multi Die (PBGA-MD), Enhanced Ball Grid Array (EBGA), Tape Ball Grid Array Package (TBGA).

Figure 2.2 illustrates two different BGA packages [30]. More information on the technology, material properties, and specification of BGA packages may be found in [22, 31].

Figure 2.2: PBGA-h and PBGA Ball Grid Arrays.

In this work the single chip PBGA-h package proposed in [1] has been selected as a case study of Compact Thermal Model (CTM) generation process in order to be consistent with the literature review study. More information can be reviewed in the datasheet of this package [21, 25].

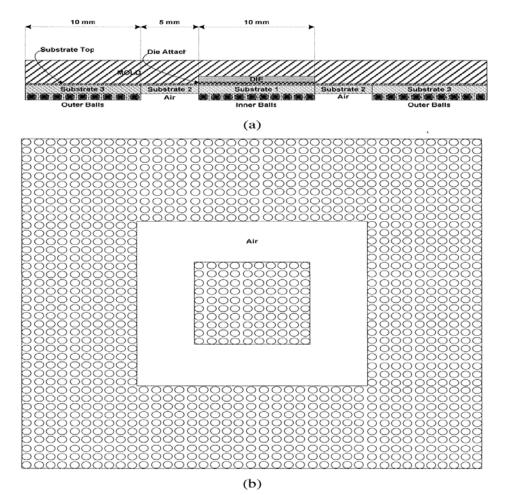

This package has several layers as follows:

- Leads or balls that establish the electrical connections between the PCB and the electronic circuit inside the package. This layer includes inner balls which will be called LEAD1 later in this work and outer balls which will be LEAD2.

- Air is the empty space between inner and outer balls.

- Substrate 1 which is located on top of the inner balls.

- Substrate 2 which is located on top of the air layer.

- Substrate 3 which is located on top of the outer layer.

- Substrate top layer which is located on top of the substrate 1, 2, and 3 layers.

- Die attach is located on top of the substrate top layer and align with the substrate 1 and inner balls layers.

Figure 2.3: PBGA-h Layout in the Literature Research (a) Cross Section (b) Bottom View.

- Die which is the silicon chip on which the electronic circuit is built and which is located on top of the die attach layer.

- Mold which is the covering material located on top and around the die and encapsulates it for protection.

These layers have been illustrated in figure 2.3 (a) which is a cross section view of the BGA package. Figure 2.3 (b) illustrate the bottom view of the package.

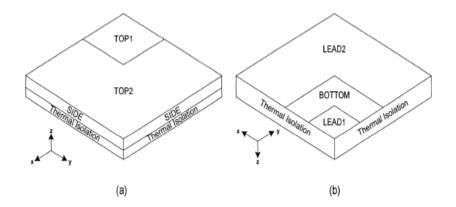

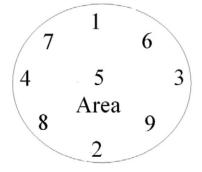

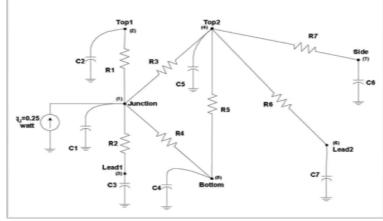

Figure 2.4 shows these mentioned layers. The area of different nodes considered in the layout due to different surfaces (and different heat flux and properties) as listed in table 2.1 in the BGA simulation with the finite element software of COMSOL for the literature review and also this study whenever they are needed.

| Node                 |    | Area m <sup>2</sup>  |

|----------------------|----|----------------------|

| Top 1 (inner top)    | Г1 | 4.12036E-5           |

| Top 2 (outer top)    | Г2 | 3.58796E-4           |

| Lead 1 (inner leads) | LI | 2.5E-5               |

| Lead 2 (outer leads) | L2 | 3E-4                 |

| Bottom               | В  | 7.5E-5               |

| Side                 | S  | 6.6E-5               |

| Junction J (Volume)  |    | 5E-10 m <sup>3</sup> |

Table 2.1: Different Nodes in the Layout and Their

Surface Areas.

Figure 2.4: (a) Top1, Top2, Side areas, (b) Lead1, Lead2, Bottom areas.

### 2.1.2 Governing Heat Transfer Equations

Heat transfer mechanisms are *Conduction, Convection, and Radiation* [14, 23]. For most electronic component, heat conduction is the most important heat transfer phenomenon; therefore most researchers consider a component that has thermal conduction as its only mode of internal heat transfer. Therefore, heat conduction equation described by equation (2.1) will be used for thermal modeling of electronic component in this research work.

$$q_g + \nabla \cdot (k \nabla T) = \rho \cdot C \cdot \frac{\partial T}{\partial t}$$

(2.1)

where:

C (J/K) is the specific heat capacity of solid material, and p (Kg/m3) is the density of material, and q (J) is the heat energy generated inside a solid, and T (K) is the temperature of the solid, and , is the vector of divergence operator.

$\nabla = \frac{\partial}{\partial x}\hat{i} + \frac{\partial}{\partial y}\hat{j} + \frac{\partial}{\partial z}\hat{k}$  For a homogeneous and isotropic solid material where thermal conductivity is a scalar parameter independent of direction and location, equation (2.2) is simplified as follows:

$$\frac{\partial^2 T}{\partial x^2} + \frac{\partial^2 T}{\partial y^2} + \frac{\partial^2 T}{\partial z^2} + \frac{q_g}{k} = \frac{1}{\alpha} \frac{\partial T}{\partial t}$$

(2.2)

where:

$\alpha = \frac{k}{C \cdot \rho}$ , is thermal diffusivity of the solid material.

Numerical methods such as finite element method and finite difference method can be applied to various kinds of heat conduction problems (e.g. isotropic, non-isotropic, linear, non-linear, homogeneous, and non-homogeneous) for thermal analysis of electronic system. Nevertheless using such numerical methods might be time-consuming and could be replaced by experimental results for gaining the boundary conditions temperatures of a device under test.

### 2.1.3 Compact Thermal Modeling

The temperature profile (temperature at any desirable location of a solid object) and inward/outward heat flux from the surfaces of the solid object obey the heat transfer equation by conduction as stipulated. Nevertheless, if an object with a complex geometry such as a modern electronic package with several layers of materials is the subject of the thermal analysis problem, it's hard to find an analytical solution for this equation.

Employing numerical methods developed for solving the heat transfer equation with specified boundary and initial conditions is a sophisticated solution which exists in order to obtain the temperature profile and outward/inward heat fluxes. However, another solution is using experimental case studies for different workloads which could be more practical for a different set of applications, especially when time and computations are in higher priorities than abstract and precise, yet time-unbounded methods. The idea of generating a compact thermal model stems from such a preference. In fact, this method enables elimination of the redundant or extra data in all nodes except one (the junction is set for this node in this work.) The full-detailed thermal profile is tracked in junction node to get proper and valuable data from only one point in the board; knowing that the other nodes have logical thermal restrictions and a relationship with the tracking node.

The numerical simulation approach may be expensive and inefficient for the customer of the electronic package. Another issue is the confidentiality of the electronic packages which guides the researchers to new solutions [1]. In order to perform the detailed thermal analysis of an electronic package with simulation-based software such as COMSOL, exact information about the internal structure of the package, dimensions and physical properties such as thermal conductivities, thermal capacities, and densities of the different layers of the package is necessary. Package producers however usually consider these specifications as classified information and do not publish them in the public domain. The solution to overcome this situation is *Compact Thermal Modeling* (CTM) of packages. Nevertheless in this work generating such CTMs are examined regardless of, or with the least amount of knowledge from inside the packages using experimental techniques such as Infrared (IR) camera system.

A smaller or *compact model* that is capable of calculating only the hot spots, the temperatures and heat fluxes at some desired locations can help the designer to perform the thermal analysis much more easily and quickly, and with the required accuracy.

### 2.1.3.1 DELPHI compact thermal model

There are several methods of compact model generation; however for steady state compact modeling purpose there is one dominant approach proposed by DELPHI consortium (a collaborative European project) which is based on resistor network. The main goal of this project which involved six end-user electronic equipment companies from five European states was to propose a methodology to generate compact thermal models for electronic packages [15]. The DELPHI consortium members were Thomson CSF, Philips CFT, Alcatel Bell, Alcatel Space, Flomerics, and the National Microelectronics Research Centre in Ireland. The first four companies which were the industrial partners of project are well known producers of electronic equipment in the area of civil and military radar, lighting and consumer electronics, telecommunications equipments, and satellite electronics. The fifth partner of project Flomerics is a developer of a thermal CAD tool used in the electronic industry.

The DELPHI procedure of generating static (steady state) compact thermal model has several steps as following:

1- A detailed thermal model of the package is generated by a thermal CAD tool.

2- Using the thermal CAD tool, thermal simulations are performed on package for a set of boundary conditions proposed by DELPHI consortium and average temperatures and heat fluxes of desired locations (thermal nodes that correspond to the volumes and areas inside or on the surfaces of package) are obtained.

3- A network is postulated. This network consists of several resistors that connect the thermal nodes to each other.

4- The values of resistors are then calculated using the detailed model results.

### 2.1.3.2 Static compact model definition

Following the DELPHI methodology, the thermal characteristics of the package can be modeled by a resistor network as mentioned earlier. Using node analysis method, the general formula relating the voltages (temperatures) and currents (heat fluxes) of the electric network can be expressed as:

$$q_i = \sum_{k=0}^{N} Y_{ik} T_k$$

(2.3)

where:

Y is the conductance matrix,

N is the number of nodes,

qi (Watts) is the heat flux leaving the node i,

and Ti (Volt) is the voltage of node i.

If the package is considered a linear thermal system (i.e. the thermal conductance and other physical properties of the package are temperature independent), it can be modeled by a linear system such as equation (2.3) and matrix Y. This can represent the static compact thermal model of the package. The higher value of N, the higher accuracy will be achieved by this modeling. Note that each node in equation (2.3) represents a specified area or volume within or on the surfaces of the package such as junction region, side walls, top surface, leads... Node voltages calculated by the equation (2.3) are equal to the average temperature of their corresponding volume or area

### 2.1.4 Infrared (IR) Camera in Thermal Analysis of Electronic Packages

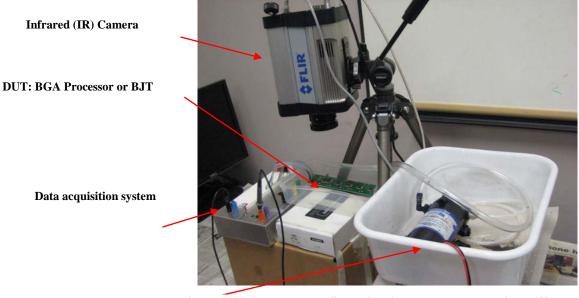

A recent infrared thermography setup for thermal analysis of electronic packages was proposed by [2] in 2009. The measurement setup is used to perform two types of analysis a) steady state analysis, b) transient analysis. In steady state analysis, after switching the power ON, a time interval is given to the system to reach its steady state condition. This is due to the fact that oil based heat-sink takes some period of time to completely cover the whole surface of the device under test (DUT) and remove the heat homogenously. To perform transient analysis on the DUT, an abnormal stress is imposed to a system in the form of different load work conditions.

The major apparatus used in the proposed experimental setup include an FLIR infrared camera system, data acquisition system, digital thermometer, infrared transparent oil (Aldrich oil), oil pump and power supply. A typical measurement setup is shown in figure 2.5. The measurement setup is capable of capturing up to 420 frames per second (fps) with a  $10\mu m \times 10\mu m$  spatial resolution, and it can be applied to multiple chips with relative simplicity. The IR camera frame rate can be increased up to 10 KHz as long as the bandwidth of the camera stays under 1GB/s. The equipment and instrumentation used to conduct the experimental measurement are discussed in this chapter.

**Oil pump**

Figure 2.1: Proposed Test Setup for simple BJT Introducing Different Equipment.

### 2.1.4.1 Infrared Camera

The infrared camera used in this measuring setup is a FLIR SC4000 camera (Fig. 2.6) which is a high-speed, high-resolution, high sensitivity, science-grade infrared camera with Gigabit Ethernet, Camera Link and USB interfaces for maximum flexibility and performance. With a  $320 \times 256$  pixel Indium Antimonide (InSb) detector, the ThermoVision SC4000 camera offers unmatched resolution and thermal sensitivity. An extremely sensitive detector and high speed read out design, provide the camera with extraordinary image quality for the most demanding applications.

Figure 2.6: Infrared (IR) Camera SC4000.

The Thermo Vision SC4000 outputs 14-bit digital data at rates up to 50 Mega pixels per second, yielding 420Hz frame rates for  $320 \times 256$  pixel imagery. For high speed applications and increased frame rates the ThermoVision SC4000 supports windowed readout modes, allowing a subset of the total image to be selectively read out with user-adjustable window size at a much higher frame rate. The sub-sample window sizes and locations can be arbitrarily chosen and are easily defined using the camera control software [24].

### 2.1.4.2 Data Acquisition System

The data was captured and analyzed using the integrated data acquisition system of the optical system, supported by PC-based ThermaCAM Researcher software for data acquisition, analysis and reporting. ThermaCAM Researcher software contains powerful measurement and analysis functions for extensive temperature analysis, including

isotherms, line profiles, area histograms and image subtraction capability. The acquired input data were recorded in real time for subsequent analysis using this software package. Additionally, the SC4000 camera system has an optional Software Development Kit (SDK) for custom programming and interfacing to the camera which is introduced in detail in Chapter 3.

### 2.1.4.3 Heat-sink

A heat-sink is a medium that enhances heat dissipation from a hot surface, usually the case of a heat generating component, to a cooler ambient, usually air. In most situations, heat transfers across the interface between the solid surface and the coolant air and the solid-air interface represents the greatest barrier for heat dissipation. A heat-sink lowers this barrier mainly by increasing the surface area that is in direct contact with the coolant. This allows more heat to be dissipated and/or lowers the device operating temperature.

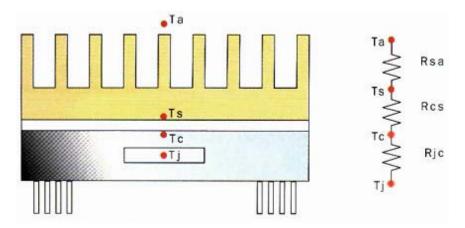

The primary purpose of a heat-sink is to maintain the device temperature below the maximum allowable temperature specified by the device manufacturer [19]. Using temperatures and the rate of heat dissipation, a quantitative measure of heat transfer efficiency across two locations of a thermal component can be expressed in terms of thermal resistance R, defined as:

$$R = \frac{\Delta T}{Q} \tag{2.4}$$

where  $\Delta T$  is the temperature difference between the two locations. Figure 2.7 shows the thermal resistance circuit between junction and ambient of a chip. The measurement unit of thermal resistance is in °C/W, indicating the temperature rise per unit rate of heat dissipation. This thermal resistance is analogous to the electrical resistance  $R_e$ , given by Ohm's law:

$$R_e = \frac{\Delta V}{I} \tag{2.5}$$

with  $\Delta V$  being the voltage difference and I the current.

Figure 2.7: Thermal Resistance Circuit.

#### A) Heatsink Selection

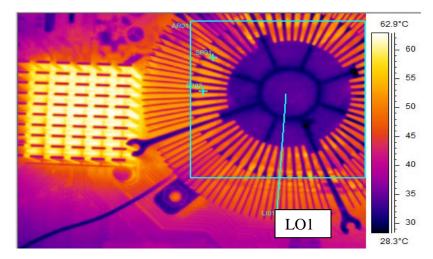

One of the most important considerations in this measuring setup is to have the DUT operating in the conditions under which it was designed to operate. Under these conditions the cooling system of our DUT (a FPGA processor with BGA technology or a simple BJT) is a passive air cooling system which uses a fan with variable speed to remove the heat according to power dissipation.

The temperature distribution of the DUT with a cooling fan is shown in figure 2.8. The thermocouple installed under the heat-sink (LO1) indicates temperature of 52.3°C. However the heat-sink is not transparent to IR radiation, therefore; the DUT temperature cannot be obtained directly.

Several liquids to act as coolants were explored in [2]. Water, which has a very high specific heat, makes it ideal for such experiments, but it is opaque to the IR camera. Several fluoride materials are extremely transparent to IR with a high capacity to cool down modern processors, but their toxic nature makes them unsuitable. The most transparent IR material was olive oil which was transparent enough to perform good measurement, but difficult to be pumped due to its high viscosity.

Aldrich Mineral Oil 161403 was selected as the heat-sink for the test setup due to its elevated transparency in the infrared spectrum, high specific heat, relatively high thermal conductivity, relatively low viscosity, and chemical safety. The oil was pumped to the surface of the chip and is capable of removing 100W heat from the DUT.

Figure 2.8: Temperature Distribution of the DUT with Air Cooling.

### B) Heatsink Flow

The oil flow regime is a major factor affecting the temperature measurement of the DUT in the experimental setup. Several different oil flow scenarios were studied below.

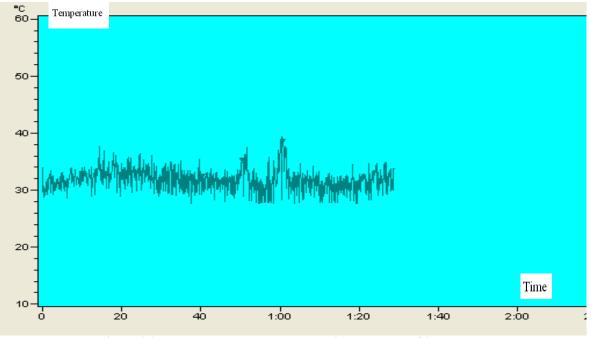

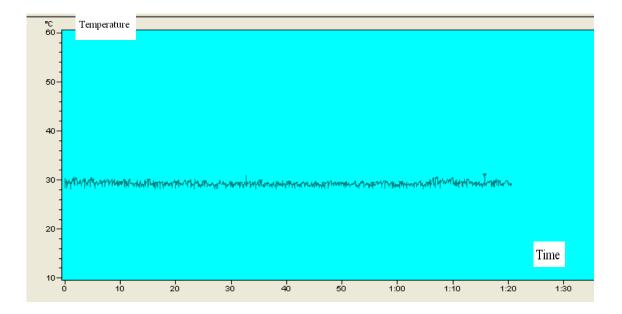

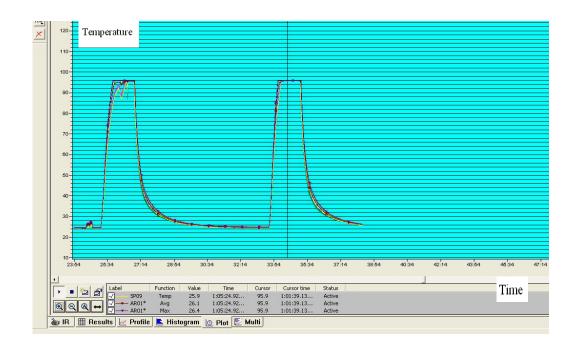

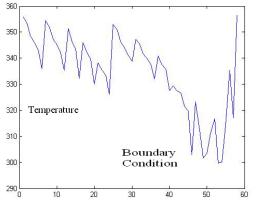

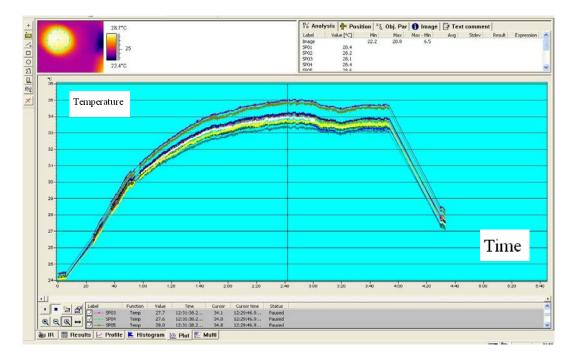

1) Turbulent flow: the oil pipe is positioned about 5 cm above the DUT and the oil was pumped directly to the surface of the DUT. The magnitude of the temperature versus time is represented in figure 2.9.

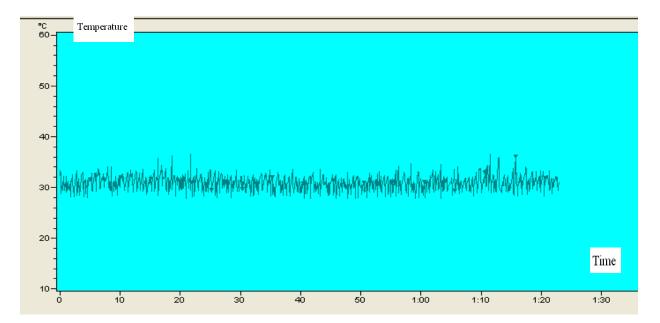

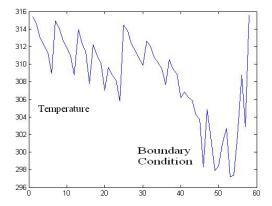

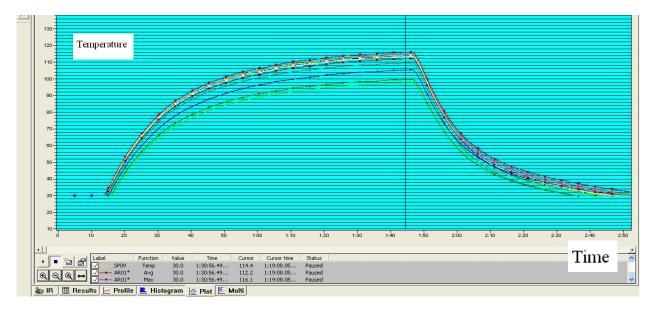

2) Turbulent flow at an angle of 45 degree: the oil pipe is positioned about 5 cm above the DUT, but the oil was pumped with a 45 degree angle. The magnitude of the temperature versus time is represented in figure 2.10.

3) Laminar flow: oil flows over the DUT with an almost angle of zero and in parallel layers. The magnitude of the temperature versus time is represented in figure 2.11.

Figure 2.9: Temperature Measurement with Turbulent Oil Flow.

The obtained results indicate that the turbulent flow in both figure 2.9 and figure 2.10 has more fluctuations in temperature than laminar flow shown in figure 2.11. Laminar oil flow regime was chosen as the heat-sink system.

Figure 2.10: Temperature Measurement with Turbulent Oil Flow at an Angle of 45°.

Figure 2.11: Temperature Measurement with Laminar Oil Flow.

### 2.1.4.4 Oil Pump

The utility pump shown in the figure 2.12 is suitable for variety of tasks such as pumping mineral oil since it is designed especially for harsh fluid transfer. A 12V DC battery was used to power the pump.

Figure 2.12: Utility Pump

### 2.1.4.5 Thermocouple and Digital Thermometer

The measured temperature in this setup is initially verified by using a thermocouple. A variety of thermocouples are available for different measuring applications. They are usually selected based on the temperature range and sensitivity needed. Thermocouples with low sensitivities (B, R, and S types) have correspondingly lower resolutions. In this setup a type K (*chromel–alumel*) thermocouple is used which is the most common general purpose thermocouple. It is inexpensive and available in a wide variety of probes. They are available in the -200 °C to +1350 °C range.

An Omega HH-23A digital thermometer was used with the thermocouple probe to record and display the temperature of the DUT [32].

#### 2.1.4.6 Emissivity

One of the most important parameters that affect the temperature measurement of the DUT is emissivity. As described previously it defines the fraction of radiation emitted by an object as compared with emitted by a perfect radiator (blackbody). Emissivity value is between 0 and 1 and depends on the material of the object, surface condition (surfacing method, geometry), the temperature of the object, wavelength, and direction of radiation.

The default emissivity of camera is set to 0.93; however the real emissivity might be different from this value. Figure 2.13 illustrate the temperature measurement of the DUT using different emissivity values and the average error percentage of the IR thermography measurement with reference to thermocouple measurement, respectively.

Figure 2.13: Emissivity Effect on Temperture Measurement of the DUT.

### 2.2 Summary

Different Ball Grid Array (BGA) technology and packages were introduced. This type of package was selected to the subject of thermal analysis in this work. In addition, adequate layout description of BGA was presented.

The heat conduction mechanism which is the most important heat transfer phenomenon for most electronic components, including the BGA, was discussed. CTM approach with applications to a BGA is also presented.

The infrared (IR) thermography measurement setup used to obtain the temperature profile and power dissipation of a BGA was discussed. The major equipments and the systems used in the experiment setup were discussed in this chapter. The effect of various parameters such as the oil flow condition and emissivity of the target were studied and the proposed setup for this work was presented.

# **CHAPTER 3**

## **Software and Computing**

### **3.1 Introduction**

Various hardware and software pieces are required to obtain a compact thermal model of a package. This chapter describes the software and computing tools used during this work. These tools were applied to the test setup (pre-experimental section), various Coding programs, execution and running the experimental case studies and postprocessing analysis.

The application of the developed software and computing tools was illustrated via a number of obtained figures, equations and tables to clarify the process.

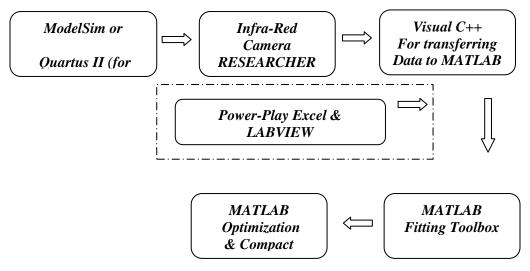

Three different categories of software were applied in this work: Pre-Experimental software is those related to the programming of a BGA, due to its functionality as a microprocessor. Then, infrared (IR) camera system's dedicated software is discussed as part of the data acquisition system. The last category is mathematical and post-processing software to obtain the compact thermal model for a BJT and a BGA.

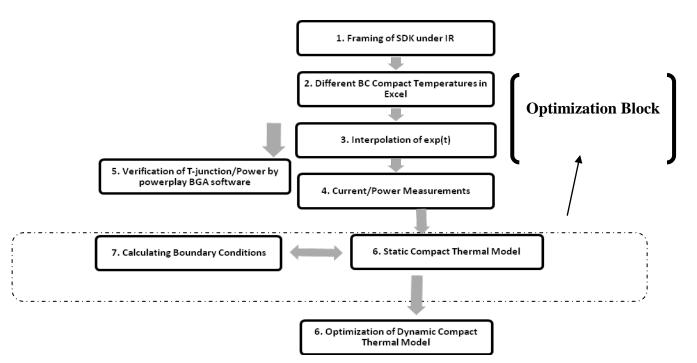

The hierarchy of these sets of software is shown in figure 3.1. The flowchart shows the time-line of the software application in this work. The dashed box shows the concurrent flow of finding the power and current with the respective software.

Figure 3.1: Flowchart of Software Application.

#### 3.2 ModelSim & Quartus II

The application of the ModelSim [33] and Quartus II [33] module to run the BGA is described in this section. The aim of implementing this module is to run the BGA in a way that the circuitry and as such the BGA, drives a current into the circuit and by calculating the power (/ current) of the BGA and having the temperature profile of the BULK (of the device under test (DUT) and tracking the junction spot's profile) the static and dynamic compact thermal model may be obtained. The major difference between these two modules in programming a FPGA is the fact that the Quartus II is a block diagram-based and hence *object-oriented* software whereas ModelSim consists of Verilog codes (a hardware description language) which are in *C* and *C*++ coding structure [33]. Therefore, using this module is more appropriate in terms of the availability of more authorities, basic machine language; in contrast, more time is needed to make the codes compatible with different DUTs.

The development kit of the BGA has sets of example demonstration codes of Verilogs (with \*.v format) [25, 34], which were used in the analysis efforts.

Beside the "No Load" situation of the FPGA, which the whole board was on the idle mode and no instructions were implemented, several different codes were developed as independent experiments and their sets of thermal analysis (temperature profiles and maximum currents/ powers) were acquired with the infrared camera. Two of these sets were developed in Verilog format and two others in Quartus II block diagram basis. Parts of the Verilog scribe is illustrated in figure 3.2.

Music Synthesizer Demonstration: This code is a complex code consisted of different modules to cooperate in order to synthesize a set of different elements of the board simultaneously to get more power in a less time-consuming ways from the circuit. More details on the implementation aspect are described in [34] (Advanced Examples section).

```

183

184

185

reg (31:0)VGL CLK o:

keyboard_syscIk=VGA_CLK_o[11];

186

wire

wire demo clock =VGA CLK o[18]:

187

essign VGA CLK

18B

=VGA CLK o[0];

189

always @ (posedge CLOCK_50) VGA_CLK_0=VGA_CLK_0+1;

19D

191

/////demo-sound-CH1//////

192

193

wire [7:0] demo code1;

demo soundl ddl |

194

.clock(demo_clock),

195

196

.key_code(demo_code1),

197

.k_tr(KEY[1])

19B

);

/////demo-sound-CH2//////

199

200

wire [7:0]demo_code2;

201 🔳

demo sound2 dd2 |

202

.clock(demo_clock),

203

.key_code(demo_codeZ),

204

.k_tr(KEY[1])

205

1:

206

207

20B

wire [7:0]scan_code;

209

wire get gate;

21D

wire key1 on;

wire key2 on;

211

2 1 Z

wire [7:0] keyl code;

213

wire [7:0] key2_code;

214 🔳

PS2_KEYBOARD keyboard(

215

.ps2 dat (PS2 DAT),

//ps2bus data

inout

.ps2_clk (PS2_CLK),

216

//ps2bus_clk

indut

217

.sys_clk (keyboard sysclk),//system clock

input

//system reset

21B

.reset

(KEY[3]),

input

219

.reset1

(KEY[2]),

//keyboard reset

input

22D

.scandata (scan code),

//scan code

output

221

.key1_an(key1_on),

//key1 triger

222

.key2_on(key2_on),

//key2 triger

223

.key1_code(key1_code),

//key1 code

224

.key2_code(key2_code)

//key2_code

225

);

226

227

wire [15:0]sound1;

22B

229

wire [15:0]sound2;

23D

wire [15:0]sound3:

231

wire [15:0]sound4;

232

wire sound off1:

233

wire sound off2;

wire sound off3;

234

235

wire sound off4;

wire [7:0] sound_code1=(!SW[9])?demo_code1:key1_code;//SW[9]=0 is DEMO SOUND,otherwise key

236

237

wire [7:0] sound_code2=(!SW[9])?demo_code2:key2_code;//SW[9]=0 is DEMO SOUND,otherwise key

23B

wire [7:0] sound_code3-8'hf0;

```

#### Figure 3.2: Parts of the Verilog code for a Music Synthesizer Implemented in the BGA.

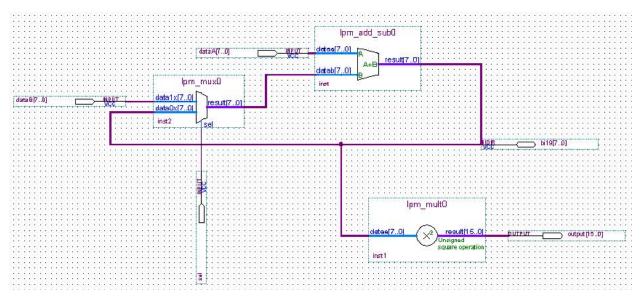

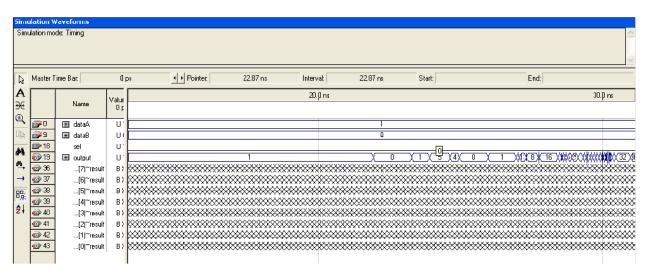

The block which represents the more complicated instruction in the Quartus II compared to a simple Multiplier, is shown in figure 3.3. This figure would also be used as the schematics of the Load 3 in the Chapter 5 Section 5.2. It consists of a Multiplier, an Adder and a Multiplexer and gets two 8 bit input signals and generates a 16 bit output. The typical result obtained from this block diagram is shown in figure 3.4. The simulated noise for each block is present and affects the ultimate results.

Figure 3.3: Relatively Complex Block Diagram for a Quartus II Instruction for the FPGA.

Figure 3.4: Results for the Complex Quartus II Code.

## 3.3 Infrared (IR) Camera's Dedicated Softwares

#### 3.3.1 ThermaCam Researcher Software

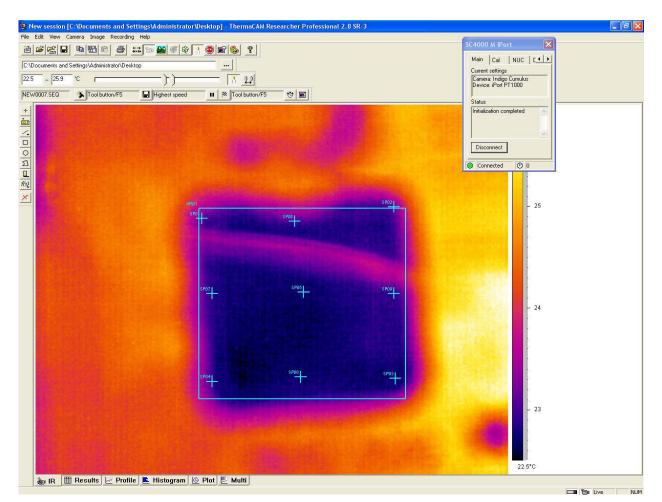

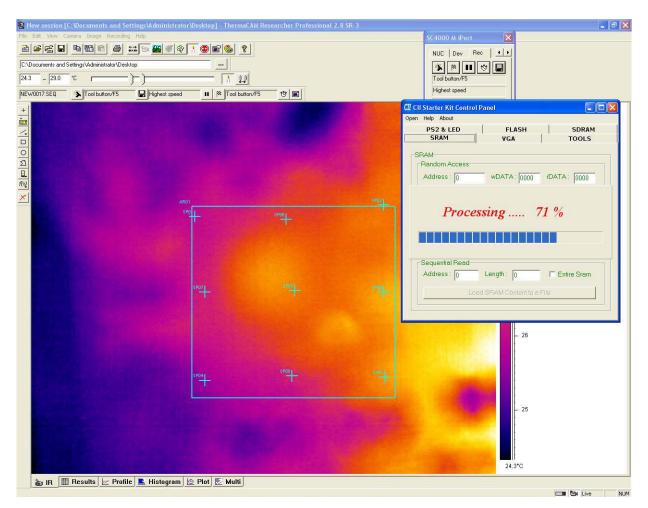

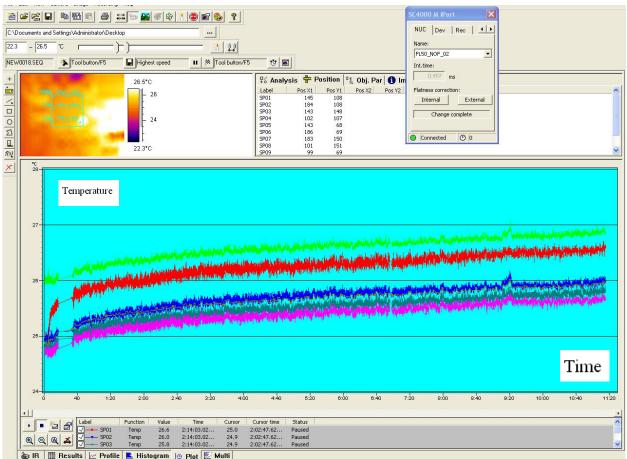

When the implementation was accomplished in either mode of Instruction and with Quartus II or Verilog codes, the "ThermaCam Researcher" (Researcher) and the "Software Development Kit" (SDK) were applied as the dedicated softwares related to the IR camera system to record and to track the temperature profile of the BGA. Figures 3.5 and 3.6 are helpful to understand an instance of the implementation of the Verilog code or the Quartus II Block-based instruction into the DUT while the IR camera is tracking the temperature profile using Researcher software.

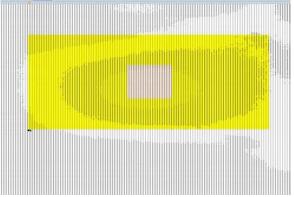

Figure 3.5: Temperature Profile of the BGA at a Given Time Frame by Showing the Physical BGA under its Screen before Starting the Power.

It can be observed from these figures that the environment of the Researcher contains a Graphic User Interface (GUI) which allows acquiring and saving of the data (in this case the temperature profile) of each time step in the screen. Figure 3.5 showed the physical BGA under its screen before starting the power while figure 3.6 is after the startup.

Figure 3.6: Indicating the Implementation Process While Acquiring Temperature Profile in a Researcher.

Figure 3.6 also shows the implementation process while acquiring the temperature profile using Researcher software. It's also helpful to notice from figure 3.5 & 3.6 that the BGA was recognized with at least 4 nodes of a square. This is a drawback of the Researcher compare to the SDK that in order to track a point in the surface the exact coordinates should be defined.

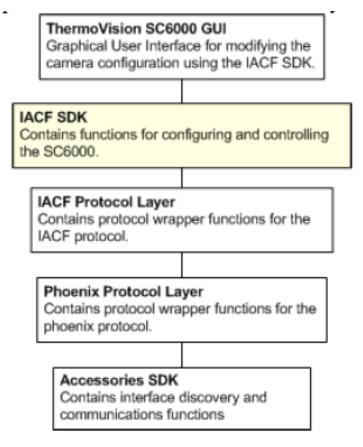

# 3.3.2 Software Development Kit (SDK)

Software Development Kit (SDK) of the IR camera system SC4000 is a collection of several custom programming, each with a specific function. The SDK allows users to write applications that can control and acquire the temperature profile as a collection of data points. The IR camera's SDK diagrams as component layers are shown in the figure 3.7.

Figure 3.7: IR Camera's SDK Diagrams as Component Layers.

In summary the SDK works in the *Command Prompt level* which gives more options to communicate with these different layers and obtain the data directly without any restricting interface. This setup and data acquisition system was applied as the data in transfer to the next levels in this work; nevertheless the figures of the Researcher were selected to demonstrate some facts and suggest some clarifications and apply the presentation privileges of Researcher as in Section 4.3 in the next chapter.

# 3.4 Visual C++

All the work stations at the *Electrothermal Laboratory* works with the Visual Studio Version 2008 which enables the Researcher program to run the (Visual) C++ coding applied in this work. To use the raw data from SDK software which is in the form of several thousands of Excel frames for every experiment, where each file stands for a given time frame, another code is necessary in the command prompt window of Visual Studio software to transfer these raw data in another Excel file where the specified data is highlighted or picked and the extra costly information which is useless for the compact thermal model generation is ignored. The first lines of this preliminary code and the Visual C++ libraries maintained are shown in figure 3.8.

```

E:\Canera>cl /EHsc SDKcodepack.cpp

Microsoft (R) 32-bit C/C++ Optimizing Compiler Version 15.00.21022.08 for 80x86

Copyright (C) Microsoft Corporation. All rights reserved.

SDKcodepack.cpp

Microsoft (R) Incremental Linker Version 9.00.21022.08

Copyright (C) Microsoft Corporation. All rights reserved.

/out:SDKcodepack.cxc

SDKcodepack.obj

E:\Canera>_

```

```

// The aim of this code is to open and read a number of file's

//specific Point defined from before and storing them into an Array.

# include <iostream>

# include <fstream>

# include <fstream>

# include <string>

using namespace std;

int main()

{

```

Figure 3.8: First Lines of a Visual C++ Code Including the Libraries Maintained and the Command Prompt Environment.

This code was written to transfer the .CSV formatted files of the output of the SDK software to Excel files focusing on a specific point or node, in this work mainly the junction temperature, which is the input and typically hottest spot on the surface of a chip.

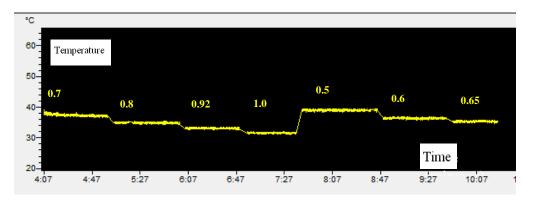

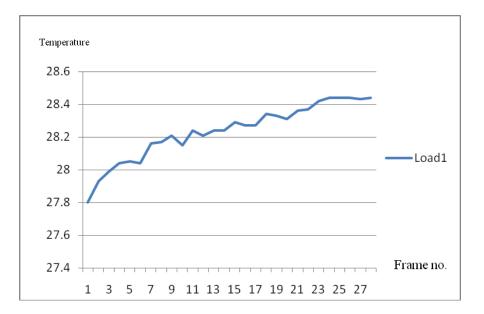

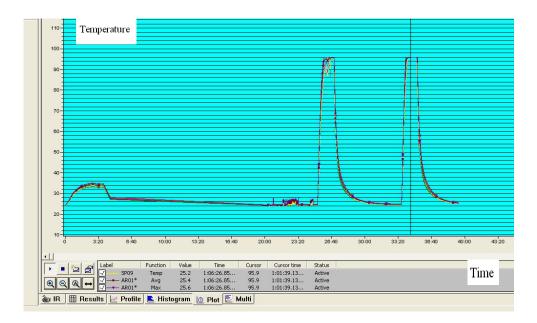

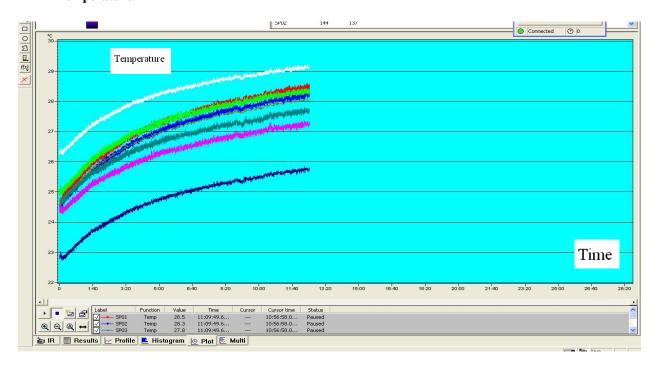

The output frames of the SDK software for the BGA were set to 2700 frames which displays a couple of minutes after the device is turned on and the implementation is done. Figure 3.9 shows the rise in the temperature with the sampling rate of 1/10th of Maximum 30frame /sec for the IR camera in the BGA with a specific Quartus II code instruction called "Load 1" which was a simple Multiplier. In this figure the temperature is indicated in the Y axis and X axis is demonstrating the frame sequence which is in linear relationship with time of the operation.

The challenge of C++ code was I/O issue of inserting 2700 files and working with so many files to extract a specific point's temperature profile (In this case the junction temperature or the hottest spot was in coordinates: Row = 121 & Column = 61); keeping in mind the fact that C++ is only able to work with less than 50 files open at the same time, due to I/O coding limitations [35]. The time of this extraction takes a couple of minutes with that many files and exporting a new file with the optional coordinate's temperature profile.

Given that the results are on a discrete basis, it makes it suitable for the *Fast Fourier Transform* (FFT) process. A method was used to obtain these files data with a less optional frequency which maintains a total of 27 frames less than the total frames. This would definitely increase the maximum error marginally, while cutting the time consumed to export the whole files in one fetch. This method of coding is applicable especially if the trend of the increase or decrease in the temperature is relatively smooth and doesn't imply any external temperature shocks.

# **3.5MATLAB**

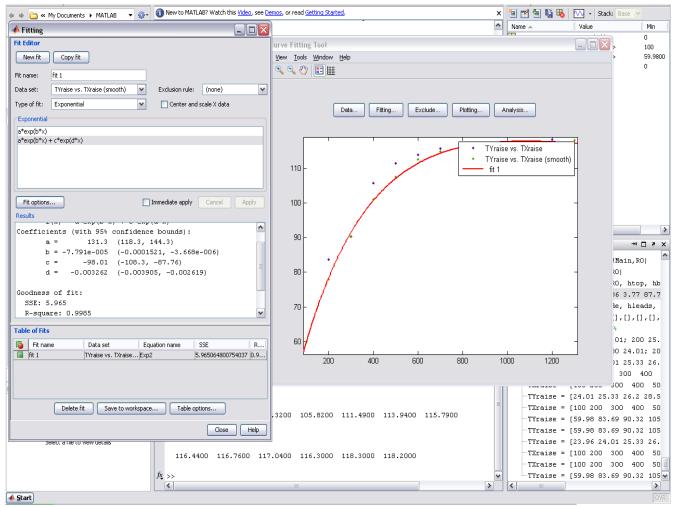

#### 3.5.1 MATLAB as a Mathematical Fitting Toolbox

MATLAB was used as a computational tool. The experimental data are processed and the results are post analyzed to obtain a compact thermal model. In order to find the static

Figure 3.9: Temperature (Celsius) Profile of Junction Temperature in a BGA in a Specific Experiment of a Quartus II Instruction Called Load 1 which was Simple Multiplier Vs the Frame no.(× 100).

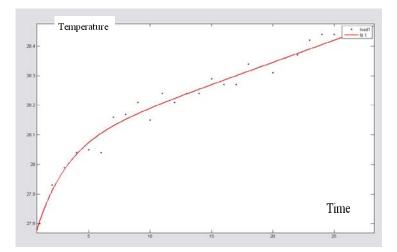

And especially the dynamic compact thermal model as the last element of the desired outcome, the fitting toolbox was applied both for the BJT and BGA experiments. The reason is that the transient time always refers to the capacitor properties and dynamic mode of the change in the profile must be taken into account. However, the static model may be obtained by using the end of the experiment or final temperature value and the initial value or starting point (this could be different from the ambient temperature of the experiment, since the delay run time of the SDK software should be considered). This toolbox in MATLAB is shown in figure 3.10. In addition, the obtained result for the junction temperature profile is shown in figure 3.11.

|                                                 | fit 1                                                              |                                                                        |                                                                                                                      |

|-------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Data set:                                       | load                                                               | 11                                                                     |                                                                                                                      |

| Type of fit:                                    | Exp                                                                | onential                                                               |                                                                                                                      |

| Exponentia                                      | <u> </u>                                                           |                                                                        |                                                                                                                      |

| a*exp(b*x)                                      | 1                                                                  |                                                                        |                                                                                                                      |

| a*exp(b*x)                                      | ) + c*e:                                                           | xp(d*x)                                                                |                                                                                                                      |

|                                                 |                                                                    |                                                                        |                                                                                                                      |

|                                                 |                                                                    |                                                                        |                                                                                                                      |

|                                                 |                                                                    |                                                                        |                                                                                                                      |

|                                                 |                                                                    |                                                                        |                                                                                                                      |

| L                                               |                                                                    |                                                                        |                                                                                                                      |

|                                                 |                                                                    | 0                                                                      |                                                                                                                      |

| Fit option                                      | IS                                                                 |                                                                        |                                                                                                                      |

|                                                 |                                                                    |                                                                        |                                                                                                                      |

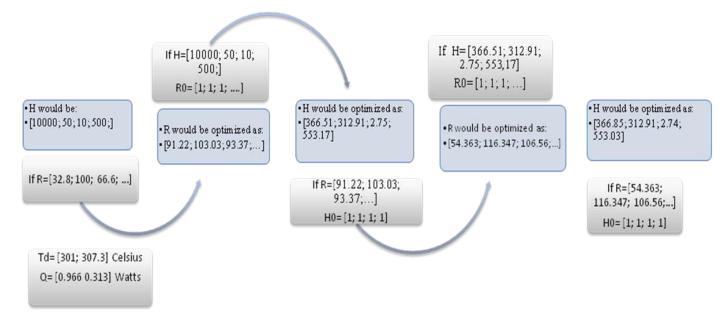

| Results                                         |                                                                    |                                                                        |                                                                                                                      |