## MAGNETICALLY COUPLED RESONANT WIRELESS POWER TRANSMISSION SYSTEM THAT MEETS THE REZENCE EFFICIENCY AND FREQUENCY SPECIFICATION

By

Jean-Claude Leslie Clarke

Bachelor of Engineering in Computer Engineering

Ryerson University, 2014

A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Applied Science

in the program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2018

© Jean-Claude Clarke, 2018

### Author's Declaration for Electronic Submission of a Thesis

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public

#### Magnetically Coupled Resonant Wireless Power Transmission

System that Meets the Rezence Efficiency and Frequency Specification

Master of Applied Science, 2018

Jean-Claude Clarke

**Electrical and Computer Engineering**

Ryerson University

### Abstract

High efficiency Class-E Power Amplifiers (PA) are difficult to analytically design using the original design equations. We present a high frequency (HF) Class-E PA design methodology that simplifies design in this thesis. A high-efficiency Class-E PA was designed using a low-cost power FET by following this design-flow.

Due to their small size, it's difficult to design efficient MCR-WPT resonators for portable electronics. We propose a novel multi-layer MCR-WPT Printed Spiral Coil (PSC) design and design methodology. Two MCR-WPT PSC resonators were designed for smartphones and tablets to meet the Rezence Self-Resonant Frequency and efficiency specifications using this novel design and design methodology.

The MCR-WPT resonators power transfer efficiency is reduced when their separation distance is below the optimal Critical Coupling Distance (CCD) due to frequency splitting. We present a novel maximum-peak detection and auto-tuning circuit that automatically improves efficiency using capacitive tuning when the separation distance is below the CCD.

### Acknowledgements

First and foremost I want to say that I am thankful for the peace of the *Holy Spirit*. These past three years have been challenging, as there have been many months that I thought that I wouldn't be able to finish this thesis. But by His grace and strength, I was able to push through the many roadblocks I came across throughout this period.

Next, I would like to express my gratitude to Prof. Fei Yuan and his research team for the opportunity to do this project under his guidance. He gave me the chance to do my master's with him even though I was only an average student in his classes during my undergrad. He has helped me many times during our discussions his kind guidance, and constructive suggestions for all my ideas. Thanks are also due to the research team members Matthew, Sandeep, Young, and Durand for their willingness to bounce around ideas whenever I got stuck.

I would like to thank my family, especially my parents for their financial and emotional support during this experience. They have been listening ears in my time of need, and I appreciate them every day.

Lastly, I would like to thank Ryerson University providing the opportunity for me to pursue a master's degree. Thanks to Jason Naughton and Daniel Gianitelli for their help in getting all the software tools I used on their platform fixed quickly whenever a problem arose. I also want to say thanks to James Koch for his help with PCB design and fabrication. And finally Keysight's technical support. They have been a pleasure to work with whenever I came across problems with their software. They always responded quickly to my issues and had a solution in a timely manner.

# **Table of Contents**

| Author's l                | Declaration for Electronic Submission of a Thesisii           |

|---------------------------|---------------------------------------------------------------|

| Abstract.                 | iii                                                           |

| Acknowle                  | edgements iv                                                  |

| List of Ta                | blesx                                                         |

| List of Fig               | guresxiii                                                     |

| List of Ap                | opendices xxii                                                |

| Abbreviat                 | tions xxiv                                                    |

| <b>1 Introd</b><br>1.1 Ba | uction       1         ckground and Literature Review       2 |

| 1.1.1                     | Basic overall Architecture                                    |

| 1.1.2                     | Communication between the MCU                                 |

| 1.1.3                     | Power Supply, Oscillator, and Gate driver5                    |

| 1.1.4                     | Power Amplifier and Impedance Matching                        |

| 1.1.5                     | Magnetic Coupling Resonant Wireless Power Transmission Coils  |

| 1.1.6                     | Rectifiers and DC-to-DC converters                            |

| 1.2 Mo                    | otivations and Objectives                                     |

| 1.2.1  | Class E PA design                                                | 9             |

|--------|------------------------------------------------------------------|---------------|

| 1.2.2  | Coil Design                                                      | 11            |

| 1.2.3  | Impedance Matching, and Tuning to Counteract Frequency Splitting |               |

| 1.3 Co | ontributions of Thesis                                           | 13            |

| 1.3.1  | High-Efficiency, Cost-Effective Class E Amplifier Design         | 13            |

| 1.3.2  | Multilayer Spiral MCR-WPT PSC Design                             | 13            |

| 1.3.3  | Capacitive Auto-Tuning Impedance Matching Technique for Improve  | ed Efficiency |

|        | 14                                                               |               |

| 1.4 Th | esis Organisation                                                | 14            |

| 1.5 Ch | apter Summary                                                    | 15            |

|        | ce WPT System Analog Component Blocks Design                     |               |

| 2.2 Os | scillator on Gate Driver Circuitry                               |               |

| 2.2.1  | Oscillator Selection and Design                                  |               |

| 2.2.2  | Gate Driver Circuit Selection and Design.                        |               |

| 2.3 Cl | ass-E Power Amplifier with High Efficiency                       |               |

| 2.3.1  | Class-E Amplifier Basics and Theory                              |               |

| 2.3.2  | Class-E Design Methodology                                       | 29            |

| 2.3.3  | Other Class-E Design Considerations                              |               |

| 2.3.4  | Class-E PA Specifications, Simulations and Experimental Result   |               |

| 2.4 Hi | gh Frequency, Power Rectifiers                                   |               |

| 2.4.1      | Rectifier and Diodes Basics and Considerations                           | . 43  |

|------------|--------------------------------------------------------------------------|-------|

| 2.4.2      | Types of Rectifier Diodes                                                | . 47  |

| 2.4.3      | Simulations and Results                                                  | . 48  |

| 2.5 Bro    | badband DC Isolation Transformers                                        | . 51  |

| 2.5.1      | Isolation Transformer Theory and Considerations                          | . 52  |

| 2.5.2      | Isolation Transformer Design, Testing, and Results                       | . 55  |

| 2.6 Cha    | apter Summary and Conclusions                                            | . 57  |

|            | agnetically Coupled Resonant Wireless Power Transmission Coils for Small |       |

|            | Devices<br>ral Inductor Basics and Theory                                |       |

| 3.1.1      | Spiral Inductor Geometries                                               | . 63  |

| 3.1.2      | Effects of Single Layer Inductor Dimensions on Inductance                | . 63  |

| 3.1.3      | Effects of Multilayer Inductor Parameters on Inductance                  | . 65  |

| 3.1.4      | Spiral Inductor Parasitics and Loss Mechanisms                           | . 67  |

| 3.1.5      | Spiral Inductor Basics Summary and its relationship to MCR-WPT Coils     | . 76  |

| 3.2 Sin    | gle Layer MCR-WPT Coils                                                  | . 77  |

| 3.2.1      | MCR-WPT PSC Basics                                                       | . 78  |

| 3.2.2      | Design Methodology and Simulation Setup.                                 | . 81  |

| 3.2.3      | Simulations, Results, and Summary                                        | . 88  |

| 3.3 Do     | uble and Multi-Layer MCR-WPT Coils and Proposed 6.78MHz MCR-WPT Coils    | s for |

| small elec | tronics Devices                                                          | . 91  |

| 3.3.1                                                                                                                                   | Double Layer Parallel and Series Stacked MCR-WPT coils                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3.2                                                                                                                                   | Novel MCR-WPT Multi-Layer Design                                                                                                                                                                                                        |

| 3.3.3                                                                                                                                   | Effects of Multilayer Parameters on Resonance of Novel design                                                                                                                                                                           |

| 3.4 Sir                                                                                                                                 | nulations and Experimental Results, and Discussion of Proposed System                                                                                                                                                                   |

| 3.4.1                                                                                                                                   | Double Layer MCR-WPT PCB Coil Specifications                                                                                                                                                                                            |

| 3.4.2                                                                                                                                   | 5x2.5in <sup>2</sup> FR4 Double Layer MCR-WPT PSC Coil Design for Smartphones 102                                                                                                                                                       |

| 3.4.3                                                                                                                                   | 5x2.5in <sup>2</sup> Alumina Double Layer MCR-WPT PCB Coil Cellphone Design 107                                                                                                                                                         |

| 3.4.4                                                                                                                                   | 8x4in <sup>2</sup> FR4 Double Layer MCR-WPT PCB Coil Design for Tablets 110                                                                                                                                                             |

| 3.4.5                                                                                                                                   | Results Summary                                                                                                                                                                                                                         |

|                                                                                                                                         |                                                                                                                                                                                                                                         |

| 3.5 Ch                                                                                                                                  | apter Summary and Conclusions                                                                                                                                                                                                           |

| 4 Au<br>Efficiency .                                                                                                                    | to-Tuning Technique to Overcome Frequency Splitting and Improve System<br>ugnetically Coupled Resonance (MCR) and Frequency Splitting Theory and Tuning                                                                                 |

| 4 Au<br>Efficiency.<br>4.1 Με                                                                                                           | to-Tuning Technique to Overcome Frequency Splitting and Improve System<br>ugnetically Coupled Resonance (MCR) and Frequency Splitting Theory and Tuning                                                                                 |

| <b>4 Au</b><br>Efficiency .<br>4.1 Ma<br>12                                                                                             | to-Tuning Technique to Overcome Frequency Splitting and Improve System<br>agnetically Coupled Resonance (MCR) and Frequency Splitting Theory and Tuning<br>1                                                                            |

| <b>4 Au</b><br>Efficiency .<br>4.1 Ma<br>12<br>4.1.1                                                                                    | to-Tuning Technique to Overcome Frequency Splitting and Improve System<br>120<br>agnetically Coupled Resonance (MCR) and Frequency Splitting Theory and Tuning<br>1<br>Frequency Splitting Theory, Modes of Operation for MCR-WPT Coils |

| <b>4 Au</b><br>Efficiency .<br>4.1 Ma<br>12<br>4.1.1<br>4.1.2                                                                           | to-Tuning Technique to Overcome Frequency Splitting and Improve System<br>120<br>120<br>120<br>120<br>120<br>120<br>120<br>120                                                                                                          |

| <ul> <li>4 Au</li> <li>Efficiency .</li> <li>4.1 Ma</li> <li>12.</li> <li>4.1.1</li> <li>4.1.2</li> <li>4.1.3</li> <li>4.1.4</li> </ul> | to-Tuning Technique to Overcome Frequency Splitting and Improve System<br>120<br>Ingenetically Coupled Resonance (MCR) and Frequency Splitting Theory and Tuning<br>Frequency Splitting Theory, Modes of Operation for MCR-WPT Coils    |

| <ul> <li>4 Au</li> <li>Efficiency .</li> <li>4.1 Ma</li> <li>12.</li> <li>4.1.1</li> <li>4.1.2</li> <li>4.1.3</li> <li>4.1.4</li> </ul> | to-Tuning Technique to Overcome Frequency Splitting and Improve System<br>120<br>agnetically Coupled Resonance (MCR) and Frequency Splitting Theory and Tuning<br>Frequency Splitting Theory, Modes of Operation for MCR-WPT Coils      |

|                          | mulation Results                      |

|--------------------------|---------------------------------------|

| 4.3.1                    | Specifications                        |

| 4.3.2                    | Simulations Setup 149                 |

| 4.3.3                    | Auto-Tuning 5x2.5In MCR-WPT Coils 152 |

| 4.3.4                    | Auto-Tuning 8x4In MCR-WPT Coils 153   |

| 4.3.5                    | Results Summary and Discussion        |

| 4.4 C                    | hapter Summary and Conclusions 160    |

|                          |                                       |

|                          | usions and Future Works               |

| 5.1 C                    |                                       |

| 5.1 C                    | onclusions 162                        |

| 5.1 C<br>5.2 F           | onclusions                            |

| 5.1 C<br>5.2 Ft<br>5.2.1 | onclusions                            |

## **List of Tables**

| Table 1.1-1 PRU and PTU device classifications [6].    4                                      |

|-----------------------------------------------------------------------------------------------|

| Table 2.3-1 Class-E PA final design parameters.    40                                         |

| Table 2.3-2 Class-E PA measurement results.    42                                             |

| Table 2.4-1 CSD01060 SiC diode datasheet parameters.    50                                    |

| Table 2.5-1 Transformer insertion loss measurements and results.    57                        |

| Table 3.1-1 Summary of the effect on physical parameters on spiral coil inductance            |

| Table 3.1-2 Types of resistive loss, their description, and methods to reduce their effects75 |

| Table 3.1-3 Types of spiral inductor capacitive parasitics, their benefits, and drawbacks     |

| Table 3.2-1 Benefits and drawbacks of changing MCR-WPT coil parameters on SRF & efficiency.   |

| All other parameters are constant                                                             |

| Table 3.2-2 Single layer MCR-WPT PSC parameters                                               |

| Table 3.2-3 single layer MCR-WPT coils SRF and S21dB specifications vs simulation results. 91 |

| Table 3.3-1 MCR-WPT PSC parameters used in the different number of layers simulation test.97  |

| Table 3.3-2 MCR-WPT PSC parameters for different substrate thicknesses simulation test 98     |

| Table 3.3-3 MCR-WPT PSC parameters for different dielectric substrate types simulation test.  |

|                                                                                               |

| Table 3.4-1 5x2.5in <sup>2</sup> double layer FR4 MCR-WPT PSC parameters                      |

| Table 3.4-2 5x2.5In <sup>2</sup> double layer FR4 MCR-WPT coils SRF and S21dB specifications vs         |

|---------------------------------------------------------------------------------------------------------|

| simulation results                                                                                      |

| Table 3.4-3 5x2.5in <sup>2</sup> double layer FR4 MCR-WPT coils output peak voltage and apparent power  |

| at different separation distances                                                                       |

| Table 3.4-4 5x2.5In <sup>2</sup> double layer FR4 MCR-WPT coils harmonic balance and experimental peak  |

| output power results comparison 107                                                                     |

| Table 3.4-5 5x2.5In <sup>2</sup> double layer alumina MCR-WPT PSC parameters.       108                 |

| Table 3.4-6 5x2.5in <sup>2</sup> double layer alumina MCR-WPT coils SRF and S21dB specifications vs     |

| simulation results                                                                                      |

| Table 3.4-7 8x4in <sup>2</sup> double layer FR4 MCR-WPT PSC parameters                                  |

| Table 3.4-8 8x4In <sup>2</sup> double layer FR4 MCR-WPT coils SRF and S21dB specifications vs           |

| simulation results                                                                                      |

| Table 3.4-9 8x4in <sup>2</sup> double layer FR4 MCR-WPT coils output peak voltage and apparent power at |

| different separation distances                                                                          |

| Table 3.4-10 8x4In <sup>2</sup> FR4 double layer MCR-WPT coils harmonic balance and experimental peak   |

| output power results comparison 115                                                                     |

| Table 3.4-11 MCR-WPT PSC efficiency summary                                                             |

| Table 3.4-12 Size, SRF and efficiency comparisons between the novel double layer $5x2.5in^2$ FR4        |

| MCR-WPT PSC and other double layer coil research                                                        |

| Table 4.1-1 Comparison between harmonic balance and experimental MCR-WPT tuning                         |

| capacitance and peak output power                                                                       |

| Table 4.1-2 Output peak voltage and apparent power of the 8x4In and 5x2.5In MCR-WPT coils               |

| for different inputs and at different separation distances and capacitance tuning values                |

| Table 4.1-3 Comparison between the harmonic balance simulation results and the Class-E PA and   |

|-------------------------------------------------------------------------------------------------|

| function generator experimental results at 1600pF tuning capacitance and 0.5in separation       |

| distance                                                                                        |

| Table 4.3-1 List of discrete electronic components and key parameters used in maximum peak      |

| detection and auto-tuning simulations                                                           |

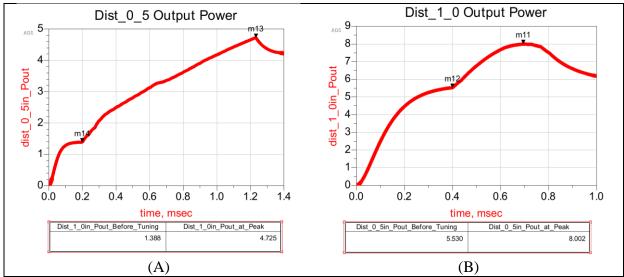

| Table 4.3-2 Tuning time, tuning capacitance and bridge rectifier output power before tuning and |

| at maximum efficiency for 8x4In and 5x2.5In MCR-WPT coils maximum peak detection and auto-      |

| tuning simulations at different separation distances                                            |

| Table 4.3-3 Comparison of tuning times to reconfigure the system for maximum efficiency with    |

| other methods                                                                                   |

# List of Figures

| Figure 1.1-1 One of Tesla's wireless power transmission experiment [7]2                           |

|---------------------------------------------------------------------------------------------------|

| Figure 1.1-2 Rezence magnetic resonance wireless power specification [18] 4                       |

| Figure 1.1-3 Rezence power supply sub-blocks                                                      |

| Figure 1.1-4 Basic impedance matching networks using lumped components                            |

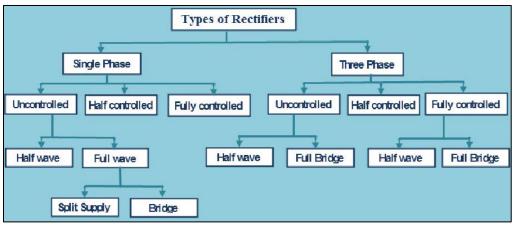

| Figure 1.1-5 Types of rectifiers [21]                                                             |

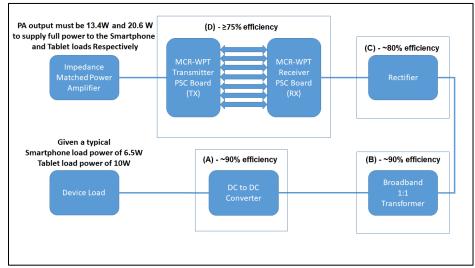

| Figure 2.1-1 Rezence system block diagram with block component efficiencies to calculate the      |

| minimum output power of the PA                                                                    |

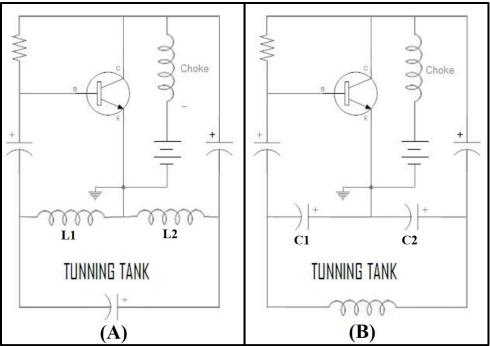

| Figure 2.2-1 Circuit comparison between (A) Hartley oscillator; (B) Colpitts oscillator           |

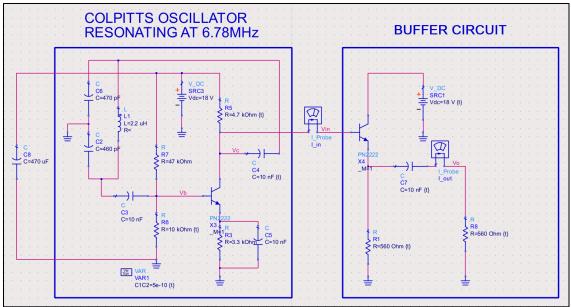

| Figure 2.2-2 Colpitts oscillator and buffer circuit schematic in ADS                              |

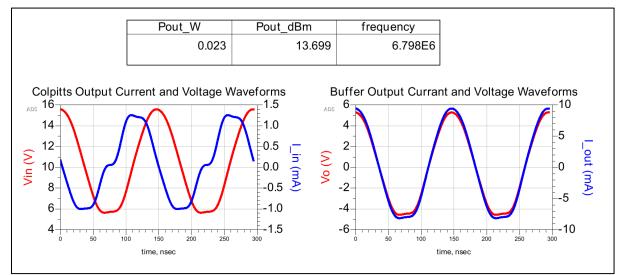

| Figure 2.2-3 Colpitts oscillator and buffer circuit ads data display simulation results in ADS 21 |

| Figure 2.2-4 Class-AB gate driver schematic in ADS                                                |

| Figure 2.2-5 Class-AB gate driver simulation data display results in ADS                          |

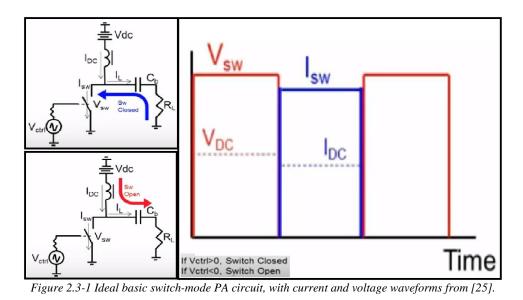

| Figure 2.3-1 Ideal basic switch-mode PA circuit, with current and voltage waveforms from [25].    |

|                                                                                                   |

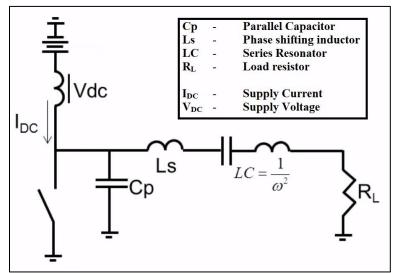

| Figure 2.3-2 Ideal Class E circuit topology [25]                                                  |

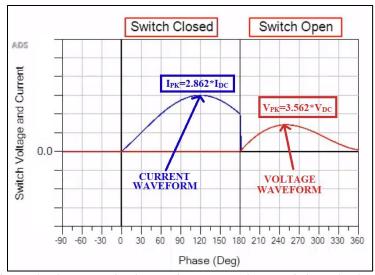

| Figure 2.3-3 Ideal 50% duty cycle Class-E switch voltage and current waveforms, with the peak     |

| voltage and current values [25]                                                                   |

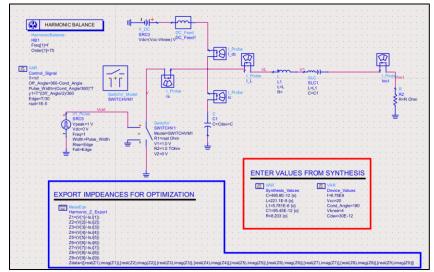

| Figure 2.3-4 Ideal Class E verification schematic in ADS                                          |

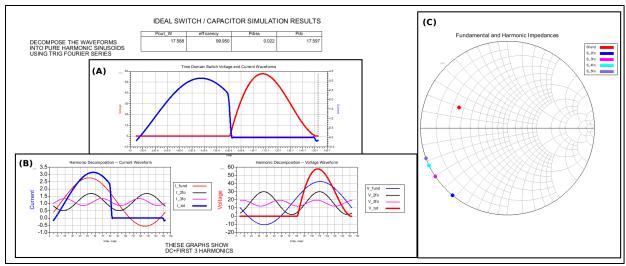

| Figure 2.3-5 Ideal Class-E harmonic balance simulation data display results in ADS: (A) time      |

|---------------------------------------------------------------------------------------------------|

| domain drain voltage and currents; (B) time domain drain current and voltage harmonics; (C)       |

| frequency domain harmonic impedances                                                              |

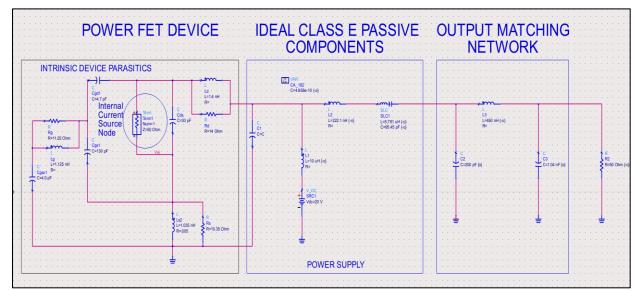

| Figure 2.3-6 Class-E output impedance matching circuit in ADS                                     |

| Figure 2.3-7 Class-E input impedance and final circuit design schematic in ADS                    |

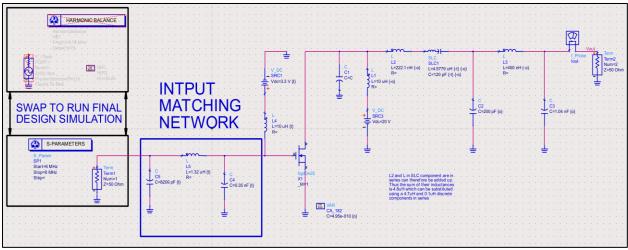

| Figure 2.3-8 Class-E Design Methodology Flow Chart                                                |

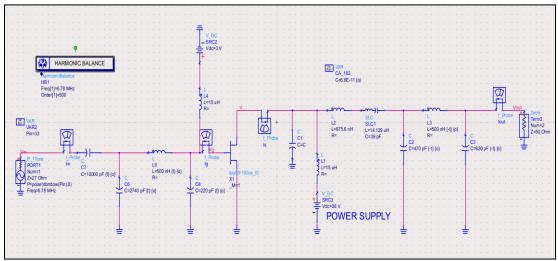

| Figure 2.3-9 Class-E final design schematic in ADS 40                                             |

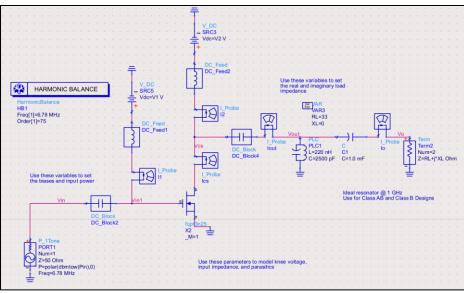

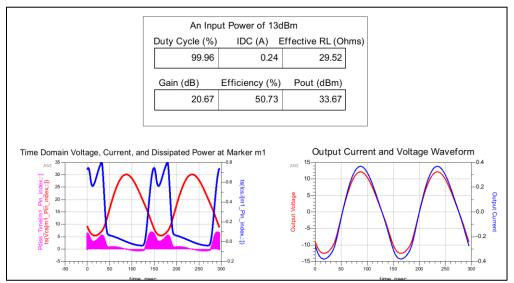

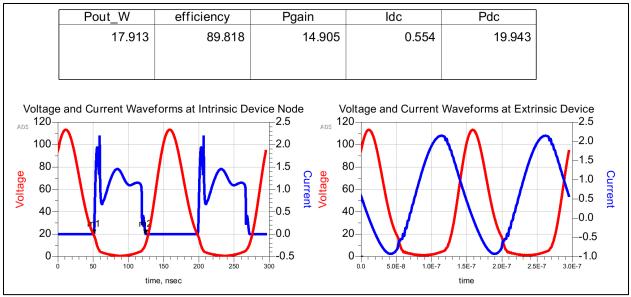

| Figure 2.3-10 Simulation data display results of the Class-E Design done in ADS                   |

| Figure 2.3-11 Class-E PCB experimental test circuit                                               |

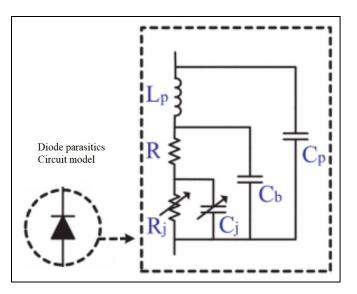

| Figure 2.4-1 Model of a real diode parasitics [36]                                                |

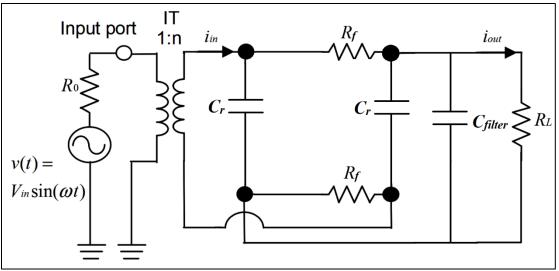

| Figure 2.4-2 Rectifier with parasitic forward resistance and reverse capacitance and filter       |

| capacitor                                                                                         |

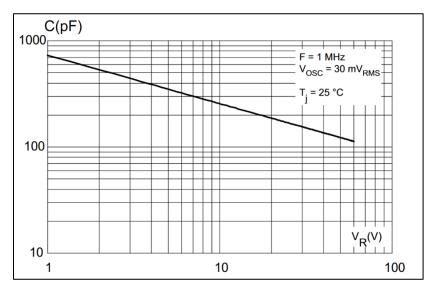

| Figure 2.4-3 Typical junction capacitance for stps5160 Schottky diode [39]45                      |

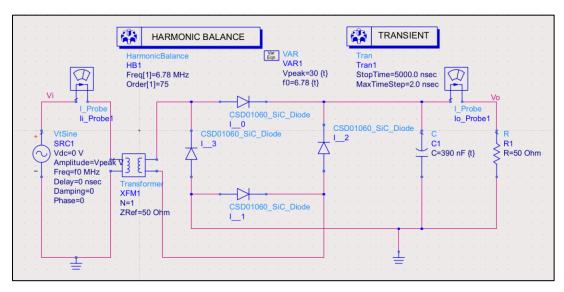

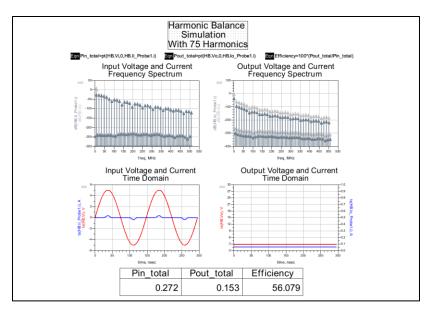

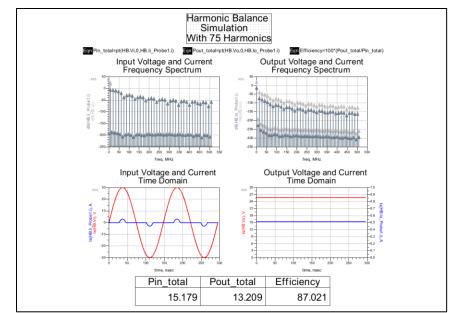

| Figure 2.4-4 CSD01060 SiC diode bridge rectifier ADS schematic test bench                         |

| Figure 2.4-5 5V input signal simulation data display results for the CSD01060 SiC diode bridge    |

| rectifier                                                                                         |

| Figure 2.4-6 30V input signal simulation data display results in ADS for the CSD01060 SiC diode   |

| bridge rectifier                                                                                  |

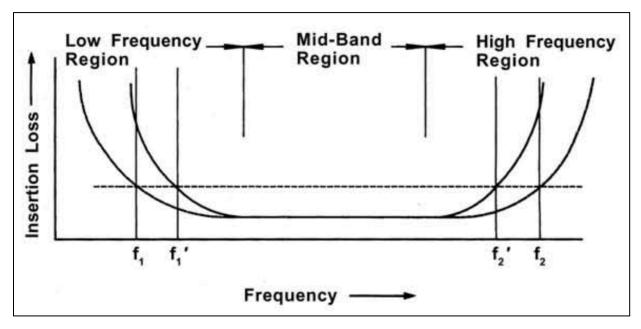

| Figure 2.5-1 Typical broadband transformer insertion loss vs frequency characteristic curve [44]. |

|                                                                                                   |

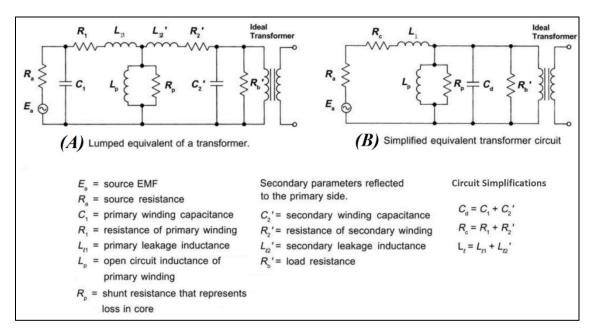

| Figure 2.5-2 Transformer equivalent circuit models: (a) Lumped model; (b) Simplified model [44].  |

|                                                                                                   |

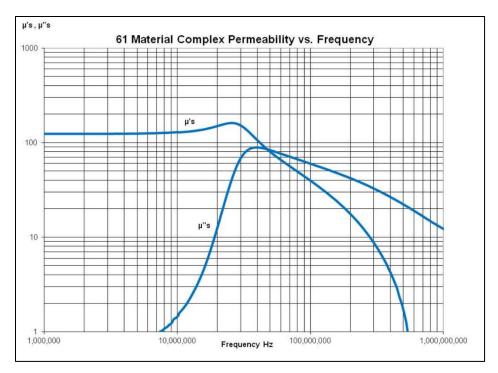

| Figure 2.5-3 Complex permeability vs frequency measured on standard toroids (18/10/6 mm) at                  |

|--------------------------------------------------------------------------------------------------------------|

| 25°C [47]                                                                                                    |

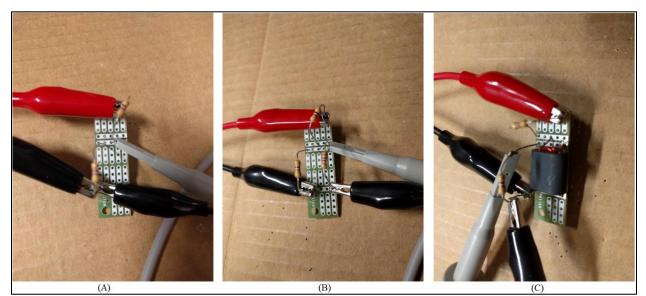

| Figure 2.5-4 Transformer insertion loss test setup: (A) Before Insertion; (B) $270\Omega$ resistor inserted; |

| (C) Transformer inserted                                                                                     |

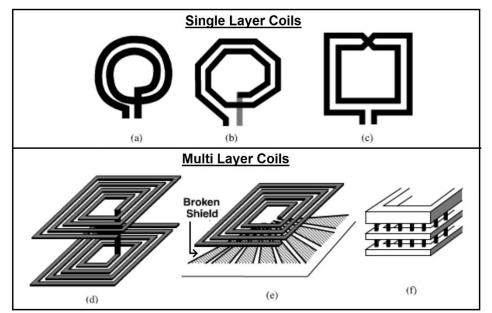

| Figure 3.1-1 Various spiral inductor structures: (a) circular; (b) octagonal; (c) symmetric; (d) series      |

| stacked; (e) with ground shield; (f) parallel stacked                                                        |

| Figure 3.1-2 Simple spiral inductor: (A) various physical parameter dimensions; (B) inductance               |

| and turn definitions [51]                                                                                    |

| Figure 3.1-3 Series stacked spiral inductors                                                                 |

| Figure 3.1-4 Effect of placing tightly coupled inductors in parallel                                         |

| Figure 3.1-5 Capacitance types and their models: (a) bottom plate capacitance and or multilayer              |

| series inductor capacitance; (b) interwinding Capacitance                                                    |

| Figure 3.1-6 Equivalent capacitance for series stacked inductors: (a) layers close together; (b)             |

| layers further apart                                                                                         |

| Figure 3.1-7 Substrate loss due to capacitive coupling                                                       |

| Figure 3.1-8 Metal resistance in spiral inductors                                                            |

| Figure 3.1-9 Current distribution in a conductor: (a) low frequencies; (b) high frequencies 72               |

| Figure 3.1-10 Proximity effect: (a) current distribution in adjacent turns; (b) eddy currents in the         |

| wire due to the magnetic field generated from a nearby adjacent wire; (c) reduction of the substrate         |

| and multilayer capacitance due to current crowding                                                           |

| Figure 3.1-11 Magnetic coupling to the substrate                                                             |

| Figure 3.2-1 Basic circuit diagram of an MCR-WPT coils system connected to a source and load                 |

| [53]                                                                                                         |

| Figure 3.2-2 Equivalent lumped circuit models of the MCR-WPT 4-coil system: (a) complete        |

|-------------------------------------------------------------------------------------------------|

| model; (b) simplified model [53]                                                                |

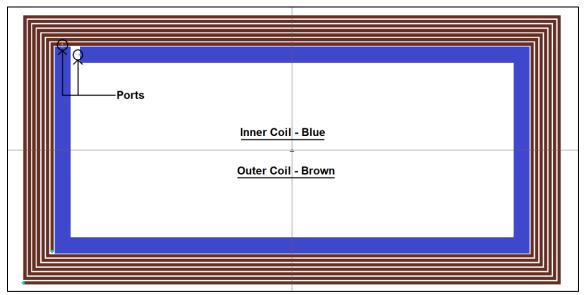

| Figure 3.2-3 Layout of PSC board with inner and outer coils and port connections in momentum.   |

|                                                                                                 |

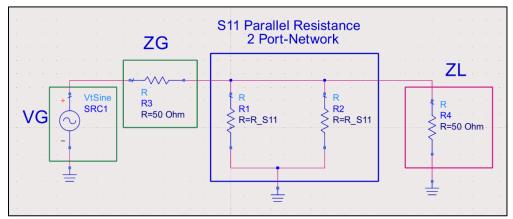

| Figure 3.2-4 Insertion loss analysis schematic used to calculate and predict the maximum S21    |

| MCR-WPT coils system                                                                            |

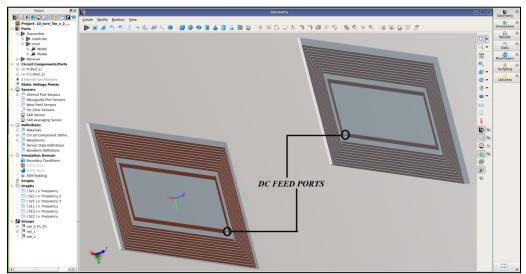

| Figure 3.2-5 Example EMPro 3D assembly of the MCR-WPT coils system with 2 ports                 |

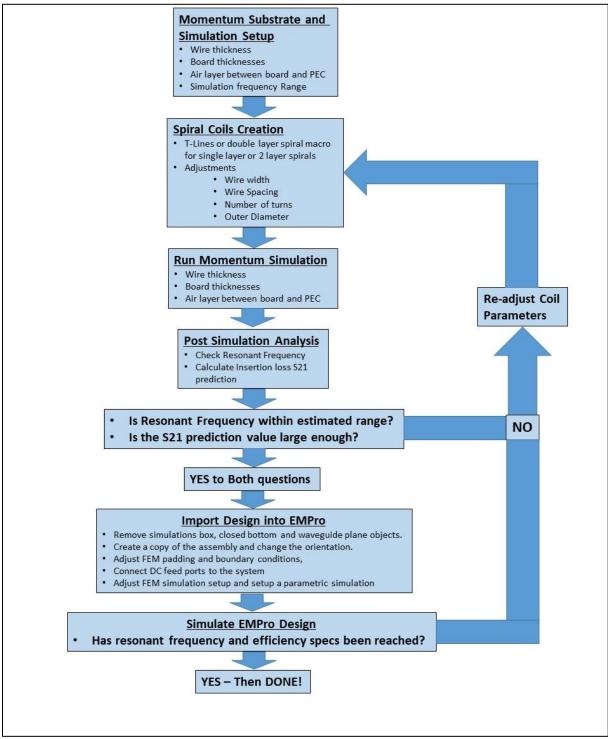

| Figure 3.2-6 MCR-WPT COILS SYSTEM DESIGN FLOW                                                   |

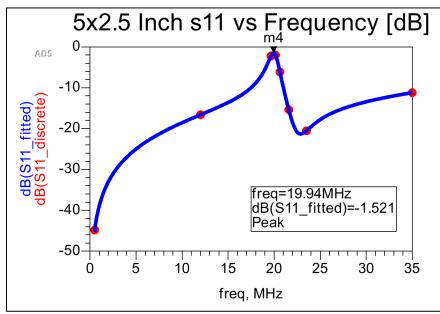

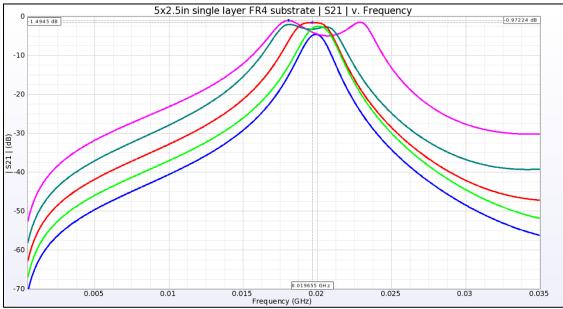

| Figure 3.2-7 5x2.5in single layer PSC board S11 momentum simulation data display result 89      |

| Figure 3.2-8 5x2.5in single layer PSC board S11-resistance momentum simulation data display     |

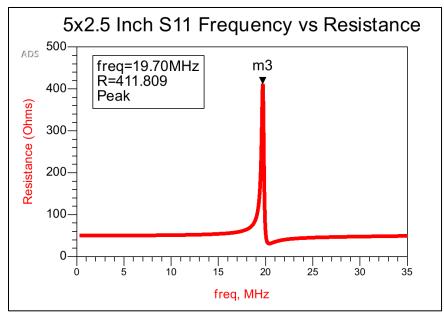

| result                                                                                          |

| Figure 3.2-9 single layer MCR-WPT coils S21 EMPro simulation result                             |

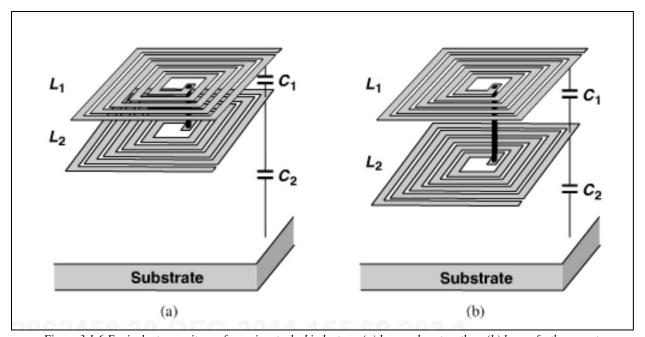

| Figure 3.3-1 Geometry of double layer parallel stacked MCR-WPT coils proposed in [57] 92        |

| Figure 3.3-2 Geometry of double layer series stacked MCR-WPT resonator coil proposed in [29].   |

|                                                                                                 |

| Figure 3.3-3 Geometry of double layer series stacked MCR-WPT resonator coil proposed in [30].   |

|                                                                                                 |

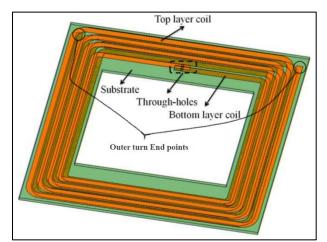

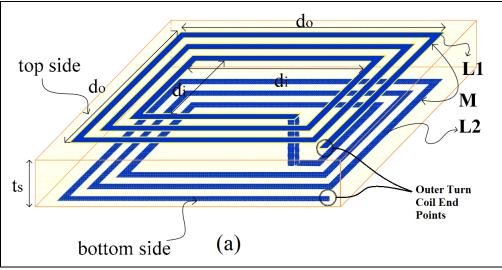

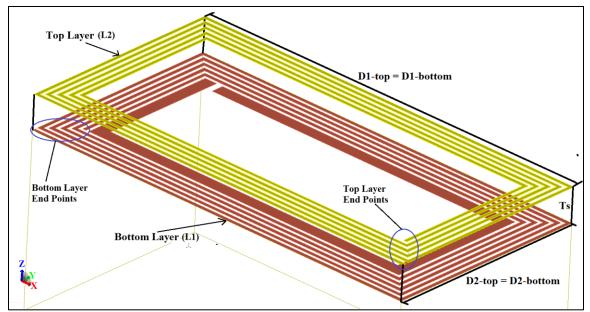

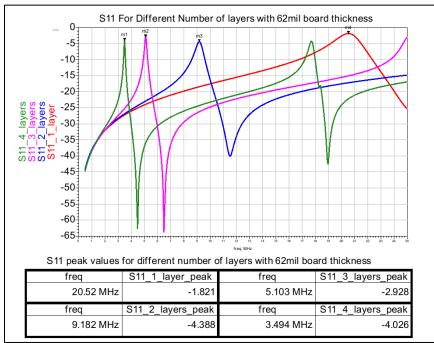

| Figure 3.3-4 Novel double layer MCR-WPT resonator coils design to reduce the SRF                |

| Figure 3.3-5 Momentum data display results for the effects of changing the number of layers on  |

| the SRF in the novel design with a 62mil PSC board thickness                                    |

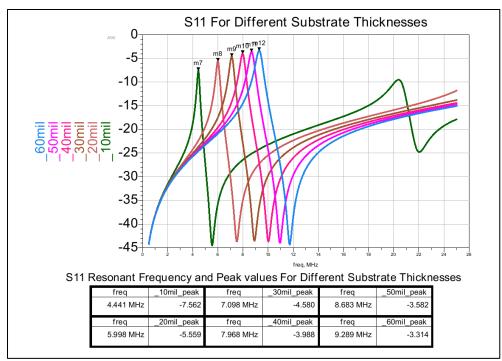

| Figure 3.3-6 Momentum data display results for the effects of changing the dielectric substrate |

| thickness on SRF in the double layer novel design                                               |

| Figure 3.3-7 Momentum data display results for the effects of changing the type of dielectric              |

|------------------------------------------------------------------------------------------------------------|

| substrate on SRF in the double layer novel design                                                          |

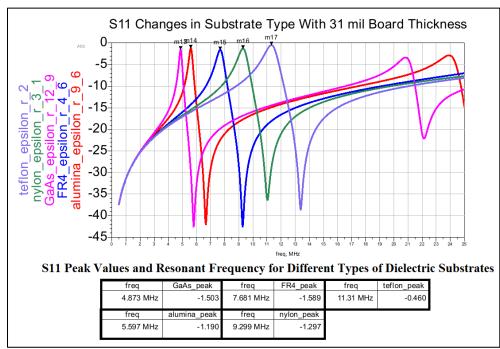

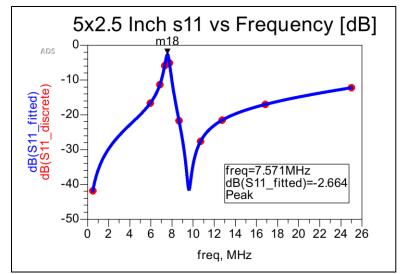

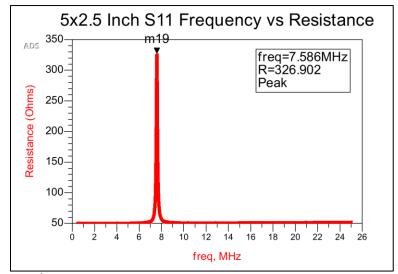

| Figure 3.4-1 5x2.5In <sup>2</sup> double layer FR4 PSC board S11 momentum simulation data display result.  |

|                                                                                                            |

| Figure 3.4-2 5x2.5In <sup>2</sup> double layer FR4 PSC board S11-resistance momentum simulation data       |

| display result                                                                                             |

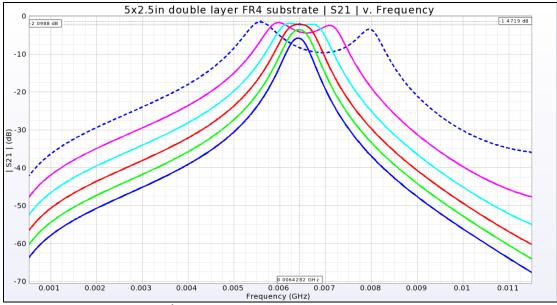

| Figure 3.4-3 5x2.5in <sup>2</sup> double layer FR4 MCR-WPT coils S21 EMPro simulation result 104           |

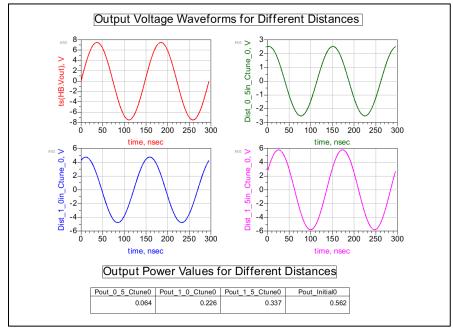

| Figure 3.4-4 5x2.5In <sup>2</sup> double layer FR4 MCR-WPT coil design harmonic balance transient and      |

| output power simulation data display results for multiple separation distances 105                         |

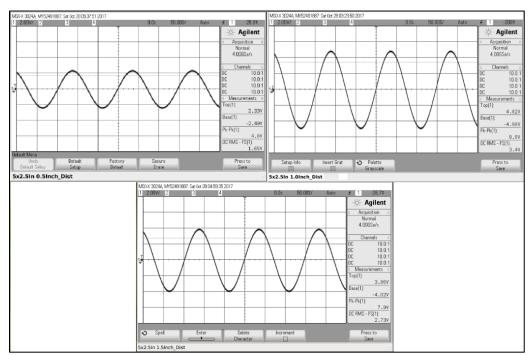

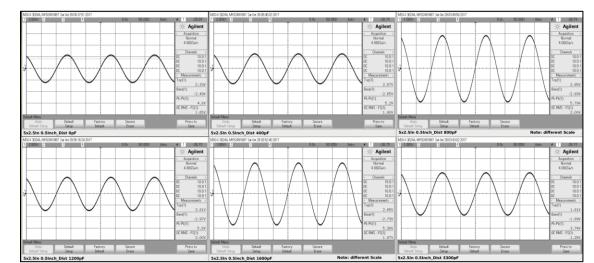

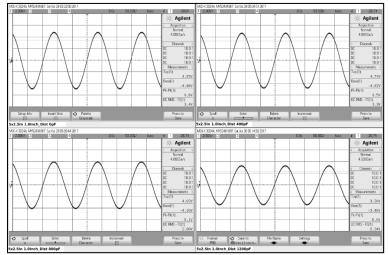

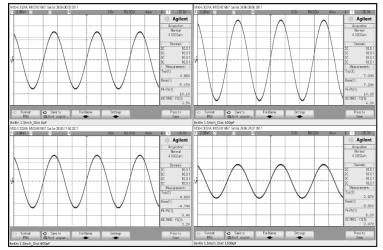

| Figure 3.4-5 5x2.5In <sup>2</sup> double layer FR4 MCR-WPT Coil test with function generator input at 0.5- |

| 1.5 inch separation distances                                                                              |

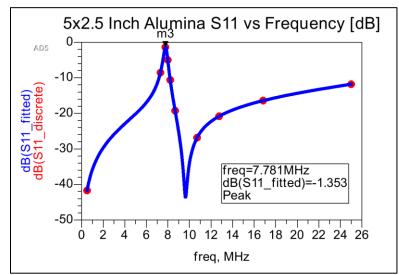

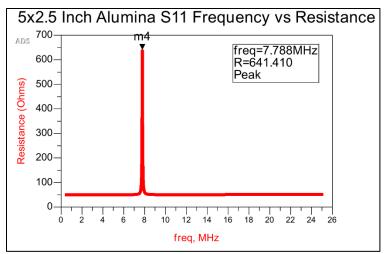

| Figure 3.4-6 5x2.5in double layer Alumina PSC board S11 momentum simulation data display                   |

| result                                                                                                     |

| Figure 3.4-7 5x2.5in double layer Alumina PSC board S11-resistance momentum simulation data                |

| display result                                                                                             |

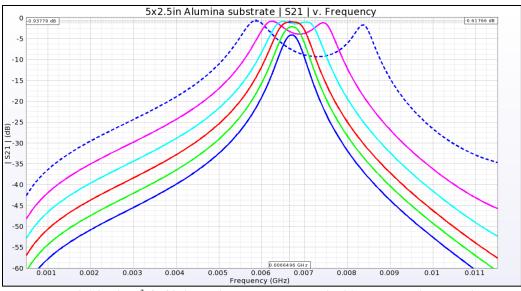

| Figure 3.4-8 5x2.5in <sup>2</sup> double layer Alumina MCR-WPT coils S21 EMPro simulation results. 110     |

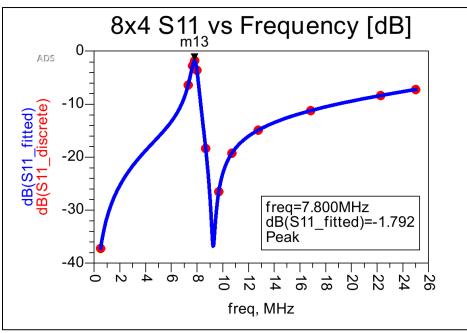

| Figure 3.4-9 8x4In <sup>2</sup> double layer FR4 PSC board S11 momentum simulation data display result.    |

|                                                                                                            |

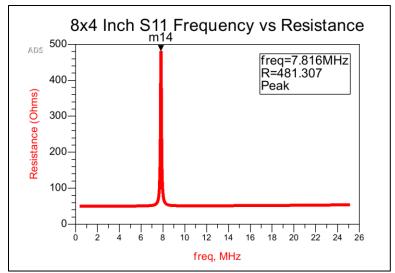

| Figure 3.4-10 8x4In <sup>2</sup> double layer FR4 PSC board S11-resistance momentum simulation data        |

| display result                                                                                             |

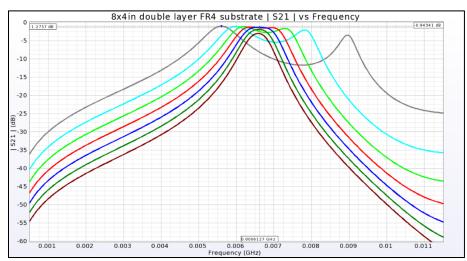

| Figure 3.4-11 8x4In <sup>2</sup> double layer FR4 MCR-WPT coils S21 EMPro simulation result 112            |

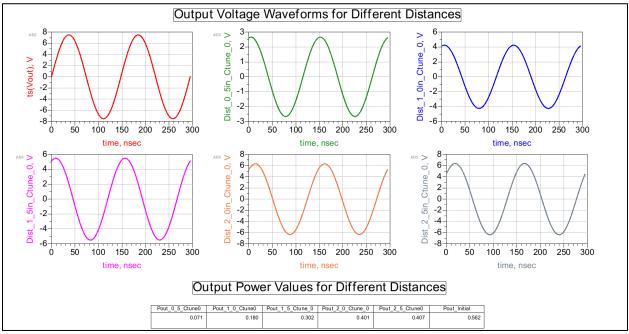

| Figure 3.4-12 8x4In <sup>2</sup> double layer FR4 MCR-WPT coil design harmonic balance transient and       |

| output power simulation data display results for multiple separation distances                             |

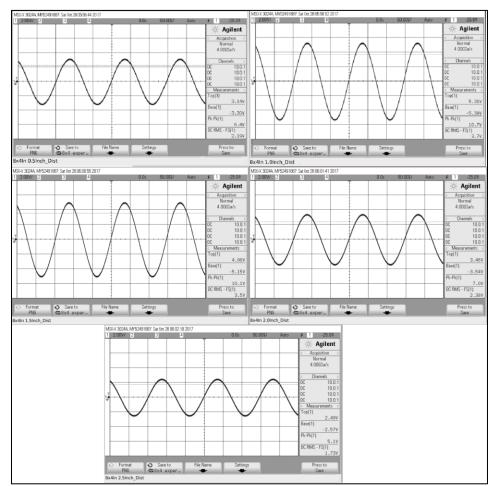

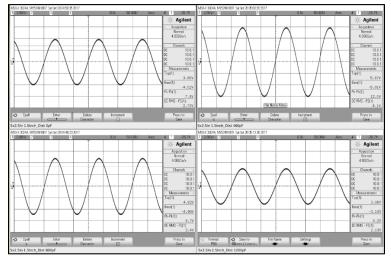

| Figure 3.4-13 8x4In <sup>2</sup> double layer FR4 MCR-WPT Coil test with function generation input at 0.5- |

|------------------------------------------------------------------------------------------------------------|

| 2.5 inch separation distances                                                                              |

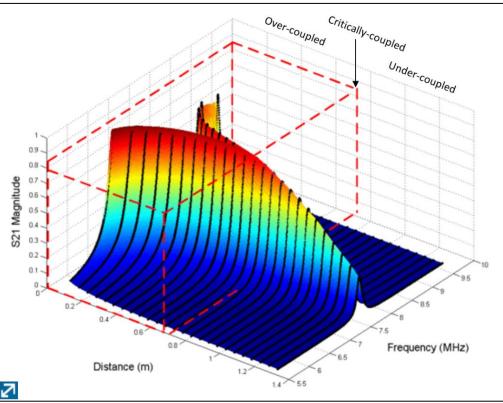

| Figure 4.1-1 S21 magnitude as a function of frequency and transmitter-to-receiver distance.                |

| Retrieved and modified from [65] 123                                                                       |

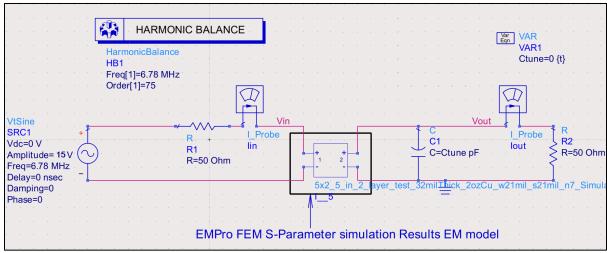

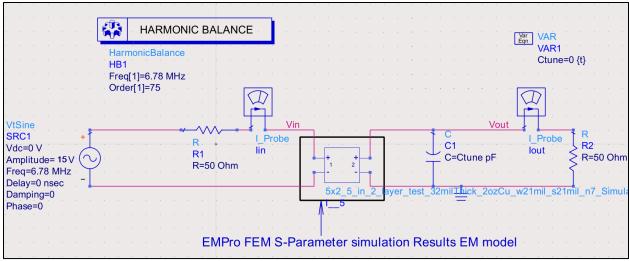

| Figure 4.1-2 Schematic Setup for harmonic balance simulation on the MCR-WPT coils in Keysight              |

| ADS 124                                                                                                    |

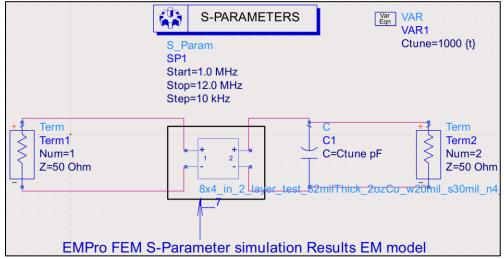

| Figure 4.1-3 Schematic setup for s-parameter simulation on the MCR-WPT coils in Keysight ADS.              |

|                                                                                                            |

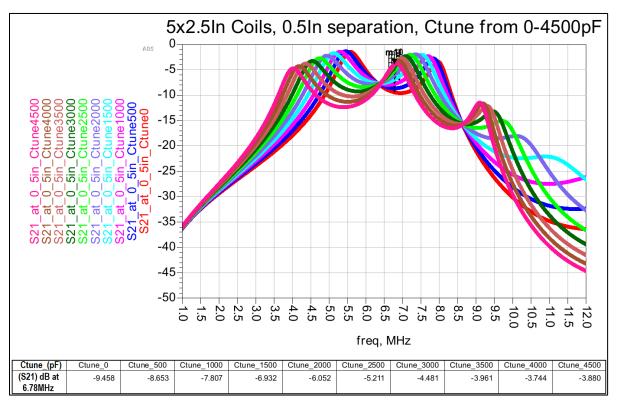

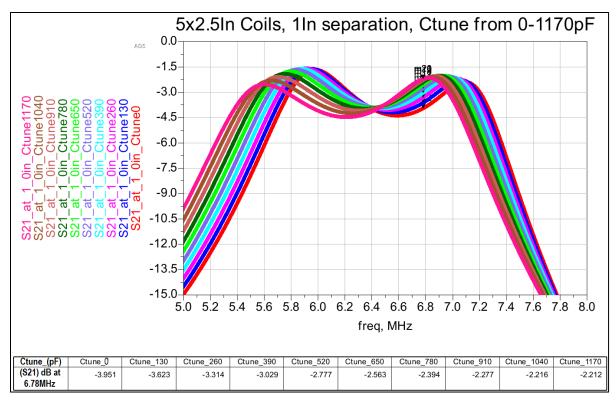

| Figure 4.1-4 5x2.5In MCR-WPT coil design s-parameter (S21) simulation data display results in              |

| ADS for 0.5 inch coil separation, C <sub>tune</sub> 0-4500pF                                               |

| Figure 4.1-5 5x2.5In MCR-WPT coil design s-parameter (S21) simulation data display results in              |

| ADS for 1in coil separation, C <sub>tune</sub> 0-1170pF                                                    |

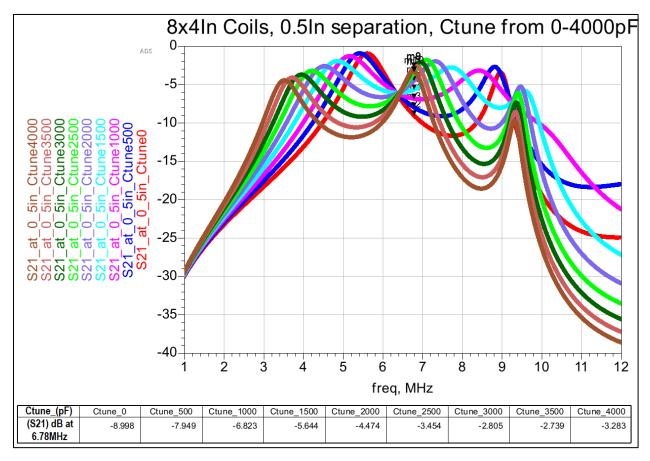

| Figure 4.1-6 8x4In MCR-WPT coil design s-parameter (S21) simulation data display results in                |

| ADS for 0.5 inch separation, C <sub>tune</sub> 0-4000pF                                                    |

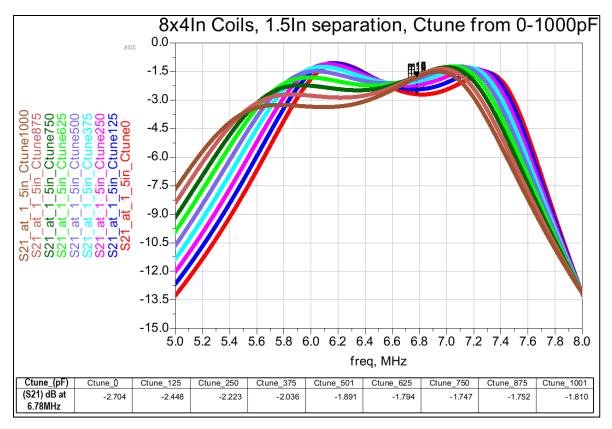

| Figure 4.1-7 8x4In MCR-WPT coil design s-parameter (S21) simulation data display results in                |

| ADS for 1.5inh separation, C <sub>tune</sub> 0-1000pF                                                      |

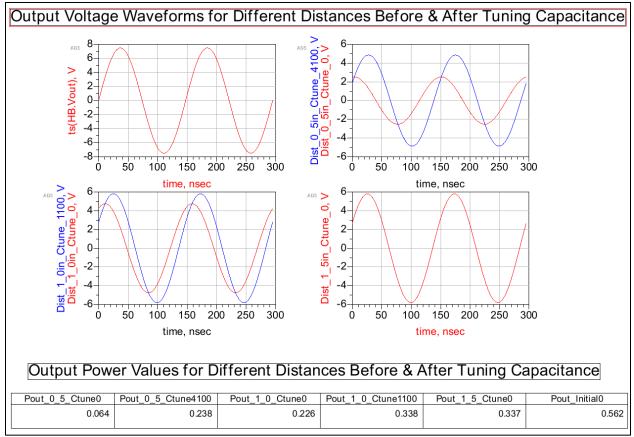

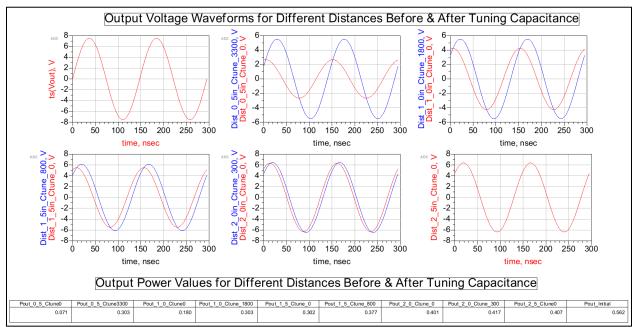

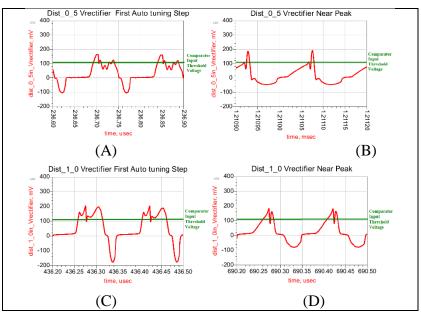

| Figure 4.1-8 5x2.5In MCR-WPT coil design harmonic balance transient and output power                       |

| simulation data display results for multiple separation distances before and after capacitance             |

| tuning                                                                                                     |

| Figure 4.1-9 8x4In MCR-WPT coil design harmonic balance transient and output power                         |

| simulation data display results for multiple separation distances before and after capacitance             |

| tuning                                                                                                     |

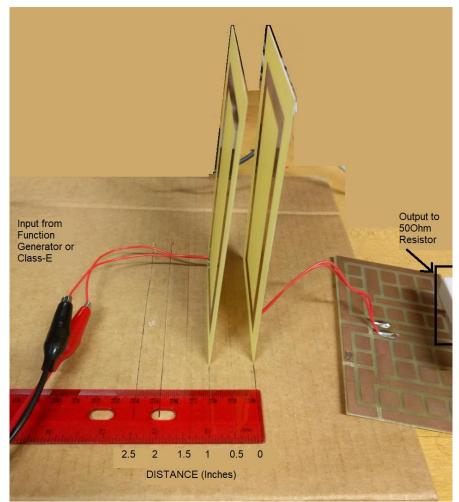

| Figure 4.1-10 Experimental test setup for MCR-WPT coil tuning during frequency splitting 130               |

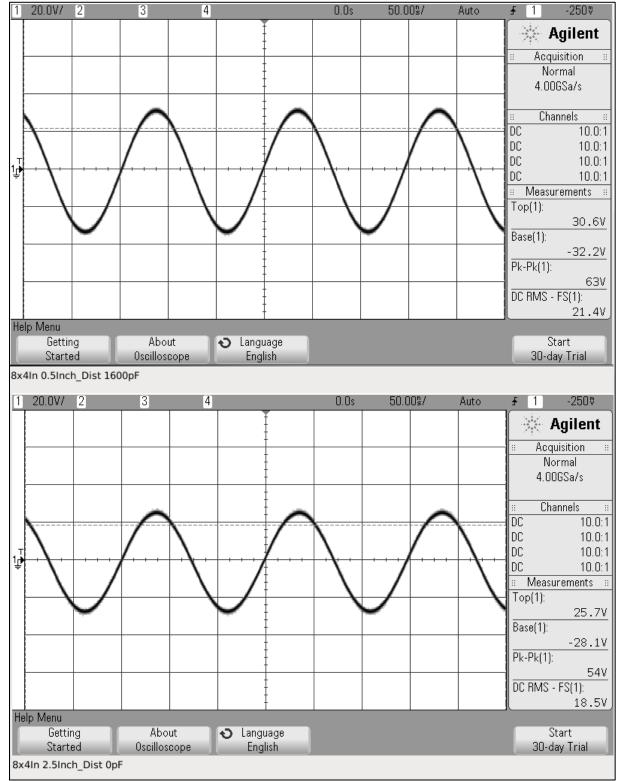

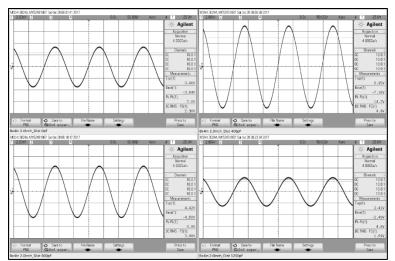

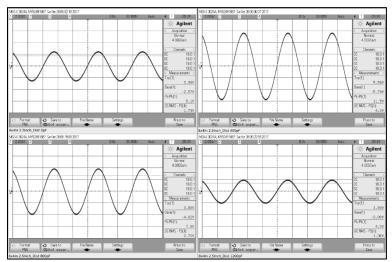

| Figure 4.1-11 8x4In MCR-WPT coils capacitive tuning test with Class-E PA input at 0.5in               |

|-------------------------------------------------------------------------------------------------------|

| separation distance                                                                                   |

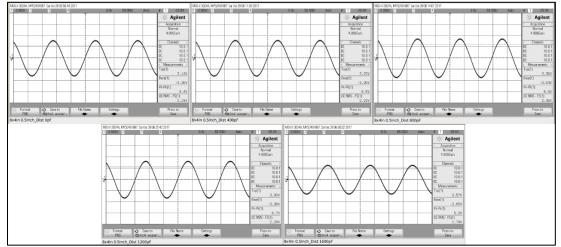

| Figure 4.1-12 5x2.5In MCR-WPT coils capacitive tuning tests with function generation input at         |

| 0.5in separation distance                                                                             |

| Figure 4.1-135x2.5In MCR-WPT coils capacitive tuning tests with function generation input at          |

| 1.0in separation distance                                                                             |

| Figure 4.1-14 5x2.5In MCR-WPT coils capacitive tuning tests with function generation input at         |

| 1.5in separation distance                                                                             |

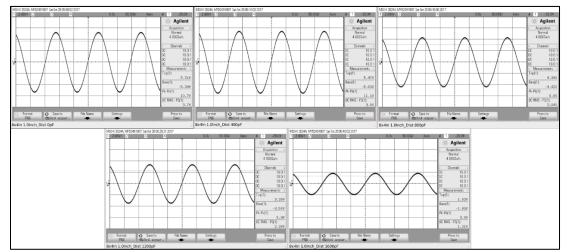

| Figure 4.1-15 8x4In MCR-WPT coils capacitive tuning tests with function generation input at           |

| 0.5in separation distance                                                                             |

| Figure 4.1-16 8x4In MCR-WPT coils capacitive tuning tests with function generation input at           |

| 1.0in separation distance                                                                             |

| Figure 4.1-17 8x4In MCR-WPT coils capacitive tuning tests with function generation input at           |

| 1.5in separation distance                                                                             |

| Figure 4.1-18 8x4In MCR-WPT coils capacitive tuning tests with function generation input at           |

| 2.0in separation distance                                                                             |

| Figure 4.1-19 8x4In MCR-WPT coils capacitive tuning tests with function generation input at           |

| 2.5in separation distance                                                                             |

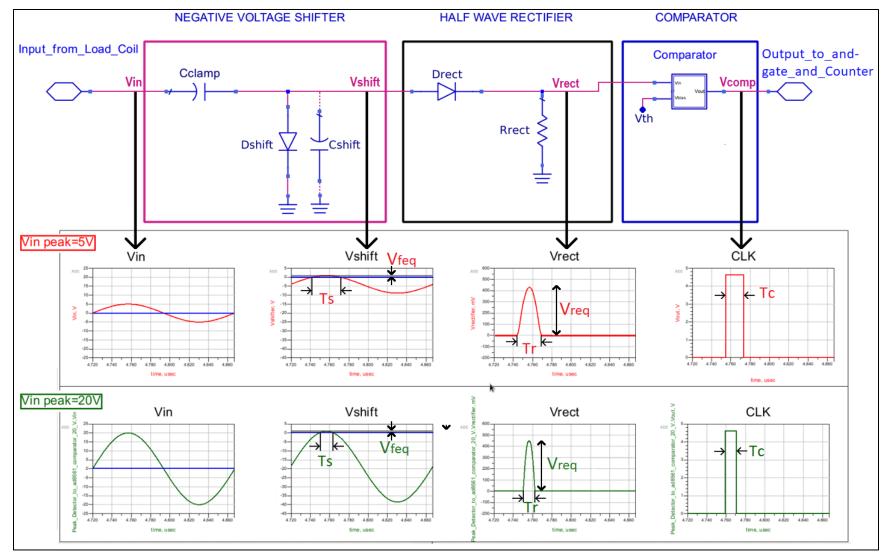

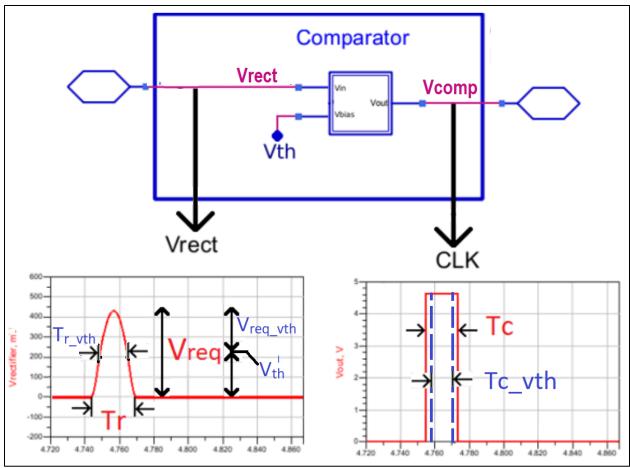

| Figure 4.2-1: Maximum peak detection circuit and with ideal nodal waveforms for 5V and 20V            |

| peak signals                                                                                          |

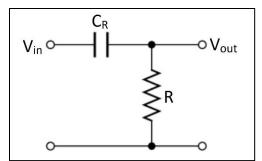

| Figure 4.2-2: High-pass filter formed by the half-wave rectifier in reverse bias mode, where $C_r$ is |

| the reverse bias capacitance                                                                          |

| Figure 4.2-3: Maximum peak detector comparator functionality when $v_{th} = 0V$ and $V > 0V$ 142      |

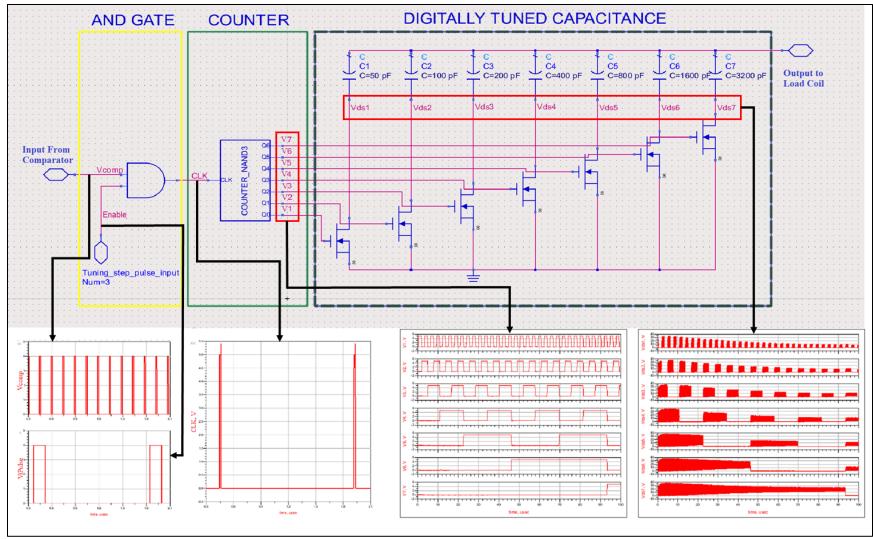

| Figure 4.2-4 Auto-tuning circuit with output plots at each node                                        |

|--------------------------------------------------------------------------------------------------------|

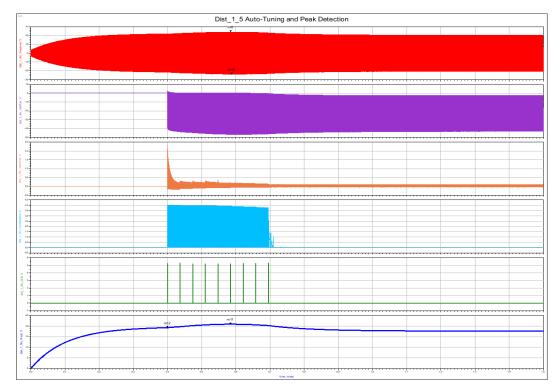

| Figure 4.3-1 Maximum peak detection and auto-tuning simulation test bench schematic in ADS.            |

|                                                                                                        |

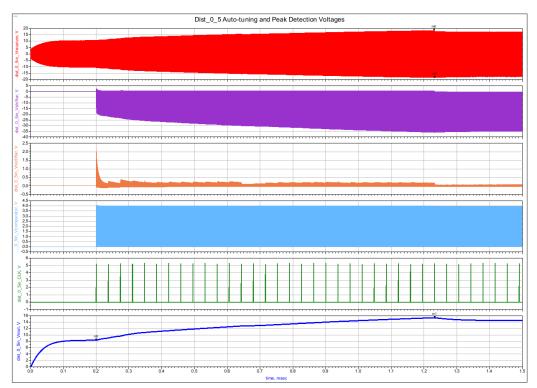

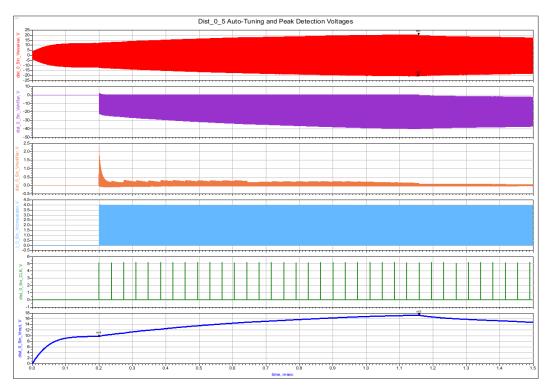

| Figure 4.3-2 5x2.5In MCR-WPT coil design maximum peak detection and auto-tuning simulation             |

| data display results in ADS at 0.5in distance152                                                       |

| Figure 4.3-3 5x2.5In MCR-WPT coil design maximum peak detection and auto-tuning simulation             |

| data display results in ADS at 1.0ih distance152                                                       |

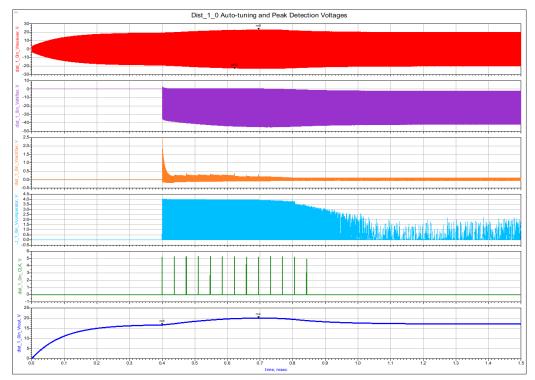

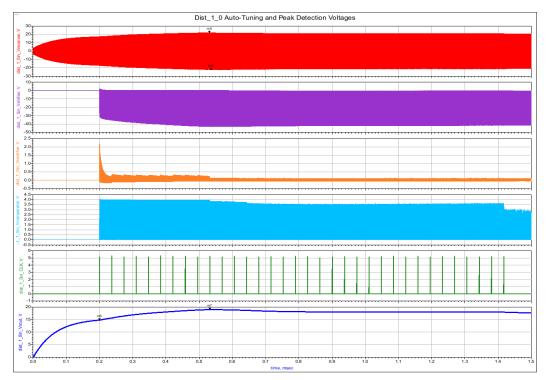

| Figure 4.3-48x4In MCR-WPT coil design maximum peak detection and auto-tuning simulation                |

| data display results in ADS at 0.5in distance                                                          |

| Figure 4.3-5 8x4In MCR-WPT coil design maximum peak detection and auto-tuning simulation               |

| data display results in ADS at 1.0in distance                                                          |

| Figure 4.3-6 8x4In MCR-WPT coil design maximum peak detection and auto-tuning simulation               |

| data display results in ADS at 1.5in distance154                                                       |

| Figure 4.3-7 5x2.5In MCR-WPT coil design maximum peak detection and auto-tuning output                 |

| power simulation data display results plots: (A) 0.5 inch separation distance; (B) 1.0 inch            |

| separation distance                                                                                    |

| Figure 4.3-8 8x4In MCR-WPT coil design maximum peak detection and auto-tuning output power             |

| simulation data display results plots: (A) 0.5in separation distance; (B) 1.0in separation distance;   |

| (C) 1.5in separation distance                                                                          |

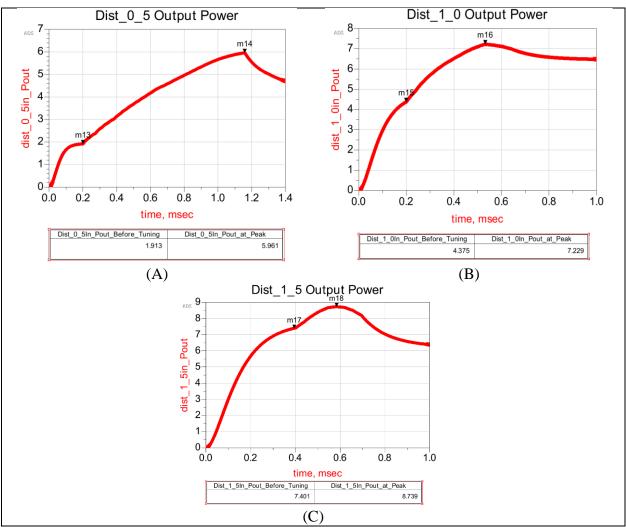

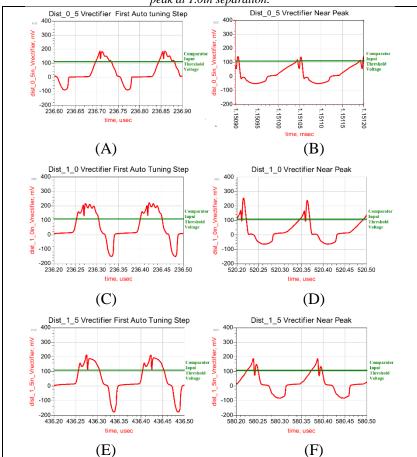

| Figure 4.3-9 5x2.5In MCR-WPT coil design maximum peak detection and auto-tuning simulation             |

| half wave rectifier simulation data display results plots: (A) and (B) first tuning step and near peak |

| at 0.5in separation; (C) and (D) first tuning step and near peak at 1.0in separation                   |

# List of Appendices

| A. Passive Voltage Level Shifters                          |     |

|------------------------------------------------------------|-----|

| A.1. Basic Operation and Considerations                    |     |

| A.2. Considerations Summary                                |     |

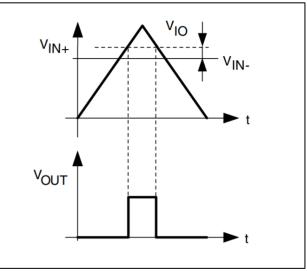

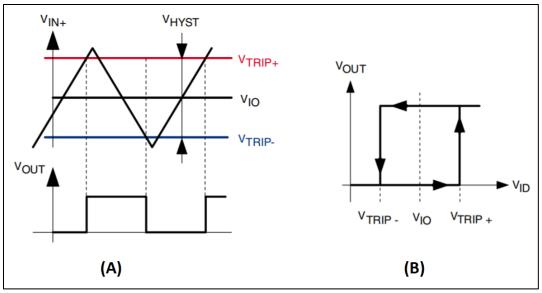

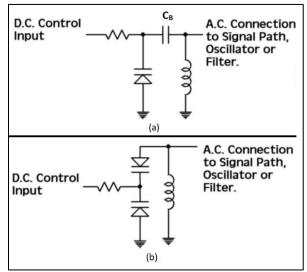

| B. Comparators                                             |     |

| B.1. Comparator Considerations                             |     |

| B.1.1. Input Offset Voltage (V <sub>IO</sub> )             |     |

| B.1.2. Hysteresis                                          |     |

| B.1.3. Input Common Mode Voltage Range (V <sub>ICM</sub> ) |     |

| B.1.4. Propagation Delay (t <sub>PD</sub> )                |     |

| B.1.5. Other Parameters to Be Considered                   |     |

| B.2. Comparator Considerations Summary                     |     |

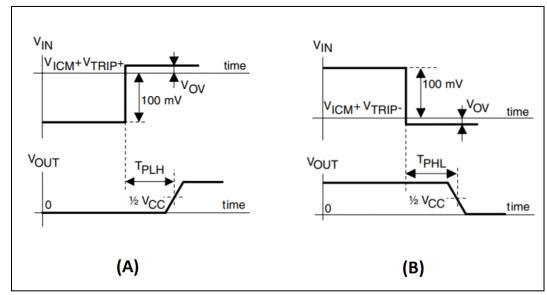

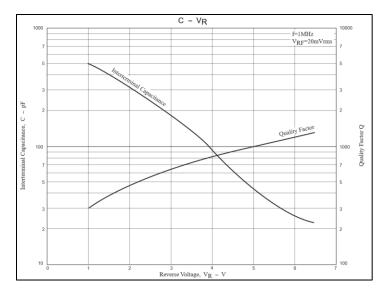

| C. Varactors                                               | 174 |

| C.1. PN-Junction Varactors (Vericap)                       |     |

| C.1.1. Basic Operation and Theory                          | 175 |

| C.1.2. Benefits, Drawbacks, and Availability               |     |

| C.2. Regular MOSFETs as varactors                          |     |

| C.3. Accumulation MOS Varactors                            |     |

| C.3.1      | Basic Operation and Theory                                                                              |  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| C.3.2      | Benefits, Drawbacks, and Availability 180                                                               |  |  |  |  |  |  |

| C.4. V     | Varactors Summary                                                                                       |  |  |  |  |  |  |

| Capacitor  | crete Charge Pump and Varactor using a Counter, MOS Switches, and Discrete<br>rs                        |  |  |  |  |  |  |

| D.1.1      | . Maximum Clock Frequency $(f_{max})$ , Propagation Delay $(t_{PD})$ , Setup and Hold Time              |  |  |  |  |  |  |

| (tsu a     | nd tw)                                                                                                  |  |  |  |  |  |  |

| D.1.2      | . Input transition rise or fall rate ( $\Delta t/\Delta v$ )                                            |  |  |  |  |  |  |

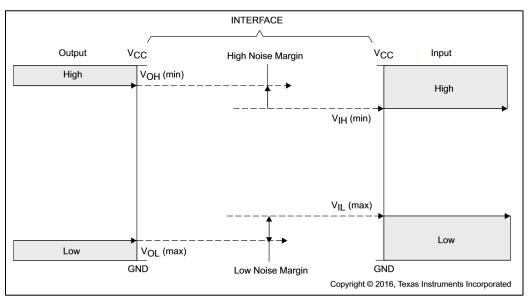

| D.1.3      | . Logic Compatibility between Devices and Effects of Different Supply Voltages                          |  |  |  |  |  |  |

| (VCC       |                                                                                                         |  |  |  |  |  |  |

| D.2. N     | AOS Switches                                                                                            |  |  |  |  |  |  |

| D.2.1      | . Drain-Source Breakdown Voltage (BV <sub>DSS</sub> ), Static Drain-Source On-Resistance                |  |  |  |  |  |  |

| $(R_{DS})$ | (NC)                                                                                                    |  |  |  |  |  |  |

| D.2.2      | . Gate Threshold Voltage ( $V_{GS(th)}$ ), Input Capacitance ( $C_{iss}$ ), Gate-Drain Charge ( $Q_g$ ) |  |  |  |  |  |  |

|            |                                                                                                         |  |  |  |  |  |  |

| D.3. S     | ummary 186                                                                                              |  |  |  |  |  |  |

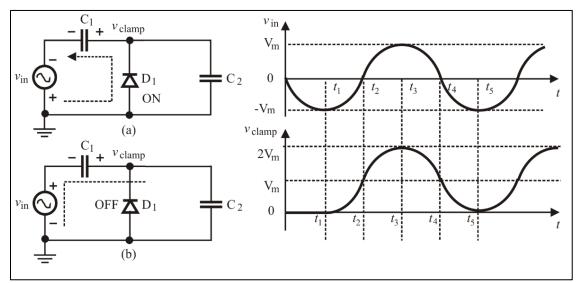

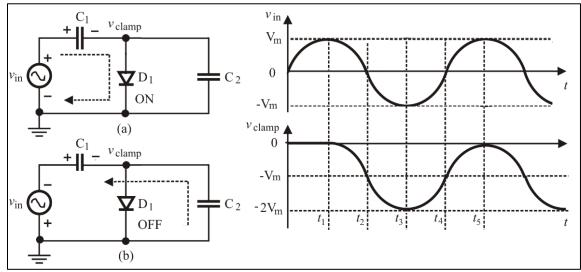

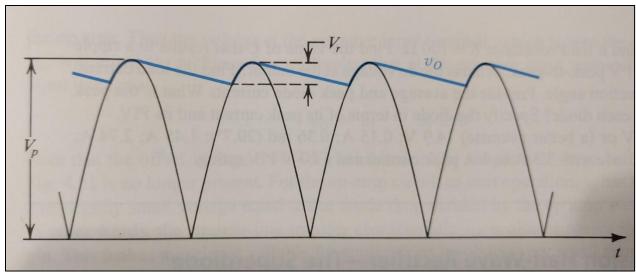

| F. Inser   | ge Rectifier and Filter Capacitor Background Theory                                                     |  |  |  |  |  |  |

# Abbreviations

| A4WP  | Alliance for Wireless Power         |  |  |  |

|-------|-------------------------------------|--|--|--|

| AC    | Alternating Current                 |  |  |  |

| ADS   | Advanced Design System              |  |  |  |

| BSIM  | Berkeley Short-channel IGFET Mode   |  |  |  |

| CAD   | Computer Aided Design               |  |  |  |

| CCD   | Critical Coupling Distance          |  |  |  |

| dB    | Decibel                             |  |  |  |

| dBm   | Decibel with respect to 1 Milliwatt |  |  |  |

| DC    | Direct Current                      |  |  |  |

| EM    | Electromagnetic                     |  |  |  |

| EMI   | Electromagnetic Interference        |  |  |  |

| EMPro | Electromagnetic Professional        |  |  |  |

| FEM   | Finite Element Method               |  |  |  |

| FET   | Field Effect Transistor             |  |  |  |

| FR4        | Flame Retardant 4                                                                        |  |  |  |

|------------|------------------------------------------------------------------------------------------|--|--|--|

| HF         | High Frequency                                                                           |  |  |  |

| IPC        | Association Connecting Electronics Industries (formerly -Institute Printed for Circuits) |  |  |  |

| kHz        | kiloHertz                                                                                |  |  |  |

| MCR-WPT    | Magnetically Coupled Resonant Wireless Power Transmission/Transfer                       |  |  |  |

| MCU        | Micro Controller Unit                                                                    |  |  |  |

| MHz        | MegaHertz                                                                                |  |  |  |

| mil one-th | nousandth of an inch                                                                     |  |  |  |

| MOM        | Method of Moments                                                                        |  |  |  |

| MOS        | Metal Oxide Semiconductor                                                                |  |  |  |

| MOSFET     | Metal Oxide Semiconductor Field Effect Transistor                                        |  |  |  |

| РА         | Power Amplifier                                                                          |  |  |  |

| PCB        | Printed Circuit Board                                                                    |  |  |  |

| PEC        | Perfect Electric Conductor                                                               |  |  |  |

| PRU        | Power Receiving Unit                                                                     |  |  |  |

| PSC        | Printed Spiral Coil                                                                      |  |  |  |

| PTU        | Power Transmitting Unit                                                                  |  |  |  |

| Rx         | Receiver                                                                                 |  |  |  |

SRF Self-Resonant Frequency

Tx Transmitter

- WPC Wireless Power Consortium

- WPT Wireless Power Transmission/Transfer

# **Chapter 1**

## 1 Introduction

The Airfuel (formerly known as A4WP) Rezence Wireless Power Transmission (WPT) standard was established 2012 [1] to wirelessly power portable devices. Researchers from MIT developed the Magnetically Coupled Resonant Wireless Power Transmission (MCR-WPT) techniques in 2007 [2] which the Rezence technology is based on. Some of the applications that the MCR-WPT technique is used in are charging TVs, electric vehicles and other large electronics [3], [4] and [5]. With this technique, Rezence has the ability to charge in smaller electronic devices such as tablets, smartphones and Bluetooth headsets [6]. These devices can be charged at a distance allowing for freedom of placement in horizontal and vertical dimensions for a true drop and go user experience [1]. Power solutions from 1-50W range allow it to support multi-device charging.

In this chapter, the basic background of the Rezence standard is presented in section 1.1. We then go through some of the design issues associated with the Rezence standard in section 1.2. This is followed by the contributions of this thesis in section 1.3. Then the thesis organization is briefly described in section 1.4. Finally, we conclude this chapter in section 1.5.

### **1.1 Background and Literature Review**

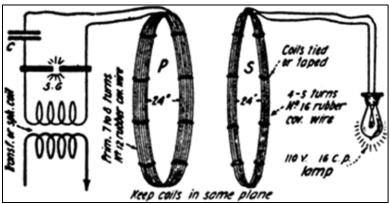

Wireless Power Transmission (WPT) has been around for more than a century. One of the earliest research done used wireless power and resonance techniques for a transformer system for electric railways in 1894 by M. Hutin and M. Leblanc [7], [8]. Extensive research was later done by Nicola Tesla on WPT, who by 1910s held many patents [9] for WPT applications including WPT using high-tension tesla coils [10], and an apparatus for transmitting electrical energy [11]. Tesla also did multiple other experiments with WPT, in one of them he used the experimental setup shown in Figure 1.1-1 to wirelessly power an electric light bulb using a pair of coils. Because of his broad and cutting-edge research on WPT, Tesla is considered a pioneer of the field [7].

There are multiple works done by Tesla in WPT that have helped to pave the way for the establishment of WPT. After Tesla, there was a pause in WPT research until after WWII [12], wherein 1962 the first long-range microwave WPT system was demonstrated by William C. Brown [13]. At around the same time in the 1960s, research was being done with short-range WPT systems for biomedical applications using inductive WPT such as in [14] and [15]. Lots more research was done over the next few decades using various types of WPT in different applications, which is discussed in more detail in [7] and [12].

Figure 1.1-1 One of Tesla's wireless power transmission experiment [7]

In 2007, a group of researchers from MIT demonstrated Wireless power transmission using strongly coupled magnetic resonance [2], also known as MCR-WPT [16]. The work uses impedance matching and resonance to extend the transmission distance to mid-range WPT. This new approach is the foundation of the WiTricity Drive11 WPT standard for cars [4], and the Airfuel Rezence WPT standard portable electronic devices [17].

### **1.1.1 Basic overall Architecture**

The Rezence WPT standard uses magnetic resonance, instead of inductance to wirelessly charge portable electronic devices. According to [6], it brings many improvements over its inductive counterparts for wireless charging, which include:

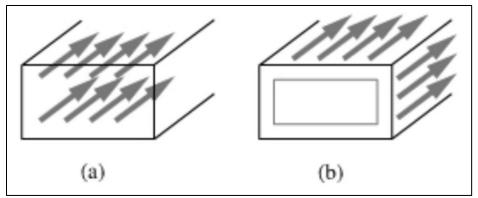

- Large charging range instead of being limited to a charging pad, the device can be placed anywhere in the charging range.

- **Multiple device charging** devices with different power requirements (such as smartphones and tablets) can be charged simultaneously.

- **Real world safe charging** Stray metallic objects such as keys and utensils tend to heat up in the presence of magnetic fields due to eddy currents generated in the metals. Due to the resonant nature of MCR-WPT, most of these object won't heat up unless they resonate at the transmission frequency, which reduces the risk of power loss in nearby stray metallic objects. Also using Bluetooth 4.0 LE, Rezence charging surfaces will only transmit power when compatible devices are present, thereby further reducing this hazard.

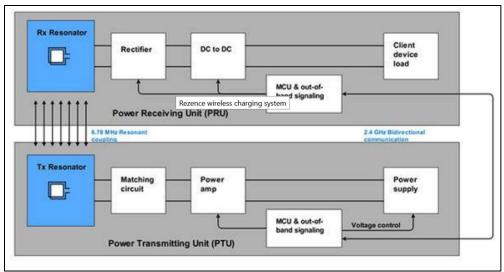

To accomplish these improvements, the Rezence WPT standard uses the system architecture provided in Figure 1.1-2. The standard transmits power using 6.78MHz resonators. The overall system which is composed of a Power Transmit Unit (PTU) and a Power Receiving

Figure 1.1-2 Rezence magnetic resonance wireless power specification [18]

Unit (PRU). The PTU is has a power supply block, Power Amplifier, matching network and transmitter Resonator (Tx). The PRU is has a Receiver Resonator (Rx), Rectifier, and DC-DC Converter. There are two Microcontroller Units (MCU), one at the PTU and PRU respectively. Each Block will be briefly discussed here and more detail in the subsequent chapters. There are 5 categories of PRU and 5 classes of PRUs which are presented in Table 1.1-1.

### **1.1.2** Communication between the MCU

The MCUs uses a propriety protocol via Bluetooth 4.0 LE (smart) to allow to PTU and PRUs to communicate with one another. This enables the PTU to identify compatible PRU

| Power Receiving Unit (PRU) |           | Power Transmitting Unit (PTU) |       |                                                  |

|----------------------------|-----------|-------------------------------|-------|--------------------------------------------------|

| Category                   | Bluetooth | (On                           | Class | (On Roadmap) – Supporting 1 category 1 device    |

| 1                          | Headset   | Roadmap)                      | 1     |                                                  |

| Category                   | Feature   | 3.5 Watts                     | Class | 10 Watts- Supporting 1 category 1, 2 or 3 device |

| 2                          | Phone     |                               | 2     |                                                  |

| Category                   | Smart     | 6 Watts                       | Class | 16 Watts – Supporting 2 category 1, 2, or 3      |

| 3                          | Phone     |                               | 3     | devices, or 1 category 4 device                  |

| Category                   | Tablet    | (On                           | Class | 22 Watts – Supporting 3 category 1, 2, or 3      |

| 4                          |           | Roadmap)                      | 4     | devices, or 1 category 4 device.                 |

| Category                   | Laptop    | (On                           | Class | (On Roadmap) – TBD                               |

| 5                          |           | Roadmap)                      | 5     |                                                  |

Table 1.1-1 PRU and PTU device classifications [6].

devices before it starts transmitting power. This is done to ensure that power is not transmitted in the presence of stray metallic objects. It is also used to adjust the Impedance Matching Network to improve the efficiency when the device is not at the optimal location for maximum efficiency. The protocol allows for the communication between PTU and PRUs so that the Power Amplifier input power can be adjusted to accommodate the number of PRUs in range

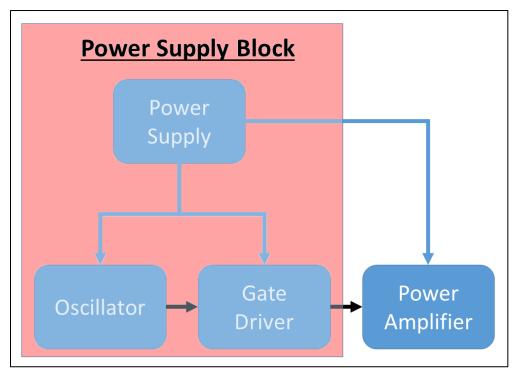

### 1.1.3 Power Supply, Oscillator, and Gate driver

The Power Supply block is composed of 3 sub-blocks including the Power Supply, Oscillator and Gate Driver as illustrated in Figure 1.1-3. The power supply provides a stable voltage supply for the oscillator, gate driver and PA. It can be adjusted to by the MCU to deliver a more or less power to the PA depending on how many Load devices need to be powered up. Since the oscillator and gate driver blocks need a constant voltage supply, a voltage regulator could be used to supply constant supply voltage in the presence of the changing power supply

Figure 1.1-3 Rezence power supply sub-blocks

There are many types of oscillators, such as the Colpitts, Crystal and Hartley Oscillators among others. Since the Rezence frequency specification is 6.78MHz  $\pm 15$ kHz, the oscillator accuracy and stability are a primary concern. Extra attention should be given to the selection of oscillator components that are unaffected by temperature and voltage variations.

Gate Drivers are used to supply the PA input with enough power so that it can function correctly. The gate of switch mode PAs must be charged and discharged quickly so that it acts as a switch, and can be done with two types of gate drivers, a square or sine wave. Both types of gate drivers need additional circuitry to operate correctly, where the square wave gate drivers need an analog to digital converter between the oscillator output and its input, and the sine wave gate driver needs an impedance matching network between its output and the PA input. The selection of the gate driver is dependent on which gate driver enables the PA to achieve higher output efficiency when applied to the PA input.

### 1.1.4 Power Amplifier and Impedance Matching

The Power Amplifier (PA) supplies to the power that the Tx Resonator transmits to the Rx resonator. There are many types of PAs available which are grouped into two main categories, namely controlled conduction angle and switch mode PAs. The controlled conduction angle PAs are composed of the common class A, AB, B and C PAs which have simpler designs, with the exception of the class C PA, generally have higher input to output power linearity at the cost of a lower efficiency. Switch mode amplifiers which include D, E, and other PA classes, use digital input signals to constantly drive the transistor output into saturation and cut-off regions by switching the input between "fully-ON" and "fully-OFF". These PAs generally have a higher efficiency, with some PAs achieving 100% efficiency, but they are non-linear, so additional circuitry is required to ensure the amplified input signal is not altered at the output. Power

Amplifier (PA) linearity is highly important when transmitting information and data. The Rezence resonators are not concerned with PA linearly since they only transmit power. Because of this switch-mode PAs like the class D and E are used for their high efficiency.

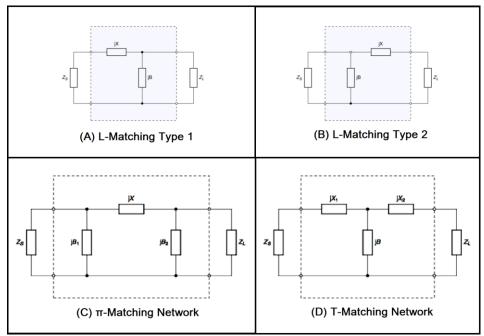

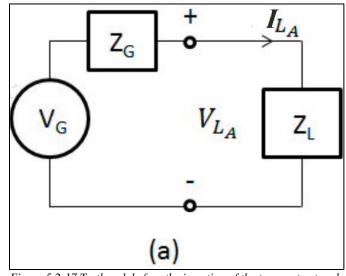

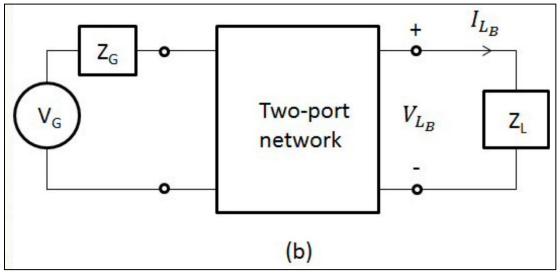

Regardless of the type of PA used to supply power to the TX resonator, the output must be impedance matched to the Tx resonator input to ensure maximum power transfer. This is done with a power matching network composed of capacitors and inductors which ideally have purely imaginary impedances with no resistive losses. In reality, all passive devices exhibit some resistive loss, but since the 6.78MHz Rezence operating frequency is much less than 300MHz (the frequency where transmission line effects should be taken into account the frequency wavelength is comparable to the wire trace lengths). There are a few basic impedance matching network topologies such as the L,  $\pi$  and T networks which are shown in Figure 1.1-4. Impedance matching theory is not discussed in detail in this thesis, but many books and articles that discuss the theory of these networks, example [19].

Figure 1.1-4 Basic impedance matching networks using lumped components

#### **1.1.5 Magnetic Coupling Resonant Wireless Power Transmission Coils**

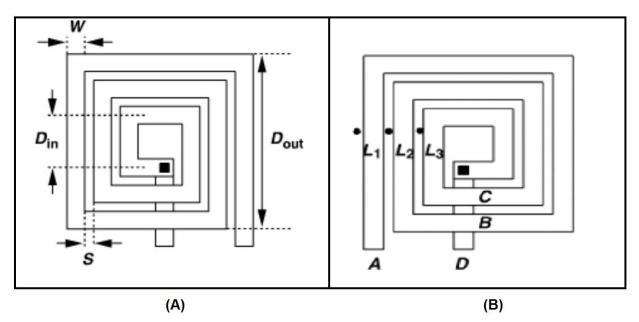

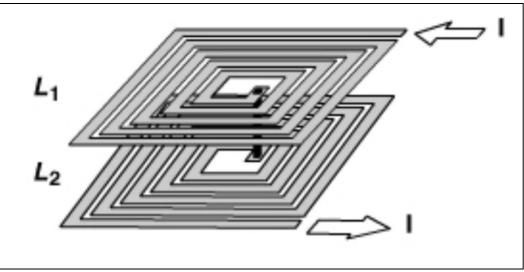

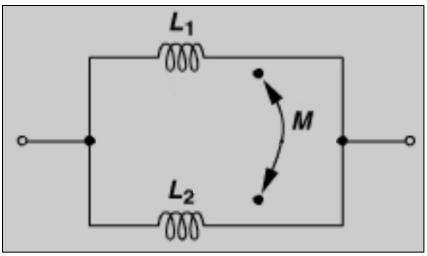

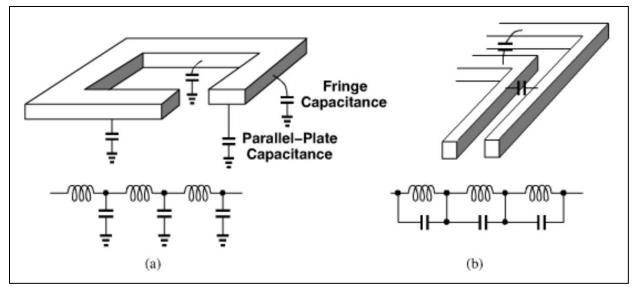

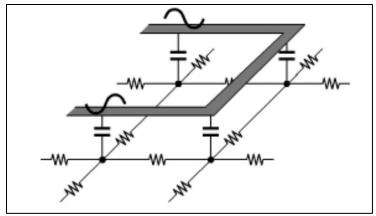

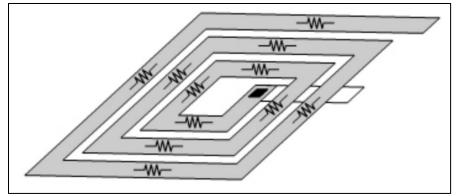

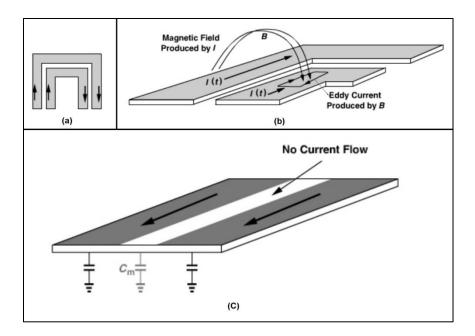

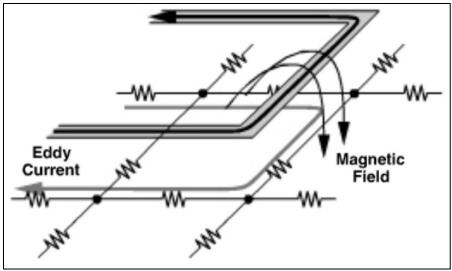

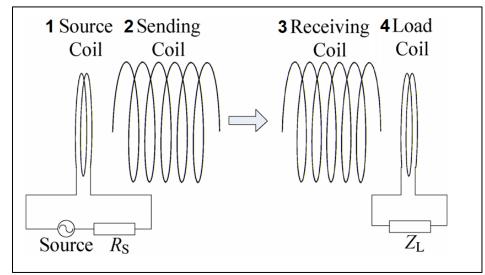

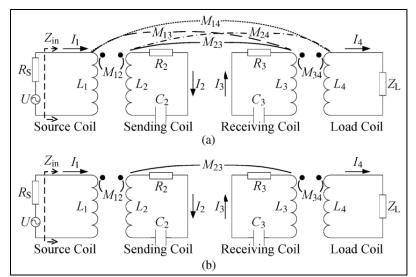

The Magnetic Coupling Resonant Wireless Power Transmission (MCR-WPT) coils used to design the Tx and Rx resonators, supply power to the PRU from the PTU. It does so by converting AC current to a resonant magnetic field at the Tx resonator, which is received by the Rx resonator and converted back to an AC current. The physical dimensions of the Tx and Rx resonators such as the number of turns, wire width, wire thickness, wire spacing, inner and outer coil diameters, and the number of layers have a direct impact on the self-inductance and selfcapacitance. These parameters also determine the efficiency, Self-Resonant Frequency (SRF), and the transmission distance between the Tx and Rx. There are multiple inductor coil geometries available which can be used for the resonator designs.

#### **1.1.6 Rectifiers and DC-to-DC converters**

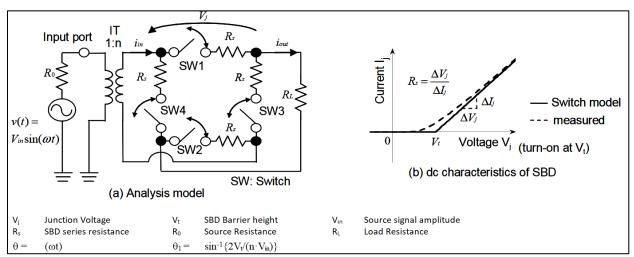

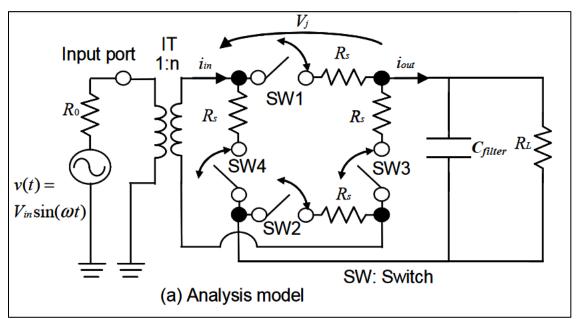

AC to DC rectification is generally implemented using a rectifier. There are many types of rectifiers used for both single and three phase systems which can be categorized into 3 groups, uncontrolled, half-controlled and fully controlled rectifiers, which are shown in Figure 1.1-5. When designing or selecting a rectifier for frequencies above 1MHz, extra attention should be placed on the reverse recovery time and reverse bias capacitance as they significantly reduce the rectifier efficiency.

DC-DC converters are used in a multitude of applications including electric motor drives, Switch mode DC power supplies, etc. There are two device categories, linear voltage regulators which have low efficiency, and switch mode DC-DC converters which can have efficiencies near 90%. The switch mode DC-DC converters can also be subdivided into types, converters with without isolation, such as the boost and buck converters, and converters with isolation, such as the full-bridge and push-pull converters among others [20]. For WPT system the Buck converters are

Figure 1.1-5 Types of rectifiers [21]

mostly used. The above material about converters are provided for informational purposes and is not discussed in detail in this thesis, but many books and articles that provide this information.

### **1.2 Motivations and Objectives**

Even with all these advantages, the Rezence standard has over the other WPT standards, the system suffers from an overall low transmission efficiency [22]. These efficiency challenges include difficulties designing high-efficiency PAs as revealed in section 1.2.1. Also low-efficiency MCR-WPT Tx and Rx resonators due to coil size restrictions on the coil parameters as mentioned in section 1.2.2. Finally, reduced efficiency occurs when the Rx resonator is not placed at the optimal separation distance from the Tx resonator which is brought up in section 1.2.3. Our objectives are, therefore, to simplify the design flow for a high power Class E PA, design MCR-WPT PSCs to achieve high efficiency at the 6.78MHz Rezence frequency specification, and to implement impedance match tuning to counteract changes in mutual inductance due to distance changes and improve efficiency

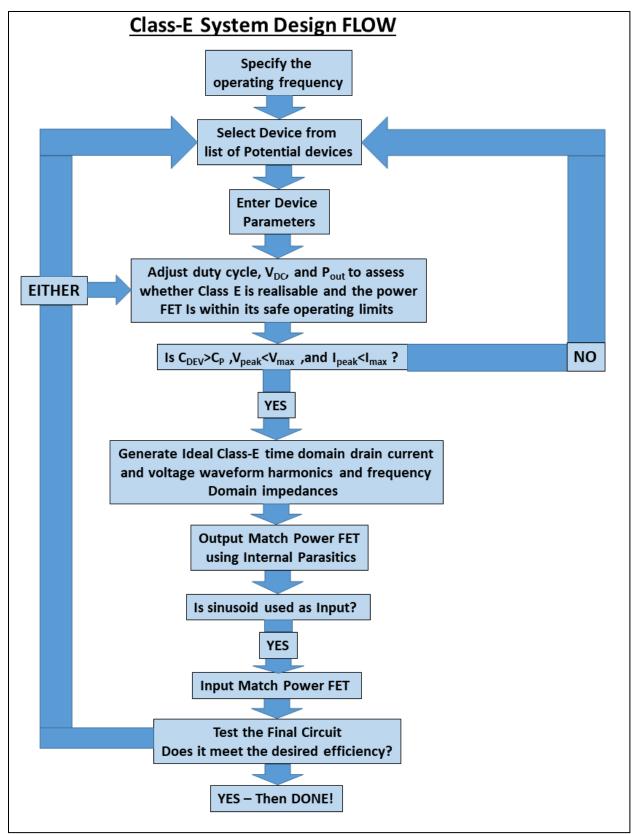

### 1.2.1 Class E PA design

Ideal Class-E PAs can achieve high efficiency using a relatively compact circuit topology, but they are difficult to design. The original work [23] takes into consideration a 50% duty and presents 3 equations that use the design frequency, output power, supply voltage, and knee voltage to determine the Class-E parallel capacitor, shifting inductor and load resistor values. These equations are simple but they don't give much insight into how to design a Class-E PA for a given specification, or how to impedance match the output. Therefore, there is a need to create a Class-E PA design flow that speeds up the design.

There are other parameters besides those used in [23] that should be considered when designing a Class-E PA. At a 50% duty cycle, large peak voltage and currents waveforms, which are high multiples of the supply voltages and currents, appear at the drain of the Power FET, so the Power FET's absolute maximum voltages and currents should be above these values to guarantee device reliability. Since the magnitude of these peak values is dependent on duty cycle, using a duty cycle other than 50% would decrease these current and voltage values enough, to allow for Class-E PA design using power FET devices unable to handle the 50% duty cycle peak values. There are theoretical design equations which include the duty cycle [24]. But these equations are lengthy, which makes them difficult to use to analytically design a Class-E PA. Other factors such as the Power FET's intrinsic output capacitance, should be considered to ensure proper Class-E operation during simulations and device reliability. There are also many other factors that need to be considered to realize physical prototype such as power FET power dissipation limits and temperature, passive component tolerances and available discrete values, capacitor maximum currents and voltages, inductor maximum current and SRF to name a few.

This thesis presents a proposed design flow based on [25], that simplifies and speeds up Class-E design for shortwave HF applications such as the Rezence 6.78MHz. Using this flow it is shown that a high-efficiency Class-E PA can be designed using a low-cost Power FET.

#### 1.2.2 Coil Design

Due to their small size Bluetooth devices, Feature phones and Smartphones place restrictions on the physical dimensions of an embedded MCR-WPT Rx Resonator. These size restrictions significantly affect the maximum efficiency and the minimum SRF that can be achieved when designing the MCR-WPT Rx Resonator. This is because the dimensions of the coils used in their design are directly related to the coil inductance. To increase the inductance of the coil, the number of turns and the inner and outer diameter must be increased, but this is limited by the device restrictions.

The available coil types that can be used to design the Rx is also limited. Previous MCR-WPT coil designs with high efficiency and low SRF using 4-coil helix [2], inner magnetic core [26], and non-planar (wire-wound) coils [27] designs can't be used in this application due to the thickness restrictions of these devices. However Printed Spiral Coils (PSC), whose design is based on spiral inductors that have been broadly used in RF Integrated circuit for many years [28] can be used in this application due to their small size

Single layer MCR-WPT PSCs can be designed to achieve a high efficiency in small devices. But when their size is decreased to fit in the devices, the SRF increases. This can be overcome by significantly increasing the wire thickness to increase capacitance and inductance, or by adding an external capacitor [16]. But this makes the coils too bulky for our application. Double layer MCR-WPT coils based on series stacked inductors which have been shown to reduce the SRF [29] and [30] have been used.

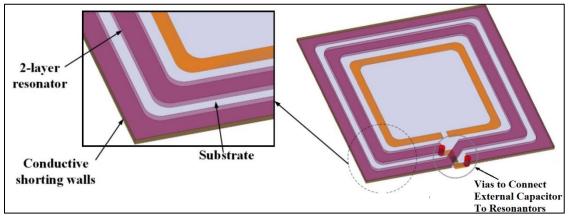

A proposed modified version of the double layer MCR-WPT PSCs without vias is presented in this thesis. We demonstrate that the efficiency can be increased and the SRF can be reduced to meet the specifications in the Rezence system without external passive components. It is also shown that the design can be further improved by changing the dielectric substrate and increasing the number of layers.

#### 1.2.3 Impedance Matching, and Tuning to Counteract Frequency Splitting

The Rezence system can wirelessly transmit power over a wide distance range and is capable of high-efficiency WPT at the optimal separation distance known as the Critical Coupling Distance (CCD), between the Tx and Rx resonators. However, when the Rx resonator is placed at a distance that is less than the CCD, the transmission efficiency decreases. This decrease in efficiency is from the frequency splitting phenomenon which is inherent to all MCR-WPT coils. Frequency splitting is caused by the change in mutual induction due to a change in separation distance less than the CCD, resulting in a reduced efficiency at the design frequency and the system resonating at two new frequencies which are higher and lower than the original design frequency.

To get the system back into resonance, either the transmission frequency, inductance or capacitance should be adjusted. The operating frequency can't be changed because the Rezence operating frequency specification is fixed and the Class E PA is a highly tuned frequency dependent circuit. Changes in the MCR-WPT coil Inductance is dependent on the physical parameters of the coils, and since these parameters are fixed after they are manufactured, they cannot be changed. Therefore, the only method that can be used counteract the effects of frequency splitting and bring the MCR-WPT coils system back to resonance is capacitive changes.

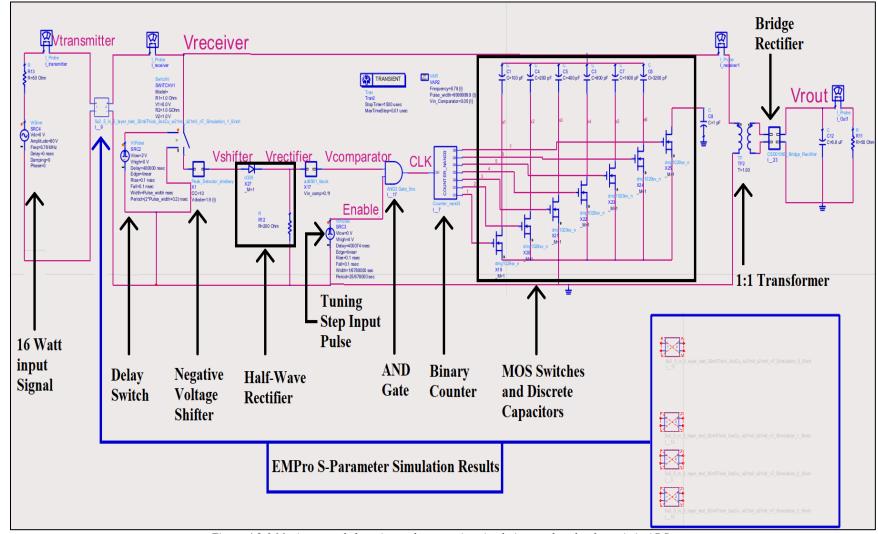

In this thesis, we propose a capacitive tuning method to counteract the effect of frequency splitting using a Maximum Peak Detection and Auto-Tuning circuit. We demonstrate through simulations that the system efficiency can be rapidly improved through this method.

## **1.3 Contributions of Thesis**

This section gives a summary of the original contributions contained in the different chapters of this thesis,

#### **1.3.1** High-Efficiency, Cost-Effective Class E Amplifier Design

This thesis proposes a high-efficiency Class E PA design flow. The design flow modified from [25] to design the Class-E PA at frequencies below 100MHz. The flow allows for rapid CAD design and assessment of Class-E PA using different Power FETs, and supply voltage, duty cycle and output power combinations. By following this flow, a Class-E PA circuit that has a low supply current and high supply voltage, and using a low-cost power FET was design with efficiency. Detailed information on the simulation and experimental setups and results are given

#### 1.3.2 Multilayer Spiral MCR-WPT PSC Design

A new planar spiral MCR-WPT PSC design with multiple layers is put forth in this thesis. Identical copies of the outer resonator coil which are rotated on the Z axis, or mirrored on the X or Y-axis, are placed on subsequent layers. This allows for a simple and symmetric design. Using this design we show that coil SRF is continually reduced with each additional metal layer while maintaining a relatively constant efficiency, and outer length, width and thickness dimensions. We also show that by changing the dielectric substrate material, the SRF can be further reduced with the efficiency kept relatively constant, or the efficiency can be increased with a constant frequency. This makes it possible to design smaller Tx and Rx resonators with high efficiency, making them attractive for smartphone and small Bluetooth device changing applications. Detailed MCR-WPT PSC simulation and experimental setups information and results are provided.

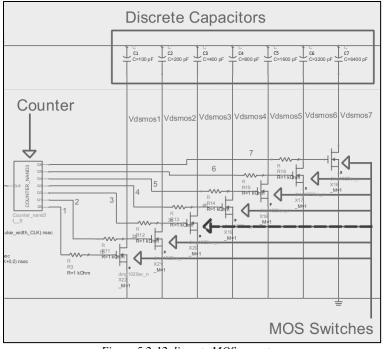

# **1.3.3 Capacitive Auto-Tuning Impedance Matching Technique for Improved** Efficiency

We propose a novel impedance matching auto tuning technique at the PRU of the Rezence system. This technique will both tune the resonant frequency of the coils and impedance match them to the Class E output. We demonstrate that it reduces energy loss through the Class E Power FET due to impedance mismatch and efficiency loss in the coils due to frequency splitting. The novel matching technique includes: (1) a discrete varactor tuning technique which includes a binary counter, MOS switches and discrete capacitor components, and (2) a self-tuning technique which use maximum peak voltage detection circuit composed of a negative voltage level shifter and comparator. Detailed simulation setup information and results are provided

# **1.4 Thesis Organisation**

This thesis presents the newly proposed techniques to improve the overall system efficiency, and is organized in the following order:

Chapter 2 presents the design of the component blocks of the Rezence system architecture. These blocks include the Power Supply, Class-E PA, and Rectifier blocks. The design of a 1:1 isolation transformer, required for the implementation of the auto-tuning system at the PRU, is also included. Particular focus is placed on the new Class-E design flow and the design of a highefficiency Class E PA. It includes extensive simulation and experimental results

Chapter 3 presents the design of the novel small profile, low SRF, and high-efficiency multi-layer spiral MCR-WPT PSC coils.

Chapter 4 presents the issues associated with MCR-WPT PSC coil systems, mainly frequency splitting. It then explores previous methods used to reduce the effects of this issue and then presents the new auto-tuning method used to counteract frequency splitting and improve efficiency with simulation results provided.

Chapter 5 we conclude this thesis and present future works that could be done for improved results.

# **1.5 Chapter Summary**

In this chapter, we presented an overview of the Rezence standard. The potential benefits of the Rezence standard were discussed as well as the basic building blocks that make up the Rezence architecture were introduced with brief descriptions. A short description of the design challenges associated with PA and MCR-WPT coil design that make it difficult to achieve high-efficiency at 6.78MHz is given. Another issue that was briefly discussed is the frequency splitting phenomenon which causes a decrease in transmission efficiency. New and novel methods used to address these issues by creating a modified design flow that simplifies Class-E PA design, a new multilayer planar spiral MCR-WPT PSC design achieve higher efficiency in small devices, and an auto-tuning design to counteract frequency splitting were presented.

# Chapter 2

# 2 Rezence WPT System Analog Component Blocks Design.

Rezence is the name given to the Airfuel (formerly the Alliance for Wireless Power - A4WP) WPT system standard in 2013 [6]. It is one of two main standards used for WPT in mobile devices, with the other being the WPC Qi standard. Based on the MCR-WPT design introduced in 2007 by a group of researchers from MIT [2], the Rezence WPT standard has the ability to transmit power over short distances. As mentioned in section 1.1.1, it is composed of PTU with a front-end power supply (which include an Oscillator and Gate Driver), an MCU, and Power Amplifier (PA) with impedance matching, and a Tx Resonator. It also has a PRU with an Rx transmitter, a regulator (which includes a rectifier according to [31]), DC-DC converter and an MCU.

We present the selection and design of the PTU and PRU analog blocks within the Rezence WPT system excluding the MCUs, DC-DC converter, and transmitters in this chapter. These analog blocks are the foundational circuitry required for the design and test of the novel MCR-WPT PSCs and Maximum Peak Detection and Auto-Tuning circuits presented in the later chapters of this thesis. The blocks are designed with the Rezence standard operating frequency of 6.78MHz, with the PTU unit between a Class3 and Class4 to supply power to category 4 devices and below. This chapter presents the design, simulations, and results of the analog component block of the Rezence WPT system. In section 2.1 we cover the specifications and derivations of the Rezence WPT system components. This is followed by the front end oscillator and gate driver selection and design discussed in Section 2.2. Then section 2.3 presents the design methodology, simulations, and results of the Class-E Power Amplifier. Next, the design and simulations of the RF bridge rectifier circuit are presented in Section 2.4. Finally, we conclude the chapter with the design and test results of an RF 1:1 transformer which is required for the implementation of the maximum peak detection and auto-tuning circuitry discussed in Section 2.5.

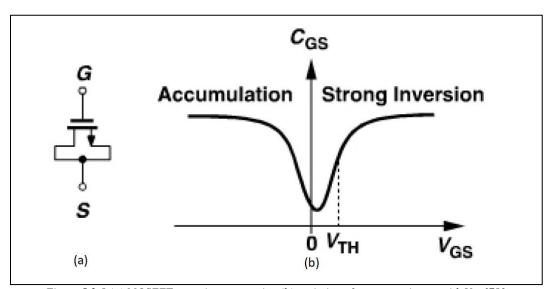

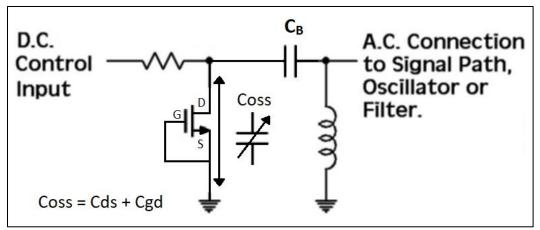

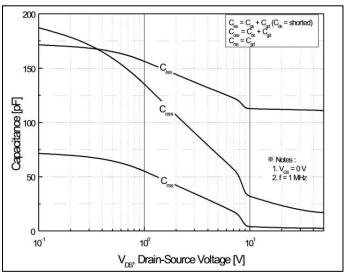

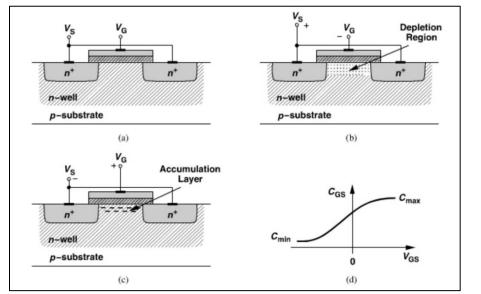

# 2.1 Rezence WPT System Blocks Efficiency Specifications.