#### **Ryerson University** Digital Commons @ Ryerson

Theses and dissertations

1-1-2007

## Embedded e-maintenance for an FPGA-based reconfigurable system

Dina Goldenberg Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

Goldenberg, Dina, "Embedded e-maintenance for an FPGA-based reconfigurable system" (2007). Theses and dissertations. Paper 308.

This Thesis Project is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

# Embedded e-Maintenance for an FPGA-based reconfigurable system

## By Dina Goldenberg

A project

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

**Master of Engineering**

in the department of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2007

© Dina Goldenberg 2007

UMI Number: EC53694

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform EC53694

Copyright 2009 by ProQuest LLC

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

| Author's  | $\mathbf{D}_{\alpha\alpha}$ | lamatian |   |

|-----------|-----------------------------|----------|---|

| Allinor S | Dec                         | iaramon  | • |

| I hereby declare that I am the sole author of this project.                                   |

|-----------------------------------------------------------------------------------------------|

| I authorize Ryerson University to lend this project to other institutions or individuals for  |

| the purpose of scholarly research.                                                            |

|                                                                                               |

|                                                                                               |

| Dina Goldenberg                                                                               |

|                                                                                               |

| I C. d D II. i i d d d d d d d d and                                                          |

| I further authorize Ryerson University to reproduce this project by photocopying or by        |

| other means, in total or in part, at the request of other institutions or individuals for the |

| purpose of scholarly research.                                                                |

|                                                                                               |

|                                                                                               |

| Dina Goldenberg                                                                               |

## **Borrow List**

Ryerson University requires the signatures of all persons using or photocopying this project.

Please sign below, and give address and date.

| Name | Signature | Address | Date |

|------|-----------|---------|------|

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

## Acknowledgement

I would like to express my deep gratitude to my supervisor Professor Lev Kirischian for his support and encouragement during my M.Eng project. I am very grateful for his guidance and valuable advice.

I would also like to thank the Department of Electrical and Computer Engineering and Embedded Reconfigurable Systems Lab (ERSL) for providing facilities and resources necessary for this project. My special thanks to Mr. Valeri Kirischian for his technical assistance during the experimental phase of this project.

## Embedded e-Maintenance for an FPGA-based reconfigurable system

#### **Abstract**

In recent years with the use of Internet Technologies e-Maintenance systems for remote diagnostics were introduced. connectivity, performance monitoring and reconfigurable systems based on FPGAs are becoming more and more popular due to their low time-to-market and reprogrammable feature, new possibilities for e-Maintenance are opened allowing remote repair of the system by sending new firmware via Internet for reconfiguration of FPGA. Up until recently programming of FPGA has been a complicated hardware design process. However, as FPGAs were evolving, their reconfiguration time was significantly reduced and partial reconfiguration became available, application programming into FPGA can be simplified as presented in [1]. This method is based on temporal partitioning of FPGA and periodically reloading it with segments of application for different tasks. This allows utilization of smaller and thus much cheaper FPGA and also simplifies the programming. With the help of e-Maintenance the whole system can be dynamically reconfigured. Remote programmer can perform partial reconfiguration, chose the physical location in FPGA for reconfiguration and upgrade different segments.

In this project a research of remote maintenance and reconfigurable systems is conducted and an e-Maintenance system is developed for an FPGA-based platform.

#### **Contents**

| 1. | Introduction                                  | 1  |

|----|-----------------------------------------------|----|

|    | 1.1 Motivation                                | 1  |

|    | 1.2 Project Objective                         | 2  |

|    | 1.3 Project Organization                      | 3  |

| 2. | Theory overview                               | 4  |

|    | 2.1 Introduction                              | 4  |

|    | 2.2 System Maintenance                        | 4  |

|    | 2.2.1 Testing Process                         | 6  |

|    | 2.2.2 Maintenance                             | 8  |

|    | 2.2.3 Diagnosis                               | 9  |

|    | 2.2.4 Built In Self Test                      | 11 |

|    | 2.2.5 System Monitoring                       | 12 |

|    | 2.3 E-Maintenance                             | 13 |

|    | 2.3.1 Internet Communication                  | 14 |

|    | 2.3.1.1 World Wide Web                        | 16 |

|    | 2.3.1.2 Hypertext Transfer Protocol (HTTP)    | 16 |

|    | 2.3.1.3 Transfer Protocols                    | 18 |

|    | 2.3.1.4 Transport Layer Protocols             | 19 |

|    | 2.3.2 E-Maintenance of Reconfigurable Systems | 22 |

|    | 2.4 FPGA-based Systems                        | 23 |

|    | 2.4.1 FPGA Architecture                       | 24 |

|    | 2.4.1.1 LUT-based Logic Blocks                | 24 |

|    | 2.4.1.2 SRAM-based Technology                            | 25 |

|----|----------------------------------------------------------|----|

|    | 2.4.1.3 Embedded RAM                                     | 26 |

|    | 2.4.1.4 Embedded Processor Cores                         | 27 |

|    | 2.4.2 Diagnosis of FPGA                                  | 29 |

|    | 2.4.3 Partial Reconfiguration of FPGA                    | 30 |

|    | 2.4.3.1 Run-Time Temporal Partitioning of FPGA Resources | 30 |

|    | 2.4.3.2 Macro-Programming of FPGA-based Systems          | 33 |

|    | 2.5 Summary                                              | 35 |

| 3. | System Development                                       | 36 |

|    | 3.1 Introduction                                         | 36 |

|    | 3.2 Functional Specification                             | 36 |

|    | 3.3 Requirements of the System                           | 37 |

|    | 3.4 System Architecture                                  | 38 |

|    | 3.5 Hardware/Software Partitioning                       | 39 |

|    | 3.6 System Hardware Components                           | 41 |

|    | 3.6.1 Serial Communication                               | 42 |

|    | 3.6.1.1 Serial Ports                                     | 42 |

|    | 3.6.1.2 RS-232                                           | 43 |

|    | 3.6.1.3 Ethernet Port                                    | 43 |

|    | 3.5.2 Memory                                             | 44 |

|    | 3.7 System Software Implementation                       | 44 |

|    | 3.7.1 TCP/IP Stack Initialization                        | 45 |

|    | 3.7.2 Interface Configuration                            | 45 |

|    | 3.7.                                      | .7.3 Allocating Socket Buffers 45        |                                     |    |  |

|----|-------------------------------------------|------------------------------------------|-------------------------------------|----|--|

|    | 3.7.                                      | .7.4 Specifying a Listen Queue           |                                     |    |  |

|    | 3.7.                                      | 5 HTTP                                   | server implementation               | 46 |  |

|    |                                           | 3.7.5.1                                  | HTML page                           | 46 |  |

|    |                                           | 3.7.5.2                                  | MIME Type Mapping Table             | 47 |  |

|    |                                           | 3.7.5.3                                  | CGI Functions                       | 47 |  |

|    |                                           | 3.7.5.4                                  | Resource Table                      | 48 |  |

|    |                                           | 3.7.5.5                                  | HTTP structure                      | 49 |  |

|    |                                           | 3.7.5.6                                  | Upload functionality implementation | 50 |  |

|    | 3.7.                                      | 6 Comn                                   | nunication With System Under Test   | 52 |  |

|    |                                           | 3.7.6.1                                  | Serial Port Setting                 | 52 |  |

|    |                                           | 3.7.6.2                                  | Communication Protocol              | 53 |  |

|    | 3.8                                       | Summary                                  | ,                                   | 55 |  |

| 4. | Exp                                       | erimental                                | Results                             | 56 |  |

|    | 4.1                                       | Introducti                               | ion                                 | 56 |  |

|    | 4.2                                       | Testing M                                | <b>1</b> ethodology                 | 56 |  |

|    | 4.3                                       | Experime                                 | ental Setup                         | 57 |  |

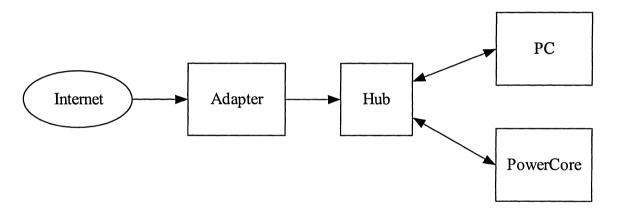

|    | 4.4                                       | Setting th                               | e Network                           | 60 |  |

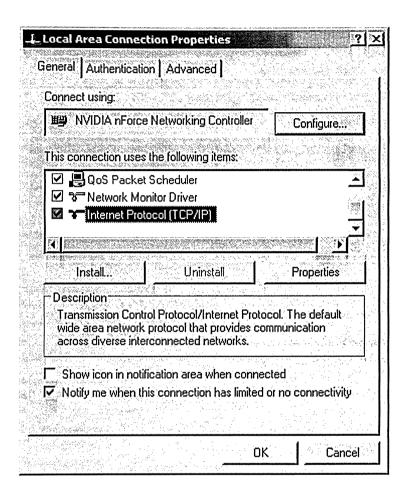

|    | 4.5                                       | Configuri                                | ng the IP Address                   | 60 |  |

|    | 4.6                                       | HTTP Sea                                 | rver Test                           | 62 |  |

|    | 4.7                                       | Upload and Download Functionality Test 6 |                                     |    |  |

|    | 4.8 Communication with FPGA Platform Test |                                          |                                     | 67 |  |

|    | 4 9                                       | Remote FPGA Reconfiguration Test         |                                     |    |  |

| 4.10 Timing Analysis of Remote Reconfiguration of the FPGA 6       |                                               |    |  |

|--------------------------------------------------------------------|-----------------------------------------------|----|--|

| 4.10.1 Bau                                                         | nd Rate Test                                  | 69 |  |

| 4.10.2 FPGA Platform Response Time                                 |                                               | 70 |  |

| 4.10.3 File                                                        | Transmission Initialization Time              | 71 |  |

| 4.10.4 Bits                                                        | stream Upload Time                            | 72 |  |

| 4.11 Estimation                                                    | of Remote Reconfiguration for Xilinx Virtex 4 |    |  |

| Family of F                                                        | FPGAs                                         | 73 |  |

| 4.12 Summary                                                       |                                               | 75 |  |

| 5. Conclusions                                                     |                                               | 76 |  |

| References                                                         |                                               | 78 |  |

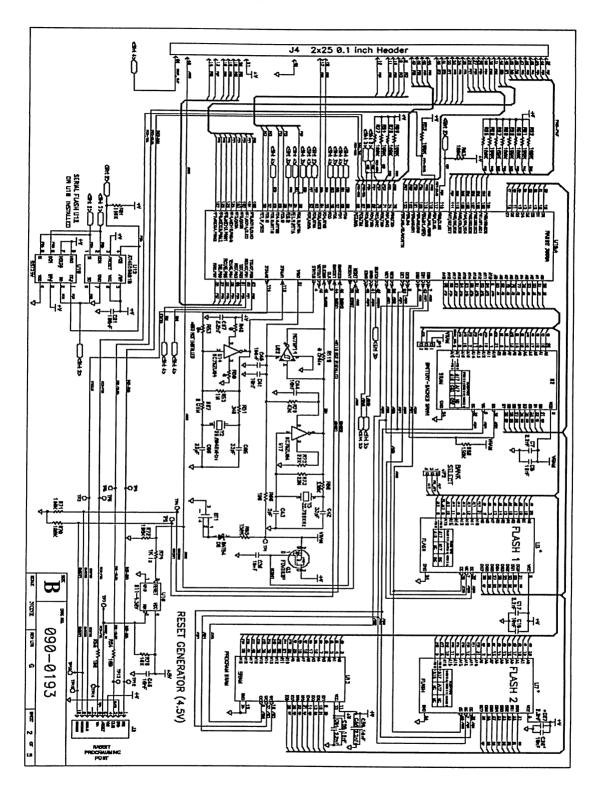

| Appendix A1 – Schematic                                            | Diagram PowerCore FLEX                        | I  |  |

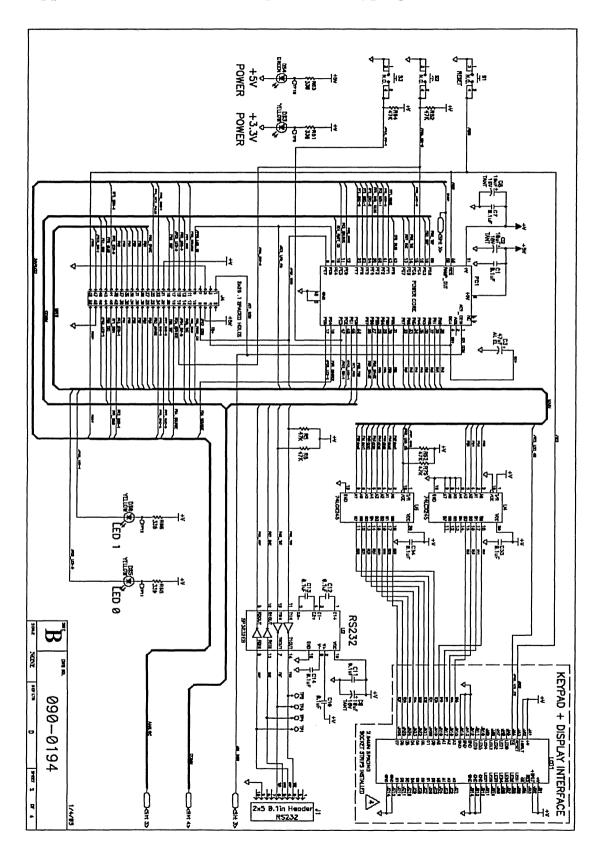

| Appendix A2 – Schematic Diagram Prototyping Board                  |                                               |    |  |

| Appendix B1 – Photographic Image of e-Maintenance System Prototype |                                               |    |  |

| connected to FPGA-based Platform III                               |                                               |    |  |

| Appendix B2 – Photograp                                            | hic Image of System Setup for Measurements    | IV |  |

| Appendix B3 – Photographic Image of the Whole System Setup V       |                                               |    |  |

| Appendix C – Source Code for e-Maintenance System VI               |                                               |    |  |

| Appendix D – HTML Source XI                                        |                                               |    |  |

## List of Figures

| Figure 2.1. System realization process                                   | 5  |

|--------------------------------------------------------------------------|----|

| Figure 2.2. Principal of testing                                         | 6  |

| Figure 2.3. BIST hierarchy                                               | 11 |

| Figure 2.4. E-maintenance system                                         | 13 |

| Figure 2.5. TCP/IP reference model                                       | 14 |

| Figure 2.6. Data flow and header utilization within TCP/IP network       | 15 |

| Figure 2.7. The TCP header                                               | 20 |

| Figure 2.8. The UDP header                                               | 21 |

| Figure 2.9. Generic FPGA architecture                                    | 23 |

| Figure 2.10. A simplified view of programmable logic block               | 24 |

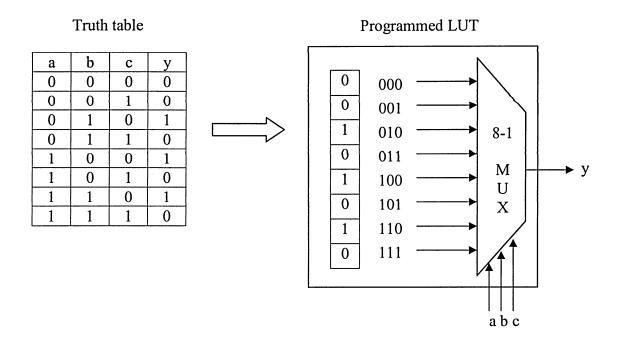

| Figure 2.11. LUT configuration                                           | 25 |

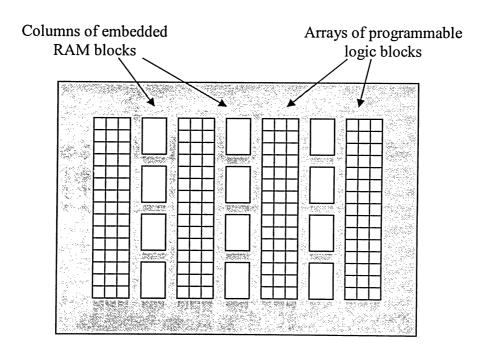

| Figure 2.12. Simplified view of chip with embedded RAM blocks            | 26 |

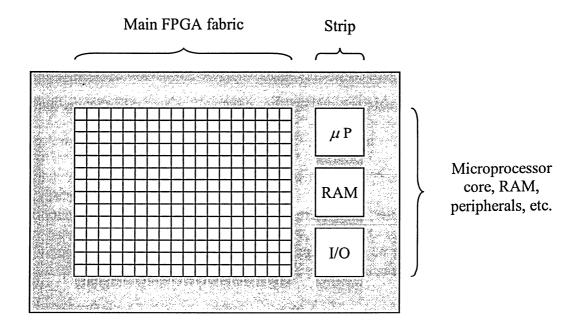

| Figure 2.13. Chip with embedded core outside of the main fabric          | 28 |

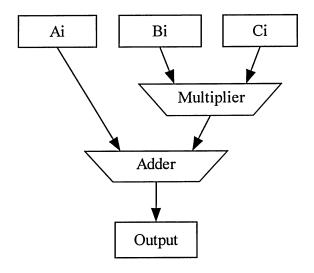

| Figure 2.14. Stream processing circuit for $Z_i = A_i + B_i \times C_i$  | 31 |

| Figure 2.15. Run-time temporal partitioning                              | 32 |

| Figure 2.16. Utilization of Macro-Operators                              | 34 |

| Figure 3.1. Overall system block diagram                                 | 38 |

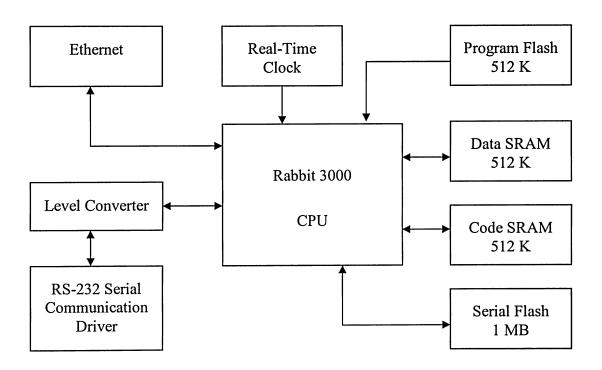

| Figure 3.2. PowerCore Subsystems                                         | 41 |

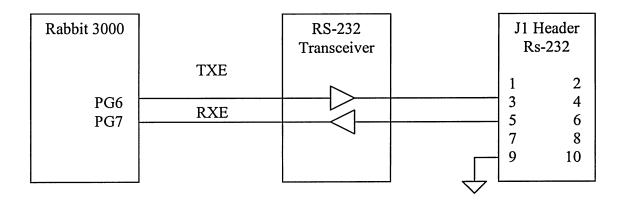

| Figure 3.3. RS-232 Interface                                             | 43 |

| Figure 3.4. RJ-45 Ethernet Port Pinout                                   | 44 |

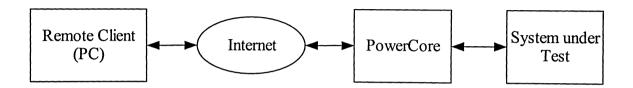

| Figure 4.1. Testing Scheme                                               | 56 |

| Figure 4.2. Experimental Setup for the prototype of e-Maintenance system | 57 |

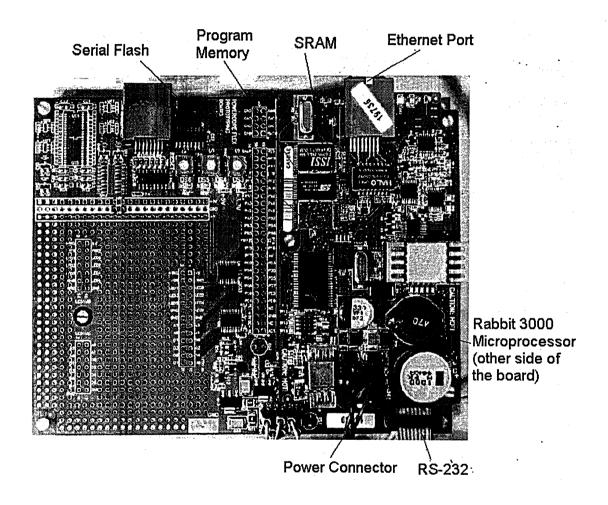

| Figure 4.3. Photographic image of the e-Maintenance system                   | 58 |

|------------------------------------------------------------------------------|----|

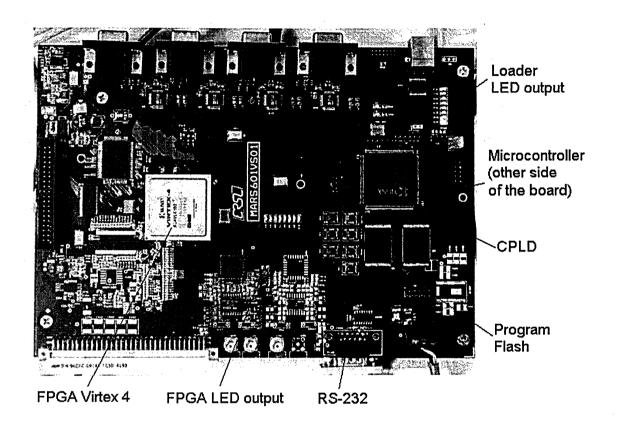

| Figure 4.4. Detailed photographic image of MARS FPGA platform                | 59 |

| Figure 4.5. Network Setting                                                  | 60 |

| Figure 4.6. Local Area Connection Properties                                 | 61 |

| Figure 4.7. Setting Internet Protocol Properties                             | 61 |

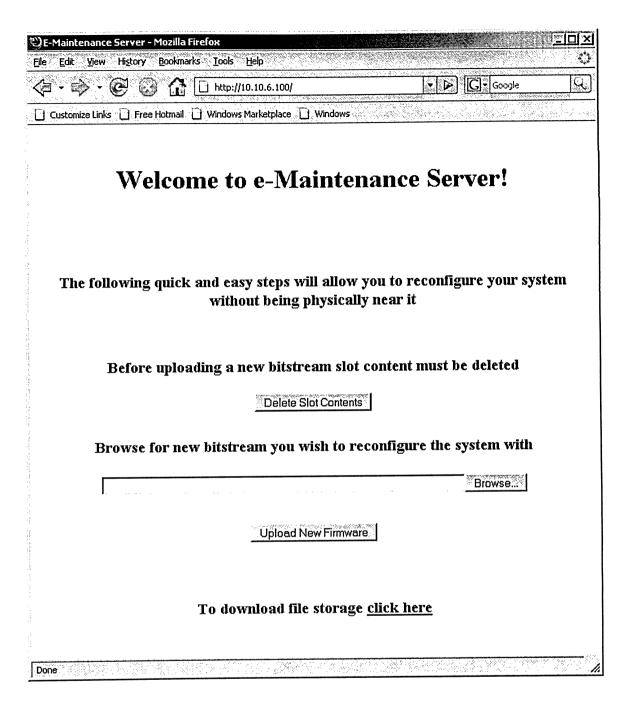

| Figure 4.8. Home Page of e-Maintenance Server                                | 63 |

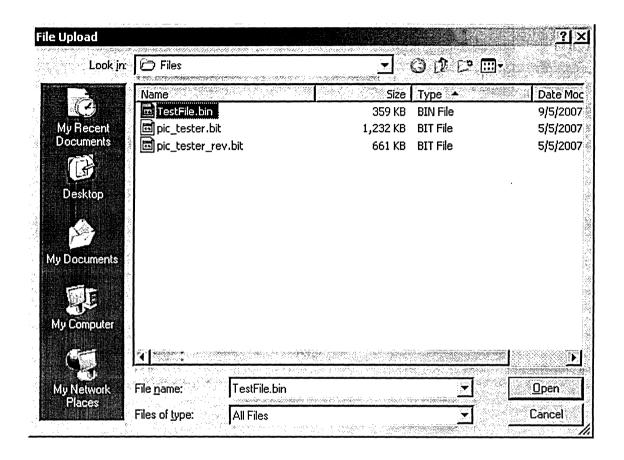

| Figure 4.9. File Browse Dialog from HTTP Server                              | 64 |

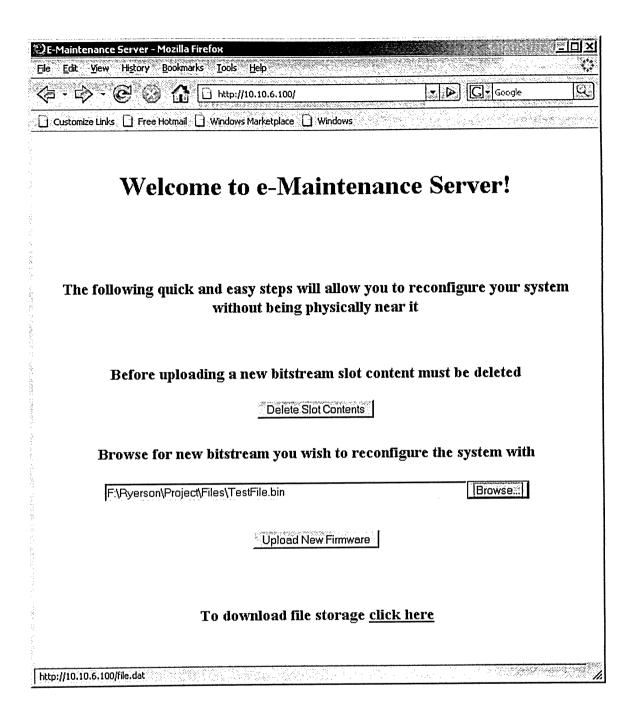

| Figure 4.10. Selected test file                                              | 65 |

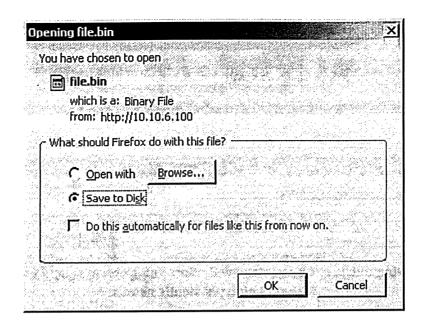

| Figure 4.11. File Download Dialog                                            | 66 |

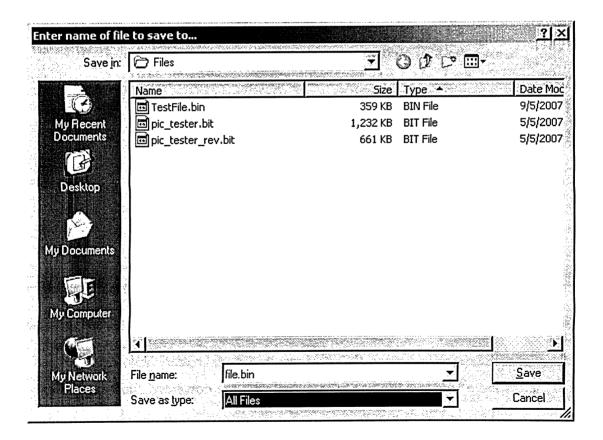

| Figure 4.12. Saving File Dialog                                              | 66 |

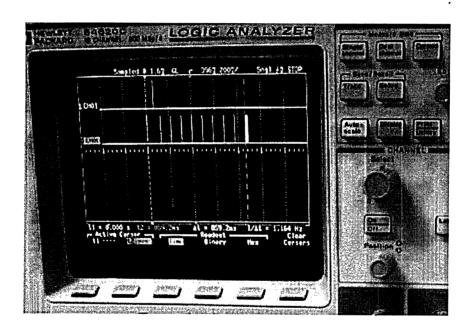

| Figure 4.13. HP54620C logic analyzer used as a measuring tool for the system | 68 |

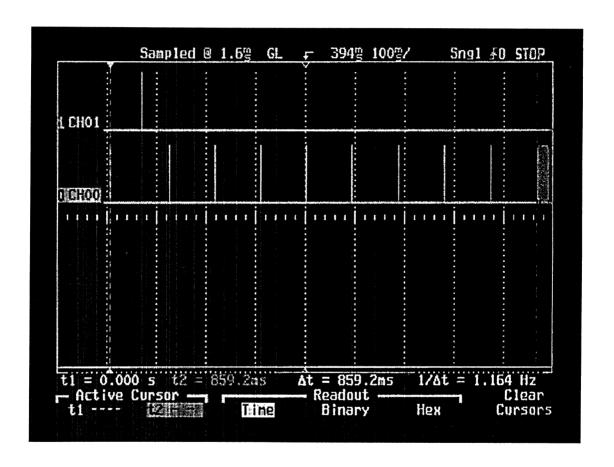

| Figure 4.14. Baud Rate Test                                                  | 69 |

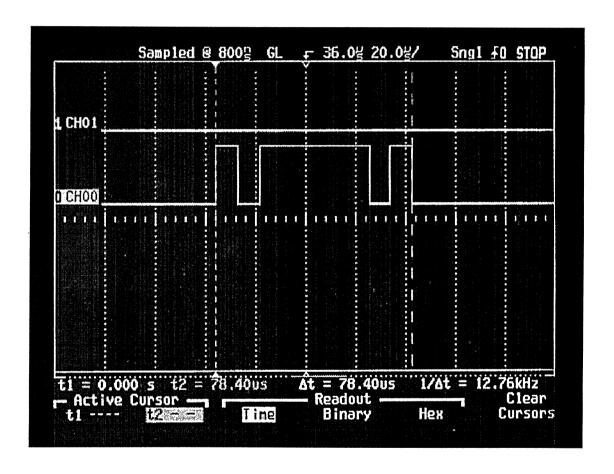

| Figure 4.15. FPGA platform response time                                     | 70 |

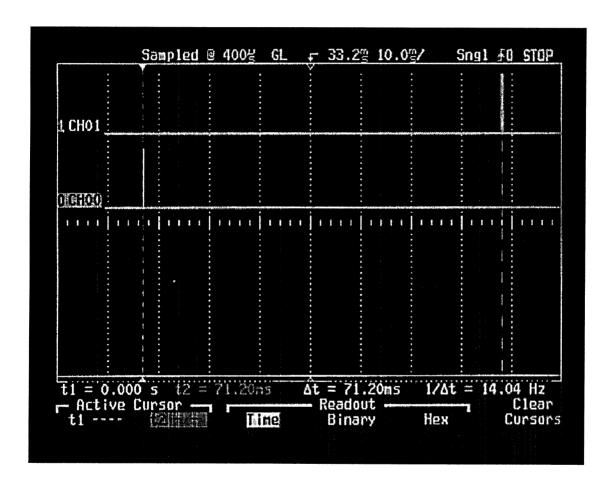

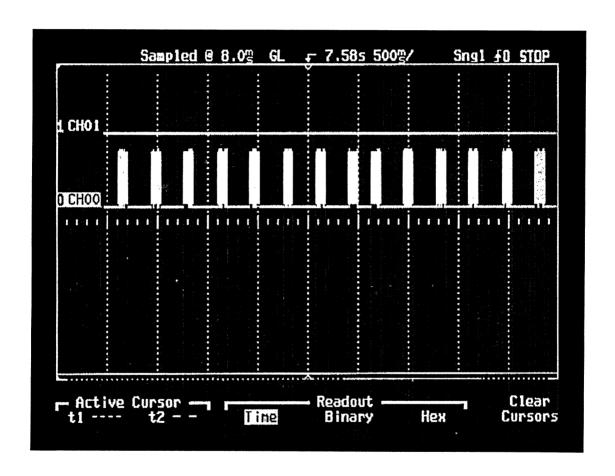

| Figure 4.16. File Transmission Initialization Time                           | 71 |

| Figure 4.17. Transmitted Bitstream Packets                                   | 72 |

## List of Tables

| Table 3.1. Serial Port Signals                                                |    |  |

|-------------------------------------------------------------------------------|----|--|

| Table 4.1. Estimated remote reconfiguration time for Virtex-4 family of FPGAs | 74 |  |

#### **Chapter One**

#### Introduction

#### 1.1 Motivation

Maintenance of a system is the next important task after manufacturing and production. Since system reliability is crucial for any sold product and customer satisfaction is of a greatest value in the modern commercial world, the system maintenance must be effective and inexpensive. In large complex systems reliability is difficult to achieve since many boards and sub-blocks are involved in system design and integration and therefore probability of malfunctioning and faults is high. When system malfunctioning is detected in the field, the work to repair the system can be simplified if some information about malfunctioning is known. Saving data to log files that later on will be viewed by technicians can shed light on the source of the problem. Self check and self diagnostic subsystems are designed and added to complex systems in order to facilitate maintenance process. Latest Internet technologies have enabled remote connectivity to the system which opens huge opportunities for design of remote e-Maintenance systems to perform remote monitoring, remote access to log files and diagnostic. With new possibility to reconfigure FPGA systems by downloading new firmware some remote repair work became possible.

FPGA-based systems carry big advantages over ASIC systems due to possibility to be reconfigured and adapt to different requirements for different applications. Due their small sizes and high density they are vulnerable to external disturbances, which can cause temporary or permanent damage. In case of SEU (Single Event Upset) the damage might be not of a permanent nature and by simply reloading FPGA the problem can be fixed.

Also Internet connection opens possibilities for remote reconfiguration of the system for new applications. As modern FPGA require significantly less time for reconfiguration and posses the ability of partial reconfiguration constant periodic reconfiguration of FPGA for different tasks becomes possible allowing utilization of smaller FPGA for complex systems. These tasks can be programmed remotely and uploaded to FPGA partitions with the help of e-Maintenance system.

#### 1.2 Project Objective

The objective of this project is to conduct research in the area of e-Maintenance, which includes system maintenance and Internet communication. FPGA-based systems study has to be conducted as well.

Next, e-Maintenance for FPGA-based system has to be created. HTTP server is to be implemented in order to provide remote connectivity to FPGA platform to allow observing its performance and diagnostic, fixing malfunctions by reloading firmware and upgrading the system by sending a new bitstream over the Internet and reconfiguring FPGA dynamically.

Finally the role of e-Maintenance in periodic partial reconfiguration of FPGA systems based on temporal partitioning for different applications is to be evaluated.

#### 1.3 Project Organization

The project is organized in five chapters. First chapter opens with a brief introduction of the project, stating its objective and organization.

Second chapter follows with theoretical overview of system maintenance in general and e-Maintenance in particular including overview of Internet and its main protocols. FPGA-based system is introduced followed by temporal partitioning and partial reconfiguration.

The role of e-Maintenance for FPGA programming and reconfiguration is discussed.

Development of Embedded e-Maintenance for FPGA-based Reconfigurable System is presented in chapter three. Requirements of the system are determined, system architecture is presented and detailed implementation is described.

Chapter four holds experimental results. HTTP server functionality is tested, communication with FPGA platform is established, reconfiguration of FPGA-based system is fulfilled and observation of different FPGA reconfigurations is presented.

Finally, conclusions are drawn in chapter five. Future work and possible further research is discussed.

#### **Chapter Two**

#### Theory overview

#### 2.1 Introduction

In this chapter theoretical overview is presented. It is divided into three major parts:

- system maintenance which talks about system diagnosis and testing process

- e-Maintenance and Internet communication

- FPGA-based system

#### 2.2 System Maintenance

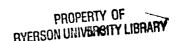

Every system goes through several stages within its lifetime as illustrated in Figure 2.1. In the first stage the requirements of the system need to be determined according to customer's needs.

Based on the requirements specification is prepared. Specification includes functional characterics such as specifying inputs and outputs of the system, operating characteristics such as power and frequency, environmental characteristics such as reliability of the system at a certain temperature range, and so on.

In the next stage all the necessary data for the manufacturing stage is prepared. Highlevel decisions are made about the overall structure of the system, its architecture, and the strategies used to implement the system. The system is divided into functional blocks and afterwards each block is being designed to details. After the design is complete, the first stage of testing is conducted. It is meant to compare the actual system performance to the required one and in this way to discover the defects of the system, which could be caused by equipment malfunctions, defects in materials and human errors [2].

Figure 2.1. System realization process.

In the manufacturing stage mechanical transformation of materials into new products in large quantities is conducted, assembling component parts into new products. After that new products are tested again to verify they are working correctly.

Now the product is ready to be shipped to the customer. Ideally, its performance should be 100% correct for as long as the customer needs to use the product. Unfortunately, the reality is different. At a certain point some defects may appear in the system due to

improper handling, environment conditions, aging of the system, or initial defects that were not discovered at the testing stage. Here the maintenance stage comes in, when the supplier must check the system, find the source of the problem and replace the necessary component. If the customer needs to add new features to the existing system, the supplier upgrades it at the maintenance stage as well.

#### 2.2.1 Testing Process

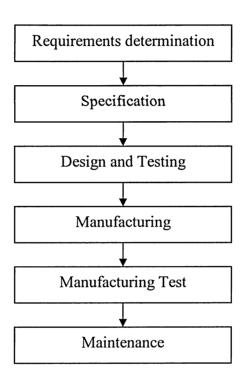

The role of testing is to detect whether there is a defect in the system and if possible to locate it. Basic principal of testing is illustrated in Figure 2.2.

Figure 2.2. Principal of testing.

A test performed on a system may be functional in which case the correct function of the system needs to be verified [2]. A complete functional test will check each entry in the truth table. In case of a large circuit with many inputs such test will take extremly long time to finish. Therefore in most cases only a certain amount of test patterns is applied. Another way to make a large system test less complicated is to divide the system into smaller functional blocks and run an individual test on each of those blocks.

Another type of testing is called structural test. This type of testing depends on the specific structure of the circuit such as gate types, interconnects, etc. These tests enable

developing algorithms with the help of fault models. A fault is representation of a defect at function level.

#### Several levels of fault models are possible:

- Behaivioral level at this level, which is often called high level, the behaivior of an electronic system is described in computer-readable form and is written in a programming or a hardware description language. The variables and operations correspond to specific application domain and the behaivioral faults refer to incorrect execution of the language constructs. Examples of such faults are branch fault, which affects a branch statement and causes it to branch to an incorrect destination and instruction fault, which causes an instruction to be incorrectly executed. Functional fault models of semiconductor memories are also a part of behaivioral faults, since their function is very simple and exhausive functional test is normally used.

- Register-transfer level (RTL) or sometimes called logic level, which uses a

netlist of gates. Stack-at faults are the most common fault models for this level.

Stack-at fault is modeled by assigning a fixed value to a signal line in the circuit.

Also common to this level are bridging fault, which represents a short between a

group of signals and delay faults.

- Transistor level often reffered as component level includes stack-open types of faults, which are modeled as the switch being permanently in open or shorted state, considering a MOS transistor as an ideal switch.

With the use of these fault models an algorithm for testing the system can be created.

Thus the system can be tested on different levels, from the highest to the lowest.

#### 2.2.2 Maintenance

Maintenance is necessary whenever the system is malfunctioning. During maintenance process the system is tested to determine which part of the system stopped functioning, after which the faulty component is replaced.

Malfunctioning of the system can occur due to various reasons. With the help of latest technologies semiconductor devices operate on a lower power voltages, have smaller sizes and high density. However, these qualities make the system more volnerable to external and internal disturbances such as electromagnetic interference, cosmic radiation and power supply fluctuations [3]. All these disturbances can cause defects in the system.

Defects can be of permanent and temporary nature:

- Hard faults caused by hardware defect in the circuit and considered to be faults

of a permanent nature. Such faults will produce steady system malfunction.

Examples of these faults are stack-at faults and stuck-open faults.

- Soft Faults faults of no permanent nature. These faults happen as a result of

external interferences and are called Single Event Upset (SEU). These faults

happen occasionally even in case of no electromagnetic interference present and

power supply lines being steady, cosmic radiation can still cause SEU.

#### 2.2.3 Diagnosis

Whenever any disturbance occurs, causing the system to stop functioning properly a diagnosis must be performed. Diagnosis is a way to determine exactly what part of the system is corrupted and how to solve the problem with minimum effort and cost. Testing is a very important part of diagnosis.

Even for a relatively small system, consisting of several components, testing can be a tedious process. Running an exhaustive test on a whole system and checking for all possible faults will take an infinite amount of time. In order to perform diagnosis effectively, the system must be divided into blocks and each block must undergo its own separate test. Based on the results of those tests a decision can be made as to which component in the system is faulty.

Diagnosis of a system can be performed on a structural and on a functional levels [4]. On a structural level the division of the system into blocks is performed based on the system structure that is a certain amount of printed circuit boards, chips, wiring etc. The system is divided into blocks according to its components and each of them is tested separately. After the testing is finished the faulty component should be found.

When the diagnosis is performed on a functional level, the testing is based on system functionality. Each system has to perform certain functionality and it can be viewed as a combination of several functional modules. Once the division of the system into these modules is defined, a separate functional test can be performed on each of those modules, thus revealing the faulty one. Functional module corresponds to an actual structural component (or several components), which needs to be substituted. Functional and

structural levels may overlap which can create flexibility in a test design. This may allow choosing the type of testing which is easier to perform.

In certain cases diagnosis of communication is necessary. In a complex system where several components are constantly communicating with each other, system malfunctions might be caused by communication faults. One of the tasks of system diagnosis is to detect faults in communication. This can be accomplished with the help of communication protocols, when the transmitting end can send special control messages and the receiver must send appropriate acknowledgments. When the acknowledgement is not received the source of the problem can be in faulty communication or defected component. Communication between components can be improved by adding checksum bytes to transmitted data. These bytes are analyzed by the receiver to verify the integrity of data and if necessary the receiver can send a request to transmit the same data again. Many different encoding techniques are used for verifying data integrity, among which Cyclic Redundancy Check (CRC) is the most popular.

In reloadable systems, which require initialization stage malfunctioning can be caused by faulty elements responsible for uploading the data/software. Usually these elements are memory devices such as FLASH, SRAM, EPROM, etc. A common way to verify correct functionality of such devices is to upload a small amount of data, read it back and compare it with the original. If this test repeatedly results in an error a conclusion can be drawn that the memory device is indeed faulty. With this procedure this single component failure might be verified prior to system initialization stage.

#### 2.2.4 Built In Self Test (BIST)

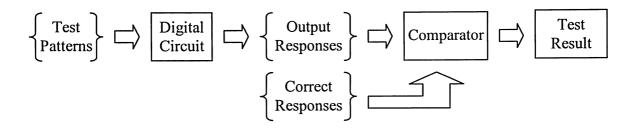

As technology evolves integrated circuits become more and more complex. Since it is almost impossible to trace and probe internal signals in these circuits it is very difficult to test them thoroughly and quickly. For such systems design-for-test (DFT) techniques are a good solution for improving system testability such as Build In Self Test (BIST) [4]. BIST is very useful for maintenance and diagnosis, since it reduces test generation effort at all levels. This test is specified as one of the system functions. At the highest level of system test, this test is usually implemented in software. Software approach provides flexibility, but on the other hand it can be slow and expensive to develop. Therefore for some systems it is preferable to implement self-testing in the hardware.

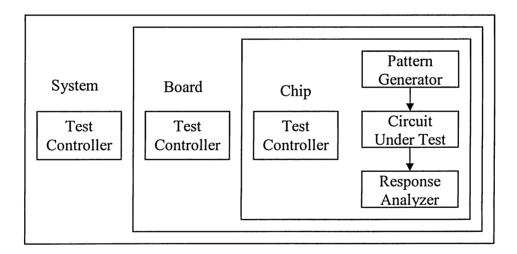

Figure 2.3. BIST hierarchy.

BIST system hierarchy is shown in Figure 2.3. System test controller can activate the test on all PCBs. Each PCB has its own test controller, which in turn activates self-tests on all chips on the board. Likewise each chip test controller activates self-test of the chip itself. After the tests are finished, the results are transmitted to the main test controller: all chips

test controllers transmit the results to board test controller, which collects them and sends them further to test controller of the system. Upon receiving all the results, system test controller is able to detect faulty chips and boards and isolate them.

#### 2.2.5 System Monitoring

Real-time continuous monitoring is now generally considered to be a part of the mechanism for improving system reliability [5]. It can significantly reduce the time spent on testing the system, since just by observing the event log system specialist can understand which part of the system is malfunctioning [6]. Also, some malfunctions will only take place under specific conditions, which might not be reproduced in regular off-line testing environment. In order to provide a proper event log, a monitor must systematically observe execution behavior of the system. Its activity must not disturb system functions and it must keep up with target execution by imposing real-time constraints on its internal processing [7]. Such systems are important in general applications that are subject to time-dependent process interaction anomalies.

#### 2.3 E-Maintenance

Effective diagnostics and maintenance are very important factors in system cost, because during the process of diagnostics and repair the system is not functioning. In many cases when a problem occurs to the system, the supplier will send service engineers to customer's site to perform diagnostics, testing, and replacement of faulty components in the system. Sometimes, the service engineer cannot resolve the problem solely and needs to bring the symptom back to the supplier's diagnostics center and uses the information system to inquire the solution information or purchase the required maintenance components. Thus the diagnosis and repair of failed system usually cannot be performed immediately and therefore the downtime of the system can be long and can cause a significant production loss.

With the development of Internet technologies remote connectivity to the system becomes available. This opens huge opportunities for design of remote e-Maintenance systems to perform remote monitoring, remote access to log files and diagnostic, which can significantly reduce the downtime of the system [8].

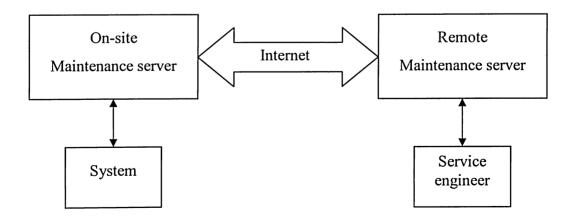

Figure 2.4. E-maintenance system.

Figure 2.4 presents the concept of e-maintenance system. The system preferably containing a self-testing mechanizm and an embedded monitoring device for effective diagnosis is connected by a local network to on-site maintenance server. This server receives log files and self diagnostic results from the system and keeps them in its database, so that they are available for service engineers. Connected to a local host service engineer can access these log files and diagnosis results by connecting to on-site maintenance server through internet. He can view current status of the system, provide diagnostics or even upgrade the system with new firmware without being close to the system physically.

#### 2.3.1 Internet Communication

The Internet is a global system of computer networks. Each computer is independent – a host, and it can get information from any other computer. Internet provides services such as file transfer, email and the World Wide Web. It uses a set of protocols called TCP/IP (for Transmission Control Protocol/Internet Protocol).

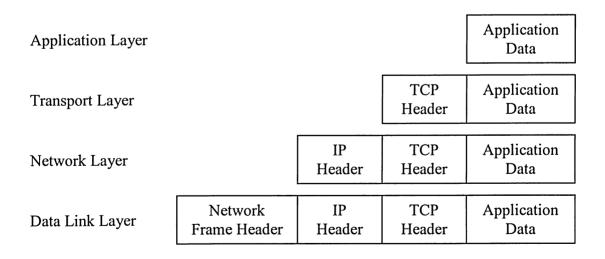

Internet communications can be presented with the help of four layers, as illustrated in Figure 2.5.

| Application layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | HTTP, FTP, Other Applications                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| Transport layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TCP or UDP                                     |

| The second confidence of the second confidence |                                                |

| Network layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IP                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |

| Data Link layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ethernet, Token Ring, Other Network interfaces |

| dates in company to the horse of the Annie Company in the Company  |                                                |

Figure 2.5. TCP/IP Reference Model.

Communications functions are divided into responsibilities of each specific layer [9].

These layers are:

- Application Layer this layer is a client/server communication. Data is sent as commands from the user.

- Transport Layer is responsible for sending the data, determining whether it has been lost and needs to be resend. Sometimes error check is performed at this level.

- Network Layer this layer manages the logical connection between two nodes of the network.

- Data Link Layer at this layer data is transmitted across single network.

The data flow within TCP/IP network is presented in Figure 2.6. Each network layer adds a header to the data, so that the next layer can handle it properly.

Figure 2.6. Data Flow and Header Utilization within TCP/IP network.

#### 2.3.1.1 World Wide Web

The World Wide Web is a hypertext-based, distributed information system, which provides its users with a graphical interface to access data stored anywhere in the world. Hypertext is a method of creating online documents [9]. Documents written as hypertext contain links to other documents or other resources. Hypertext provides visual indications for these links, such as changing the shape of a mouse pointer when it is placed on a section of a document that points to another resource or highlighting that link. Web documents are created using Hypertext Markup Language (HTML).

A Web server is a program that serves the files from Web pages to Web users on client machines. Web client connects to Web server and sends a request for service. Web servers are used for serving e-mail, downloading requests for File Transfer Protocol (FTP) files, and building and publishing Web pages. Therefore web servers are required to be compatible with application level protocols and TCP/IP protocol (or UDP). Considerations in choosing a Web server depend on requirements of the system and may include how well it works with the operating system and other servers, its ability to handle server-side programming, security characteristics, and publishing, search engine, and site building tools that may come with it.

#### 2.3.1.2 Hypertext Transfer Protocol (HTTP)

Requesting and moving web documents from a server to a client is defined by Hypertext Transfer Protocol (HTTP) [10]. HTTP is a request/response protocol: if the client needs to receive service from the server it must send a request first. HTTP request includes a request method to note what the client needs from the server, what resource the client

wants to manipulate through the Uniform Resource Identifier (URI) and a protocol version. A server response also includes the protocol version, followed by a success or an error code. The response also contains server information and web information.

The first HTTP version was HTTP/0.9. This was a very simple protocol for transferring text files only. The next version HTTP/1.0 was a more complicated protocol allowing transfer of many types of files and resources. However this protocol is based on a perception that every time the resource is requested, a new connection must be established. Since web pages became more complex containing several text and graphic files, a new version was developed: HTTP/1.1. This version allows keeping one connection open to send and receive more than one request/ response pair.

Several request methods are used in HTTP/1.1 such as:

- GET clients use this method to request web content.

- PUT used by clients to submit material to a specific web URI.

- POST used by clients to add material to an existing URI.

- OPTIONS a request for information about available communication options, so

that a client can determine the options and requirements of the resource or the

capabilities of the server.

- HEAD used for testing hypertext links for accessibility and recent modification.

- DELETE this method requests that the origin server deletes the resource identified by the Request-URI.

- TRACE clients use this method to see what is being received at the other end of the request chain in order to use that data for testing or diagnostic information.

#### 2.3.1.3 File Transfer Protocols

File Transfer Protocols allow the user to access files on remote hosts, send and receive files through Internet [9]. There are two main protocols of such kind: File Transfer Protocol (FTP) and Trivial File Transfer Protocol (TFTP).

With the help of File Transfer Protocol the user can operate on remote resources as if they were on his local computer. The user can view the directories, open files, copy them and move them. FTP is a full-featured protocol, it offers a vast variety of operations between two hosts. Hosts can exchange files regardless of their operating systems or file structure. FTP can handle any type of file and is very reliable. FTP uses two different TCP channels. The first channel is for transferring data such as directory information and transferred files. The second channel is for control purposes, through this channel commands from the client to the server and backwards are sent.

TFTP is a simplified version of FTP. It is useful for hosts with limited memory, limited file download requirement and less need for reliability. It cannot list directory content of another host, its main purpose is to read files from and write files to a remote server. TFTP uses UDP and therefore files are transferred through independent exchange of packets. The client sends an RRQ (read request) or WRQ (write request) packet to the server, containing the filename and transfer mode. The server replies with an ACK (acknowledgement) packet and sends the first part of the file. The client sends an acknowledgement upon receiving the packet, and the server sends the next part. This process continues until the whole file is sent. TFTP protocol is very simple, it has only five types of messages: Read request, Write Request, Data to be read or written, Acknowledgement and Error.

#### 2.3.1.4 Transport Layer Protocols

Transport layer provides interface between a network layer below and an application layer above. There are two primary transport layer protocols: Transmission Control Protocol (TCP) and User Datagram Protocol (UDP) [9].

TCP is a connection-oriented protocol, which means that the data can be transmitted from one host to another only after both hosts have initiated a connection. This requires a handshaking process called three-way handshake to be completed before establishing the connection. One end is sending a request to the other host to open a TCP circuit. The client-side of a connection sends an initial SYN segment to the server to show that the synchronization process is taking place. Upon receiving the acknowledgment the server-side should respond to a valid SYN request with a SYN/ACK. Finally, the client-side should respond to the server with an ACK, completing the 3-way handshake and connection establishment phase.

TCP connection is duplex, meaning hosts can send data at the same time and it will travel in parallel. Also TCP is a reliable delivery protocol – it guarantees delivery of data between two hosts. Both hosts must acknowledge of all data received from the other host. In case of missing data it will be retransmitted.

TCP Header Structure is shown in Figure 2.7.

| Source Port Number          |          | nber      | Destination Port Number |

|-----------------------------|----------|-----------|-------------------------|

| Sequence Number             |          |           |                         |

| Acknowledgment Number       |          |           |                         |

| Header<br>Length            | Reserved | TCP Flags | Window size             |

| TCP Checksum Urgent Pointer |          |           | Urgent Pointer          |

| TCP Options                 |          |           |                         |

| Data                        |          |           |                         |

Figure 2.7. The TCP header.

- The first two fields are source and destination port numbers. They are used by the receiver and the transmitter respectively to identify each other.

- Since data is divided into packets rather than sending the whole chunk at once, sequencing is necessary. Sequence number ensures that packets will not be misordered and missing packets will be noted.

- Header length field is usually 4 bits in length, but since inclusion of options can result in variable-length header, the presence of this field is necessary.

- TCP flag bits are used to negotiate and manage the connection.

- Window field indicates the maximum number of bytes for the receiver to expect.

- Checksum field provides error detection capability.

- Urgent pointer field is used when the URG flag in TCP flags field is set indicating that current TCP segment is urgent.

TCP options field enables the support of various options such as Maximum Segment Size.

Unlike TCP, UDP is a connectionless protocol, which means that an application using UDP can have its data transmitted without establishing a connection with the receiver first. This simplifies the communication process. UDP does not provide the reliability and ordering guarantees that TCP does; messages (called datagrams) may arrive out of order or go missing without notice. However, as a result, UDP is faster and more efficient for many lightweight or time-sensitive purposes for which using TCP would result in a high level of overhead. Also UDP header is simplified and is much smaller than that of TCP. It is presented in Figure 2.8.

| Source Port Number  | Destination Port Number |

|---------------------|-------------------------|

| UDP Datagram Length | UDP Checksum            |

| Data                |                         |

Figure 2.8. The UDP header.

- Source and destination port numbers are used by the receiver and the transmitter respectively to identify each other.

- Length field indicates the length of UDP datagram.

- Checksum field is used when checksum is required by the application.

#### 2.3.2 E-Maintenance of Reconfigurable Systems

Previous generation of E-maintenance systems dealt with embedded microprocessors based systems. It was possible to conduct remote monitoring and diagnosis for them, thus internet was merely servicing information exchange such as log files or testing results.

Today, as FPGA's become more and more popular and many systems are based on them,

E-Maintenance can have a new important task – remote repair of the system through dynamic reconfiguration of processor structure. Thus without substituting the hardware remote reconfiguration of the system for repair as well as for new applications is becoming possible.

### 2.4 FPGA-based System

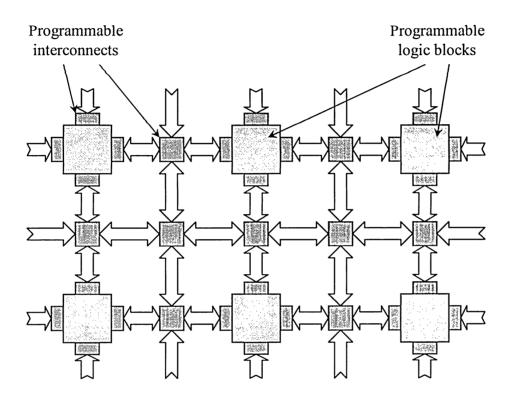

FPGA stands for Field Programmable Gate Array. It is a digital integrated circuit that contains programmable logic blocks and configurable interconnects between them [11]. Figure 2.9 illustrates generics FPGA logic and routing resources.

Figure 2.9. Generic FPGA logic and routing resources.

Based on their implementation FPGAs can be reconfigured multiple number of times, while other type of FPGAs can be programmed only a single time.

Today FPGAs are used to implement a variety of products such as communications devices, digital signal processing applications and embedded microcontroller applications. FPGAs are being used to implement designs that previously have been implemented using application-specific integrated circuits (ASICs). Although the cost of

ASIC in massive productions is lower than that of FPGA, implementing design changes is much faster in FPGA as well as the time to market of FPGA design is faster. These qualities make FPGA very popular, especially for small innovative design companies.

#### 2.4.1 FPGA Architecture

The main feature of FPGA is its ability to be reconfigured many times. In this section the mechanism that allows reprogramming FPGAs is explained as well as some architectural features.

#### 2.4.1.1 LUT-based logic blocks

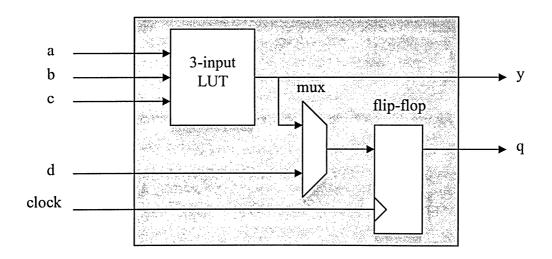

Lookup table (LUT) based blocks consist of a multiple input lookup table, a register that can act as a flip-flop or a latch and a multiplexer, as shown in Figure 2.10.

Figure 2.10. A simplified view of programmable logic block.

Each one of those blocks can be configured to perform a different function [11]. For example, if LUT is required to perform the function y = (a OR b) AND (NOT c). The

LUT needs to be loaded with values as shown in Figure 2.11. 8-1 Mux represents a cascade of transmission gates for selecting the desired SRAM cell.

Figure 2.11. LUT configuration.

Different number of inputs has been researched in the past. Today all successful architectures use 4-input LUTs.

### 2.4.1.2 SRAM-based Technology

The majority of FPGAs are based on the use SRAM configuration cells [11]. Static RAM is employed because the values in the cells don't need to be refreshed as in dynamic RAM. They remain unchanged unless altered by designer or until the power is removed from the system. SRAM cell consists of multitransistor SRAM storage elements. Output of each element drives an additional control transistor. Based on element's content (0 or 1) this control transistor will either be OFF or ON.

SRAM-based FPGA has to be reprogrammed every time the system is powered on, which requires the use of an external memory devise. Since each cell consists of several transistors, it consumes a lot of silicon. However, SRAM-based technology's big advantage is that these cells can be reprogrammed quickly and repeatedly.

#### 2.4.1.3 Embedded RAMs

Since many applications require the use of memory, latest FPGAs include embedded RAM called block RAM [11]. These blocks can be positioned around the periphery of the devise or organized in columns, as shown in Figure 2.12.

Figure 2.12. Simplified view of chip with embedded RAM blocks.

Each block of RAM can be used independently or if a larger chunk of memory is needed, several blocks can be combined to be used as one. They can be used to implement different functions such as FIFO, state machines and so on.

#### 2.4.1.4 Embedded processor cores

Most of electronic designs are implemented using microprocessors. Until recently microprocessors have been included in the design as a separate device. Lately they became available as part of high-end FPGAs [11]. These microprocessors are referred as embedded cores. Using such FPGA saves the cost of having two separate devices, as well as makes the design simpler, since there is no need in connecting those devices on board. Microprocessor core can be implemented in FPGA in two ways: as hard core and soft core.

A hard microprocessor core is a predefined block in FPGA, positioned at a certain place in the chip. This place can be on the side of the main FPGA fabric called "strip", as shown in Figure 2.13. Additional functions can be added with microprocessor core such as memory, peripherals, etc. More than one microprocessor can be embedded into the chip.

Another option is for embedded core to be placed directly into the main FPGA fabric. In this case the memory necessary for the core is formed from embedded RAM blocks, and various peripherals are formed from programmable logic blocks. The advantage of this position is speed gain due to proximity of microprocessor core to the main FPGA fabric.

Figure 2.13. Chip with embedded core outside of the main fabric.

Soft cores are programmed into FPGA by configuring a group of programmable blocks to act as a microprocessor. Such core can be provided in a form of RTL netlist that will be synthesized with the other logic or as a placed and routed block of LUTs. All additional devices like memory controllers, interrupt controllers and so on are implemented in the same way as microprocessor core.

These cores are simpler and up to 50% slower than hard cores. However they give the designer the flexibility to include the core according to his needs as well as any peripheral device. Also several cores can be implemented as long as there are enough programmable blocks in FPGA.

### 2.4.2 Diagnosis of FPGA-based system

SRAM-based technology is very sensible to Single Event Upsets (SEU). Such events may be originated by high energy particles hitting the silicon substrate, and thus changing the logical state of the memory elements [12]. SEUs may alter the memory elements in the design such as the content of a register in the data-path, or the content of the state register of a control-unit. Another aspect of SEU effects is possible change in the content of the memory storing the device configuration information, such as the content of a Look-Up Table (LUT) inside a Configurable Logic Block (CLB) or the routing of a signal in a CLB or between two CLBs. Therefore SEU by changing one bit can cause malfunctioning of the whole device.

One way to avoid this problem is to use radiation hardened FPGA devices [13]. However, these devices are much more expensive. Another possible solution is to use FPGAs based on antifuse technology, but they have a major drawback – they cannot be reprogrammable.

Therefore periodic testing of FPGA is necessary. It will detect the effect of SEU and by reprogramming FPGA the defect can be fixed. FPGA-based systems which are designed to work in outer space are equipped with a special reloading system. This system allows to reprogram FPGA frequently while FPGA is in working mode. Such systems are very expensive, but necessary in space conditions with very high ratio of SEU.

It is also important to test FPGA regularly because some manufacturing defects in the reconfigurable hardware may result in faulty behavior only for spesific configurations.

The malfunctioning FPGA component may actually pass manufacturing test and work

properly for a number of different configurations, but one particular configuration might cause it to fail [14].

E-maintenance opens new possibilities for repair of FPGA-based systems, since whenever FPGA needs to be reconfigured, new firmware can be sent to the system remotely via internet.

### 2.4.3 Partial reconfiguration of FPGA

Not only can FPGA be reprogrammed with new logic whenever it is necessary, but it can also be reprogrammed partially [15]. A certain predefined subset of FPGA can be reconfigured, while the rest of the device continues operating. The process of partial reconfiguration is based on dividing FPGA into blocks according to their functionality and reloading each block with it's own bit stream. Thus in order to reconfigure a part of FPGA, it is not required for the whole system to stop operating. This feature comes very handy for systems that deal with mission-critical tasks that cannot be interrupted.

# 2.4.3.1 Run-Time Temporal Partitioning of FPGA Resources

Today digital signal processing systems need to process streamed data at very high speed. Traditionally embedded microprocessors were the basis for designing such systems. However, the performance of such systems is limited due to sequential process of instructions execution in microprocessors. Furthermore, microprocessors require many additional clock cycles for each instruction: instruction fetch, instruction decode, data fetch, store result. Thus completion of a certain set of operations will take longer time than just data processing itself.

For example, suppose the following set of operations is to be implemented:

$$Z_i = A_i + B_i \times C_i$$

, for  $i = 1, 2, ..., 100$

For each value of vector elements 7 instructions have to be executed: load B, load C, multiply B and C, load A, add A to the result of previous operation, increment i, compare i to 100. Even if we assume that the number of clock cycles for each operation is 1, the whole task will take 7 clock cycles \* 100 = 700 clock cycles.

But if this function is to be implemented in a specially designed circuit presented in Figure 2.14 it will take far less time to execute: Total time = Latency + Output rate \* 1 clock cycle = 2 clock cycles + 100 \* 1 clock cycle = 102 clock cycles. That is 7 times faster. In reality multiplication and adding take much more time than 1 processor clock cycle, therefore custom designed circuits operate even faster than shown in this example.

Figure 2.14. Stream processing circuit for  $Z_i = A_i + B_i \times C_i$

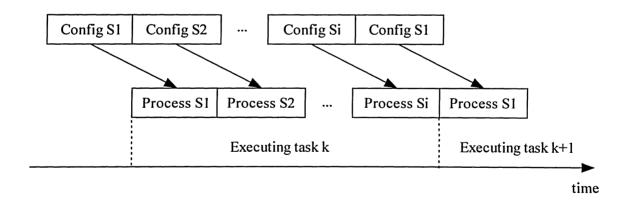

Growing demand for high-speed data processing resulted in moving away from microprocessors to implementing such systems in ASIC or FPGA devices. As was noted previously, ASIC has major drawbacks compared to FPGA, since FPGA has a lower time-to-market and can be reprogrammed. Furthermore, use of partially reconfigurable FPGA devices makes possible achieving high-cost efficiency. This is done by dividing FPGA into segments when each segment is configured with a specific IP-core designed for a certain task. After the task was executed, temporal results are stored in the memory and a new configuration data reloads FPGA for the next portion of operations to be executed. Such approach allows using same resources of FPGA for execution of different tasks during different time periods and as a result minimization of hardware per task. Figure 2.15 illustrates the concept Run-Time Temporal Partitioning when S<sub>1</sub>, S<sub>2</sub>, ..., S<sub>i</sub> are segments.

Figure 2.15. Run-Time Temporal Partitioning.

### 2.4.3.2 Macro-Programming of FPGA-based System

Utilization of FPGAs can be quite complicated. It is expensive and requires a lot of time since many stages are involved: development, circuit design, prototyping and verification. If a complex system is implemented it can result in using a large and therefore extremely expensive FPGA due to complex routing inside the chip. As an outcome a lot of FPGA's logic resources will not be used for the processing itself. Also it will require long compilation cycle. And finally, FPGA prototyping calls for highly qualified developers. Such developers are hardware designers and usually are not experts in the technological process itself.

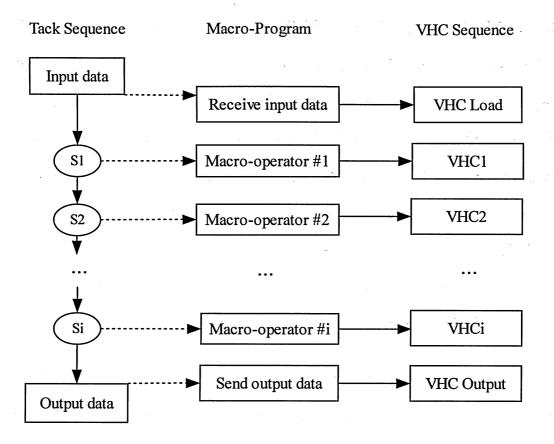

A concept of Macro-Programming presented in [1] investigates the possibility of simplifying task programming without detailed knowledge of FPGA hardware organization. It is based on dividing the stream-processing application into segments S<sub>1</sub>, S<sub>2</sub>, ..., S<sub>i</sub> when each segment is linked to a given stream-processing unit configured in FPGA. Each of those stream-processing units is called virtual hardware component (VHC) and functions like IP-core, it is used for configuration of FPGA for a specific task – macro-operator, it has interface to memory units for temporal data storage and possible Input/Output interface. Assuming a library of VHC-cores can be produced that for every category of applications, such library is to be supplied by vendors of FPGA platform. Each VHC should be optimized for a certain task and associated with a specific macro-operator. A sequence of macro-operators scheduled according to sequence of tasks is called Macro-Program. Figure 2.16 illustrates the concept of using Macro-operators for application programming.

Figure 2.16. Utilization of Macro-Operators.

Such approach allows easier task programming since first of all breaking tasks into segments simplifies the development of the system. Each separate segment is less complicated thus it is easier to design a stream-processing circuit for its fulfillment. Second, macro-operators could be used for execution of different tasks and this way a library of macro-operators can be created. And finally, since the stage of hardware implementation will be finished with the development of stream-processing circuits, task programming itself becomes easy for the programmer. He needs to know how to operate with macro-operators, that is parameterize them correctly and sequence them according to the specific technological process. Eventually, the program will be a schedule of macro-operators, loading appropriate bit-streams into FPGA in specified time periods.

Such program can be loaded to any system containing FPGA-based stream-processing platform. E-maintenance system opens number of possibilities for Macro-programming. The whole Macro-Program can be uploaded remotely. A library of Virtual Hardware Components can be developed remotely and uploaded via Internet as well. If later on this library has to be extended or updated, necessary VHC can be developed remotely and loaded via Internet. It can then be used by the Macro-Program for FPGA reconfiguration for updated task. Thus the system can be upgraded without stopping the execution of its other tasks.

# 2.5 Summary

A theoretical overview of e-Maintenance and FPGA was presented in this chapter. As part of e-Maintenance general system maintenance was described and overview of Internet communication with main Internet protocols was demonstrated. Theoretical background of FPGA was presented as well as latest possibilities for its reconfiguration were studied.

# **Chapter Three**

# **System Development**

### 3.1 Introduction

In this project a prototype of e-Maintenance system for FPGA-based reconfigurable system will be implemented. Requirements for such system, its architecture and implementation are described in this chapter.

# 3.2 Functional Specification

An e-Maintenance system for FPGA-based reconfigurable system must possess the following functionality:

- Provide remote connectivity to supporting personnel via Internet.

- Capable of receiving new firmware via Internet.

- Allow reloading FPGA's firmware.

- Provide monitoring of reconfigurable system and keep log files of system events.

- Provide diagnostic of reconfigurable system.

- Allow viewing log files and reconfigurable system performance via any standard browser.

- Allow downloading log files via Internet.

### 3.3 Basic Requirements of the System

In order to possess all the capabilities listed above this system must fulfill several basic requirements. First of all it must contain an embedded web server to enable remote connectivity, viewing log files of reconfigurable system, downloading them, and sending new firmware if necessary. System maintenance web page presenting system performance, faults and diagnostics must be designed. The system upgrade and downloading log file will be accessed through maintenance web page.

Therefore the requirements of a web server are:

- To have one or two simple web pages.

- Provide uploading/downloading files capability.

- Provide TCP/IP connectivity.

- Provide compatibility with HTTP protocol.

Second, the system must have enough memory to store log files, embedded web server related items such as web pages, controls, etc.

Finally, an embedded microcontroller is necessary to coordinate the whole system. It will monitor reconfigurable system performance, maintain system log file and provide boot loading to the system.

And like general embedded systems this system should be flexible, compact, low power and low cost to be affordable for mass production.

### 3.4 System Architecture

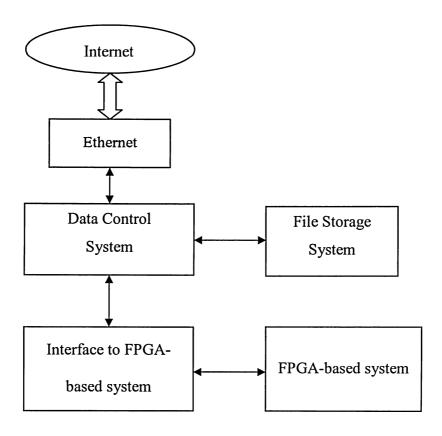

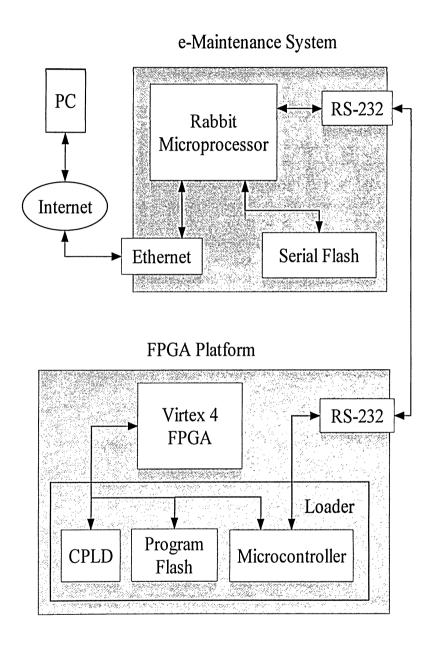

The overall block diagram of the system is presented in Figure 3.1.

Figure 3.1. Overall system block diagram.