## COST MINIMIZATION ALGORITHMS FOR SCHEDULING PARALLEL, SINGLE-THREADED, HETEROGENEOUS, SPEED-SCALABLE PROCESSORS

by

Rashid Khogali B.A.Sc., University of Toronto, 2009

A thesis presented to Ryerson University in partial fulfillment of the requirements for the degree of Master of Applied Science (M.A.Sc.) in the Program of Electrical and Computer Engineering Toronto, Ontario, Canada, 2013

© Copyright 2013 by Rashid Khogali

All Rights Reserved

# **Author's Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public.

Rashid Khogali

#### COST MINIMIZATION ALGORITHMS FOR SCHEDULING PARALLEL, SINGLE-THREADED, HETEROGENEOUS, SPEED-SCALABLE PROCESSORS

Rashid Khogali Master of Applied Science Electrical and Computer Engineering Ryerson University, 2013

## Abstract

We synthesize online scheduling algorithms to optimally assign a set of arriving heterogeneous tasks to heterogeneous speed-scalable processors under the single threaded computing architecture. By using dynamic speed-scaling, where each processor's speed is able to dynamically change within hardware and software processing constraints, the goal of our algorithms is to minimize the total financial cost (in dollars) of response time and energy consumption (TCRTEC) of the tasks. In our work, the processors are heterogeneous in that they may differ in their hardware specifications with respect to maximum processing rate, power function parameters and energy sources. Tasks are heterogeneous in terms of computation volume, memory and minimum processing requirements. We also consider that the unit price of response time for each task is heterogeneous because the user may be willing to pay higher/lower unit prices for certain tasks, thereby increasing/decreasing their optimum processing rates. We model the overhead loading time incurred when a task is loaded by a given processor prior to its execution and assume it to be heterogeneous as well.

Under the single threaded, single buffered computing architecture, we synthesize the SBDPP algorithm and its two other versions. Its first two versions allow the user to specify the unit price of energy and response time for executing each arriving task. The algorithm's second version extends the functionality of the first by allowing the user or the OS of the computing device to further modify a task's unit price of time or energy in order to achieve a linearly controlled operation point that lies somewhere in the *economyperformance mode* continuum of a task's execution. The algorithm's third version operates exclusively on the latter. We briefly extend the algorithm and its versions to consider migration, where an unfinished task is paused and resumed on another processor. The SBDPP algorithm is qualitatively compared against its two other versions. The SBDPP' dispatcher is analytically shown to perform better than the well known Round Robin dispatcher in terms of the TCRTEC performance metric. Through simulations we deduce a relationship between the arrival rate of tasks, number of processors and response time of tasks.

Under the Single threaded, multi-buffered computing architecture we have four contributions that constitute the SMBSPP algorithm. First, we propose a novel task dispatching strategy for assigning the tasks to the processors. Second, we propose a novel preemptive service discipline called Smallest remaining Computation Volume Per unit Price of response Time (SCVPPT) to schedule the tasks on the assigned processor. Third, we propose a dynamic speed-scaling function that explicitly determines the optimum processing rate of each task. Most of the simulations consider both stochastic and deterministic traffic conditions. Our simulation results show that SCVPPT outperforms the two known service disciplines, Shortest Remaining Processing Time (SRPT) and the First Come First Serve (FCFS), in terms of minimizing the TCRTEC performance metric. The results also show that the algorithm's dispatcher drastically outperforms the well known Round Robin dispatcher with cost savings exceeding 100% even when the processors are mildly heterogeneous. Finally, analytical and simulation results show that our speed scaling function in current literature.

Under a fixed budget of energy, we synthesize the SMBAD algorithm which uses the micro-economic laws of Supply and Demand (LSD) to heuristically adjust the unit price of energy in order to extend battery life and execute more than 50% of tasks on a single processor (under the single threaded, multi buffered computing architecture). By extending all our multiprocessor algorithms to factor independent (battery) energy sources that is associated with each processor, we analytically show that load balancing effects are induced on heterogeneous parallel processors. This happens when the unit price of energy is adjusted by the battery level of each processor in accordance with LSD. Furthermore, we show that a variation of this load balancing effect also occurs when the heterogeneous processors use a single battery as long as they operate at unconstrained processing rates.

## Acknowledgements

I graciously thank my supervisor, Dr. Olivia Das for her genuine support, guidance and encouragement. I deeply appreciate her for granting me the opportunity to carry out formal research under her supervision. I am quite fortunate to have been supervised by a wise, easy going and perspicuous supervisor.

I am grateful to Prof. Venetsanopoulos, Prof. Anpalagan, Dr. Raahemifar, Dr. Yifeng and Prof. Gu for effectively exposing me to valuable graduate courses that provided me with sufficient background to carry out novel research projects. I greatly thank the members of my thesis committee: Prof. Anpalagan, Dr. Yang, and Dr. Jaseemuddin for taking time to review my thesis and for providing constructive feedback.

I thank Bruce Darwin for setting up and troubleshooting the laboratory workstations. I appreciate Ryerson University for financially supporting my efforts through awards and various teaching assistantship opportunities. I also acknowledge the Natural Sciences and Engineering Research Council of Canada (NSERC) for financially supporting publications stemming from this thesis.

I dedicate this thesis to my parents who have sacrificed so much for my siblings and I. To my wonderful mother (Mama) who continues to battle a severe case of type II Diabetes, yet she finds the strength to encourage, advice and assist my family in ways that are immeasurable. Mama, my queen, you are the pulse of my heart. To my father (Baba), an honorable man of great insight, work ethic and generosity. The effort invested in this thesis is but a drop compared to their ocean of devotion.

Last but not least, I cherish my magnificent siblings and friends for always being there and making life delightful.

| Contents                                                          | Pg     |

|-------------------------------------------------------------------|--------|

| 1 Introduction                                                    |        |

| 1.1 Motivation                                                    | 1      |

| 1.2 Research Overview                                             | 2      |

| 1.3 Related works                                                 | 4      |

| 1.4 Thesis Contribution                                           | 6      |

| 1.5 Thesis Outline                                                | 10     |

| 2. Background                                                     | 11     |

| 2.1 Introduction                                                  | 11     |

| 2.2 Speed Scaling                                                 | 11     |

| <b>2.3 PDM (Under Static Speed Scaling) For Single Processors</b> | 12     |

| 2.3.1 PDM Problem Scenario                                        | 13     |

| 2.3.2 Competitive Analysis (Relevant to PDM)                      | 14     |

| 2.3.3 PDM for Two States                                          | 14     |

| 2.3.4 PDM for Multiple States                                     | 14     |

| 2.4 Dynamic Speed Scaling (Single Processors)                     | 15     |

| 2.4.1 Competitive Analysis (Relevant to Dynamic Speed Scaling)    | 16     |

| 2.5 Deadline Based Scheduling (Single Processor)                  | 16     |

| 2.5.1 Overview of Yao et al's Framework, Algorithms and Related   |        |

| Extensions for Single Processor Systems.                          | 17     |

| 2.5.2 Deadline Based Scheduling Constrained Speed (Single Process | or) 18 |

| 2.6 Minimizing Temperature (Single Processor)                     | 18     |

| 2.7 Minimizing Flow time (Single Processor)                       | 19     |

| 2.8 Flow Time Plus Energy (FTPE) For Single Processors            | 19     |

| 2.8.1 FTPE - Unweighted                                           | 19     |

| 2.8.2 FTPE - Fractionally Weighed                                 | 21     |

| 2.8.3 FTPE - Weighed                                              | 22     |

| 2.8.4 Multithreading (Processor sharing) Extension                | 22     |

| 2.9 Dynamic Speed scaling Multiprocessor Algorithms                   |    |

|-----------------------------------------------------------------------|----|

| 2.9.1 Deadline Based Scheduling for Multiprocessors                   | 24 |

| 2.9.2 Flow Time Plus Energy (FTPE) For Multi Processors               | 25 |

| 2.9.3 Flow Time Plus Energy (FTPE) For Heterogeneous Multi Processors | 25 |

| 2.10 Limitations of Speed Scaling                                     | 25 |

| 3.The | oretical Framework: Model and Notation                             | 26 |

|-------|--------------------------------------------------------------------|----|

|       | 3.1 A Task                                                         | 27 |

|       | 3.2 A User Profile                                                 | 29 |

|       | 3.3 A Processing Stream                                            | 30 |

|       | 3.3.1 Stream Processor                                             | 31 |

|       | 3.3.2 Memory Queue                                                 | 32 |

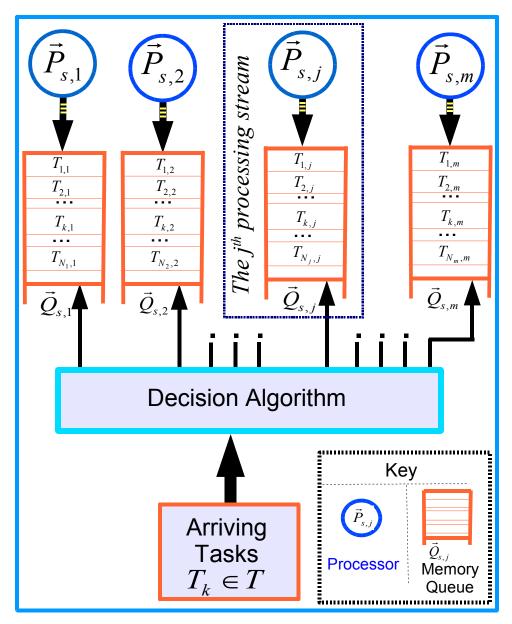

|       | 3.3.3 Parallel Processing Streams                                  | 32 |

|       | 3.4 Mobile Hardware Resources                                      | 32 |

|       | 3.4.1 Mobile Hardware Parameters                                   | 32 |

|       | 3.4.2 Single or Multiple Energy Sources                            | 33 |

|       | 3.5 Task's Processing Rate and Time Consumption                    | 34 |

|       | 3.5.1 Modeling Overhead Access Time                                | 34 |

|       | 3.5.2 Modeling Processing Rate and Execution Time                  | 34 |

|       | 3.6 A Task's Energy & Power Consumption                            | 35 |

|       | 3.7 Description of a Task's Computation Volume upon Execution.     | 36 |

|       | 3.8 The Decision Algorithm                                         | 39 |

|       | 3.8.1 Memory, Processing Rate and Energy Constraints               | 39 |

|       | 3.8.2 The Decision Algorithm                                       | 40 |

|       | 3.9 Performance Metrics                                            | 41 |

|       | 3.9.1 Measuring Response Time in a Sequential Process              | 41 |

|       | 3.9.2 Criticisms of Performance Metrics Used in Current Literature | 42 |

|       | 3.9.3 TCRTEC Performance Metric                                    | 43 |

|      | 3.9.4 Distinguishing our Model from Dynamic Speed Scaling                    |    |

|------|------------------------------------------------------------------------------|----|

|      | Models Found in Current Literature (Major Differences)                       | 43 |

|      | 3.9.5 Mapping Our work in Current Literature                                 | 44 |

|      | 3.10 Defining Traffic conditions                                             | 45 |

|      | 3.11 Conclusions                                                             | 46 |

| 4. C | ost Minimization of Scheduling Single-buffered Processors                    | 47 |

|      | 4.1 Introduction                                                             | 47 |

|      | 4.2 Problem Formulation                                                      | 49 |

|      | 4.2.1 Processing Streams with Single Buffers                                 | 49 |

|      | 4.2.1 A Processing Stream Cost Function                                      | 51 |

|      | 4.2.3 Minimized Cost Function of the j-th processing stream                  | 52 |

|      | 4.2.4 Minimized Constrained Cost Function of the j-th processing stream      | 53 |

|      | 4.3 Single-Buffer Decision & Parallel Processing Algorithm (SBDPP)           | 55 |

|      | 4.4 Calibrating the Ratio of Time and Energy Prices                          | 56 |

|      | 4.4.1 Determining a Task's Mode of Operation                                 | 58 |

|      | 4.4.2 Minimized Constrained Cost Function Using The Power Sensitivity Factor | 60 |

|      | 4.5 Alternative Versions of the SBDPP Algorithm                              | 62 |

|      | 4.5.1 Single Buffer Assisted Decision & Processing Algorithm (SBADPA)        | 62 |

|      | 4.5.2 Fixed Power Decision & Processing Algorithm (FPDPA)                    | 64 |

|      | 4.5.3 Extending the Algorithms to Allow Migration                            | 64 |

|      | 4.6 Analysis                                                                 | 65 |

|      | 4.6.1 Qualitative Comparison of Algorithms                                   | 65 |

|      | 4.6.2 Quantitative Comparison of Algorithm's Dispatcher to Round Robin       | 66 |

|      | 4.6 Simulations                                                              | 68 |

|      | 4.6.1 MATLAB Simulations                                                     | 68 |

|      | 4.6.1 Java Simulations & Insights                                            | 70 |

|      | 4.6 Conclusions                                                              | 70 |

| 5. Cost Minimization of Single-threaded, Multi-buffered Processors                                                                            | 73      |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 5.1 Introduction                                                                                                                              | 73      |

| 5.2 Problem Formulation                                                                                                                       | 75      |

| 5.2.1 Processing Streams with Multiple Buffers                                                                                                | 75      |

| 5.2.2 The Cost Function of the j-th Processing Stream                                                                                         | 76      |

| 5.2.3. The Minimized Cost Function of the j-th Processing Stream                                                                              | 78      |

| 5.2.4. The Minimized Constrained Cost Function of the j-th Processing Stream                                                                  | 81      |

| 5.3 Algorithms Description                                                                                                                    | 82      |

| 5.3.1 SMBSPP Algorithm's Dispatcher (MMCVITPS)                                                                                                | 82      |

| 5.3.2 SMBSPP Algorithm's Service Discipline/Policy (SCVPPT)                                                                                   | 82      |

| 5.3.3 Single-threading Multi-buffer Scheduling & Processing Algorithm                                                                         | 83      |

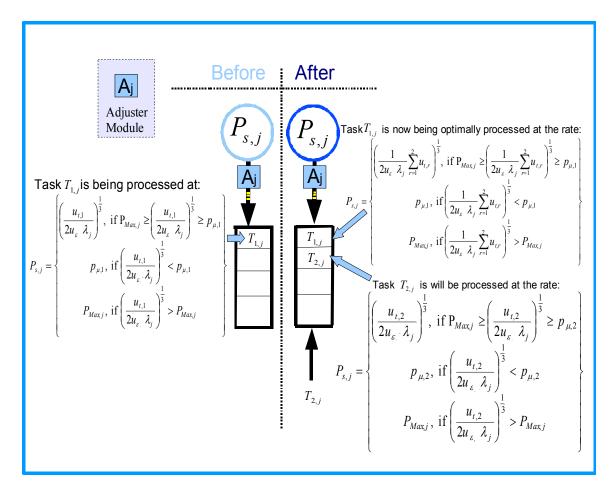

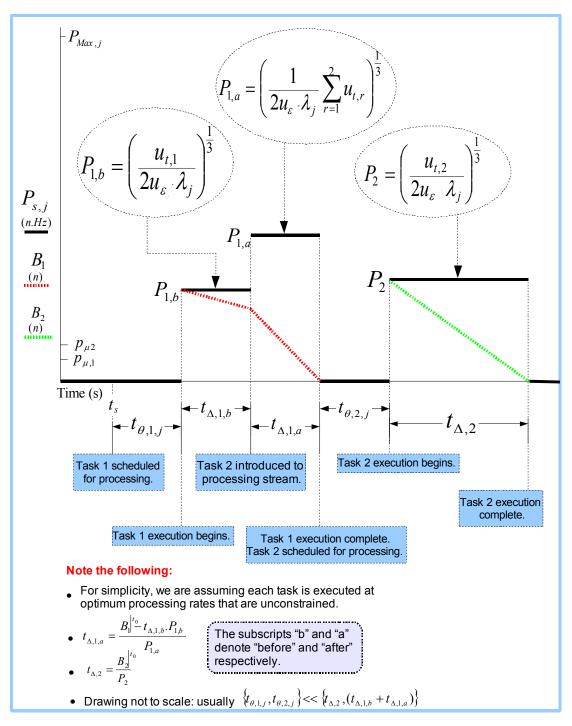

| 5.4 Analytical Demonstration                                                                                                                  | 85      |

| 5.4.1 A SMBSPP Robustness: Handles Dynamic Inclusion of Tasks                                                                                 | 85      |

| 5.5 Simulations                                                                                                                               | 88      |

| 5.5.1. Performance Metrics                                                                                                                    | 88      |

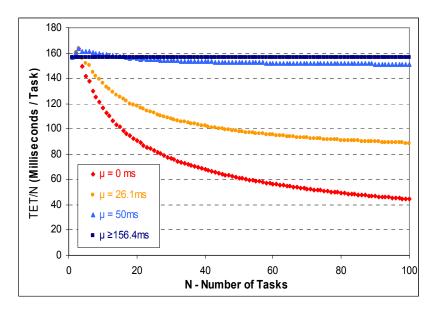

| 5.5.2 Simulation I: Sensitivity of SMBSPP Alg. To Inter-arrival Periods                                                                       | 88      |

| 5.5.3 Simulation II: Comparing SMBSPP Algorithm's Dispatcher Versus Round<br>Robin Dispatcher under FCFS, SRPT and SCVPPT Service Disciplines | l<br>91 |

| 5.5.4 Simulation III: Evaluating SMBSPP Algorithm's Dispatcher<br>(MMCVITPS) under FCFS, SRPT and SCVPPT Service Disciplines                  | 94      |

| 5.6 Comparing the SMBSPP Algorithm's Speed-Scaling Function                                                                                   |         |

| to a Competitive Speed Scaling Function in Current Literature                                                                                 | 95      |

| 5.6.1 Analytically Comparing OSTSSF to a Competitive Speed Scaling<br>Function in Current Literature                                          | 95      |

| 5.6.2 Simulation IV: Comparing SMBSPP Algorithm's Speed-Scaling                                                                               |         |

| Function (OSTSSF) to $\tilde{p}(\beta n)^{-1}$ under the SRPT Service Discipline                                                              | 98      |

| 5.7 Conclusions                                                                                                                               | 101     |

| 6. Using the Laws of Supply and Demand to Extend Battery Life and                                                                             |         |

| Improve Load Balancing                                                                                                                        | 104     |

| 6.1 Introduction                                                                                                                              | 104     |

| 6.2 Synthesizing the STMBAD Algorithm                                                             | 106 |

|---------------------------------------------------------------------------------------------------|-----|

| 6.2.1 Introduction                                                                                | 106 |

| 6.2.2 Mobile Hardware Resources of A Single Processor                                             | 107 |

| 6.2.3 Managing the Remaining Battery Energy Percentage                                            | 108 |

| 6.2.4 Showing How Increased Supply Leads To Lower Price & Vise Versa                              | 110 |

| 6.2.5 Problem Formulation                                                                         | 111 |

| 6.2.6 Cost Function                                                                               | 112 |

| 6.2.6 Minimized Cost Function                                                                     | 113 |

| 6.2.7 Minimized Constrained Cost Function                                                         | 115 |

| 6.3 The STMBAD Algorithm                                                                          | 115 |

| 6.4 Simulating The STMBAD Algorithm                                                               | 116 |

| 6.4.1 Performance Metrics                                                                         | 116 |

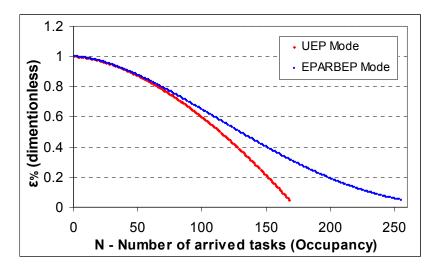

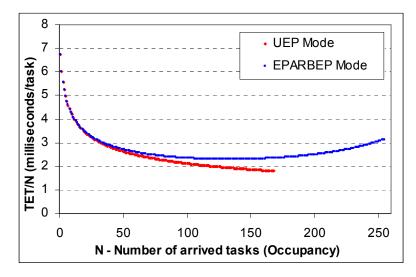

| 6.4.2 Simulation I: STMBAD Algorithm's EPARBEP Mode Versus UEP                                    | 117 |

| Mode While Processing N Homogenous Tasks                                                          | 117 |

| 6.4.3 Simulation II: STMBAD Algorithm's EPARBEP Mode Versus UEP<br>mode for N Heterogeneous Tasks | 122 |

| 6.5 Multiple Energy Sources                                                                       | 124 |

| 6.5.1 Mobile hardware Parameters of multiple energy sources.                                      | 124 |

| 6.5.2 Single or Multiple Energy Sources                                                           | 124 |

| 6.5.3 Defining operation modes for multiple energy sources                                        | 125 |

| 6.6 Extending The SBDPP Algorithm to Include EPARBEB Mode                                         | 125 |

| 6.6.1 A Processing Stream Cost Function                                                           | 125 |

| 6.6.2 Minimized Constrained Cost Function of the jth processing stream                            | 126 |

| 6.6.3 SBDPP Algorithm Under EPARBEP and UEP modes                                                 | 127 |

| 6.7 Extending The SBADPA Algorithm to Include EPARBEB Mode                                        | 129 |

| 6.8 Extending The SMBSPP Algorithm to Include EPARBEB Mode                                        | 131 |

| 6.8.1 The Minimized Constrained Cost Function of the j-th Processing                              |     |

| Stream under EPARBEP                                                                              | 131 |

| 6.8.2 SMBSPP Algorithm Under EPARBEP and UEP Modes                                                | 132 |

| 6.9 Effects of the EPARBEB and UEP Modes on the Speed Scaling        |     |

|----------------------------------------------------------------------|-----|

| Functions and Dispatchers of the Algorithms                          | 134 |

| 6.9.1 Effects of the EPARBEB and UEP Modes on the Speed Scaling      |     |

| Functions of the Algorithms                                          | 134 |

| 6.9.2 Effects of the EPARBEB and UEP Modes on the Dispatchers of the |     |

| Algorithms                                                           | 136 |

| 6.10 Conclusion                                                      | 141 |

|                                                                      |     |

| 7. Conclusion                                                        | 144 |

| 7.1 Research Summary                                                 | 144 |

| 7.1.1 Theoretical Framework                                          | 145 |

| 7.1.2 Single-buffered Processors                                     | 145 |

| 7.1.3 Multi-buffered Processors                                      | 146 |

| 7.1.4 Laws of Supply & Demand and Energy Sources                     | 148 |

| 7.2 Research Limitations                                             | 150 |

| 7.2.1 Algorithmic Overhead                                           | 150 |

| 7.2.2 Overhead Energy                                                | 151 |

| 7.2.3 Scope of Analysis                                              | 151 |

| 7.2.4 System Calibration                                             | 152 |

| 7.3 Future Research                                                  | 152 |

| 7.4 Closing Remarks                                                  | 153 |

|                                                                      |     |

| Bibliography                                                         | 154 |

| Appendices                                                           | 162 |

| Appendix I: Initial Modeling of A Task's Energy & Power Consumption  | 162 |

| Appendix II: Calibrating the Ratio of Time and Energy Prices under   |     |

| EPARBEP Mode                                                         | 163 |

| Appendix III: Determining a Task's Mode of Operation with            |     |

EPARBEP mode

# **List of Tables**

| Table 3.1: Other hardware parameters of the computing device              | 33  |

|---------------------------------------------------------------------------|-----|

| Table 3.2: Energy, power and execution time incurred (example scenario)   | 39  |

| Table 4.1: Interpretation of power sensitivity factor                     | 60  |

| Table 4.2: Qualitative comparison of algorithms                           | 65  |

| Table 4.3: Dispatcher cost savings: SBDPP algorithm versus TEST           | 67  |

| Table 5.1: Performance metrics                                            | 88  |

| Table 5.2: Interpretation of inter-arrival periods                        | 89  |

| Table 6.1: Hardware parameters of a mobile device with a single processor | 108 |

| Table 6.2: Performance metrics                                            | 117 |

| Table 6.3: Multiple energy sources                                        | 124 |

| Table 6.4: Load balancing effect on dispatchers by EPARBEP modes          | 141 |

# **List of Figures**

| Fig. 1.1: Thesis outline                                                                                                             | 10 |

|--------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.1: Overview of speed scaling problems (an algorithmic perspective)                                                            | 12 |

| Fig. 2.2: Single processor literature review and research gap                                                                        | 23 |

| Fig. 3.1: Interpretation and possible implementation of a User Profile                                                               | 30 |

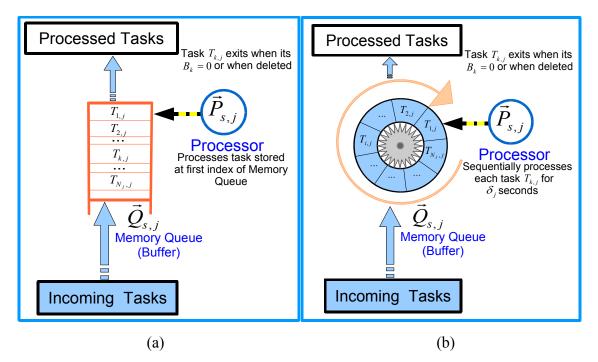

| Fig. 3.2: Processing Stream under (a) Single-threading and (b)<br>Multithreading computing architectures                             | 31 |

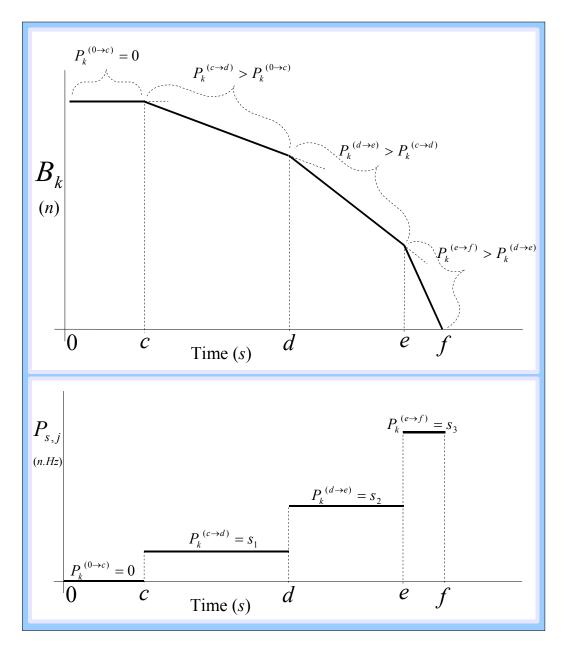

| Fig. 3.3: An example describing the remaining computation volume of a task during execution over a finite number of intervals        | 38 |

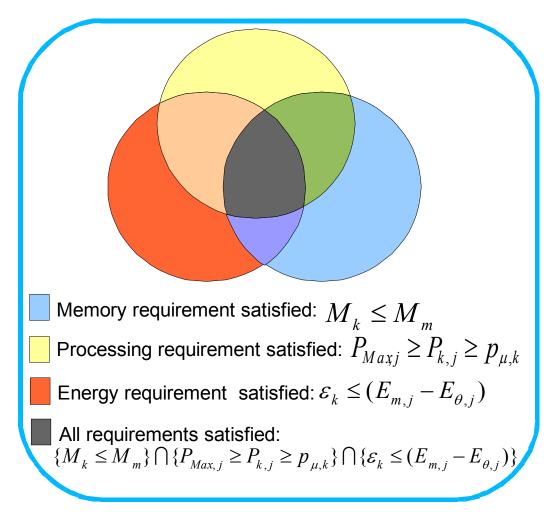

| Fig. 3.4: Memory, processing rate and energy constraints                                                                             | 40 |

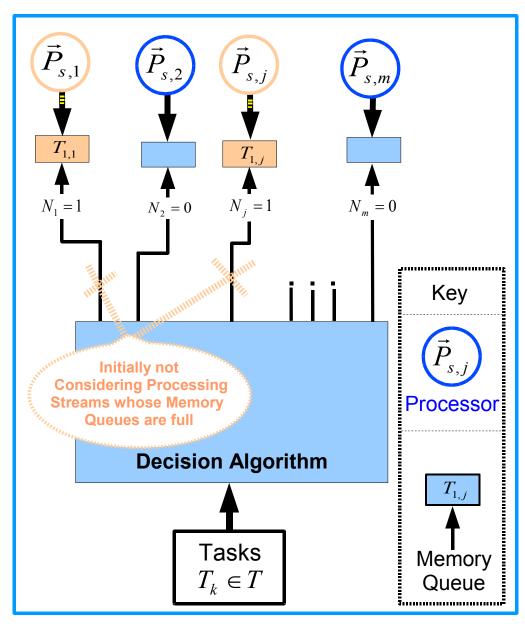

| Fig. 3.5: Placing our problem relative to the single processor problems in literature                                                | 44 |

| Fig. 4.1: Illustrating the parallel single-buffer scenario                                                                           | 50 |

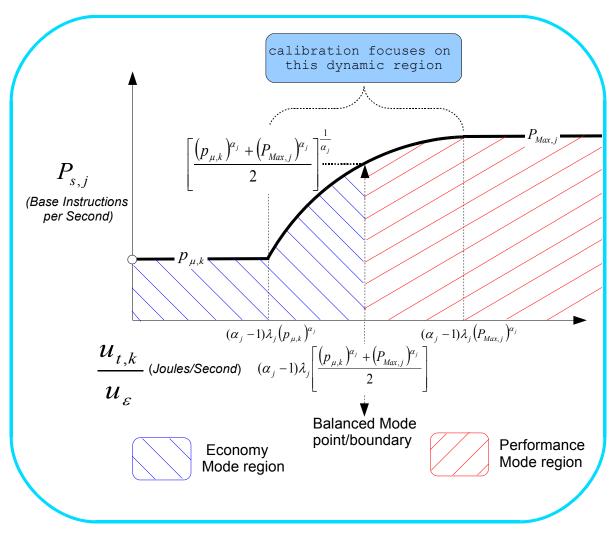

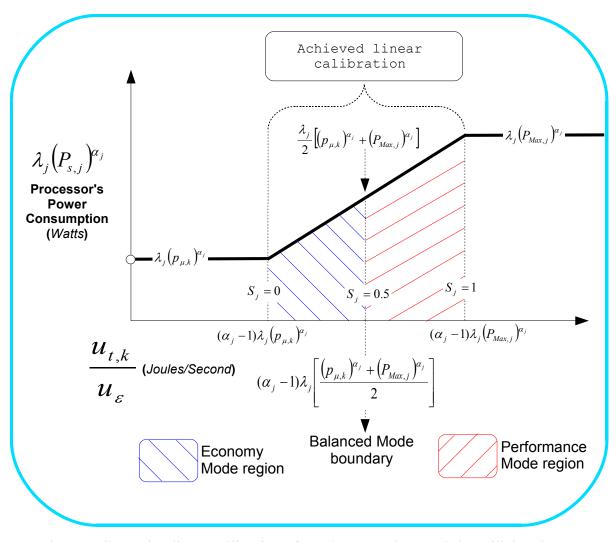

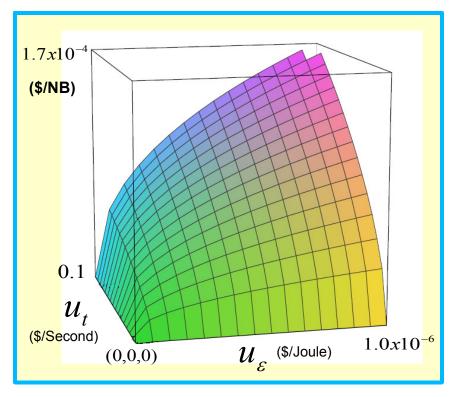

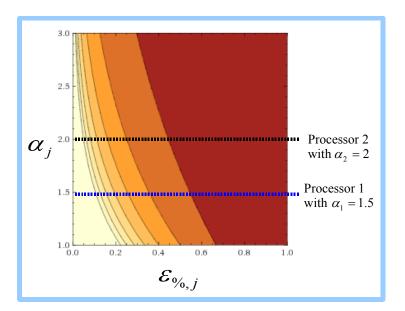

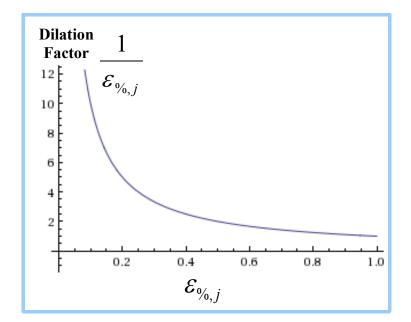

| Fig. 4.2: A task's operating mode and optimum processing rate as a function of user-defined unit prices                              | 57 |

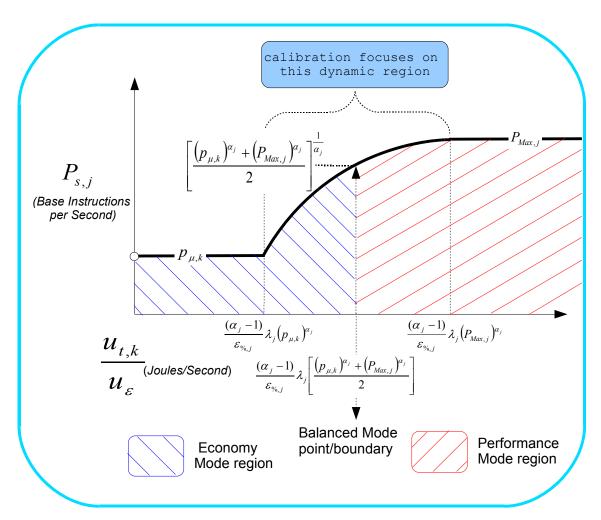

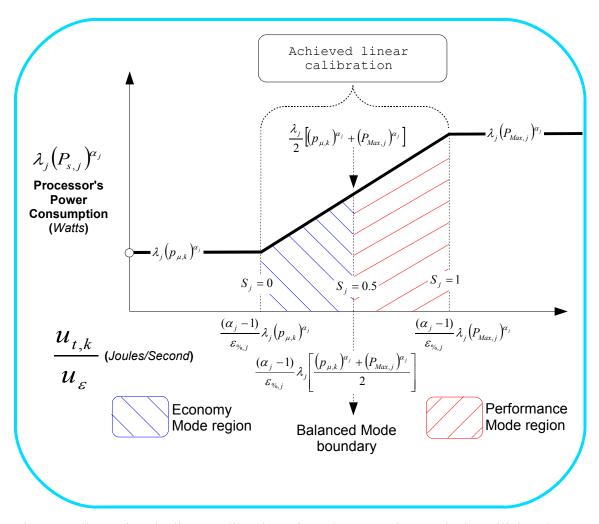

| Fig. 4.3. Illustrating linear calibration of a task's operation mode by utilizing the processor's power consumption during execution | 59 |

| Fig. 4.4: Dispatcher cost savings: SBDPP algorithm versus TEST                                                                       | 68 |

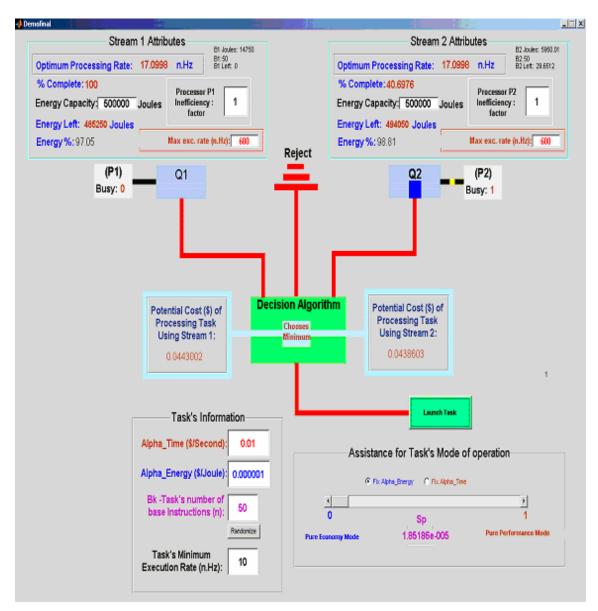

| Fig. 4.5. MATLAB GUI simulation validating all three algorithms                                                                      | 69 |

| Fig. 5.1: The parallel multi-buffer scenario                                                                                         | 76 |

| Fig. 5.2: Example demonstrating how SMBSPP robustly handles dynamic inclusion of tasks                                               | 86 |

| Fig. 5.3: Time analysis of the processor as it executes each of the two tasks in the example                                         | 87 |

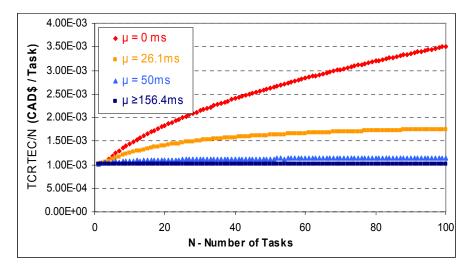

| Fig. 5.4: Average execution time for N homogeneous Tasks: effect                   |    |

|------------------------------------------------------------------------------------|----|

| of deterministic arrival periods $(\mu)$                                           | 90 |

| Fig. 5.5: Average cost of response time & energy consumption for N                 |    |

| homogeneous tasks: Effect of deterministic arrival periods ( $\mu$ )               | 90 |

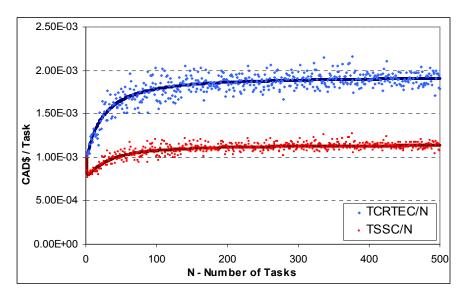

| Fig. 5.6: Average cost of response time & energy consumption versus                |    |

| average cost of system time & energy consumption for N                             |    |

| homogenous tasks with Poisson arrivals (heavy traffic)                             | 91 |

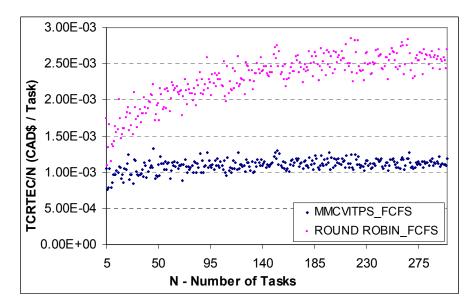

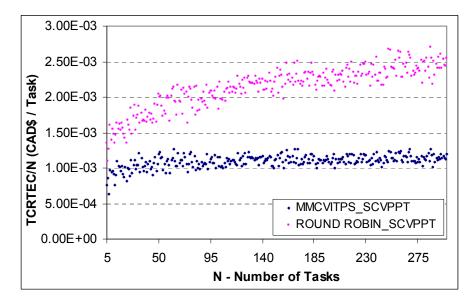

| Fig. 5.7: MMCVITPS Versus Round Robin for N heterogeneous tasks with               |    |

| Poisson arrivals (heavy traffic) and Gaussian dist. CV; heterogeneous              |    |

| unit prices of response time under FCFS Service Discipline                         | 92 |

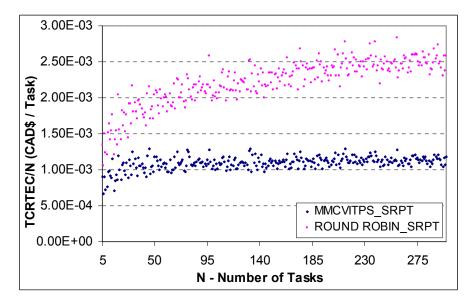

| Fig. 5.8: MMCVITPS Versus Round Robin for N heterogeneous tasks with               |    |

| Poisson arrivals (heavy traffic) and Gaussian dist. CV; heterogeneous              |    |

| unit prices of response time all under SRPT Service Discipline                     | 93 |

| Fig. 5.9: MMCVITPS Versus Round Robin for N heterogeneous tasks with               |    |

| Poisson arrivals (heavy traffic) and Gaussian dist. CV; heterogeneous              |    |

| unit prices of response time all under SCVPPT Service Discipline                   | 93 |

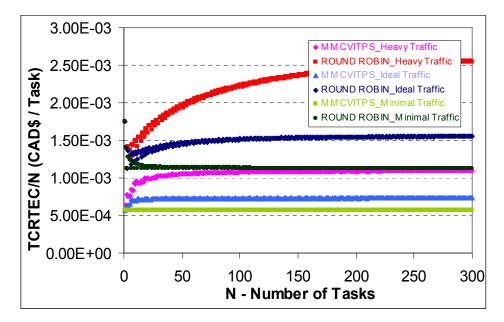

| Fig. 5.10: MMCVITPS Versus Round Robin for N homogeneous tasks under               |    |

| three main deterministic arrival periods with homogeneous unit                     |    |

| prices of response time                                                            | 94 |

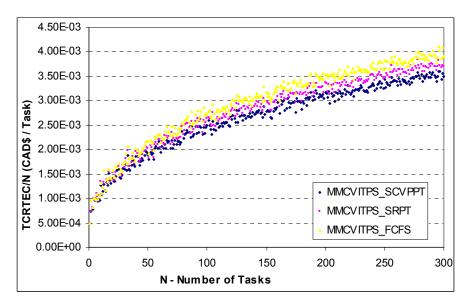

| Fig. 5.11: MMCVITPS Dispatcher performance under SCVPPT, SRPT and                  |    |

| FCFS service disciplines for N heterogeneous tasks; Poisson arrivals;              |    |

| extreme traffic; Gaussian Distributed CV and response time pricing                 | 95 |

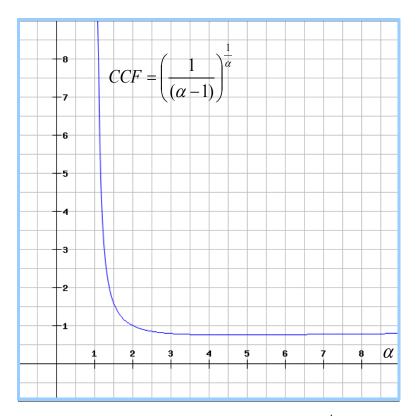

| Fig. 5.12: Constant Correction Factor between $\tilde{p}(\beta n)^{-1}$ and OSTSSF | 98 |

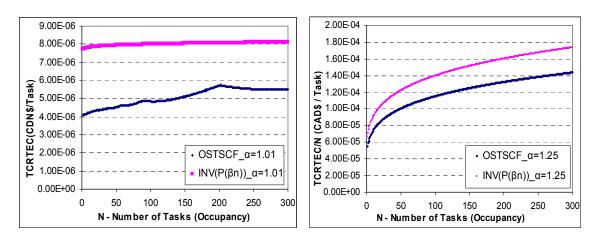

| Fig. 5.13: OSTSSF versus $\widetilde{p}(\beta n)^{-1}$ for $\alpha = 1.01$         | 99 |

| Fig. 5.14: OSTSSF versus $\tilde{p}(\beta n)^{-1}$ for $\alpha = 1.25$             | 99 |

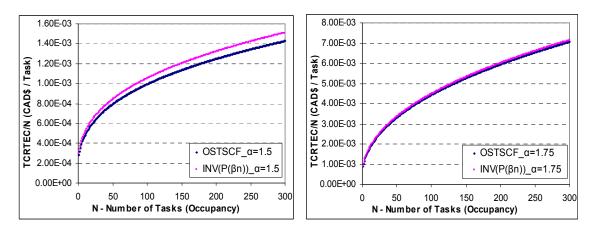

| Fig. 5.15: OSTSSF versus $\tilde{p}(\beta n)^{-1}$ for $\alpha = 1.5$              | 99 |

| Fig. 5.16: OSTSSF versus $\tilde{p}(\beta n)^{-1}$ for $\alpha = 1.75$                                                                          | 99  |

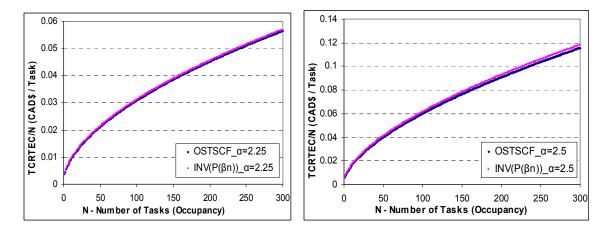

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.17: OSTSSF versus $\tilde{p}(\beta n)^{-1}$ for $\alpha = 2.25$                                                                          | 100 |

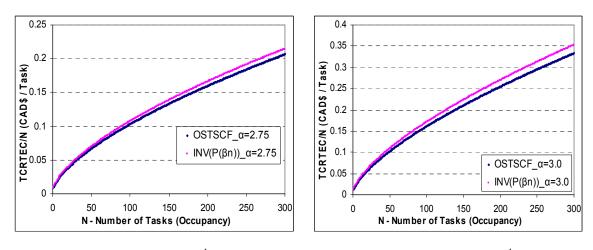

| Fig. 5.18: OSTSSF versus $\tilde{p}(\beta n)^{-1}$ for $\alpha = 2.5$                                                                           | 100 |

| Fig. 5.19: OSTSSF versus $\tilde{p}(\beta n)^{-1}$ for $\alpha = 2.75$                                                                          | 100 |

| Fig. 5.20: OSTSSF versus $\tilde{p}(\beta n)^{-1}$ for $\alpha = 3.0$                                                                           | 100 |

| Fig. 6.1:Remaining battery energy percentage of an iPhone 5                                                                                     | 109 |

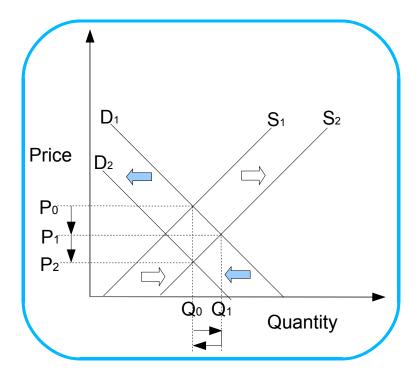

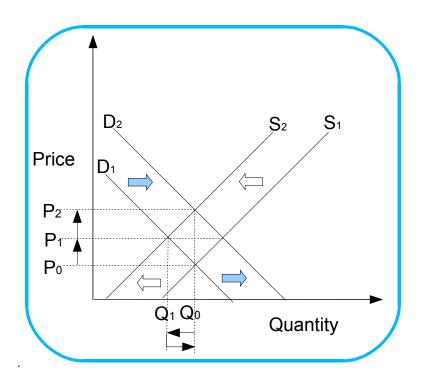

| Fig. 6.2: Increased supply of a commodity leads to lower price                                                                                  | 110 |

| Fig. 6.3: Decreased supply of a commodity leads to higher price                                                                                 | 111 |

| Fig. 6.4: Remaining battery energy percentage $\varepsilon_{\%}$ after executing N tasks                                                        | 118 |

| Fig. 6.5: Average execution time of executing N homogeneous tasks                                                                               | 119 |

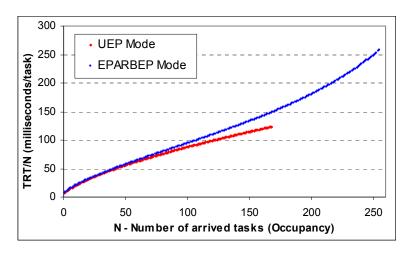

| Fig. 6.6: Average response time for N homogeneous tasks                                                                                         | 120 |

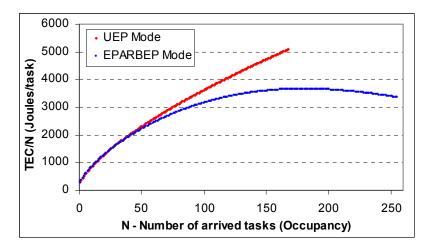

| Fig. 6.7: Average energy consumption for executing N homogeneous tasks                                                                          | 121 |

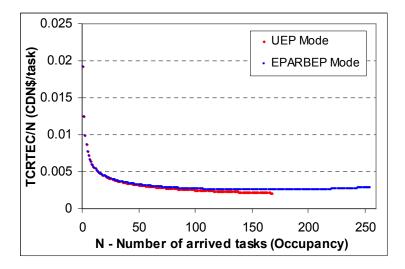

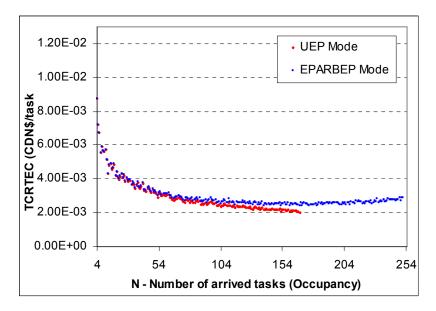

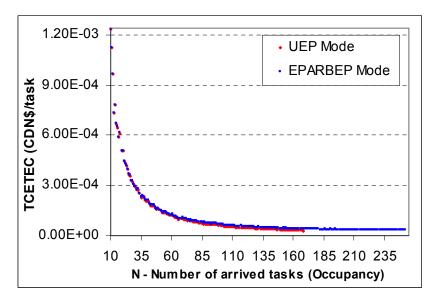

| Fig. 6.8: Average cost of response time and energy consumption for executing N homogeneous tasks                                                | 121 |

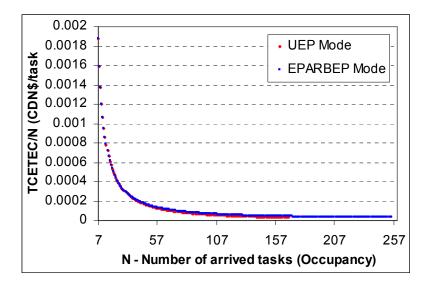

| Fig. 6.9: Average cost of execution time and energy consumption for executing N homogeneous tasks                                               | 122 |

| Fig. 6.10: Average cost of response time and energy consumption for executing N heterogeneous tasks (Gaussian distributed computation volumes)  | 123 |

| Fig. 6.11: Average cost of execution time and energy consumption for executing N heterogeneous tasks (Gaussian distributed computation volumes) | 123 |

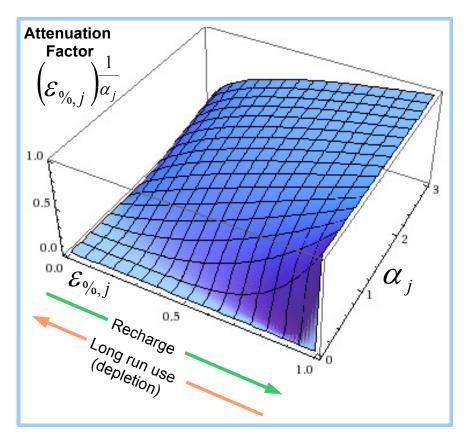

| Fig. 6.12: Attenuation factor induced by the EPARBEP mode on speed scaling functions                                                            | 135 |

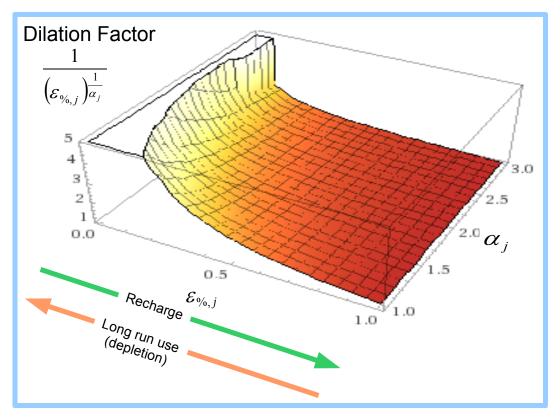

| Fig. 6.13: Dilation factor induced by the EPARBEP mode on dispatchers under unconstrained processing rates                                      | 138 |

| Fig. 6.14: Contour diagram of Figure 6.13 with a superimposed example         | 139 |

|-------------------------------------------------------------------------------|-----|

| Fig. 6.15: Dilation factor induced by the EPARBEP mode on dispatchers under   |     |

| constrained processing rates                                                  | 140 |

| Fig. A1: A task's operating mode and optimum processing rate as a function of |     |

| user-defined (time/energy) unit prices under EPARBEP mode                     | 164 |

| Fig. A.2: linear calibration of a task's operation mode using the processor's |     |

| power consumption during execution under EPARBEP mode                         | 167 |

# List of Abbreviations

| ACPI     | Advanced Configuration and Power Interface architecture                                                                 |

|----------|-------------------------------------------------------------------------------------------------------------------------|

| AMD      | Advanced Micro Devices: a technology company                                                                            |

| AR       | Average Rate: an algorithm                                                                                              |

| BAL      | Bampis, Angel and Letios: an algorithm                                                                                  |

| ВКР      | Bansal, Kimbrel and Pruhs: an algorithm                                                                                 |

| BPS      | Bansal, Pruhs and Stein: an algorithm                                                                                   |

| CMOS     | Complementary Metal Oxide Semiconductor                                                                                 |

| CPU      | Central Processing Unit                                                                                                 |

| EDF      | Earliest Deadline First: a service discipline/policy                                                                    |

| EPARBEP  | Energy Price Affected by Remaining Energy Percentage: <i>a</i> proposed operation mode in computing                     |

| FCFS     | First Come First Serve: a well known service discipline                                                                 |

| FPDPA    | Fixed Power Decision & Processing Algorithm: <i>a proposed algorithm</i>                                                |

| FTPE     | Flow Time Plus Energy: a dynamic speed scaling problem                                                                  |

| GUI      | Graphical User Interface                                                                                                |

| HDF      | Highest Density First: a service discipline/policy                                                                      |

| НМО      | Horizontal Migratory Operation: <i>a proposed operation to tackle migration</i>                                         |

| IBM      | International Business Machines Corporation: <i>a technology company</i>                                                |

| LSD      | Laws of Supply and Demand (micro-economic)                                                                              |

| MATLAB   | MATtrix LABoratory: a numerical computing environment                                                                   |

| MMCVITPS | Minimum among Minimized Costs of Virtually Introducing the Task to each Processing Stream: <i>a proposed dispatcher</i> |

| OA       | Optimum Available: an algorithm                                                                                         |

| OS       | Operating Software                                                                                                      |

| OSTSSF   | Optimum Single-Threading Speed Scaling Function: <i>a proposed speed scaling function</i>                               |

| PDM      | Power Down Mechanisms                                                                                                   |

| PS       | Processor Sharing: a well known computing architecture                                                                  |

| SBADPA   | Single-Buffer Assisted Decision & Processing Algorithm: <i>a</i> proposed algorithm                                     |

| SBDPP    | Single-Buffer Decision & Parallel Processing: <i>a proposed</i> algorithm                                   |

|----------|-------------------------------------------------------------------------------------------------------------|

| SCVPPT   | Smallest remaining Computation Volume Per unit Price of response Time: <i>a proposed service discipline</i> |

| SMBSPP   | Single-threading Multi-Buffer Scheduling & Parallel Processing: <i>a</i> proposed algorithm                 |

| SRPT     | Shortest Remaining Processing Time: a well known service discipline                                         |

| ST       | System Time: a performance metric                                                                           |

| STMBAD   | Single-Threading Multi Buffer Adjusted Dynamic speed-scaling algorithm: <i>a proposed algorithm</i>         |

| TCRTEC   | Total Cost of Response Time and Energy Consumption in dollars: <i>a proposed performance metric</i>         |

| TCRTEC/N | Average Cost of Response Time and Energy Consumption for executing N tasks: <i>a performance metric</i>     |

| TEC      | Total Energy Consumption: a performance metric                                                              |

| TEC/N    | Average Energy Consumption for executing N tasks: <i>a performance metric</i>                               |

| ТЕТ      | Total Execution Time: a performance metric                                                                  |

| TET/N    | Average Execution Time of executing N tasks: <i>a performance metric</i>                                    |

| TRT      | Total Response Time: a performance metric                                                                   |

| TRT/N    | Average Response Time of N tasks: a performance metric                                                      |

| TSSC     | Total cost of System time and energy Consumption: <i>a performance metric</i>                               |

| TSSC/N   | Average cost of System time and energy Consumption for executing N tasks: <i>a performance metric</i>       |

| UEP      | Unadjusted Energy Price: a proposed operation mode in computing                                             |

| XTG      | XTG Technology: a consumer electronics manufacturer                                                         |

| YDS      | Yao, Demers, Shenker: an algorithm                                                                          |

## **Chapter 1: Introduction**

#### **1.1 Motivation**

Energy consumption is a major constraint in today's computing devices. A principal engineer at Google alerts us that in the next few years, power costs could substantially exceed (server) hardware costs under the current trend of performance and power consumption [16]. Portable/mobile computing devices e.g. laptops and mobile phones are a special class of computing devices in that they rely on batteries for energy. In portable computing devices, battery energy is indeed a scarce and essential resource. Desirable user experience, measured by sufficiently fast execution of tasks is equally important. Portable battery life can be extended by higher capacity batteries or through remote execution [55]. On the go, it can also be extended by portable energy restoration devices such as solar panel chargers produced and sold by XTG Technology [67]. An online article suggests that in 2009, Nokia worked on a technology to recharge their cellular phone battery by extracting energy emitted from ambient radio waves [62]. In that same year, another online article reports that Samsung worked to develop a prototype of a solar powered cellular phone [66]. It is evident that energy in portable computing devices is of great concern and companies that design or manufacture portable computing devices invest in battery or energy technology to remain competitive.

From an algorithmic perspective, computing devices can use variable speed processors to regulate the energy consumption and completion time of executing jobs/tasks. Intel, IBM and AMD provide a selection of multiprocessors that are indeed capable of operating at variable speeds. The ability of a processor to operate at a variable speed is known as *dynamic speed scaling*. Dynamic Speed scaling has been used as a strategy to reduce energy consumption [2, 4, 6, 7, 33, 68]. It has been used to manage a processor's temperature and energy consumption [12] as well as to mitigate processor heat failure [49]. Some speed scaling algorithms factor both time and energy consumption of tasks [1, 68].

Contemporary portable computing devices such as the recent versions of mobile phones, Tablets, iPads and gaming consoles (for example, the PSPVita [65]) utilize multiple processors. Multiple parallel processors are mostly used to improve overall processing performance needed for multi-media applications. In the domain of scheduling, considerable attention has been given to single processor architecture [1, 11-13, 15, 47, 56, 58, 68]. Fewer have considered multiprocessors [4, 7, 20, 42, 44]. Although current architectures mostly consist of homogenous collection of processors, several works suggest that future chip architectures would consist of heterogeneous processors e.g. [18, 53]. Gupta et al. [28] further suggest that scheduling heterogeneous processors is substantially more challenging than scheduling homogeneous processors.

This thesis primarily investigates how to (online) schedule arriving heterogeneous tasks to run on multiple, heterogeneous, speed-scalable processors with the goal of minimizing the financial cost of response time and energy consumption of tasks. The tasks are heterogeneous in terms of computation volume, memory and processing requirements. The processors are heterogeneous in terms of their hardware specifications with respect to maximum processing rate, power functions and energy sources. The user or OS is also allowed to dictate the unit price of response time per task so as to influence the priority of tasks. In a later chapter of this thesis, we also allow the unit price of energy for all tasks to be heuristically adjusted by the micro economic laws of demand and supply so as to conserve energy and improve load balancing on heterogeneous processors.

#### **1.2 Research Overview**

The energy consumption of a processor is commonly assumed to grow in proportion to  $s^{\alpha}$  where s is the processor speed and  $\alpha$  is a constant > 1 e.g. [4, 7, 19, 25, 68]. This implies that a high processing speed leads to fast execution, but incurs a high energy consumption. One way to reduce energy consumption is to employ dynamic speedscaling (e.g. see [13, 69]), where the speed of the processors can be changed dynamically depending on the workload. The aim is to reduce processor speed at times of low workload.

Generally, the goal of any speed-scaled multiprocessor scheduling algorithm is: (i) to minimize the response time given energy as a budget, (e.g. [59]) or (ii) to minimize the energy consumption as long as the task deadlines are not violated [56, 58, 68], or (iii) to optimize a tradeoff between energy consumption and response time [6, 15]. The objective

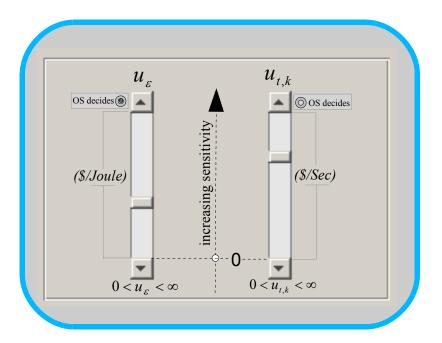

of our work is to synthesize parallel scheduling algorithms that use dynamic speed scaling to minimize the total cost (in terms of dollars) of energy and response time (**TCRTEC**). In our work, the user or OS determines unit price of response time per task. This allows the user to influence the degree of a task's execution in the economy-performance continuum. The user or OS can set the unit price of energy for all tasks depending on the actual unit price of energy in a given geographical region and time of day.

A brief summary of key assumptions made in this thesis are as follows.

- *Multiple heterogeneous processors:* Few speed scaling algorithms factor multiple processors e.g. [2, 4, 7]. Our scheduling algorithms consider heterogeneous processors that may differ in all their hardware specifications with respect to maximum processing rate, power function parameters and energy sources.

- *Heterogeneous tasks:* There are speed scaling algorithms that only consider homogenous tasks, e.g. [1, 11, 59]. We consider heterogeneous jobs/tasks that may differ in computation volume, memory and processing requirements.

- Online: Some speed scaling algorithms operate offline e.g. YDS algorithm in [68]. Our algorithms run in real time to schedule incoming heterogeneous tasks to run on heterogeneous processors.

- *Constrained processing rates*: We factor the maximum hardware processing rate of processors and the minimum software processing rate of tasks to regulate the execution of tasks as opposed to deadline based scheduling of tasks. Many speed scaling algorithms [2, 4, 7, 46, 68] utilize deadline based scheduling. Deadline based scheduling is not always practical in general because tasks that run in conventional operating systems such as Windows and Unix do not utilize it, but instead use minimum or recommended processing rates to regulate the smooth execution of a task or application. Although few speed scaling algorithms factor the maximum hardware processing rate e.g. [11, 71], our speed scaling algorithms are the only ones that explicitly factor both hardware and software processing constraints.

- User or OS determines unit cost of energy and time of a task's execution: Unlike any speed scaling algorithm, we explicitly factor the input of a user or OS with

respect to determining the unit price time for executing each task. This allows the user to influence the priority of tasks. The user or OS can set the unit price of energy for all tasks depending on the actual unit price of energy in a given geographical region and time of day.

- *Overhead access time of loading tasks:* We have not seen any dynamic speed scaling algorithm explicitly factors the overhead access time of loading and accessing a task by a given processor prior to execution.

- Multiple energy sources: Unlike any speed scaling algorithm, our algorithms allow each processor to have its independent energy source. In the future, each processor may have its own energy source to improve reliability and also to increase total energy of the mobile computing device. Our analysis effortlessly considers the single energy source as well.

- *Tasks' unit price of energy adjusted by battery energy level*: Unlike any speed scaling algorithm, we allow the unit price of energy for all tasks to be heuristically adjusted by the device's remaining battery (or batteries) energy level in accordance with the micro-economic laws of supply and demand. This is done so as to conserve energy and additionally done to improve load balancing.

#### **1.3 Related Works**

In this section, we provide a concise summary of prior related work that is most relevant to this thesis.

In the past, when energy was not a major concern, the objective of scheduling algorithms was to minimize the total response time (also called flow time) of all tasks where processors were running at fixed speeds (e.g. [10, 57]). The response time is the time elapsed since a task arrives until it is completed.

The study of energy-efficient speed-scaled scheduling was initiated by Yao et al. in [68]. They considered deadline-based scheduling for a single processor where the jobs need to complete by their given deadlines. The goal was to minimize energy consumption. Assuming the processor's power consumption (P(s)) is a convex function of processor speed (s), where  $P(s) = s^{\alpha}$  for  $\alpha > 1$ , they considered scheduling a sequence of tasks

on a single variable speed processor. Each task has a required deadline, release time and processing volume (analogous to the number of CPU cycles required to execute a task). They allow pre-emption, where a task is allowed to resume on the same processor after being interrupted. They proposed an optimal offline algorithm (YDS) to solve the task scheduling problem in polynomial time. In the same work, they further introduced two online algorithms, namely, Optimum Available (OA) and Average Rate (AR). They proved that AR has an energy competitive ratio of  $(2\alpha)^{\alpha}/2$ . Bansal, Kimbrel and Pruhs [12] worked on OA and proved it to have an energy competitive ratio of exactly  $\alpha^{\alpha}$ . To solve for multiprocessor case, Angel et al. [7] considered the problem of scheduling a set of tasks with deadlines, release dates and processing requirements, on parallel (speed scalable) processors so as to minimize the total energy consumption. They considered migration where a task is allowed to resume its execution on a different processor. They also allowed pre-emption. They name their optimal scheduling algorithm BAL which has a time complexity of  $O(nf(n)\log U)$  where, n is the number of jobs, f(|V|) is the computational complexity of solving a maximum flow in a layered graph with O|V| vertices and U is the range of all processor speed values divided by the targeted accuracy. Independently, Albers et al. [2] considered the same multiprocessor speed scaling problem with migration, and obtained an optimal scheduling algorithm that is fully combinatorial and has a time complexity of  $O(n^2 f(n))$ . Angel et al. [7] compared their BAL algorithm to the one of Albers et al. [2] and stated that when the target precision is sufficiently high, the algorithm of Albers et al. [2] is superior to BAL, otherwise if the target accuracy is relaxed, BAL's algorithm is indeed superior.

Among energy efficient scheduling algorithms, several studies have considered minimizing the response time of jobs given a set energy budget (e.g. [59]). In particular, Pruhs et al. [59] considered offline scheduling to minimize the average response time on a single processor, for a given amount of energy. They gave a polynomial time optimal algorithm for the special case when jobs are of unit size.

To better understand the tradeoff between response time and energy, Albers and Fujiwara [1] proposed minimizing the sum of total response time and energy for a single

processor. They presented an online algorithm that is  $8.3e\left(\frac{3+\sqrt{5}}{2}\right)^{\alpha}$  competitive for jobs

of unit size. This result was improved by Bansal et al. [15] who showed that this algorithm is 4-competitive. Bansal et al. [15] also gave the first constant competitive algorithm for arbitrary size jobs. The multiprocessor case was first discussed by Bunde [20] that presented an offline approximation algorithm for unit size jobs. However, Lam et al. [44] presented the first constant competitive online algorithm for arbitrary job sizes. In [44], jobs are clustered and then round robin dispatched to the processors independently for each cluster. Then they apply the BPS online algorithm given by Bansal et al. [14-15] to each processor.

In this thesis, we present online (dynamic speed scaling) scheduling algorithms that minimizes the financial cost of response time plus energy for the heterogeneous multiprocessor case.

#### **1.4 Thesis Contribution**

The contributions of the thesis are as follows:

1. Propose a theoretical frame work to tackle the problem of dynamic speed scaling in a parallel heterogeneous processing environment. We do so by carrying out the following.

- a) Define and describe a task, its computation volume and minimum processing rate.

- b) Define and describe a *user profile*.

- c) Define and describe a *processing stream* under different computing architectures and briefly describe *parallel processing streams*.

- d) Define relevant *mobile hardware resource parameters* and describing how our framework handles single and multiple energy sources.

- e) Model the *overhead access time* and describing the theoretical processing rate and execution time of a task.

- f) Use formulas in current literature to deduce useful relationships pertaining to a task's computation volume, energy and power consumption.

- g) Analytically and graphically illustrate the effect of processing on a task's remaining computation volume as well as the energy and power consumed.

- h) Describe the decision algorithm and summarizing relevant pre-processing constraints.

- i) Justify the constituents of our target performance metric and briefly critique other performance metrics used in current literature.

- j) Distinguish our model from other relevant models found in current literature and map our contributions in current literature.

- k) Define traffic conditions to systematically analyze and simulate our algorithms.

2. Present the first, elaborate, analytical study on the use of dynamic speed scaling to schedule heterogeneous tasks on single-buffered, heterogeneous, parallel processors with the objective of reducing the total cost of response time and energy consumption. We accomplish this by carrying out the following.

- a) Use our theoretical framework to formulate the problem and to synthesize the "*Single-Buffer Decision & Parallel Processing* (SBDPP)" algorithm.

- b) Achieve a linear calibration of a task's operation mode as a function of the (user-specified) unit prices of time and energy.

- c) Construct and present two other versions of the SBDPP algorithm, namely "Single Buffer Assisted Decision & Processing Algorithm (SBADPA)" and "Fixed Power Decision & Processing Algorithm (FPDPA)".

- d) Briefly describe how the SBDPP algorithm handles migration.

- e) Qualitatively compare the three versions of the SBDPP algorithm to each other.

- f) Analytically show that the dispatcher of the SBDPP algorithm outperforms the Round Robin dispatcher under minimal traffic conditions.

- g) Develop a MATLAB Graphical User Interface program to simulate the SBDPP, SBADPA and FPDPA algorithms and also validate the algorithms via discrete time based simulations written in Java.

- h) Use the simulations to deduce a relationship between the arrival rate of tasks, number of processors and response time of tasks under the (parallel) single buffered computing architecture.

- i) Provide insights on the limitations of the parallel single buffered computing architecture.

3. Study the use of dynamic speed scaling to schedule heterogeneous tasks on multibuffered, heterogeneous, parallel processors with the objective of reducing the total cost of response time and energy consumption (TCRTEC) of tasks.

We achieve this by carrying out the following.

- a) Synthesize and present the *"Single-threading Multi-Buffer Scheduling & Parallel Processing* (SMBSPP)" algorithm.

- b) Present the (SMBSPP) algorithm's dispatcher which assigns heterogeneous tasks to a given heterogeneous processors.

- c) Present the (SMBSPP) algorithm's dynamic speed-scaling function, which we name, "*Optimum Single-Threading Speed Scaling Function*" (OSTSSF).

- d) Present the (SMBSPP) algorithm's service discipline which we name the "Smallest remaining Computation Volume Per unit Price of response Time (SCVPPT)".

- e) Use a variety of performance metrics to validate the functionality of the SMBSPP algorithm by conducting discrete time based simulations written in Java (as well as analytical techniques).

- f) Use simulations to show that our MMCVITPS dispatcher works well with heterogeneous processors and drastically outperforms the classic Round Robin dispatcher with cost savings exceeding 100% on average even when processors are mildly heterogeneous. This was done under various deterministic and stochastic traffic conditions.

- g) Show that our SCVPPT scheduling discipline outperforms the two known service disciplines, Shortest Remaining Processing Time (SRPT) and the First Come First Serve (FCFS), in terms of minimizing the TCRTEC performance metric.

- h) Analytically compare our dynamic speed scaling function (OSTSSF) to a comparable and most competitive speed scaling function found in current literature.

- i) Corroborate this analytical comparison with elaborate simulations (written in Java) to show that our OSTSSF out performs this competitive speed scaling function in terms of the TCRTEC performance metric.

j) Offer a recommendation to improve the most competitive speed scaling function found in current literature in terms of minimizing the TCRTEC performance metric.

4. Use our theoretical framework and the Laws of Supply and Demand (LSD) to heuristically adjust the unit price of energy, extend battery life and improve load balancing in speed scalable processors of a mobile computing device. We do so by carrying out the following.

- a) Use LSD to heuristically adjust the unit price of energy of tasks via the remaining energy percentage parameter.

- b) Use the remaining energy percentage parameter and our theoretical framework to synthesize an online single processor (multi-buffered) speed-scaling algorithm (*Single-Threading Multi Buffer Adjusted Dynamic speed scaling* algorithm STMBAD).

- c) Use discrete time based simulations (written in Java) to show that when the STMBAD algorithm factors the remaining energy percentage parameter, it completes more than 50% more jobs for both homogenous and heterogeneous tasks and ultimately allows the mobile computing device to last longer on the go.

- d) Implement the remaining energy percentage parameter in the speed scaling functions of all algorithms presented in this thesis to analytically show that it is a heuristic controller that rations battery energy by slowing down the speed scaling functions of our algorithms (as the battery depletes).

- e) Integrate the remaining energy percentage parameter to the dispatchers of all algorithms presented in this thesis to analytically show that it is a heuristic controller that induces load balancing when each heterogeneous processor has its independent energy source.

- f) Shed light on the difference between optimum and robust speed scaling algorithms (speed scaling functions and coupled dispatchers) in the context of scheduling and processing heterogeneous tasks by heterogeneous processors with the goal of reducing response time and adjusted energy consumption.

Preliminary components of this thesis were peer-reviewed and accepted for publication in [39-41].

#### 1.5 Thesis Outline

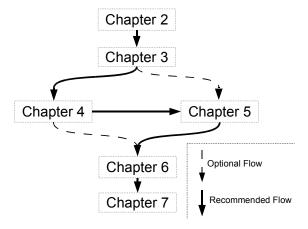

Fig. 1.1: Thesis outline

Chapter 2 provides a background of the relevant definitions, principles and models found in current literature that are pertinent to speed scaling. In chapter 3, we propose a theoretical frame work to tackle the problem of dynamic speed scaling in a parallel heterogeneous processing environment. This framework is used in all subsequent chapters of this thesis. In chapter 4, we present the first, elaborate, analytical study on the use of dynamic speed scaling to schedule heterogeneous tasks on single-buffered, heterogeneous, parallel processors with the objective of minimizing the total cost of response time and energy consumption. In Chapter 5 we study the use of dynamic speed scaling to schedule heterogeneous tasks on multi-buffered, heterogeneous, parallel processors (under the single-threaded computing architecture) with the objective of minimizing the total cost of response time and energy consumption of tasks. In Chapter 6, we use our theoretical framework and the *Laws of Supply and Demand* to heuristically adjust the unit price of energy, extend battery life and improve load balancing in speed scalable processors of a mobile computing device. Lastly, In chapter 7, we summarize the critical findings presented in this thesis, discuss the limitations of our findings, highlight interesting opportunities for future work and offer closing remarks.

# 2. Background

#### 2.1 Introduction

In this chapter we present a concise overview of speed scaling algorithms that relate to the work in this thesis. Survey papers by Albers, S. [3] and Irani et al. [35] provide elaborated studies of these algorithms. Like much of the work in existing literature, this thesis concentrates on the system and device level to formulate and solve problems through an algorithmic perspective.

#### 2.2 Speed Scaling

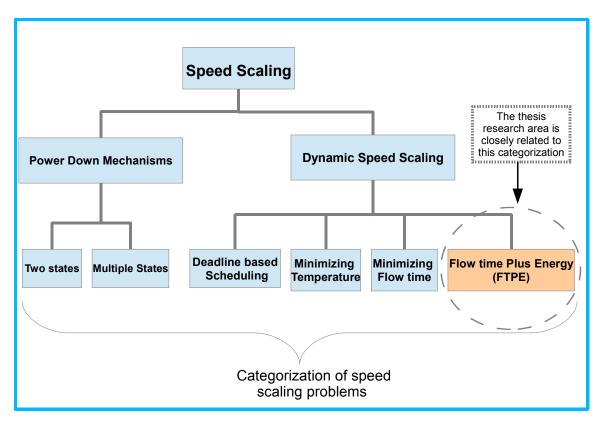

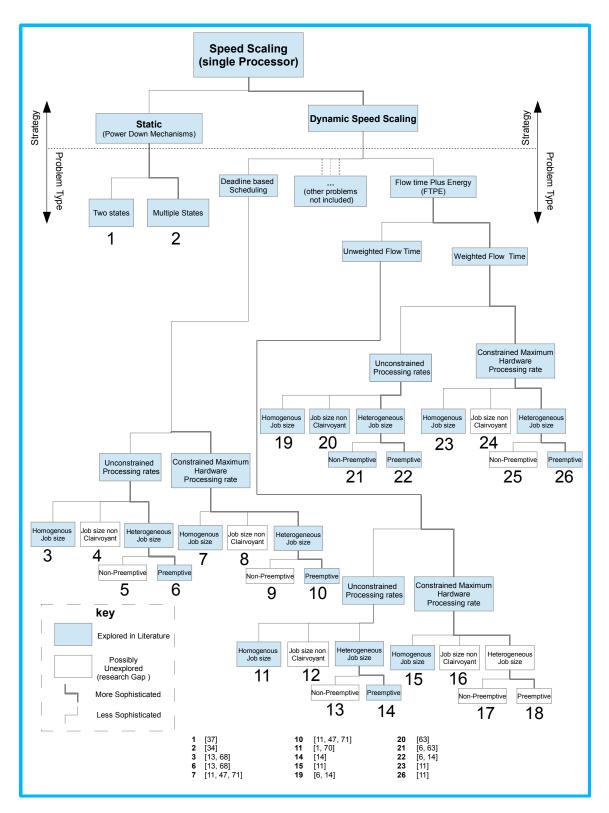

In existing literature, there are two types of speed scaling, Static and Dynamic speed scaling [6]. Static speed scaling can either involve two states or multiple states. A state is a discrete operation frequency or speed that a processor attains to consume some fixed power consumption. Static speed scaling is used to solve problems of *Power Down Mechanisms*. Dynamic speed scaling allows the processor to manipulate the entire speed/frequency spectrum. From an algorithmic perspective, dynamic speed scaling is used to solve four main problems<sup>1</sup>. They are as follows.

- Deadline Based Scheduling

- Minimizing Temperature

- Minimizing Flow Time

- (Minimizing) Flow Time Plus Energy

In subsequent sections we briefly go through the above-mentioned problems.

<sup>&</sup>lt;sup>1</sup> There is a problem known as *Makespan Minimization* that is related to deadline based scheduling problem. Although we do not discuss it in this thesis, researchers such as [20] and [59] have solved the problem in single and multiprocessor environments. The *makespan* is the point in time where a schedule ends [3].

Fig. 2.1: Overview of speed scaling problems (an algorithmic perspective)

#### 2.3 PDM (Under Static Speed Scaling) For Single Processors

Power Down Mechanisms (PDM) is an omni present strategy to manage energy in computing devices, for instance we see that laptops switch between *off, sleep* and *awake* states to conserve energy [3]. Also, desktops running operating systems such as Linux *Ubuntu* or Windows *XP*, 7 etc. deactivate their monitor and/or cut off power to some other external peripherals when the computer has been inactive for a while. The idea is to temporarily switch off the computing device through a *sleep* state when (computing) service is expected to resume in the near future or to shut down the device (*off* state) when service is not required any time soon and lastly, to maintain an active or *awake* state when the device is actively computing. In practice, computing devices consume some energy while in *sleep* state because they need to provide power to their Random-access memory which stores the memory settings of an *awake* state prior to the *sleep* state [64]. These states are managed by the operating software of the computing device. The most essential parameter in PDM techniques is the *idleness threshold*, the overhead

time interval required for the computing device to switch from an active state to a sleep state [35].

Power down mechanisms still dominate industry products because they mitigate the (processor's) current leaks that stem from the dynamic switching of processing speed <sup>2</sup> [52]. Power down mechanisms have been thoroughly studied by several researchers; from a stochastic perspective (e.g. [22]), an algorithmic perspective (e.g. [34]) as well as a learning-based perspective (e.g. [29]). Also, concentrated research from industry e.g. *Microsoft's Desktop PC Energy Savings for Enterprises* [50] and *Microsoft's Power Management and Driver Support* through *ACPI (Advanced Configuration and Power Interface Architecture*) [51] thoroughly explore and implement PDM. We refer the reader to an elaborate survey by Irani et al. [35]. In this survey, the authors comprehensively examine PDM under various approaches.

Next, we briefly mention PDM from an algorithmic perspective for two and multiple states<sup>3</sup>.

#### 2.3.1 PDM Problem Scenario

- The computing device can operate in more than one state e.g. *completely off*, *sleep*, *stand by*, *economy* and *performance* states.

- This is an online problem, implying that the computing device is not aware of future states. Also, for a given idle period, the system has no information when the period ends.

- Each state incurs a different power consumption.

- Energy consumption during *power up* (moving from a state of low power consumption to a state of higher power consumption) is substantial.

- Generally, the energy consumption during a *power down* between any two states is assumed to be insignificant.

- The goal is to minimize energy consumption.

$<sup>^{2}</sup>$  We speculate that this may soon change because leakage power is on the rise [38].

<sup>&</sup>lt;sup>3</sup> In subsequent sections, we do not attempt to summarize all the algorithms pertaining to PDM because this thesis falls under *Dynamic Speed Scaling* and not PDM. [3, 34, 35, 37] go over PDM strategies in more scope and depth.

• The challenge is as we attempt to minimize energy consumption through sustaining residency in low states, the system is inactive, but the system needs to attain higher power state(s) to compute [3]. Furthermore, a power up will incur an energy penalty and we are also not aware of future states. It may sometimes not be justifiable to greedily reside in a low power state to save energy, just to be interrupted by a request that will lead to a penalty during a power up.

#### 2.3.2 Competitive Analysis (Relevant to PDM)

- Competitive analysis is conducted to give a guarantee of worse case performance [3].

- In competitive analysis, a given algorithm ALG is compared to its optimal offline counterpart or adversary, OPT [60].

- OPT knows all future events, so it has an advantage to minimize energy through computing an offline state transition schedule [3].

- ALG is considered c-competitive for any input (*idle* periods), ALG's energy consumption is c times that of OPT [3].

#### 2.3.3 PDM for Two States

*Algorithm ALG-D* is a 2 competitive deterministic algorithm that solves the PDM problem for two states [3]. Furthermore, [3] shows that no online deterministic algorithm achieves a competitive ratio lower than 2 for the two state PDM problem.

*Algorithm ALG-R* is a stochastic algorithm that improves on *Algorithm ALG-D* by using a probability density function to transition to the sleep state from the awake state. It was presented by [37] and was shown to achieve a competitive ratio approaching 1.58.

#### 2.3.4 PDM for Multiple States

*Algorithm Lower-Envelope* was proposed by Irani et al. [34]. This is a deterministic algorithm that solves the PDM problem for the multi state scenario. The authors assume that the energy incurred during a power up is additive (not arbitrary) and proved that their

*algorithm is* 2-competitive [3]. Furthermore, [3] asserts that no online deterministic algorithm achieves a competitive ratio lower than 2 for the multi state PDM problem.

#### 2.4 Dynamic Speed Scaling (Single Processors)

Dynamic speed scaling or *dynamic voltage scaling* is the ability of a processor to operate at a variable speed. This is a relatively recent technique to save energy and achieve decent service by manipulating the full spectrum a processor's frequency (speed) [3]. Examples of modern processors that support dynamic speed scaling are the Intel's SpeedStep processor [32], IBM's Power7 processor<sup>4</sup> [31] and the AMD's PowerNow processor<sup>5</sup> [5]. Dynamic Speed scaling has been used as a strategy to reduce energy consumption [2, 4, 6, 7, 33, 68]. It has been used to manage a processor's temperature and energy consumption [12] as well as to mitigate processor heat failure [49]. Some speed scaling algorithms factor both time and energy consumption of tasks [1, 6, 11, 68]. Under dynamic speed scaling, the energy consumption of a processor is commonly assumed to grow in proportion to  $s^{\alpha}$  where s is the processor speed and  $\alpha$  is a constant > 1 (e.g. [1, 4, 6, 7, 19, 25, 68]). This implies that a high processing speed leads to a fast execution, but unfortunately incurs a high energy consumption. Note that the well known cube-root rule e.g., as suggested by [3, 43] is that  $\alpha = 3$  for a CMOS based processor<sup>6</sup>. The cube-root rule stems from the modeling of dynamic power in CMOS chips. According to [38], it is modeled as being proportional to  $cv^2 f$ , where c is the processor's capacitance, v is the voltage supplied and f is the frequency; but at high frequencies  $f \propto v$ . Surprisingly, Wierman et al. [63] carried out experiments to show that in today's CMOS based computing devices  $\alpha$  is close to quadratic (i.e. they found out that a calibration of  $\alpha = 1.8$  is more accurate). We speculate that this discrepancy in  $\alpha$ is due to an improvement in technology. Anyhow, In the algorithmic literature pertaining

Abbreviations:

<sup>&</sup>lt;sup>4</sup> IBM- International Business Machines Corporation.

<sup>&</sup>lt;sup>5</sup> AMD - Advanced Micro Devices (Technology Company).

<sup>&</sup>lt;sup>6</sup> CMOS - Complementary Metal Oxide Semiconductor.

to dynamic speed scaling, most researchers use a general  $\alpha \in (1,3]$  and some assume the cube-root rule ( $\alpha = 3$ ).

Under the single processor scenario, dynamic speed scaling gives rise to a variety of challenging problems because the scheduler needs to decide on the job/task to execute as well as the speed of processing [3]. Generally, this is more complicated in the multiprocessor environment and is even more challenging when processors are heterogeneous [28]. Typically, from an algorithmic perspective, we have four main problem categorizations that fall under dynamic speed scaling, they are: Deadline Based Scheduling, Minimizing Temperature, Minimizing Flow Time and Minimizing Flow Time Plus Energy. We briefly cover these problems in subsequent sections, but first we briefly touch on competitive analysis in application to dynamic speed scaling.

#### 2.4.1 Competitive Analysis (Relevant to Dynamic Speed Scaling)

From an algorithmic perspective, the *offline* setting is defined in literature as the scenario where we have advance knowledge of jobs/tasks [3]. The online setting is when we have to make scheduling decisions in real time without any advance knowledge of jobs, i.e. we learn about jobs when as they arrive. Online strategies, just like in PDM, are assessed using competitive analysis [3]. An Online dynamic speed scaling algorithm (*ALG*) is considered c-competitive if for every input, ALG's objective function (usually energy, but could be both energy and response time or some other performance criteria) is c times that of the optimal offline solution/adversary [3].

#### **2.5 Deadline Based Scheduling (Single Processor)**

The study of energy-efficient speed-scaled scheduling was initiated in 1995 by Yao et al. [68]. They considered the deadline-based scheduling of a single processor where the jobs need to complete by their given deadlines. Using dynamic speed scaling, the goal was to construct a schedule that minimizes energy consumption. Yao et al.s' deadline based scheduling framework has been the most extensively studied framework in the context of dynamic speed scaling algorithms [3].

# 2.5.1 Overview of Yao et al's Framework, Algorithms and Related Extensions for Single Processor Systems.

Yao et al. [68] considered scheduling a sequence of tasks on a single variable speed processor (The processor is unbound in the sense that it has no maximum processing rate). Each task has a required deadline, release time and processing volume (analogous to the number of CPU cycles required to execute a task). They allow **preemption**, where a task is allowed to resume on the same processor after being interrupted<sup>7</sup>. They proposed an optimal offline algorithm<sup>8</sup> (YDS) to solve the task scheduling problem in polynomial time via iterations. A direct implementation of the YDS algorithm has a computational complexity of  $O(n^3)$ , where *n* is the number of jobs [3]. Li et al. [46] illustrate an alternative implementation of YDS with an improved computational complexity of  $O(n^2 \log n)$  based on finding successive approximations of the optimal schedule. Furthermore, when the processor is assumed to have a *d* number of discrete voltage/speed levels, Li and Yao [47] propose an algorithm that improves the computational complexity of the offline YDS algorithm to  $O(dn \log n)$ .

In the same work, Yao et al. further introduced two online algorithms, namely, Optimum *Available (OA)* and *Average Rate (AR)*. They proved that AR has an energy competitive ratio<sup>9</sup> of  $(2\alpha)^{\alpha}/2$ . Bansal, Kimbrel and Pruhs [12] worked on OA and proved it to have an energy competitive ratio of exactly  $\alpha^{\alpha}$ . Bansal et al. [13] present an online algorithm<sup>10</sup> (*BKP*) which sort of approximates the speeds of YDS in real time [3]. In the same work,

<sup>&</sup>lt;sup>7</sup> The YDS algorithm makes use of a **preemptive** service discipline, *Earliest Deadline First (EDF)* service policy. Among the unfinished Jobs, this well-known service policy gives priority to jobs with the earliest deadline.

<sup>&</sup>lt;sup>8</sup> YDS - Yao, Demers, Shenker.

<sup>&</sup>lt;sup>9</sup> Recall that  $\alpha$  is the exponent of a processor's power function ( $s^{\alpha}$ ), where s is the processor's speed and  $\alpha$  is a constant > 1.

<sup>&</sup>lt;sup>10</sup> BKP- Bansal, Kimbrel and Pruhs.

Bansal et al. proved that their BKP algorithm achieves an energy competitive ratio that is better than *Optimal Available* for large  $\alpha$  values<sup>11</sup>, i.e. for  $\alpha \ge 5$ .

## 2.5.2 Deadline Based Scheduling Under Maximum Processing Rate Constraints (Single Processor)

Under a constrained processing rate, a summary of the extended deadline based problem and results are as follows.

- The processor is scalable between a speed of zero and some maximum speed *T*.

- The constrained maximum processing rate of *T* potentially compromises the ability to find a feasible schedule.

- The revised objective is to maximize *throughput* i.e., the total processing volume of tasks that are successfully completed by their deadline.

- [11] give an online algorithm that is constant competitive for the energy consumed and is 4-competitive for throughput.

- [71] present an online constant competitive algorithm on both throughput and energy consumption<sup>12</sup>.

What we have mentioned so far is not an exhaustive summary of all work related to deadline based scheduling in the context of dynamic speed scaling. For such work, see a survey paper by Albers [3]. Next, we move over to other dynamic speed scaling problems.

## 2.6 Minimizing Temperature (Single Processor)

Bansal et al. [13] initiate the study of using dynamic speed scaling to manage temperature, more specifically to simultaneously meet the objectives of maximizing temperature and minimizing energy consumption. These two objectives conflict because processors with high temperature incur high energy consumption. They assume the ambient environment temperature is fixed and the computing device cools according to Isaac Newton's law of

<sup>&</sup>lt;sup>11</sup> The practical significance of this result is questionable since in conventional processors,  $\alpha \in (1,3]$ .

<sup>&</sup>lt;sup>12</sup> [71] was the first to introduce the constrained speed model, where the speed is bounded from zero to T.