#### Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2013

# Rapid And Efficient Multi Objective Design Space Exploration Methods In High Level Synthesis Of Computation Intensive Applications

Anirban Sengupta Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Sengupta, Anirban, "Rapid And Efficient Multi Objective Design Space Exploration Methods In High Level Synthesis Of Computation Intensive Applications" (2013). *Theses and dissertations*. Paper 1631.

This Dissertation is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

## RAPID AND EFFICIENT MULTI OBJECTIVE DESIGN SPACE EXPLORATION METHODS IN HIGH LEVEL SYNTHESIS OF COMPUTATION INTENSIVE APPLICATIONS

By

Anirban Sengupta

Master of Applied Science

Electrical and Computer Engineering

Ryerson University, Toronto, Canada, 2010

Bachelor of Technology

**Electronics and Communication Engineering**

West Bengal University of Technology, Kolkata, India, 2008

A dissertation

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2013

©Anirban Sengupta 2013

## **Author's Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the dissertation, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis or dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis or dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the public.

\* Signature

Anirban Sengupta

### ABSTRACT

Title of Dissertation:

### RAPID AND EFFICIENT MULTI OBJECTIVE DESIGN SPACE EXPLORATION METHODS IN HIGH LEVEL SYNTHESIS OF COMPUTATION INTENSIVE APPLICATIONS

**Dissertation Submitted By:**

### Anirban Sengupta, Doctor of Philosophy, 2013 Electrical and Computer Engineering Department, Ryerson University, Canada

**Dissertation Directed By:**

Dr. Reza Sedaghat

#### Electrical and Computer Engineering Department, Ryerson University, Canada

Design Space Exploration (DSE) is an indispensable segment of the High Level Synthesis (HLS) design process. Moreover, the enormous increase in complexity of the recent Very Large Scale Integration (VLSI) circuits has only been possible due to use of advanced DSE techniques during HLS process. This dissertation presents four automated optimization algorithms and methodologies that are capable to handle various multi-objective problems during design space exploration and high level synthesis of computation intensive applications. Algorithmic solutions to four different branches of DSE problems have been proposed in this dissertation viz. a) Solution to power-performance-area/cost trade-off of Digital Signal Processing (DSP) kernels using priority factor process which also includes deriving analytical mathematical model for modern performance-area tradeoff of DSP kernels using hybridization of fuzzy algorithm and

vector design space technique with Self-Correction Scheme c) Solution to dual parametric optimization using efficient multi structure genetic algorithm for integrated scheduling and allocation and d) Solution to control step bound static power optimization using power gradient methodology for integrated scheduling and allocation. Some techniques proposed are equipped with pipelined execution time parameter (based on need), in addition to hardware area, power and cost depending on the user's objective for exploration of a final solution in a short time. In addition to architecture exploration capability, rapid automated circuit generation of DSP kernels is also possible in a short time for verification and synthesis in Field Programmable Gate Array (FPGA) platforms. The proposed exploration approaches are applied to custom data intensive applications (application specific processors/custom processors) or standalone Application Specific Integrated Circuits (ASIC's). Results of the experiments for proposed approaches on all the standard DSP benchmarks have indicated improvements either in terms of exploration runtime, quality of final solution, reduced execution time, power and area or a multiple combination of all factors when compared to recent approaches.

### Acknowledgement

I would like to thank my supervisor, Dr. Reza Sedaghat for his thoughtful guidance and advice as well as OPR-AL members for their endless support. Further, I am also thankful to my supervisor for providing me all the necessary support and required amenities to help me perform my incessant research for all the past years.

I am highly indebted to my parents for their great guidance and sacrifice all throughout my life. Further I highly owe them for being a constant source of love and motivation throughout my life, particularly in times of hardships and difficulty. They have always been a source of true guide inducing the feeling of eternal divine power in me.

Moreover I am highly obliged to my grandparents for continuously supporting me and inspiring me to always do better than before. I deeply express my gratitude for their eternal blessings.

I am also very thankful to my friends, who helped me in tough times and provided me with encouraging words to accomplish my goals.

## **Table of Contents**

| Abstract     | i                                                                           | ii   |

|--------------|-----------------------------------------------------------------------------|------|

| Acknowled    | gement                                                                      | ٠v   |

| Table of Co  | ntentsv                                                                     | /i   |

| List of Tabl | es                                                                          | ix   |

| List of Figu | res                                                                         | ·xi  |

| Nomenclatu   | ıre                                                                         | xiii |

| Chapter 1    | Introduction                                                                | -1   |

| 1.1          | Overview                                                                    | -1   |

| 1.2          | Fundamentals on Modular System Design                                       | -3   |

| 1.3          | Related Work                                                                | -4   |

| 1.4          | Background Information                                                      | 7    |

| 1.5          | Summary of Contribution                                                     | -12  |

| 1.6          | Organization of Dissertation                                                | 14   |

| Chapter 2    | Rapid Design Space Exploration in High Level Synthesis Based on Po          | wer- |

| Performan    | ce Tradeoff using Priority Factor Metric                                    | 16   |

| 2.1 1        | Mathematical Derivation for Cost/Area Model                                 | -17  |

| 2.2 1        | Mathematical Derivation for Execution Time Model                            | 20   |

| 2.3 1        | Mathematical Model for Power Consumption                                    | -23  |

| 2.4 P        | Proposed Method of Design Space Exploration of Architecture Based on Power- |      |

|              | Performance tradeoff with area/cost a as optimization criteria              | -24  |

3.1 The Proposed Theory for Fuzzy Search during Design Space Exploration------32

3.2 The Steps Needed to Obtain the Final Variant of Architecture-------38

| Chapter 4 Priority Function Driven Design Space Exploration in High Level | Synthesis |

|---------------------------------------------------------------------------|-----------|

| Based on Power Gradient Technique                                         | 53        |

| 4.1 The Proposed Exploration Approach                                     | 54        |

| 4.2 Demonstration of the proposed approach                                | 56        |

| Chapter 5 A Multi Structure Genetic Algorithm for Integrated Design Space Explo | ration |

|---------------------------------------------------------------------------------|--------|

| of Scheduling and Allocation in High Level Synthesis for DSP Kernels            | 61     |

| 5.1 The Proposed Framework Using MSGA                                           | 63     |

| 5.2. Description of the Proposed MSGA steps                                     | 68     |

| Chapter 6 Fast      | Multi-Objective     | Exploration     | and RTL       | Circuit | Generation | using |

|---------------------|---------------------|-----------------|---------------|---------|------------|-------|

| Architecture Synthe | esis Platform: Exp  | ploration Synth | hesizer       |         |            | 82    |

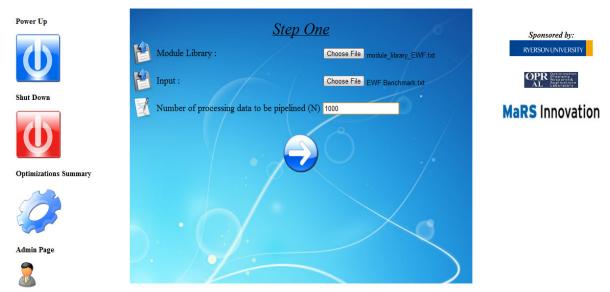

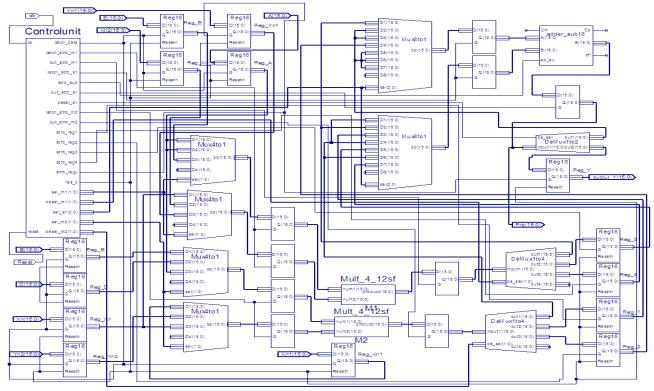

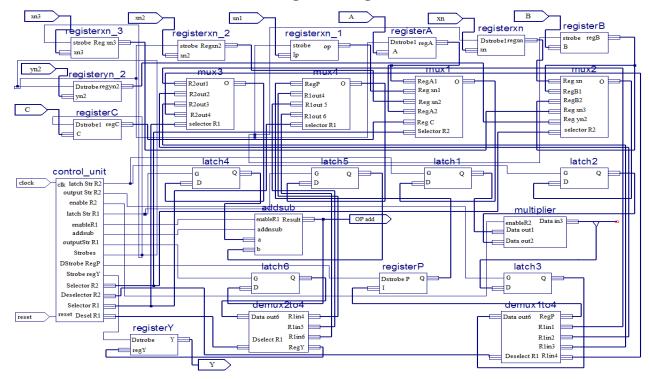

| 6.1 The Prope       | osed Exploration S  | ynthesizer Desi | ign Flow      |         |            | 83    |

| 6.2 Keystone        | s of the Proposed E | Exploration Syn | thesizer Plat | form    |            | 86    |

| 6.3 Input Form      | nat and Intermediat | e Representatio | )n            |         |            | 87    |

| 6.4 Output Det      | tails of the Tool   |                 |               |         |            | 88    |

| Chapter 7 Implementation, Results and Analysis | 90 |

|------------------------------------------------|----|

|------------------------------------------------|----|

- 7.1 Experimental results: The Proposed Approach 'Rapid Design Space Exploration in High Level Synthesis Based on Power-Performance Tradeoff using Priority Factor Metric' and comparison with recent approach ------91

- 7.2 Experimental results: The Proposed Approach 'Rapid Design Space Exploration in High Level Synthesis Based on Area-Performance and power-performance Tradeoff using Hybrid Fuzzified Algorithm' and performance comparison ---95

- 7.3 Experimental results: The Proposed Approach 'Priority Function Driven Design Space Exploration in High Level Synthesis Based on Power Gradient Technique' and comparison with recent approach-----102

- 7.4 Experimental results: The Proposed Approach 'A Multi Structure Genetic Algorithm for Integrated Design Space Exploration of Scheduling and Allocation in High Level Synthesis for DSP Kernels' and comparison with recent approach ------105

| Cha | oter 8 | Conclusion | and Future  | work | ;] | 108 |

|-----|--------|------------|-------------|------|----|-----|

| Unu |        | Conclusion | and I uture |      |    | 100 |

| lblications111 |

|----------------|

|----------------|

| References123 |

|---------------|

|---------------|

## **List of Tables**

| Table 1  | System Specifications and Constraints for PF Method26                     |

|----------|---------------------------------------------------------------------------|

| Table 2  | System Specifications for hybrid fuzzy approach40                         |

| Table 3  | Variants obtained for area after applying fuzzy search on the arranged    |

|          | design space48                                                            |

| Table 4  | Variants obtained for execution time after applying fuzzy search on the   |

|          | arranged design space51                                                   |

| Table 5  | Portion of Module Library for MSGA77                                      |

| Table 6  | Data Extracted from the integrated solution of offspring 178              |

| Table 7  | Experimental results of comparison between proposed PF approach and       |

|          | recent GA approach94                                                      |

| Table 8  | Experimental results of comparison between the proposed hybrid Fuzzified  |

|          | DSE for Area-Performance trade-off with Power as optimization criteria    |

|          | with the current approach for large benchmarks97                          |

| Table 9  | Experimental results of comparison between the proposed hybrid Fuzzified  |

|          | DSE for Area-Performance trade-off with Power as optimization criteria    |

|          | with GA based current approach98                                          |

| Table 10 | Experimental results of the proposed hybrid Fuzzified approach for Power- |

|          | Performance trade-off with Area as optimization criteria compared with    |

|          | exhaustive analysis for Benchmarks100                                     |

| Table 11 | Experimental results of the comparison between the proposed DSE for     |

|----------|-------------------------------------------------------------------------|

|          | Power-Performance trade-off with Area as optimization criteria with the |

|          | recent approach101                                                      |

| Table 12 | Experimental Results of the proposed Iterative Power Gradient approach  |

|          | for the DSP Benchmarks102                                               |

| Table 13 | Comparison of measured power consumption through Xilinx Power           |

|          | Analyzer (XPA) 9.2i103                                                  |

| Table 14 | Experimental Results of the comparison between the proposed Iterative   |

|          | Power Gradient and recent approach104                                   |

| Table 15 | Experimental Setup for MSGA105                                          |

| Table 16 | Experimental Results of Comparison of MSGA with recent approach106      |

## **List of Figures**

| Figure 1  | Generic Overview of the Proposed PF Exploration Method26                      |

|-----------|-------------------------------------------------------------------------------|

| Figure 2  | Flow chart model of the proposed algorithm27                                  |

| Figure 3  | The arranged design space for execution time parameter29                      |

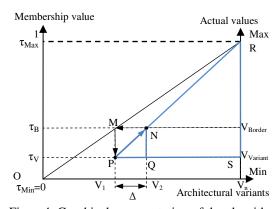

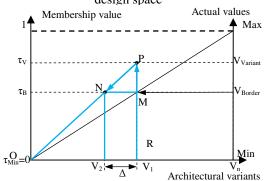

| Figure 4  | Graphical representation of the algorithm for area/power for searching a      |

|           | greater value in the design space35                                           |

| Figure 5  | Graphical representation of the algorithm for execution time for searching a  |

|           | greater value in the design space35                                           |

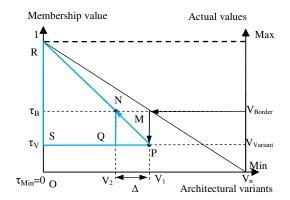

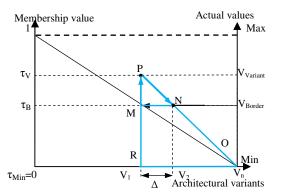

| Figure 6  | Graphical representation of the algorithm for area/power for searching a      |

|           | lesser value in the design space35                                            |

| Figure 7  | Graphical representation of the algorithm for execution time for searching a  |

|           | lesser value in the design space35                                            |

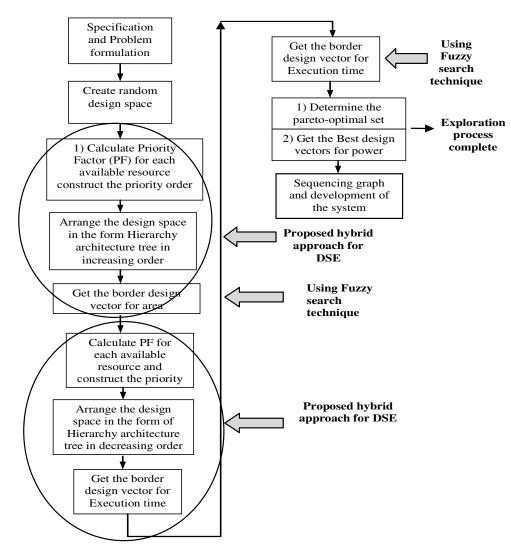

| Figure 8  | The flow for the steps required to obtain the optimal variant of architecture |

|           | using the proposed Hybrid DSE39                                               |

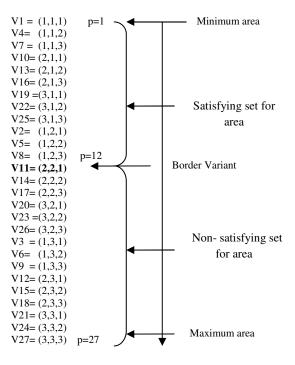

| Figure 9  | Design space with all possible resource combinations45                        |

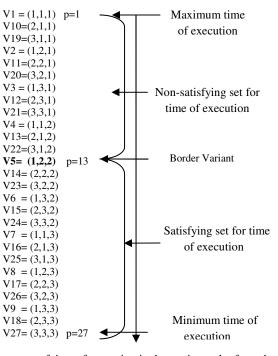

| Figure 10 | Arranged Vector Design Space for area48                                       |

| Figure 11 | Arranged Vector Design Space for execution time50                             |

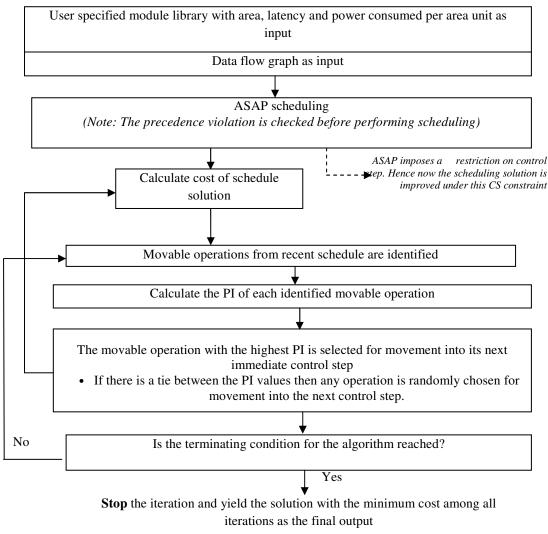

| Figure 12 | Overview of the proposed heuristic approach55                                 |

| Figure 13 | Details of the proposed heuristic Exploration approach57                      |

| Figure 14 | ASAP scheduling of DWT benchmark58                                            |

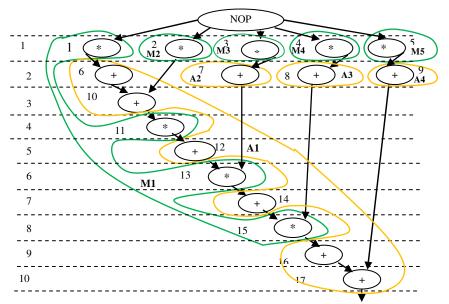

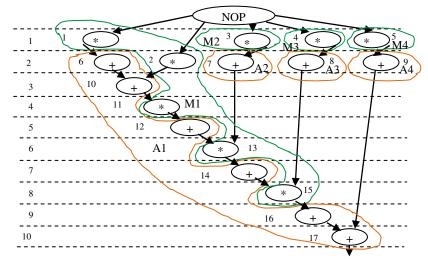

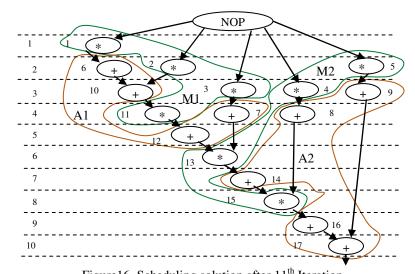

| Figure 15 | Scheduling after 1 <sup>st</sup> Iteration59                                  |

| Figure 16 | Scheduling solution after 11th Iteration60                                    |

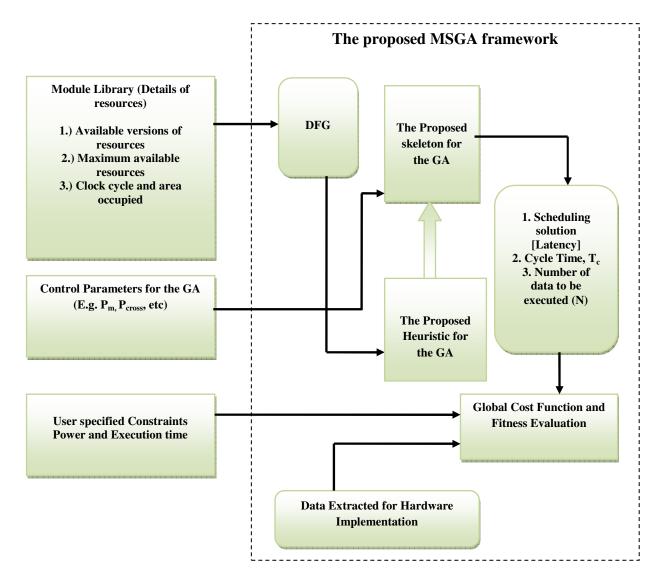

| Figure 17 | MSGA design space exploration approach overview64                             |

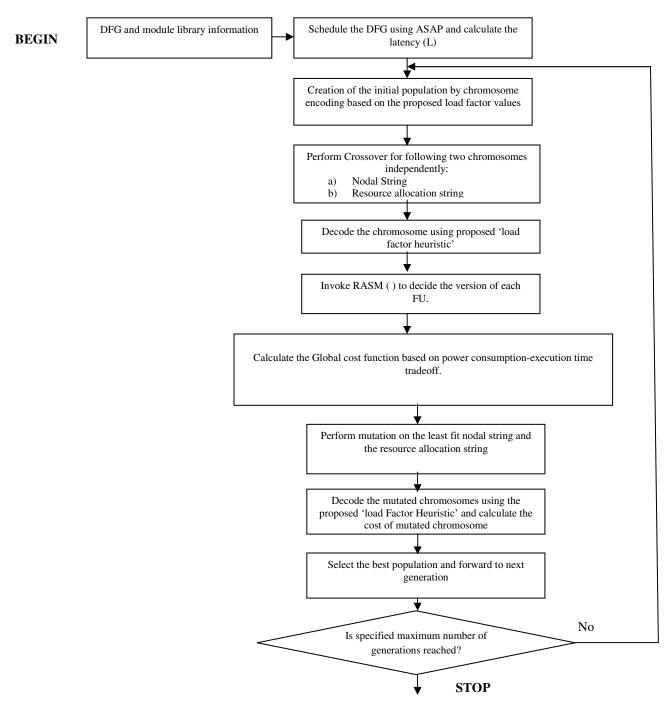

| Figure 18 | Flow chart of the proposed MSGA65                                                                             |

|-----------|---------------------------------------------------------------------------------------------------------------|

| Figure 19 | The perturbation algorithm for resource67                                                                     |

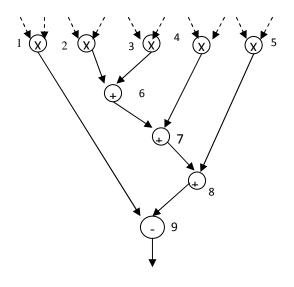

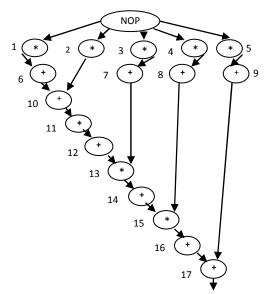

| Figure 20 | DFG of the IIR Digital Filter68                                                                               |

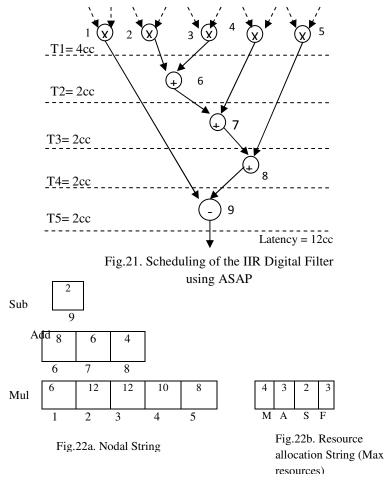

| Figure 21 | Scheduling of the IIR Digital Filter using ASAP70                                                             |

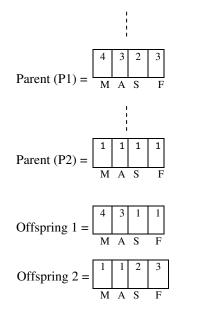

| Figure 22 | Chromosome Encoding for the first parent (P1)70                                                               |

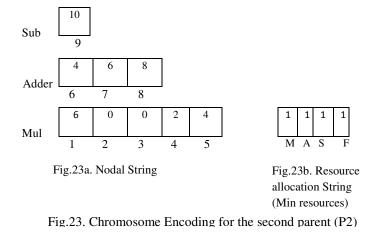

| Figure 23 | Chromosome Encoding for the second parent (P2)70                                                              |

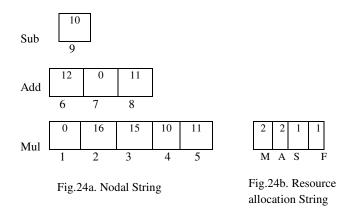

| Figure 24 | Chromosome Encoding for the third parent (P3)71                                                               |

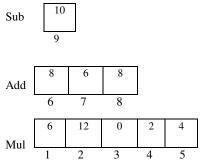

| Figure 25 | Offspring 1 obtained for the nodal string obtained after crossover between P1 and P272                        |

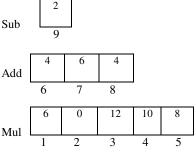

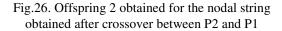

| Figure 26 | Offspring 2 obtained for the nodal string obtained after crossover between P1 and P272                        |

| Figure 27 | Offspring 1 and Offspring 273                                                                                 |

| Figure 28 | Mutation algorithm for the proposed approach74                                                                |

| Figure 29 | Proposed load-factor heuristic for the MSGA Framework76                                                       |

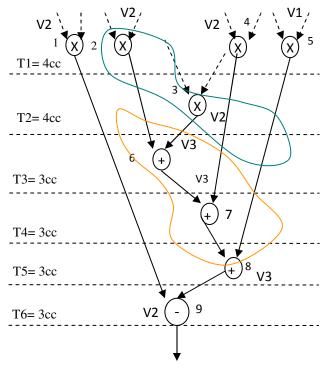

| Figure 30 | Integrated solution to offspring 1 (Decoding of the chromosome) for the IIR<br>Digital Filter benchmark77     |

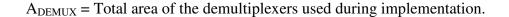

| Figure 31 | Cycle time calculation during data pipelining for offspring 180                                               |

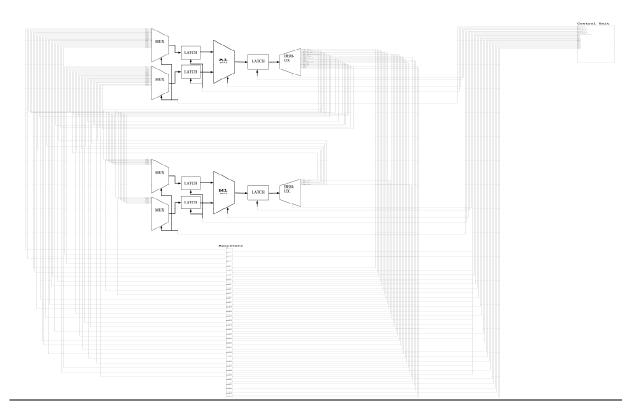

| Figure 32 | Design Flow of the proposed Exploration Synthesizer platform84                                                |

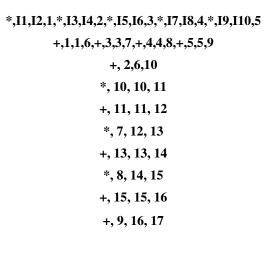

| Figure 33 | DFG of the DWT Benchmark88                                                                                    |

| Figure 34 | Application library: The intermediate representation of DWT DFG which acts as the input format for the tool88 |

## Nomenclature

| Α                       | Total Area of the resources                                           |

|-------------------------|-----------------------------------------------------------------------|

|                         | The recourses evailable for system designing                          |

| R <sub>i</sub>          | The resources available for system designing                          |

| _                       | The clock oscillator used as a resource providing the necessary clock |

| <b>R</b> <sub>clk</sub> | frequency to the system                                               |

| N <sub>Ri</sub>         | The number of resource R <sub>i</sub>                                 |

| K <sub>Ri</sub>         | The area occupied per unit resource 'Ri'                              |

| n                       | Functional resources                                                  |

| L                       | Latency of scheduling an application                                  |

| T <sub>c</sub>          | Cycle time of execution                                               |

| N (D)                   | Number of data elements to be processed                               |

| T <sub>Ri</sub>         | Number of clock cycles needed by resource 'Ri'                        |

| T <sub>p</sub>          | Time period of the clock                                              |

| Pc                      | Power consumption per area unit at particular frequency               |

| H (z)                   | The transfer function of the filter in the frequency domain           |

| р                       | Position where the variant is located in the design space             |

| i                       | An index                                                              |

| P optimal               | The constraint for Power Consumption                                  |

| T <sub>optimal</sub>    | The constraint for Execution Time                                     |

| V <sub>Ri</sub>         | Number of variants of resource 'Ri'                                   |

| Р                       | Total power consumption                                               |

| T <sub>exe</sub>        | Total execution time                                                  |

| М                       | Each Performance Parameter                                            |

| N <sub>RM</sub>      | Number of memory elements present (such as registers)                                                          |

|----------------------|----------------------------------------------------------------------------------------------------------------|

| C <sub>R</sub>       | Total cost of all resources                                                                                    |

| C <sub>Ri</sub>      | Cost per area unit of the resource (such as adders, multipliers)                                               |

| C <sub>Rclk</sub>    | Cost per area unit of the clock oscillator                                                                     |

| C <sub>RM</sub>      | Cost per area unit of memory element                                                                           |

| W                    | Total workload of all the resources                                                                            |

| X                    | position of the variant in the set                                                                             |

| τ                    | approximated membership value of the variant which is the x <sup>th</sup> element<br>in the sorted arrangement |

| α                    | order of the first element                                                                                     |

| β                    | order of the last element                                                                                      |

| τ <sub>B</sub>       | membership value of the border variant for the parameter in the space.                                         |

| $	au_{ m V}$         | membership value for the variant under test                                                                    |

| Vvariant             | Respective value of variant under test for a parameter                                                         |

| $	au_{\mathrm{Min}}$ | membership values of the minimum variants in the architecture space                                            |

| $	au_{Max}$          | membership values of the maximum variants in the architecture space                                            |

| VBorde               | actual border variant value                                                                                    |

| $	au_{ m ini}$       | calculated initial membership value                                                                            |

| $	au_{max}$          | Maximum membership value (equals to '1') corresponding to the fuzzy logic membership value rule                |

| $	au_{ m min}$       | Minimum membership value (equals to '0') corresponding to the fuzzy logic membership value rule                |

| G                    | Power Gradient                                                                                                 |

| O (i)                | Operation of a schedule                                                                                        |

| CS                   | Control step of a schedule                                                                                     |

| PI                 | Priority Indicator                                                                |

|--------------------|-----------------------------------------------------------------------------------|

| P <sub>T</sub>     | Power consumption due to dissipation of leakage current                           |

| ps                 | power dissipated per area unit when the transistors in the chip are not switching |

| L <sup>ASAP</sup>  | ASAP scheduling with maximum resource                                             |

| load factor (a)    | Load factor or workload of each resource                                          |

| β                  | Encoded value of each operation (oi) of the second parent chromosome              |

| μ                  | Random value equal or between ' $\alpha$ ' and ' $\beta$ '                        |

| W1, W2             | Tuning factor/Weightage factor                                                    |

| CL                 | Local cost function                                                               |

| Pcross             | Crossover probability                                                             |

| vn                 | Version of the each type of resources used                                        |

| C <sub>G</sub>     | Global cost function                                                              |

| A <sub>FU</sub>    | Total area of the functional units.                                               |

| T <sub>CONS</sub>  | Execution time constraint specified by user during genetic algorithm              |

| T <sub>MAX</sub>   | Max execution time taken by a solution during the specific generation             |

| A <sub>FU</sub>    | Total area of the functional units                                                |

| A <sub>REG</sub>   | Total area of registers                                                           |

| A <sub>MUX</sub>   | Total area of registers                                                           |

| A <sub>DEMUX</sub> | Total area of the demultiplexers used during implementation                       |

| P <sub>CONS</sub>  | Power consumption constraint specified by the user                                |

| P <sub>MAX</sub>   | Max power consumption of a solution during a specific generation                  |

| G(Max)             | Maximum generation of an algorithm                                                |

# Chapter 1 Introduction

#### **1.1 Overview**

The never ending increase in the growth of chip complexity has only been possible due to efficient scheduling and exploration techniques. The growth in chip capacity has enabled processing of huge amounts of data with greater flexibility and less expense. This requirement to yield high performance with a concurrent balance in power expenditure is often a primary specification in the area of Digital Signal Processing (DSP), communications and network processing. For e.g., Application Specific Processor cores are increasingly being used to simultaneously address the need for high performance, low area, minimum cost and timely operation in many embedded systems. Particularly elements used in mobile phones, such as the DSP cores, must be low cost and consume less power than their general purpose counterparts. Hence, exploration of an optimized solution that has the capability to encounter conflicting conditions such as minimizing the speed of the exploration process and maximizing the quality of the scheduling solution by limiting power expenditure at minimal control step (time) usage is extremely significant for the development of computation intensive DSP cores [1][2][3].

Moreover, the complicated process of exploration of the final scheduling solution also requires a tradeoff between the contradictory parameters of power and latency/performance in addition to the contradictory demands [1][3].

A DSE problem therefore considers two orthogonal issues: (a) how can a single design point be evaluated? (b) How can the design space be covered during the exploration process? The latter issue arises since an exhaustive exploration of the design space, including evaluating every possible design point, is usually prohibitive due to the sheer size of the design space. Therefore, trade-offs linked to the choice of appropriate evaluation and coverage methods are discussed. The designer must balance: the accuracy of the evaluation, the time it takes to evaluate one design point (including the implementation of the evaluation model), the precision/granularity of the design space coverage, as well as the possibilities for automating the exploration process.

Multi-objective algorithms could use combined objectives in order to reduce the number of dimensions to the problem. For example, it could make sense to only consider the speed-cost and the flexibility-cost ratios for a certain design and not speed, cost, and flexibility as separate optimization goals. One of the most prevalent combined objectives is energy-delay product. The energy-delay product is used to assess embedded systems. The delay-power ratio objective can be interpreted as a computational clock cycles versus power dissipated. The combined speed-cost ratio objective represents a computational complexity related to the costs of the design. It should be noted that there are also optimizer-specific metrics that guide the search, such as the steepness to surrounding solutions in the case of hill climbing or the number of dominated solutions in the case of some multi-objective, evolutionary algorithms. Hill climbing, for instance, evaluates the neighborhood of the current design to determine the next steepest step towards the optimization goal. In order to avoid being trapped on top of a local maximum, hill climbing requires backtracking mechanisms which might be expensive in "bumpy terrains". Moreover, the search becomes aimless on plains and is not able to recognize diagonal ridges since the probe directions would always lead to lower quality solutions [1][2][4]. The proposed method has a tendency to yield high quality solutions (which obeys multi parametric optimization requirement) due to its unique algorithmic and framework features. It also manages to balance the tradeoff proficiently between exploring a high quality solution and the runtime taken.

#### **1.2 Fundamentals on Modular System Design**

The design and development of modular systems with heterogeneous performance optimization objective requires extensive analysis and assessment of the design space, not only due to the assorted nature of the parameters, but also due to the diversity in architecture for implementation. Given the specifications and the system requirements the aim of designers is to reduce the large and complex design space into a set of feasible design solutions meeting performance objectives and functionality. For most modular systems and systems based on strict operational constraints the selection of the optimal architecture for system design is the most important step in the development process. Design space architecture can have innumerable design options for selection and implementation based on the parameters of optimization. Hence selection of the optimal architecture from the design space which satisfies all the performance objectives is crucial for the present generation of System-on-chip (SoC) designs [5, 6]. As it is always possible to implement different functions of a system on different hardware components, the architecture design space has become more complex to analyze. In the case of high level synthesis, performing design space exploration to choose the best candidate architecture by concurrently satisfying many operating constraints and optimization parameters is considered the most important stage in the whole design flow (details on design space exploration is provided later). The method for exploration of the best candidate architecture should not only be less in terms of complexity factor and time but should also explore the variant in an efficient way meeting all the specifications provided. The process of high level synthesis design is very complicated and descriptive and is usually performed by system architects. Depending on the application, the process of defining the problem, performing design space exploration and the other steps required for its successful accomplishment are very time consuming. Furthermore, recent advancements in areas of communications and multimedia have led to the growth of a wide array of applications requiring huge data processing at minimal power expense. Such data hungry applications demand satisfactory performance with power efficient hardware solutions. Since the selection process for the best design architecture is complex, an efficient approach to explore the design space for selecting the best design option is needed [1,2,3,4].

#### **1.3 Related Works**

An engineering problem can generally be described as a phenomenon of analyzing and managing the tradeoffs between contradictory design objectives. The problem of obtaining a comprehensive Pareto optimal set [42-46] has been addressed by few researchers. In [7] the researchers proposed an approach for synthesis of heterogeneous embedded systems by using Pareto Front Arithmetic (PFA) to explore the giant search spaces. Their method utilized the hierarchical problem structure for exploring the set of Pareto optimal solutions. Similar problem was also addressed in [8] by suggesting order of efficiency, which assists in deciding preferences amongst the different Pareto optimal points. Work in [9] suggested the identification of a few

superior design points from the Pareto set is enough for an excellent design process. In [10] evolutionary algorithms such as the Genetic Algorithm (GA) had been suggested to yield better results for the design space exploration process. The use of GA had also been suggested as a framework for DSE of data paths in high level synthesis in [11]. Another approach was introduced by researchers in [12] which were based on Pareto optimal analysis. According to their work, the design space was arranged in the form of an Architecture Configuration Graph (ACG) for architecture variant analysis and optimization of performance parameters. Their results proved quite promising for architectural synthesis of digital systems. Furthermore in [13] and [14], authors described another approach for DSE in high level systems based on binary encoding of the chromosomes. Work shown in [15] for DSE suggests that authors used an evolutionary algorithm for successful evaluation of the design for an application specific SoC. The work shown in [16] discusses the optimization of area, delay and power in behavioral synthesis, but does not focus on the high level design flow with multi parametric optimization objective. Authors in [17] introduce a tool called SystemCoDesigner that offers rapid design space exploration with rapid prototyping of behavioral systemC models. In [17] an automated integration was done by integrating behavioral synthesis into the proposed design flow. Authors in [18] have proposed a power optimization in SoC data flow systems. Although the proposed optimization yielded significant results, the focus of their work was not on control time constrained scheduling but rather power optimization hardware during exploration. Authors in [19] describe current state-of-the-art high-level synthesis techniques for dynamically reconfigurable systems. In addition to above, authors in [20] have applied GA to the binding and allocation phase. The authors have introduced an unconventional crossover technique depending on a force directed data path binding completion algorithm. One of the key features of their approach is the use of multiport memories. Its main drawback is that it accepts as input the scheduled data flow graph, thus is unable to handle the scheduling problem. Authors in [21] presented a time constrained scheduling based on the GA. A list decoder is used to decode chromosome encoding by permutation of operations, into a valid schedule. Although the method is promising, it is slow compared to the other GA approaches. In addition, authors in [22] have proposed a problem space genetic algorithm for design space exploration of data paths. They have used the concept of heuristic/problem pair to convert a data flow graph [23] into a valid schedule. Another class of scheduling algorithms presented previously includes constructive approaches such as As Soon As Possible (ASAP) [5], As Late As Possible (ALAP) [23], list scheduling [24] and Force Directed scheduling [25]. These approaches are very simple and fast in nature. These algorithms all suffer from inherent tendency to optimize one parameter at the expense of other. Moreover, non-consideration of multiple user objective and implementation runtime dilutes its ability to be used in the fore front of modern performance driven designing process. Additionally, the tradeoffs performed using above methods which tends to engulf high exploration/optimization runtime. Moreover, the execution time parameter is not taken into account during exploration where needed but only delay. For the modern generation of hardware systems, deficiency of pipelining provision (by considering only delay) is extremely fatal for efficiency enhancement. Hence, the thesis eliminates the deadlock associated with these techniques. Also in many cases, the optimization factor and performance goal of the user may completely change depending upon his design requirement. For example, besides the multiple user criteria viz. (a) Accelerated power-performance tradeoff with area/cost as minimization criteria (b) Accelerated Area-performance tradeoff with power as minimization criteria, there can be a third type of optimization goal viz. (c) static power optimization under minimum control step usage. Thus, besides being able to tradeoff based on requirement a) and b), an efficient novel optimization methodology must also be available that can address (c) which is equally significant. But unfortunately, to the best of the authors' knowledge, all the approaches so far are deficient in addressing (c). This dissertation develops a novel technique for addressing deficiency in (c).

#### **1.4 Background Information**

#### **1.4.1 Theoretical Background on High Level Synthesis**

Interdependent tasks such as scheduling, allocation and module selection are important ingredients of the high level synthesis design process. High level synthesis is a methodology of transforming an algorithmic behavioral description into an actual Register Transfer Level (RTL) structure. Therefore high level synthesis methodology contains a sequence of tasks to convert the abstract behavioral description of the algorithm into its respective structural block at RT level. The design at the RT level comprises of functional units such as Arithmetic Logic Unit (ALU), storage elements, registers, busses and interconnections. The algorithmic description specifies the inputs and outputs of the behavior of the algorithm in terms of operations to be preformed and data flow. A description of the algorithm is usually represented in the form of an acyclic directed graph known as a sequencing graph. These graphs specify the input/output relation of the algorithm and the data dependency present in the data flow. The graph is defined in terms of its vertices and edges, where the vertices signify the operations and the edges indicate the data dependency present in the function. High level synthesis is therefore a conversion from the abstract behavioral description to its respective hardware description in the form of Arithmetic Logic Units (ALU), memory elements, storage units, multiplexers/demultiplexers and the

necessary interconnections. The transformed algorithm at the RT level is comprised of a control unit and the data path unit. High level synthesis offers many advantages, such as productivity gains and efficient design space exploration [51-60]. Performing DSE at a higher level of abstraction provides more dividend than at lower levels of abstraction, i.e. transistor level or logic level. Traditional high level synthesis design methodology is much simpler than modern design techniques. In general, the initial step of synthesis is to compile the behavioral specification into an internal representation. The next step is to apply high level transformation techniques with the aim of optimizing the behavior as per the desired performance. In order to realize the structure, the final step is to perform scheduling to determine the time at which each operation is executed and the allocation, which is synthesizing the necessary hardware to perform the operations [5].

Scheduling can be of two different classes: time constrained scheduling and resource constrained scheduling. Time constrained scheduling refers to finding the minimum cost schedule that satisfies the given set of constraints with the given maximum number of control steps. Resource constraint scheduling, on the other hand, refers to finding the fastest possible schedule that satisfies the given set of constraints with the given maximum number of resources. Resource constraints are generally specified by the area occupied by the functional units like adders/subtractors, multipliers, dividers and ALUs. Although the data path of the system consists of registers and interconnections, they are not considered to be included as resource constrained because they are difficult to specify. High level synthesis can be broadly divided into the following steps: input description, internal representation, design space exploration, allocation, scheduling and binding. Therefore the final structure at the RT level consists of the data path and the control path. Traditional high level synthesis design flow falls short for the modern

generation of complex VLSI and SoC designs, because the conventional design flow just takes into account the optimization of two parameters, namely area and latency. But the new generation of system designs requires multi parametric optimization strategies in HLS while simultaneously utilizing rapid and efficient DSE approaches for finding the best suitable architecture [5].

#### **1.4.2 Theoretical Background on Design Space Exploration**

For the present generation of Very large Scale Integration (VLSI) designs with multi objective nature, the cost of solving the problem of scheduling, allocation and module selection discretely or simultaneously by exhaustive analysis is strictly prohibitive. Multi objective VLSI designs are used in low end Application Specific Integrated Circuits (ASICs) with low power dissipation and acceptable performance, as well as in high end ASICs with high performance requirements and satisfactory power expenditure. Hence, efficient design space exploration techniques are needed that not only satisfy the above requirements but also make efficient use of runtime, due to time to market pressure [6]. Design space exploration [51-60] is a procedure for analyzing the various design architectural alternatives in the design space to obtain the optimum architecture needed for the behavioral description based on the predefined user specifications. Design space exploration has always been a challenge for researchers due to the heterogeneity of the objectives and parameters involved. The current trend towards design space exploration has been the reduction of the design space into a set of Pareto optimal points [42-46] by Pareto optimal analysis. Sometimes even the Pareto optimal set can be very large for analysis and selection of the design for system implementation. In order to assist the decision maker in exploring the design space better, an accurate and fast approach efficient in terms of time

expended and quality of solution found is very significant for high level synthesis design of hardware systems.

#### **1.4.3** Overview on the Abstraction Level of Optimization

Today's electronic systems are designed starting from specifications given at a very high level of abstraction. This is because many Electronic Design Automation (EDA) tools accept a design expressed in a high-level format as input and can automatically produce the corresponding RT/Logic/transistor-level implementation with very limited human intervention. All hardware systems can be classified into various levels of abstraction such as System level, Architecture level, Register Transfer Level (RTL), Layout level and Transistor level. This abstraction level also provides an insight into the hierarchy that a system can be classified into. Optimization performed at the higher levels of abstraction provides more flexibility, productivity and design specification awareness than performing only at the lower levels of abstraction. Moreover, although effective, performing optimization only at the transistor level is not sufficient for the current generation of high performance, power hungry application specific systems (used in embedded applications) due to the enormous complexity involved. The traditional method of optimization performed by circuit designers only at low level for area and latency is insufficient for current power and performance requirements. Therefore, the role of system architects has become extremely crucial. System architects consider user goals during the architecture selection process by performing optimization of the given application based on high level parametric models. The design process must consider user goals even at the very high abstraction level (during high level synthesis process) in order to generate a quality aware solution (at the RT-Level) with greater possibility of optimization at the transistor level.

#### **1.4.4 Reasons for Studying High Level Synthesis**

There has been a trend towards automating synthesis at higher levels of the design hierarchy in the recent years. Logic synthesis has gained acceptance in industry long back and currently there has been substantial interest shown in Register Transfer Level (RTL) design obtained from higher levels of abstraction (algorithmic). The reasons are the following [27]:

**Reduced design time and high acceleration**: If more of the design process is automated, a company can complete a design faster, and thus have a better chance of hitting the market window for that design.

**Design is specification aware from the very earliest stage**: Design space exploration to perform multi-objective optimization and tradeoff is needed from the very earliest stage of designing. This will enable the designers to start the development with an architecture that is already specification aware (high level optimized) from the highest level of abstraction thus rendering more chances that final design (logic/layout) corresponds to the given constraints.

The ability to search the design space (and design alternatives): A good synthesis system can produce several designs from the same specification in a reasonable amount of time. However, final selection can be challenging with many choices. Therefore, an efficient exploration method is needed to tackle the problem from the very high abstraction level to assure the designer a greater chance of optimization and flexibility to control architecture based on user requirements. This allows the developer to explore different tradeoffs between cost, speed, power etc. or to take an existing design and produce a functionally equivalent one that is more efficient.

**Easy availability of IC technology**: As more design expertise is moved into the synthesis system, it becomes easier for non-expert designers to manufacture a chip that meets a given set of specifications and operating constraints.

#### **1.5 Summary of Contribution**

The proposed exploration approach can be used during the design process of application specific processors/custom processors or standalone Application Specific Integrated Circuits (ASIC's) custom data intensive applications. Therefore, systems that include adaptable applications which change dynamically during runtime should not be considered with these approaches.

This dissertation contributes to the following by removing bottlenecks in previous approaches:

• Solving the Problem of Design Space Exploration for Power-Performance-Cost/Area tradeoff in High Level Synthesis using novel Priority Factor approach:

(Note: Publications: S1, S2, S7, S8, S14, S15, S19, S20, S24, S22, S27 on Page: 111)

- a) Introduces /Derives mathematical model for modern parametric framework viz. performance (execution time) for Design Space Exploration.

- b) Introduces/Derives mathematical model for modern performance parametric framework viz. Hardware Cost for Design Space Exploration.

- c) Presents mathematical model for modern performance parametric framework viz.

Power for Design Space Exploration

- d) Proposes a new technique using Priority Factor Metric and Vector Design Space scheme for arranging the architecture design space.

- d) Provides significant improvements in exploration speed compared to a recent technique for various signal processing benchmarks.

- Solving the Problem of Design Space Exploration for Hardware Area/power-Performance-power/area tradeoff in High Level Synthesis using Self-Correction Scheme based Hybrid Fuzzy approach:

(Note: Publications: S3, S4, S9, S10, S13, S16, S23 on Page: 111)

- a) Proposes Hybrid Fuzzy scheme based frameworks for all cases of exploration for Area/Power and Performance parameters.

- b) Development of Fuzzy sets for representation of architecture design variances.

- c) Algorithms with Self-Correction Scheme for exploring the final design point.

- d) This hybrid technique provides an average improvements of greater than 22 % in exploration process compared to a recent technique for various size benchmarks.

- Solving the Problem of Integrated Exploration of Scheduling and Module Allocation in High Level Synthesis for static power optimization under minimum control step usage: (*Note: Publications: S5, S11, S18, S21 on Page: 111*)

- a) Proposes a mathematical expression for power gradient based on the power dissipation of the resources used during determination of high priority nodes.

- b) Presents a new priority function called 'Priority indicator (PI)' based on selection criterion that takes into account the power gradient. This new iterative exploration approach method is used for exploring the optimal/sub optimal integrated solution to the problem of scheduling and module selection.

- c) Provides a completely automated design space exploration tool for rapid exploration of scheduling and module selection in high level synthesis design process.

- d) The proposed approach successfully improves the quality of final solution by an average of 5.07 % and reduces the exploration runtime by an average of 59% compared to a current approach for standard DSP Benchmarks.

- Solving the Problem of Integrated Exploration of Scheduling and Module Allocation in High Level Synthesis for Power-Performance tradeoff using Heuristic Genetic Algorithm: (*Note: Publications: S6, S12, S17, S26 on Page: 111*)

- a) Multi Structure Genetic Algorithm is based on a novel cost function based on the power consumption-execution time tradeoff.

- b) The total execution time constraint considered in the cost function of the proposed approach is based on latency, cycle time and number of data (N) to be pipelined.

- c) Multi structure genetic algorithm is based on a new structural topology where each functional unit type is represented by an independent chromosome.

- d) Since the multi structure genetic algorithm incorporates a new seeding process with two special chromosomes, hence the final solution found is always certain to be global optimal or local optimal (in certain cases) in terms of the execution time (including latency and cycle time) and power.

- e) The results produced by proposed approach are better compared to another genetic algorithm based approach, for almost all digital signal processing benchmarks.

- Introducing a design Automation Platform (DAP) in high level synthesis for multiobjective optimization and RTL circuit generation capable of:

(Note: Publications: S1, S2, S3, S4 on Page: 111)

- a) Power-Performance Tradeoff using Area as Optimization Criteria.

- b) Hardware Area- performance Tradeoff using Power as Optimization Criteria.

#### **1.6 Dissertation Organization**

The rest of the dissertation is organized as follows: Chapter 2 describes in details the proposed techniques behind solving the problem of Design Space Exploration for power-performance-area/cost tradeoff using priority factor and vector design space technique. Chapter 3

elaborates on proposing the solution for solving the problem of design space exploration for hardware area-performance-power tradeoff using fuzzy membership based algorithm and priority factor framework. Chapter 4 proposes the approach for solving the problem of integrated exploration of scheduling and module allocation for static power optimization under minimum control step usage based on power gradient theory, while in Chapter 5, the approach for solving the problem of integrated Exploration of scheduling and module allocation for powerperformance tradeoff using multi structure genetic algorithm is proposed. Chapter 6, introduces a high level synthesis DAP for multi-objective optimization and RTL circuit generation capable of performing multi objective tradeoff. The results of the proposed DSE approaches for various well known high level synthesis benchmarks indicating exploration time and quality improvements obtained when compared to the current existing DSE approach are provided in Chapter 7. Chapter 8 is dedicated to conclusion and future scope of work in this area. The list of publications related to this field of research study and the total list of citations are also provided thereafter.

### **Chapter 2**

# Rapid Design Space Exploration in High Level Synthesis Based on Power-Performance Tradeoff using Priority Factor Metric

This chapter introduces the first algorithm of the dissertation based on priority factor metric which deals with proposing a solution to the design space exploration in high level synthesis for computation intensive applications. It is used for performing tradeoff based on power-performance constraint and area/cost as optimization criteria. The proposed approach is deterministic in nature and therefore finds the final architecture based on resolute evaluation steps (unlike heuristic methods). It is important to note that the proposed exploration approach is only applied to custom data intensive applications (application specific processors/custom processors) or standalone Application Specific Integrated Circuits (ASIC's). The priority factor metrics proposed in this chapter are based on mathematical models for modern parametric frameworks viz. power, performance area/cost. The approach also employs a special topology called vector design space based on priority order sequencing for sorted arrangement of the design space. The mathematical framework for each parameter is described and deduced below:

#### 2.1 Mathematical Derivation for Cost/Area Model

#### A. The Proposed Framework for Hardware Cost

Let the area of the resources be given as 'A'.  $R_i$  denotes the resources available for system designing; where 1<i<n. 'n' represents the maximum resource available for designing. 'Rclk' refers to the clock oscillator used as a resource providing the necessary clock frequency to the system (Note: to simplify the mathematical modeling of area, the existence of multiple clocks operating in a single system has been ignored. For high level area modeling, only the global clock operating in a system has been considered. However, the user has the flexibility to declare in the module library various clock frequency oscillators available for selection based on the exploration result). The total area can be represented as the sum of all the resources used for designing the system, such as adder, multiplier, divider, clock frequency oscillator and the memory elements. At the high level all elaborate lower level details such as routing information (wire connection etc.) are not available. Thus they have been ignored in eqn. (1) for high level area estimation. As described in [5, 41], the total area of a system mainly consists of the areas of the functional blocks; the total area can be approximated as follows:

$$A = \sum A(Ri) \tag{1}$$

$$A = (N_{R1} \cdot K_{R1} + N_{R2} \cdot K_{R2} + \dots + N_{Rn} \cdot K_{Rn}) + A(R_{clk}) + N_{RM} \cdot K_{RM}$$

(2)

Where '*NRi*' represents the number of resource 'Ri', '*K*<sub>*Ri*</sub>' represents the area occupied per unit resource '*Ri*', '*N*<sub>*RM*</sub>' represents the number of memory elements present (such as registers) and '*K*<sub>*RM*</sub>' represents the area occupied by each memory element. Let the total cost of all resources in the system is '*C*<sub>*R*</sub>'. Further, cost per area unit (in fiscal units) of the resource (such as adders, multipliers etc) is given as '*C*<sub>*Ri*</sub>', the cost per area unit (in fiscal units) of the clock oscillator is  $C_{Rclk}$  and finally the cost per area unit (in fiscal units) of memory element is  $C_{RM}$ . Therefore total cost of the resources in fiscal units is given as:

$$C_{R} = (N_{R1} \cdot K_{R1} + N_{R2} \cdot K_{R2} + \dots + N_{Rn} \cdot K_{Rn}) \cdot C_{Ri} + A(R_{clk}) \cdot C_{Rclk} + N_{RM} \cdot K_{RM} \cdot C_{RM}$$

(3)

Applying partial derivative to equation (3) with respect to  $N_{R1}$  .... $N_{Rn}$ , with respect to  $N_{RM}$  and with respect to  $A_{Rclk}$  yields equation (4) to (7) respectively as shown below:

$$\frac{\partial C_R}{\partial N_{Rl}} = \frac{\partial [(N_{Rl} \cdot K_{Rl} \cdot C_{Rl} + \dots + N_{Rn} \cdot K_{Rn} \cdot C_{Rn}) + A(R_{clk}) \cdot C_{Rclk} + N_{RM} \cdot K_{RM} \cdot C_{RM}]}{N_{Rl}} = K_{Rl} \cdot C_{Rl}$$

$$(4)$$

$$\frac{\partial C_R}{\partial N_{Rn}} = \frac{\partial [(N_{R1} \cdot K_{R1} \cdot C_{R1} + \dots + N_{Rn} \cdot K_{Rn} \cdot C_{Rn}) + A(R_{clk}) \cdot C_{Rclk} + N_{RM} \cdot K_{RM} \cdot C_{RM}]}{N_{Rn}} = K_{Rn} \cdot C_{Rn}$$

(5)

$$\frac{\partial C_R}{\partial A_{Rclk}} = C_{Rclk} \tag{6}$$

$$\frac{\partial C_R}{\partial N_{RM}} = K_{RM} \cdot C_{RM}$$

(7)

For the sake of simplicity, while applying partial derivative to a certain resource (equations (4) – (7)), the others resources are assumed fixed (or constant). In order to determine the contribution of a specific resource on the change in a parameter, other resources have to be kept fixed (constant). For example, in equation (7), while applying partial derivative with respect to  $N_{RM}$ , the change in number of resources  $N_{R1} \dots N_{Rn}$  is assumed to be fixed. Without keeping the other resources  $N_{R1} \dots N_{Rn}$  fixed during analysis, the impact of resource  $N_{RM}$  in the deviation of cost parameter cannot be determined. Now using the theory of approximation by differentials, the change in the total cost can be approximated by the following equation:

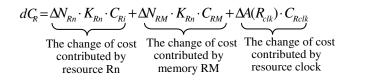

$$dC_{R} = \frac{\partial C_{R}}{\partial N_{Rl}} \cdot \Delta N_{Rl} + \frac{\partial C_{R}}{\partial N_{Rn}} \cdot \Delta N_{Rn} + \frac{\partial C_{R}}{\partial N_{RM}} \cdot \Delta N_{RM} + \frac{\partial C_{R}}{\partial A_{Rclk}} \cdot \Delta A_{Rclk}$$

(8)

Additionally, equation (8) above indicates the total change in  $C_R$  (total cost of resources) with

respect to change in number of resource  $N_{R1}$  .... $N_{Rn}$ ,  $N_{RM}$  and  $R_{clk}$ . Substituting equations (4) to

(9)

(7) into equation (8) yields equation (9) shown above:

Equation (9) represents the change in total cost of resources with the change in the number of all resources and the clock period (clock frequency). The Priority Factor (PF) for cost of resources is defined as:

$$PF(R1) = \frac{\Delta N_{R1} \cdot K_{R1} \cdot C_{Ri}}{N_{R1}}$$

(10)

. . . . .

$$PF(Rn) = \frac{\Delta N_{Rn} \cdot K_{Rn} \cdot C_{Ri}}{N_{Rn}}$$

(11)

$$PF(RM) = \frac{\Delta N_{RM} \cdot K_{RM} \cdot C_{RM}}{N_{RM}}$$

(12)

$$PF(Rclk) = \frac{\Delta A(Rclk) \cdot C_{Rclk}}{N_{Rclk}}$$

(13)

PF yields a real number, which suggests the extent to which the change in number of a particular resource contributes to the change in hardware cost. The PF is a determining factor which helps us to judge the influence of a particular resource on the variation of the optimization parameters like area, time of execution and power consumption. This PF is used later in our approach to organize the architecture design space consisting of variants in increasing or decreasing order of magnitude. The equation (10) and (11) indicates the change of cost with respect to change in resource R1,....Rn Similarly, equation (12) indicates the change of cost of the system with respect to change in number of resource 'RM'. Further equation (13) indicates

the change of cost of the system with respect to change in resource 'Rclk'.

#### **2.2 Mathematical Derivation for Execution Time Model**

For a system with 'n' functional resources the time of execution can be represented by the following formula:

Based on [5, 61,62,12], the time of execution can be represented by the following equation:

$$T_{exe} = [L + (D-1) \cdot T_c]$$

<sup>(14)</sup>

where 'L' represents latency of execution, ' $T_c$ ' represents the cycle time of execution , 'D' denotes the number of data elements to be processed . Equation (14) indicates the time needed to data pipeline an application based on data dependency and available functional units. The equation also captures any situation through initiation interval where an operation is not available for pipelining due to data hazard. It is important to mention the difference between data pipelining/data level parallelism and instruction level parallelism: In the former, there are no service operations such as instruction fetch, instruction decode, data fetch and write back. Only the execution stage can directly processes the input data and produce the output for the next operation. Therefore, no latch requirements are necessary during data pipelining. In contrast, instruction level pipelining includes service operations as well as execution stage and pipelining is effectively between the hardware units. Therefore, latches are necessary to store the information of the previous unit and to pass it to the next stage. (An example of data pipelining for a sample application is demonstrated in Chapter 6).

The term 'workload' of a resource signifies the time required (or clock cycles needed) to finish its assigned operation during scheduling. Hence the total workload (*W*) of all resources to finish their respective operations during scheduling for 'D' sets of processing data can be represented by (15):

$$W = (N_{R1} \cdot T_{R1} + N_{R2} \cdot T_{R2} + \dots + N_{Rn} \cdot T_{Rn}) \cdot D.T_P$$

(15)

Where  $N_{Rl}$  represents the number of resource 'Ri' and 'T<sub>Ri</sub>' represents the number of clock cycles needed by resource '*Ri*' (1<=i<=n) to finish each operation. 'D' is the number of sets of data elements that must be processed. Note: In the mathematical modelling process in equation (15), the operations have been considered to operate in a sequential manner for theoretical assumption and simplicity purposes. In the experimental exploration process described later, actual data parallelism has been considered while evaluating a particular solution. Therefore if variable N<sub>Ri</sub> in equation (15) is increased, then 'W' will increase. In equation (16) and (17), objective is to evaluate the deviation of workload (W) with respect to change in variable N<sub>Ri</sub>. For example, the average deviation of 'W' with respect to change in N<sub>Ri</sub> from 1 adder/subtractor to 3 adder/subtractors can be evaluated. Therefore, the motive is to determine the contribution of each resource type on a specific parameter (as explained in Section 3.2). The demonstration of this approach is described later in this chapter.

From the approximation of differentials the change in 'workload' is approximated in (16).

$$dW = D \cdot \left[ \left( \frac{\partial W}{\partial N_{R1}} \cdot \Delta N_{R1} + \frac{\partial W}{\partial N_{R2}} \cdot \Delta N_{R2} + \dots + \frac{\partial W}{\partial N_{Rn}} \Delta N_{Rn} \right) + \Delta T_p \cdot \frac{\partial W}{\partial T_p} \right]$$

(16)

Applying partial derivative to the (15) with respect to  $N_{R1}$ .... $N_{Rn}$  and  $T_p$  will produce the following set of equations:

$$\frac{\partial W}{\partial N_{R1}} = \frac{\partial [(N_{R1} \cdot T_{R1} + N_{R2} \cdot T_{R2} + \dots + N_{Rn} \cdot T_{Rn}) \cdot T_p \cdot D]}{\partial N_{R1}}$$

$$= T_{R1}T_p \cdot D$$

(17)

$$\frac{\partial W}{\partial N_{R_n}} = \frac{\partial [(N_{R_1} \cdot T_{R_1} + N_{R_2} \cdot T_{R_2} + \dots + N_{R_n} \cdot T_{R_n}) \cdot T_p \cdot D]}{\partial N_{R_n}}$$

$$= T_{R_n} T_p \cdot D$$

(18)

$$\frac{\partial W}{\partial T_p} = \frac{\partial [(N_{R1} \cdot T_{R1} + N_{R2} + \dots + N_{Rn} \cdot T_{Rn}) \cdot T_p \cdot D]}{\partial T_p}$$

(19)

$$= (N_{R1} \cdot T_{R1} + N_{R2} \cdot T_{R2} + \dots + N_{Rn} \cdot T_{Rn}) \cdot D$$

(20)

Substituting equations (17), (18) and (19) in equation (16) yields equation (21):

$$dW = \Delta N_{R1} \cdot T_{R1} \cdot T_{p} \cdot D + \Delta N_{R2} \cdot T_{R2} \cdot T_{p} \cdot D + ... + \Delta N_{Rn} \cdot T_{Rn} T_{p} \cdot D + D \cdot \Delta T_{p} \cdot (T_{R1} \cdot N_{R1} + T_{R2} \cdot N_{R2} + ... + T_{Rn} \cdot N_{Rn})$$

(21)

Equation (21) reflects the change in total workload with the change in number of all the resources and the clock period (clock frequency).

$\Delta N_{Rn} \cdot T_{Rn} \cdot T_p \cdot D$  = The change of 'W' contributed by the change in number of resource Rn.

$\Delta T_p \cdot (T_{R_1} \cdot N_{R_1} + T_{R_2} \cdot N_{R_2} + \dots + T_{R_n} \cdot N_{R_n}) \cdot D = \text{The change of 'W' contributed by the change in clock}$ period (frequency).

Considering constraint on the number of resources, the increase in total workload (*W*) will cause an increase in total execution time. Therefore, the more the workload increases, the more the execution time increases under resource constraints. Hence, the change in number of a resource (e.g. change in adder from one to three) that contributes to the change in total workload the most, also contributes to the change in total execution time the most. So based on above analysis, PF for execution time parameter is defined as:

$$PF(Rn) = \frac{\Delta N_{Rn} \cdot T_{Rn}}{N_{Rn}} \cdot (T_p)^{\max}$$

(22)

$$PF(Rclk) = \frac{N_{R1} \cdot T_{R1} + N_{R2} \cdot T_{R2} + ... + N_{Rn} \cdot T_{Rn}}{N_{Rclk}} \cdot (\Delta T_p)$$

(23)

'D' is ignored in the expression for PF because it does not contribute to the change in Priority Order (PO) sequence described later in the paper. The factors defined above reflect the average change in execution time ( $T_{exe}$ ) with the change in number of a resource (change in adder from one to three) at maximum clock period. These factors also reflect the average change in execution time ( $T_{exe}$ ) with the change in clock frequency. In the expression for PF in (23), minimum clock frequency is considered because at this frequency the clock period is the maximum. Hence, the change in number of a specific resource at maximum clock period will influence the change in execution time the most, compared to the change in execution time at other clock periods.

#### **2.3 Mathematical Model for Power Consumption**

Based on [5, 64, 12], dynamic power ( $P_D$ ) of a system as a function of operating frequency and number of devices switching due to frequency of operation can be represented as:

$$P_{D} = \sum_{i=1}^{n} (N_{Ri} \cdot K_{Ri}) \cdot p_{c}$$

(24)

Where 'n' is number of functional resources, ' $N_{Ri}$ ' represents the number of resource Ri as

mentioned earlier. ' $K_{Ri}$ ' represents the area occupied per unit resource Ri and ' $p_{c}$ ' denotes the

power consumed per area unit resource at a particular frequency of operation. Equation (24)

models the dependency of power on the activity rate (which in turn is based on frequency of

operation) of the modules in the system. Theoretically if there is no activity in the circuit the

dynamic component of the power will be zero. The leakage power has been ignored in this

model.

Applying the using partial derivative method on equation (24) (as shown in Section 2.1 for cost parameter), the Priority Factor (PF) for power consumption is extracted as follows (PF) [27]:

$$PF(Rn) = \frac{\Delta N_{Rn} \cdot K_{Rn}}{N_{Rn}} \cdot (p_c)^{\max}$$

(25)

$$PF(Rclk) = \frac{N_{R1} \cdot T_{R1} + N_{R2} \cdot T_{R2} + \dots + N_{Rn} \cdot T_{Rn}}{N_{R_{clk}}} \cdot (\Delta p_c)$$

(26)

The priority factor defined in equation (25) indicates the change of total power consumption with the change in number of resources at maximum clock frequency. In contrast, the priority factor defined in equation (26) indicates the deviation in total power consumption with respect to the change in number of clock oscillators from minimum to maximum. The priority factor helps to arrange the architectural variants of the design space in increasing or decreasing order of magnitude depending on the objective parameter. The PF is arranged in such a way that the resource with the minimum PF is chosen first, gradually increasing and then ending at the resource with the highest priority factor. The above rule applies for all three parameters described in this chapter.

### **2.4 Proposed Method of Design Space Exploration of Architecture Based on Power-Performance tradeoff with area/cost as optimization criteria**

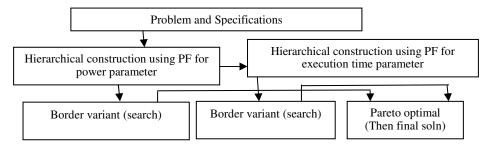

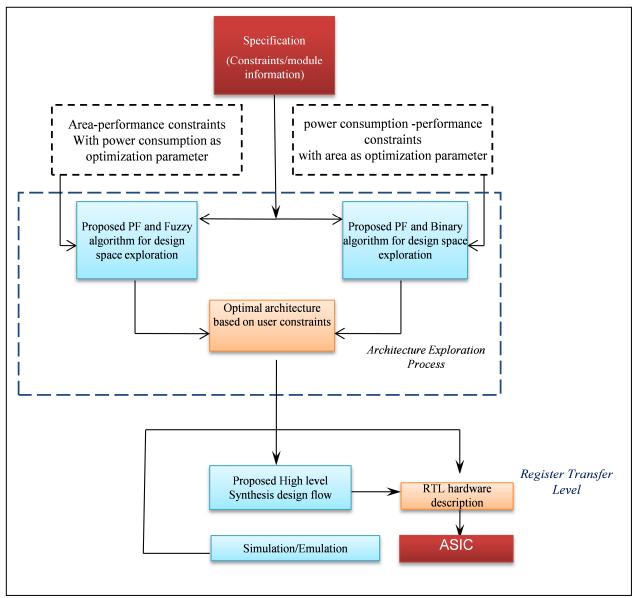

The overview of the proposed method is shown in Figure 1.

#### A. System specifications

The case study of a selected benchmark has been provided for demonstration of the proposed method based on some real system specifications (as shown in Table 1). The value assumed for area of each functional unit (in CLB slices) is obtained through synthesis in commercial logic synthesis tools. The values assumed for the clock cycle consumed for each functional unit is obtained from the literature [14, 22, 23]. If the user has different types of the same functional unit (such as 8-bit adder, 16 bit adder etc.), then the area of each functional unit type is also

specified in this stage simultaneously with the number of each functional unit type available for choice (e.g. Both the area of 8-bit adder (15 au) and the area of 16 bit adder (30 au) can be specified in addition to information 6) and 7) provided in Table 1).

*Note 1*: The parameters have fixed values assigned/specified by the user in this stage. These parametric constraints are the demand of the user and the final solution must meet these high level constraints as well as the requirement of the optimization parameter. For example, in Table 1, the assumed value of the user constraints for power and time is 8W and 140 us respectively. This indicates that the final solution must meet these high level constraints while also being minimum in occupied area. Therefore during the exploration process, the design space will be pruned based on these requirements and the best possible solution will result (as will be demonstrated later).

*Note 2:* The method assumes fixed hardware units such as 3 adder/subtractors, 4 multipliers, and 2 clock oscillators as shown in Table 1 because this is the specified maximum available units affordable by the user for this custom application specific system design. In other words, every user has a maximum limit on the permissible fixed hardware units that can be afforded based on specific configuration needs. However, for demonstration in this dissertation, these values are arbitrarily assumed for a sample application and are subject to flexibility depending on the requirement of the user and problem (as will be demonstrated latter).

*Note 3*: In Table 1 there are two available choices for clock frequency oscillators assumed to be specified by the user. The clock oscillator available for selection through exploration process is the global clock frequency of the system. For high level architecture decisions only global clock frequency has been considered in the proposed exploration method (as will be demonstrated later in this chapter).

The function of the selected second order digital IIR Butterworth filter benchmark is given in eqn (27).

$$y(n) = 0.167 x(n) + 0.5x(n-1) + 0.5x(n-2) + 0.167 x(n-3) - 0.33 y(n-2)$$

(27)

B. Calculation of the priority factor for each available resource for execution time parameter

For resource adder/subtractor (R1), multiplier (R2), clock oscillator (R<sub>clk</sub>):

$PF(R1) = \Delta N_{R1} \cdot T_{R1} \cdot (T_p)^{\text{max}} / N_{R1} = \frac{(3-1) \cdot 2}{3} \cdot (0.02) = 0.026$

$PF(R2) = \Delta N_{R2} \cdot T_{R2} \cdot (T_p)^{\max} / N_{R2} = \frac{(4-1) \cdot 4}{4} \cdot (0.02) = 0.06$

$PF(R_{clk}) = N_{R1} \cdot T_{R1} + N_{R2} \cdot T_{R2} \cdot (\Delta T_p) / N_{Rclk}$

$= (3 \cdot 2 + 4 \cdot 4) \cdot (0.02 - 0.005) / 2 = 0.165$

According to the above analysis the change in number of adder/subtractor affects the change

Figure.1.Generic Overview of the Proposed Exploration Method

Table1. System Specifications and Constraints for PF Method

- 1) Maximum power consumption: 8 watts (W)

- 2) Maximum time of execution:  $140 \ \mu s$  (for D =1000 sets of data)

- 3) Hardware area of resources: Minimum

- 4) Maximum resources available for the system design:

- a) 3 Adder/subtractor units.

- b) 4 Multiplier units

c) 2 clock frequency oscillators: 50 MHz and 200 MHz

- 5) No. of clock cycles needed for multiplier and adder/subtractor to finish each operation: 4 cc and 2cc

- 6) Area occupied by each adder/subtractor and multiplier: 20 area units (a.u) and 100a.u. (e.g. 20 CLBs on FPGA)

- 7) Area occupied by the 50MHz and 200MHz clock oscillator: 4 area units and 10 area units

8) Power consumed at 50 and 200MHz:10mW/a.u. and 40mW/a.u.

in execution time the least, while the change in clock frequency from 50 MHz to 200 MHz

affects the change in execution time the most. The minimum for adder/subtractor and multiplier

is one in above equations because the digital IIR Butterworth filter function at least requires one adder and one multiplier to successfully accomplish the functioning of the task.

C. Arrangement of resources in Priority Order based on calculation of PF for execution time

Based on the priority factors calculated, a new terminology called 'Priority Order (PO)' is defined. The priority order is a sequence ordering of the resource types (R1...Rn) based on reverse PF magnitude. In other words, the resource type with the lowest priority factor is assigned the highest priority order while the resource type with the highest priority factor is assigned the lowest priority order, i.e. the priority order of the resource increases with the decrease in priority factor of the resource.

For example, resource Rclk with the highest PF (see Section 2.4.B) has been assigned the lowest PO. On the other hand, resource R1 with the lowest PF (see Section 2.4.B) has been

Figure2. Flow chart model of the proposed algorithm

assigned the highest PO. Therefore the following PO of resources is achieved for arranging the design variants in decreasing order for execution time.

PO(R1) > PO(R2) > PO(Rclk)

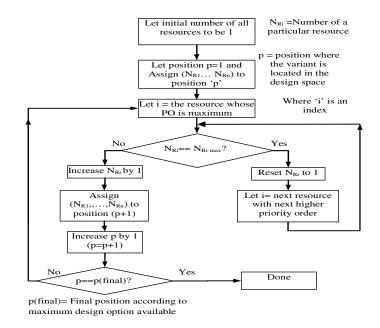

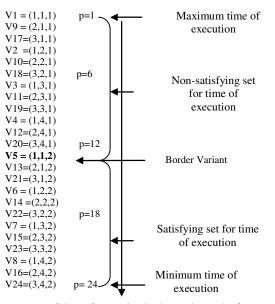

# D. Arrange the design space in decreasing order for execution time according to the priority order

This section presents an algorithm for arranging the random design space in an organized decreasing order for the execution time parameter. Before demonstrating the proposed algorithm it is imperative to identify the advantages of this algorithm compared to existing approaches [12]. The algorithm in Figure 2 differs from the existing techniques [12], which are based on the hierarchical criterion method, with respect to the topology used to represent the design variants in the design space. The proposed algorithm is based on vector design space topology while the approach used in [12] is based on tree topology. Further, the proposed algorithm does not need any variant analysis to arrange the design space in increasing/decreasing order. It therefore requires less time while performing exploration. On the contrary, approach [12] utilizes critical variant analysis to determine the hierarchy of each resource type and then constructs the arranged design in increasing/decreasing order.