b20161463

# CACHE FILTERING ALGORITHM FOR LEAST FREQUENTLY USED DATA WITH ACCURATE MEMORY SIMULATION

By Kiu Kwan Leung

B.Eng. Ryerson University, 2007

Toronto, Ontario, Canada

A thesis

presented to Ryerson University

in partial fulfillment of the

requirement for the degree of

Master of Applied Science

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2010 © Kiu Kwan Leung 2010

#### **Author's Declaration**

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other Institutions or individuals for the purpose of scholarly research.

Author's signature:

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Author's signature:

#### **Abstract**

Cache Filtering Algorithm For Least Frequently

Used Data with Accurate Memory Simulation

© Kiu Kwan Leung 2010

Master of Applied Science

Department of Electrical and Computer Engineering

Ryerson University

We propose a cache filtering algorithm to improve processor performance using a small buffer inside the processor and an algorithm to filter least frequently used accesses from L1 and L2 caches. The algorithm uses simple DRAM fast-page accessing mode to identify accesses that are not previously accessed or not frequently used and keep them out of the cache system and store them in small buffer.

We have also added a realistic page interleaved DDR3 memory simulation model to the SimpleScalar simulator. This model supports any processor and memory clock speeds, different sets of memory latencies, various configurations of memory banks and channels.

Results show that the filtering algorithm could improve performance of some applications compared to the same system that does not use the filtering algorithm.

#### Acknowledgement

I would like to express my deep gratitude to my supervisor, Dr. Nagi Mekhiel for offering me such a chance to work with him as his master student. It is always his brilliant ideas and directions that saved me out of my hurdles throughout the research process and it is always his patience and tolerance that made this research work such an enjoyable learning experience.

I must also thank my parents for their constant support throughout my life. I am thankful for their encouragement and their teachings, which had shaped me up to what I am over the years and allowed me to have such a strong sense that I have a nice place called home. I truly believe that without them, I will not be able to receive such a wonderful learning experience at Ryerson University.

Thirdly, I appreciate the assistance offered by my former supervisor, Dr. Cungang Yang, throughout my graduate studies. His has always been one of my best guides to direct me through the program and taught me how to be a good graduate assistance. I must also thank Professor Ken Clowes for his great advices. As one of the most skilled programmers across the department, he nicely explained the meanings of the advanced syntax used by the author of the SimpleScalar simulator, which enabled me to understand simulator and become a SimpleScalar developer quickly.

I am grateful for the financial assistance that I received through my supervisor and the Electrical and Computer Engineering department at Ryerson University. It is the only reason why I can stay focus and enjoy this research process.

Finally, I sincerely appreciate the Electrical and Computer Engineering department's lab support team for their kind assistance. Without their technical knowledge about the UNIX operating system, I will never finish the research at ease.

# **Dedication**

To my supervisor: Professor Nagi Mekhiel

To my family: father and mother

To my former supervisor: Professor Cungang Yang

# **Table of Contents**

| 1 Introduction                                                              |

|-----------------------------------------------------------------------------|

| 1.1 List of Contributions and Objectives of the Research                    |

| 1.2 Motivation                                                              |

| 1.2.1 Cache pollution caused by rarely used data blocks                     |

| 1.3 The organization of this thesis11                                       |

| 2 Methodology                                                               |

| 3 The Page Interleaved DDR3 Memory Module for the SimpleScalar Simulator 19 |

| 3.1 The software modeling of the memory model                               |

| 3.1.1 The data components of the memory model                               |

| 3.1.2 The functional components of the memory model                         |

| 3.2 The operation of the memory model                                       |

| 3.2.1 Overlapped memory access scheduling                                   |

| 3.2.2 Memory addressing                                                     |

| 3.2.3 The memory_access_latency function                                    |

| 3.3 Simulation and discussion                                               |

| 4 The Cache Filtering Algorithm for Least Frequently Used Data 52           |

| 4.1 The background                                                          |

| 4.2 The baseline system's memory hierarchy characteristics                  |

| 4.3 The cache filtering algorithm and its components                        |

| 4.3.1 The instruction register (IR) and data register file (DRs)55          |

| 4.3.2 The instruction and data L1 cache (I and D L1 caches)                 |

| 4.3.3 The L2 cache                                                          |

| 4.3.4 The filter buffer                                                     |

| 4.3.5 The algorithm                                                      |

|--------------------------------------------------------------------------|

| 5 Simulation and analysis of the cache filtering algorithm               |

| 5.1 The desktop/notebook computer environment and simulation settings 68 |

| 5.2 Simulation results and discussion (desktop/notebook environment) 70  |

| 6 Overview and Comparison of Related Works90                             |

| 6.1 Cache Filtering Techniques to Reduce the Negative Impact of          |

| Useless Speculative Memory References on Processor Performance(Spec) 90  |

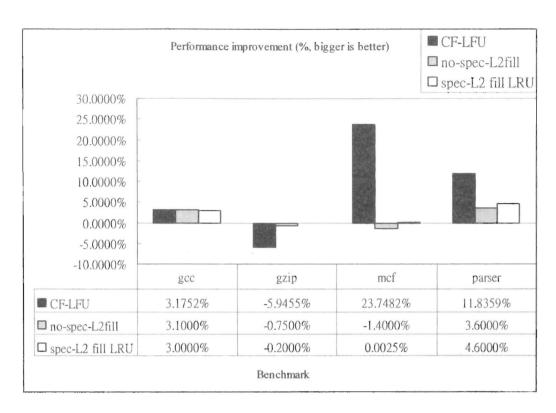

| 6.1.1 Performance improvement comparison (CF-LFU vs. Spec)               |

| 6.2 Line Distillation: Increasing Cache Capacity by Filtering Unused     |

| Words in Cache Lines (Line distillation)                                 |

| 6.2.1 Performance improvement comparison between CF-LFU and              |

| Line distillation                                                        |

| 6.3 Reducing Cache Polution via Dynamic Data Prefetch Filtering          |

| (Prefetch filter) 98                                                     |

| 6.3.1 Performance improvement comparison between CF-LFU and              |

| Prefetch filter 99                                                       |

| 7 Conclusion and future work                                             |

| Bibliography                                                             |

| Appendix110                                                              |

| A.1 Sample verification of cache filtered desktop system with 2MB L2     |

| cache running gzip110                                                    |

| A2 Memory simulation result verification 127                             |

# List of Tables

| 1.1 | Total amount of memory access requests generated within execution range | . 5 |

|-----|-------------------------------------------------------------------------|-----|

| 1.2 | Total amount of single accessed addresses within execution range        | . 5 |

| 1.3 | Total amount of repeated addresses within execution range               | . 5 |

| 1.4 | Total amount of repeated accesses within execution range                | . 5 |

| 3.1 | Simulation settings for channel and bank tes                            | 45  |

| 5.1 | Simulation settings for the desktop/notebook environment                | 69  |

| 6.1 | Simulation settings for comparison between CF-LFU, no-spec-L2 fill and  |     |

|     | spec-L2 fill LRU                                                        | 92  |

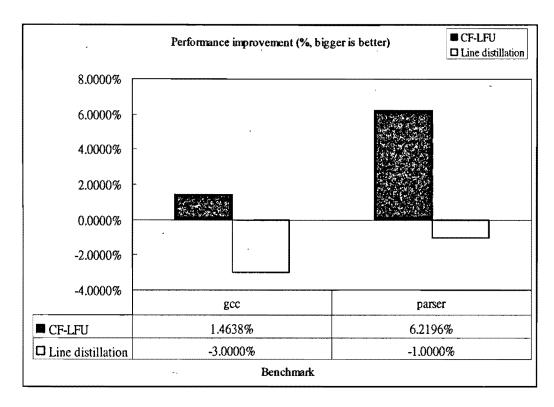

| 6.2 | Simulation settings for comparison between CF-LFU and Line distillation | 96  |

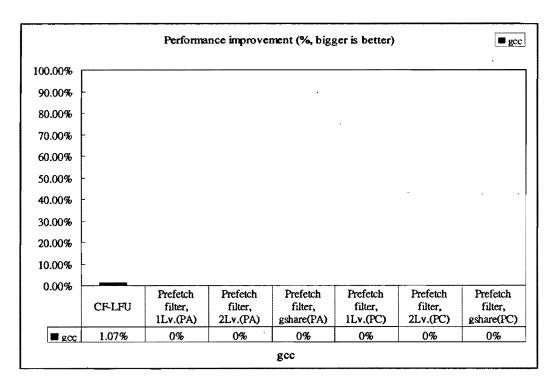

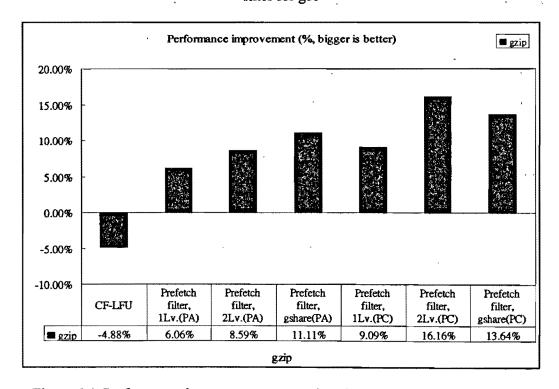

| 6.3 | Simulation settings for comparison between CF-LFU and Prefetch filter   | 99  |

# **List of Figures**

| 1.1 Ine    | performance ratio comparing to 1980s baseline computer systems –            |   |

|------------|-----------------------------------------------------------------------------|---|

| the g      | growing performance gap between processor and memory                        | 2 |

| 1.2 Initia | al content of cache                                                         | 8 |

| 1.3 Cach   | ne miss forces cache to replace Block 0                                     | 9 |

| 1.4 Cach   | ne content after replacing X with Z, program requests for X again causing   |   |

| anotl      | her cache miss to replace block 1                                           | 9 |

| 1.5 Cach   | ne content after replacing Y with X, program requests for Y again causing   |   |

| anotl      | her cache miss to replace block 0 10                                        | 0 |

| 1.6 Fina   | cache content after replacing Z with Y1                                     | 1 |

| 2.1 Simp   | oleScalar cache access function work flow                                   | 4 |

| 2.2 Simp   | oleScalar cache and memory access function sample calling sequence 10       | 6 |

| 3.1 Grap   | phical representation of the mem_t data structure                           | 1 |

| 3.2 The    | overlappable and unoverlappable phases of a random memory access 29         | 9 |

| 3.3 The    | overlappable and unoverlappable phases of a fast page memory access 29      | 9 |

| 3.4 Over   | rlapped memory access scheduling example                                    | 0 |

| 3.5 32bi   | t dual channel 8 bank memory address format                                 | 0 |

| 3.6 32 b   | it dual channel 16 bank memory address format                               | 1 |

| 3.7 32 b   | it single channel 8 bank memory address format                              | 1 |

| 3.8 32 b   | it single channel 16 bank memory address format                             | 1 |

| 3.9 Cons   | secutive read timing (current access is fast page read)                     | 0 |

| 3.10 Wri   | ite following a fast page read timing (current access is fast page write) 4 | 1 |

| 3.11 Rar   | ndom access to the same bank as the previous write timing42                 | 2 |

| 3.12 mei   | mory access latency function work flow4                                     | 4 |

| 3.13 Memory row hit rates of the gcc simulation                                      |

|--------------------------------------------------------------------------------------|

| 3.14 Row hit improvement when total amount of memory banks is doubled 47             |

| 3.15 gcc simulated performance                                                       |

| 3.16 gcc performance improvement achieved by increasing the amount of memory         |

| channels                                                                             |

| 3.17 gcc performance improvement achieved by doubling the total amount of memory     |

| banks                                                                                |

| 4.1 Block diagram of the cache filtering scheme                                      |

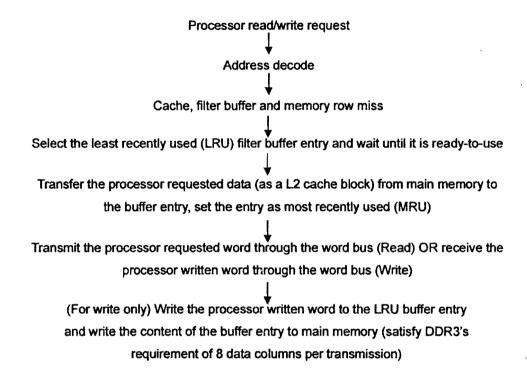

| 4.2 Filtered read/write work flow                                                    |

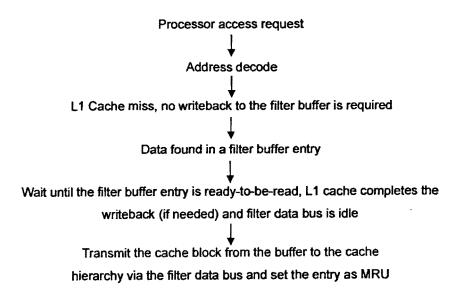

| 4.3 Cache fetching from the filter buffer work flow                                  |

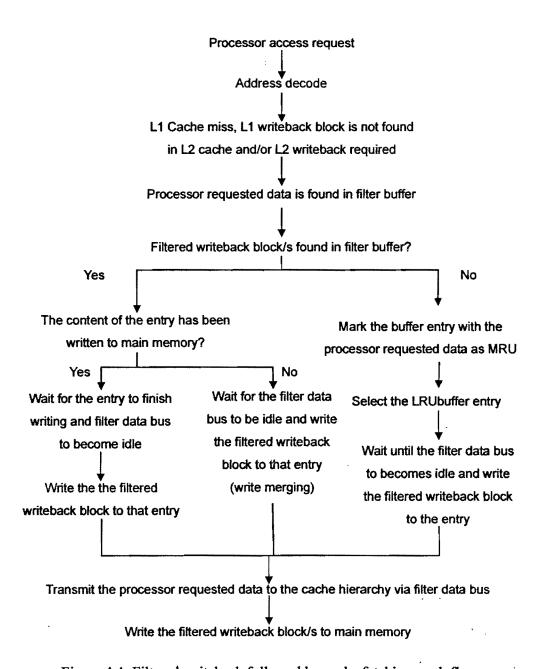

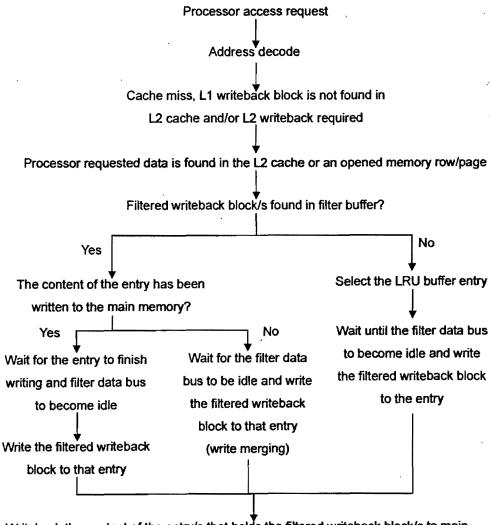

| 4.4 Filtered writeback followed by cache fetching work flow                          |

| 4.5 Filtered writeback without cache fetching work flow                              |

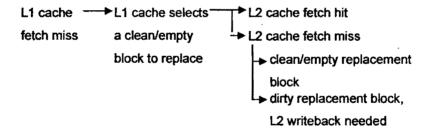

| 4.6 Possible outcomes for L1 fetch miss with L1 clean/empty replacement block 62     |

| 4.7 Possible outcomes for L1 fetch miss with L1 dirty replacement block              |

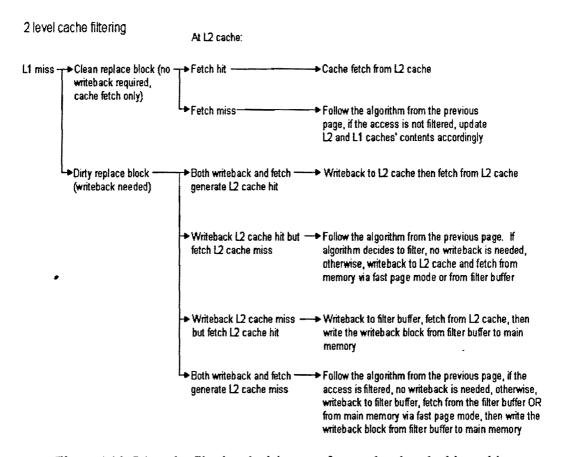

| 4.8 One level cache filtering and lowest level cache filtering decision tree for two |

| level cache hierarchies                                                              |

| 4.9 One level cache filtering and lowest level cache filtering psuedo code for two   |

| level cache hierarchies                                                              |

| 4.10 L1 cache filtering decision tree for two level cache hierarchies                |

| 4.11 L1 cache filtering psuedo code decision tree for two level cache hierarchies 67 |

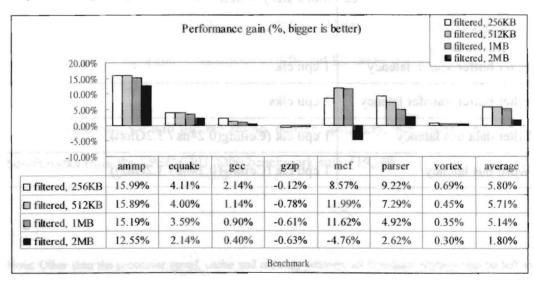

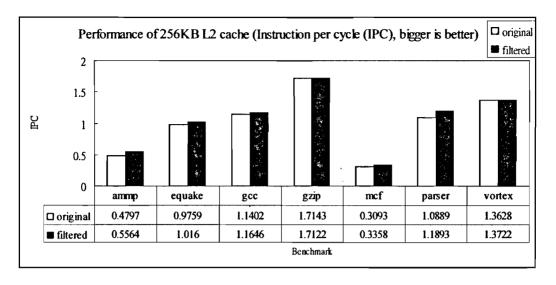

| 5.1 Performance gain of the cache filtered systems                                   |

| 5.2 Performance of the systems with 256KB L2 cache                                   |

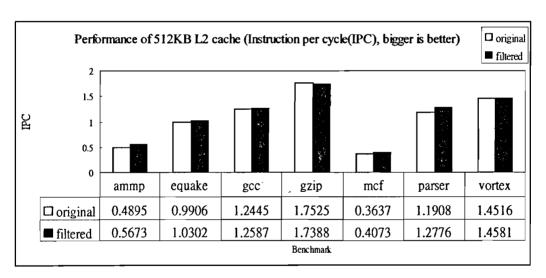

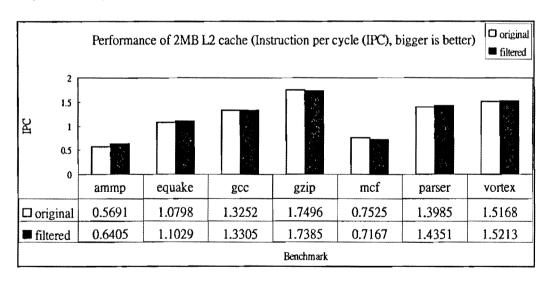

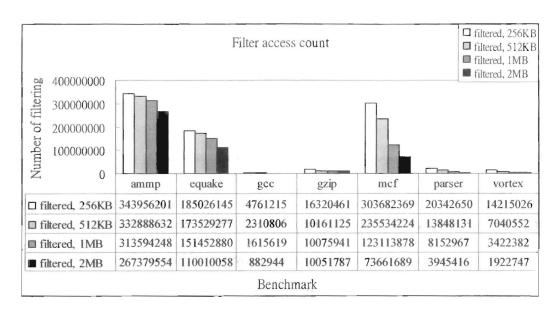

| 5.3 Performance of the systems with 512KB L2 cache                                   |

| 5.4 Performance of the systems with 1MB L2 cache                                     |

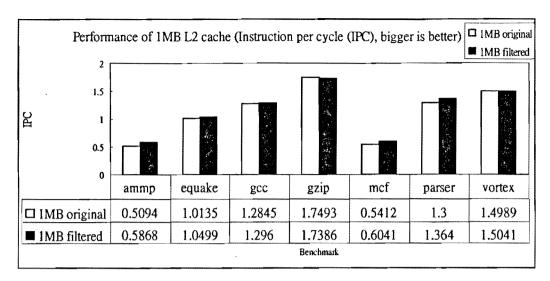

| 5.5 Performance of the systems with 2MB L2 cache                                     |

| 5.6 Total amount of cache filtering throughout benchmark execution                   |

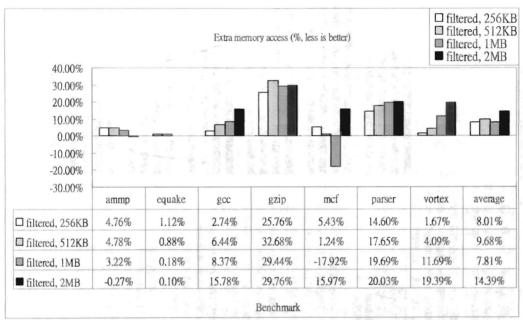

| 5.7 Extra memory accesses of the cache filtered systems                        | 5 |

|--------------------------------------------------------------------------------|---|

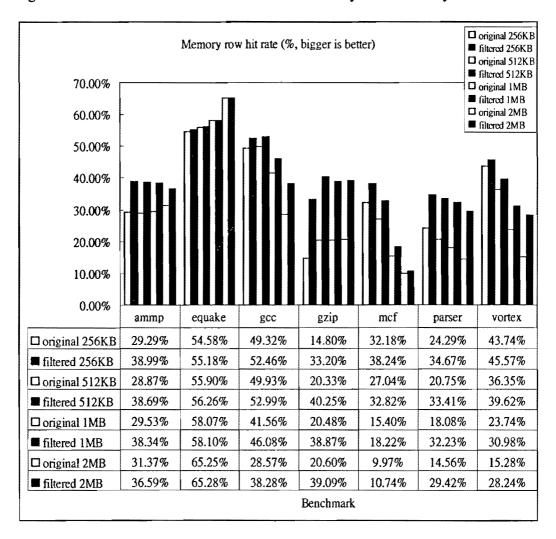

| 5.8 The memory row hit rate of the cache filtered systems                      | 6 |

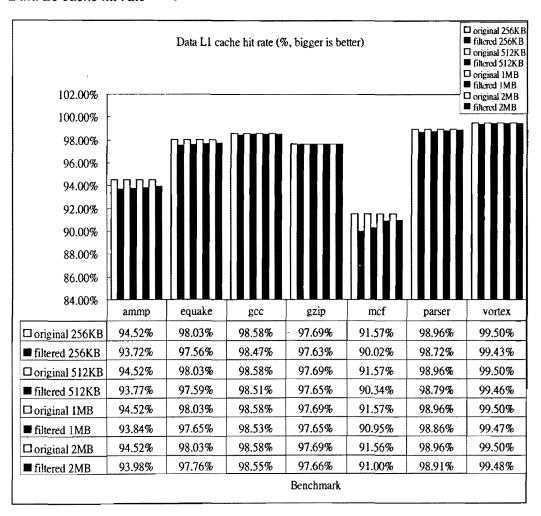

| 5.9 Data L1 cache hit rate                                                     | 7 |

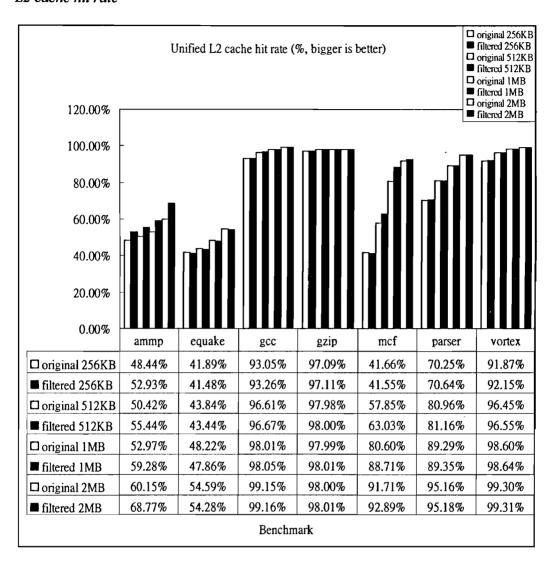

| 5.10 L2 cache hit rate                                                         | 9 |

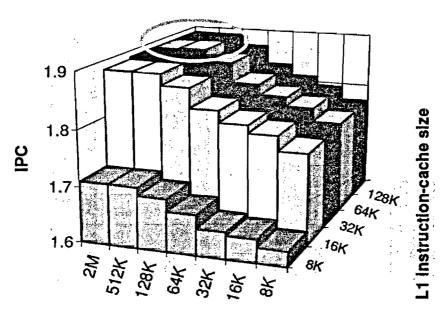

| 5.11 Xlisp simulation with varied I and D L1 cache size, extracted from [23] 8 | 1 |

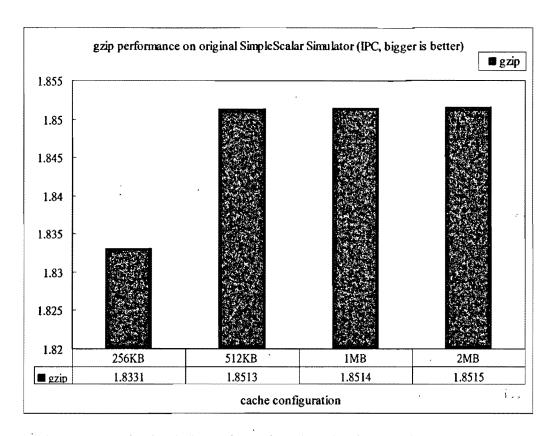

| 5.12 gzip simulations with varied L2 cache size on original SimpleScalar       |   |

| simulator                                                                      | 2 |

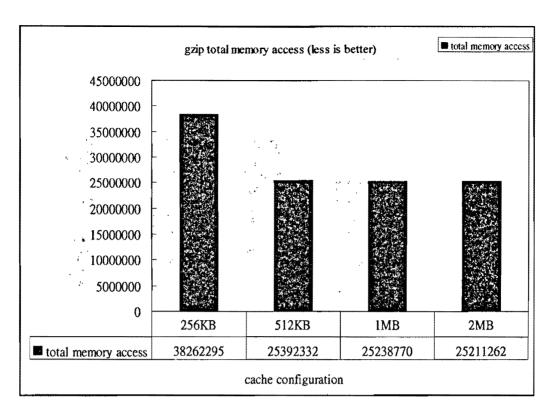

| 5.13 Total amount of gzip memory accesses                                      | 3 |

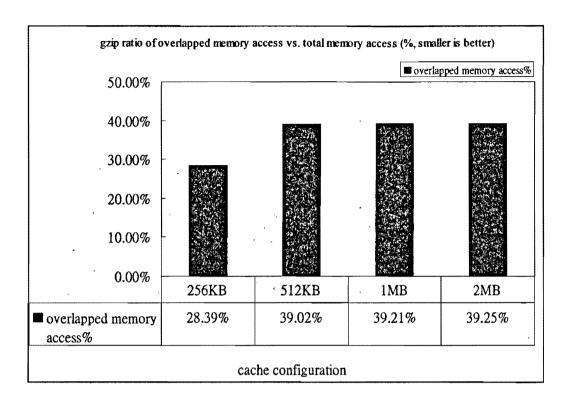

| 5.14 gzip ratio of overlapped memory access versus total memory accesses 8-    | 4 |

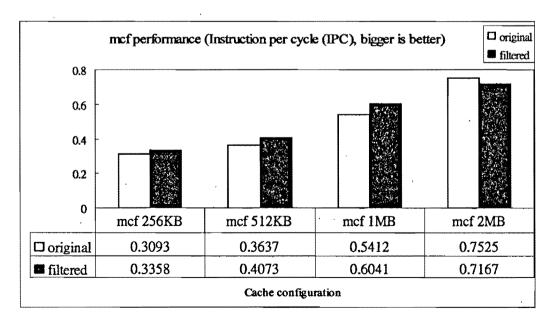

| 5.15 mcf performance in IPC                                                    | 4 |

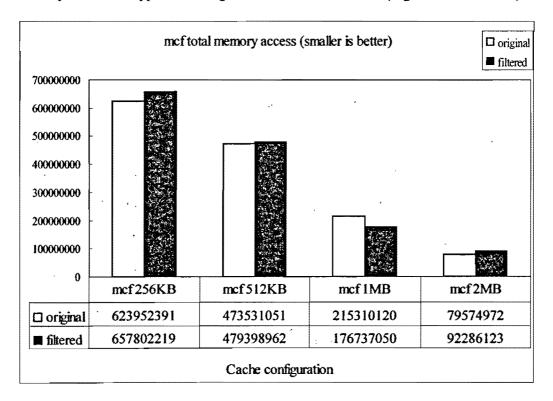

| 5.16 mcf total memory accesses                                                 | 5 |

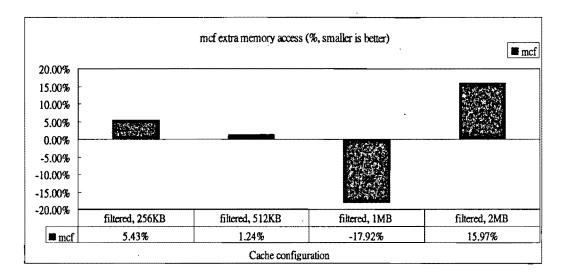

| 5.17 mcf extra memory access rate                                              | 6 |

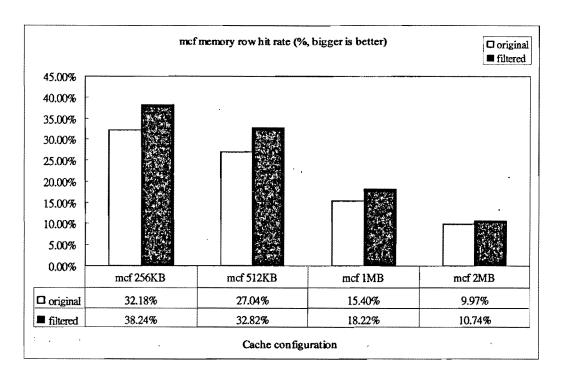

| 5.18 mcf memory row hit rate                                                   | 7 |

| 6.1 Performance improvement comparison between CF-LFU, no-spec-L2fill          |   |

| and spec-L2fillLRU9                                                            | 3 |

| 6.2 Performance improvement comparison between CF-LFU and Line                 |   |

| distillation                                                                   | 7 |

| 6.3 Performance improvement comparison between CF-LFU and prefetch filter      |   |

| for gcc                                                                        | 0 |

| 6.4 Performance improvement comparison between CF-LFU and prefetch filter      |   |

| for gzip                                                                       | 0 |

| A 1 A grin sim_outorder simulation output file                                 | 4 |

# Chapter 1

# Introduction

Over the years computer engineers and architects have been researching and developing new techniques to enhance computer performance. These technologies include increasing operating frequency of processor and memory, pipelining and developing superscalar architecture to exploit instruction-level parallelism(ILP), introducing multi-level cache system to hide the overgrowing memory latency, developing simultaneous multithreading (SMT) and multicore processors to harness the power of thread-level parallelism(TLP), etc.[1, 12 and 14]

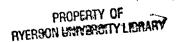

However, studies have revealed the fact that today's computer performance is not only governed by the amount of work performed per clock cycle of the processor, but also the amount of data bandwidth the memory subsystem can offer, which is inversely proportional to the latency of the memory system. According to [1 and 3], processor performance has been improving at a rate of 52% annually starting from the year 1986. However, the evolution of memory performance has only been maintaining at a steady pace of 7% per year since 1980. The industry noticed the issue of the growing performance difference between processors and memory and tried to solve this problem through various techniques.

Figure 1.1: The performance ratio comparing to 1980s baseline computer systems – the growing performance gap between processor and memory [1]

But as the performance gap between processor and memory keeps growing, modern processors will make more frequent stalls to wait for instructions and data to be transmitted from memory. Moreover, traditional solutions to solve the memory bandwidth/latency problem will also reach its physical limits so engineers must spare no efforts to reinvent more efficient way of utilizing the cache and memory systems, which is the main focus of this work.

# 1.1 List of Contributions and Objectives of the Research

The main objective of this thesis is to enhance the performance of Professor Mekhiel's patented work – Cache Filtering Method and Apparatus. The overall research contributions are summarized as follows:

- Studied modern computer programs' memory address usage pattern and established a relationship between cache pollution caused by single memory accesses and the concept of cache filtering.

- Illustrated the problem of cache pollution.

- Created a page interleaved DDR3 memory module for the SimpleScalar Simulator version 3.0d, which will be used to implement and test our cache filtering algorithm. Our memory module supports multi memory channels, multi memory banks, user configurable access latencies and allows easy extensions to other memory types (RDRAM, SDRAM, XDRRAM, etc.).

- Improved Professor Mekhiel's cache filtering algorithm by:

- Reinventing a new set of cache miss handling procedures to replace the original cache filtering scheme's procedures.

- Introducing a filter buffer to capture filtered data and prevent eviction of useful cache blocks.

#### 1.2 Motivation

We began our research by studying the memory address traces of some SPEC CPU 2000 component benchmarks. The traces were obtained from Brigham Young University Trace Distribution Center [15]. They are recorded from the first instruction to the 50 millionth instruction of the benchmarks. Through studying the address traces, we can learn history of addresses requests generated by the benchmarks from their initialization stage to middle of the execution.

We wrote a java program, which takes a memory address trace as an input file and counts the followings:

- The total amount of memory access requests generated within the instruction range;

- The total amount of unique memory addresses being requested for only once (single accessed addresses);

- The total amount of unique memory addresses being requested for more than once (repeated addresses);

- The total amount of times the program made accesses request to repeated addresses (repeated access).

The counting results and the average of the results are shown in the following tables:

Table 1.1: Total amount of memory access requests generated within execution range

| Apsi     | equake   | gcc      | mcf      | mgrid    |          |

|----------|----------|----------|----------|----------|----------|

| 10388240 | 10327879 | 10356038 | 10377283 | 10363629 |          |

| Parser   | perlmk   | swim     | twolf    | vortex   | average  |

| 9222144  | 10326311 | 9164118  | 10024960 | 10270839 | 10082144 |

Table 1.2: Total amount of single accessed addresses within execution range

| Apsi   | equake | gcc    | mcf    | mgrid  |         |

|--------|--------|--------|--------|--------|---------|

| 62231  | 52093  | 112909 | 58889  | 400161 |         |

| Parser | perlmk | swim   | twolf  | vortex | average |

| 86838  | 78304  | 316984 | 141746 | 344597 | 165475  |

Table 1.3: Total amount of repeated addresses within execution range

| Apsi   | equake | gcc    | mcf    | mgrid  |         |

|--------|--------|--------|--------|--------|---------|

| 112459 | 89547  | 175754 | 83503  | 475660 |         |

| Parser | perlmk | swim   | twolf  | vortex | average |

| 146835 | 113867 | 351524 | 211584 | 438342 | 219908  |

Table 1.4: Total amount of repeated accesses within execution range

| Apsi     | equake   | gcc      | mcf      | mgrid   |         |

|----------|----------|----------|----------|---------|---------|

| 10326009 | 10275786 | 10243129 | 10318394 | 9963468 |         |

| Parser   | perlmk   | swim     | twolf    | vortex  | average |

| 9135306  | 10248007 | 8847134  | 9883214  | 9926242 | 9916669 |

With the counting results available, we can calculate:

- the percentage of the average single accessed addresses;

- the percentage of the average repeated addresses;

- the percentage of the average single access;

- the percentage of the average repeated accesses.

Average total amount of unique memory addresses being requested within the execution range (total unique addresses):

Total unique addresses = average single accessed addresses + average repeated addresses

$$= 165475 + 219908 = 385383$$

Percentage of average single accessed addresses (average single accessed addresses %):

Average single accessed addresses % = (average single accessed address / total

unique addresses) x 100%

= (165475 / 385383) x 100% = 42.9%

Percentage of average repeated addresses (average repeated addresses %):

Average repeated addresses% = 100% - average single accessed addresses % = 100% - 42.9% = 57.1%

Average total amount of accesses to single accessed addresses (Average single accesses):

Average single access = average single accessed addresses = 165475

Percentage of average single access (average single access %):

Average single access % = (average single access / average total memory access) x 100%= (165475 / 10082144) x 100% = 1.6%

Percentage of average repeated access (average repeated access %):

Average repeated access % = 100% - average single access % = 100% - 1.6% = 98.4%

The calculations are indicating the 57.1% of repeated addresses are occupying 98.4% of the total memory accesses as they are being used for twice or more. The remaining 42.9% of memory addresses, contributing to only 1.6% of the total accesses, are being used for only once and they will be discarded by the benchmarks.

We believe that allowing the 1.6% of single accesses to enter the cache system will ultimately lead to degraded system performance because:

- they will cause cache pollution by replacing the frequently used data originally resides in the cache (to be discussed later);

- they will waste the valuable memory bandwidth to transmit them back and forth

from the main memory to the cache and vice versa as they will be accessed only

once and will soon be replaced by other cache blocks;

- they will also increase the memory row/page miss rate as those accesses will

break the normal memory accessing pattern, causing the memory to open another

rarely used page and to close the frequently used one.

#### 1.2.1 Cache pollution caused by rarely used data blocks

As cache is designed to provide high speed access to the processor, it will service any kind of access by loading the requested data and keeping the data in its cache blocks, in hope that the program will reuse the data in the future. The only problem with this approach is that it will cause a situation known as cache pollution, which is very expensive in terms of memory bandwidth and processor time as it destroys the cache's data locality (the word locality implies that when data is needed, it is already located at the cache). To explain the situation, we have included the following example:

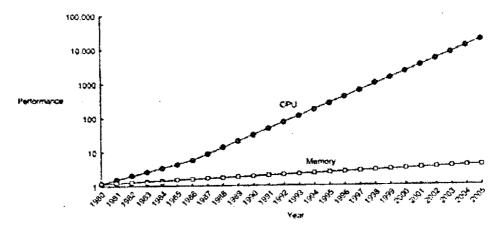

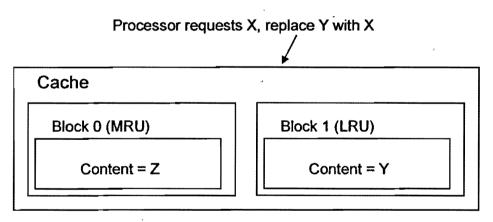

A computer has a small 2 way associative cache with 2 cache blocks and only 1 index, which implements the least recently used (LRU) cache replacement scheme, is executing a program. The program being executed makes frequent use of data located at addresses X and Y so the cache is fully occupied by those data.

Figure 1.2: Initial content of cache

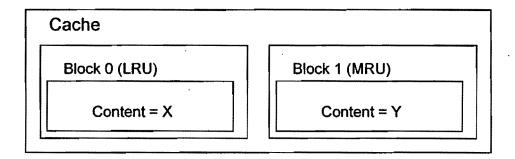

Figure 1.3: Cache miss forces cache to replace Block 0

Suddenly, the program makes request for a data from address Z, which will only be used once (or rarely used) throughout the program execution. Suppose the program had just accessed address Y, then the cache would have no space for the request of Z. It must replace cache block 0, which stores data at address X, by writing the content back to main memory and load data at address Z into the cache block.

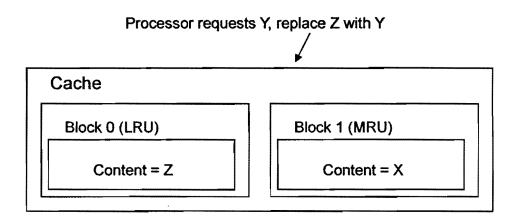

Figure 1.4: Cache content after replacing X with Z, program requests for X again causing another cache miss to replace block 1

After the program finishes using data at address Z, it resumes the regular pattern by first request for X then Y. This causes another two additional cache misses because the least recently used policy will first replace block 1 with data from address Y by data from X, then replace block 0 with data from address Z with replaced by Y.

Figure 1.5: Cache content after replacing Y with X, program requests for Y again causing another cache miss to replace block 0

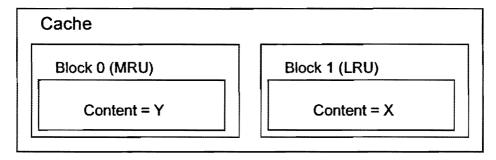

Note that each cache block replacement, depending on whether they have previously been modified or not, would require one to two memory accesses (writeback and loading) to service. Assuming all data accesses happened in this example were writes, address Z had caused three cache misses and six memory accesses to service such a request. Therefore, one can conclude that the access to address Z had polluted the cache's original content, consumed large amount of memory bandwidth, caused the processor to wait and yielded degraded performance.

Figure 1.6: Final cache content after replacing Z with Y

# 1.3 The organization of this thesis

With the motivation of this research properly defined, we will organize the following chapters to:

- introduce the SimpleScalar simulator tool set (Chapter 2);

- describe the design of the page interleaved DDR3 memory performance simulation module (Chapter 3);

- propose the cache filtering algorithm for least frequently used data (Chapter 4);

- simulation and discussion of the cache filtering algorithm for least frequently used data (Chapter 5);

- give an overview of the current technology related to cache filtering and compare

the performance gain of each technology (Chapter 6);

- Discuss the future work and conclusion (Chapter 7).

# Chapter 2

# Methodology

In this chapter, we will introduce the SimpleScalar Simulator tool set. The SimpleScalar Simulator tool set [12, 13 and 14] is a collection of many simulators written with the C language. Out of the many available simulators, we have chosen to evaluate our work on a simulator named sim-outorder.

Sim-outorder is a detailed simulator that can model a 32bit out-of-order execution superscalar processor. Out-of-order execution is a technique to boost processor performance by allowing the processor to, based on the availability of the processor's functional units, change the instruction execution order of a program. The approach is valid as long as the correctness of the data being processed is maintained and data are being written back to memory in the correct order.

Sim-outorder is also a performance simulator. That is, sim-outorder simulates by executing a compatible program binary/executable file like an ordinary computer, with an emulated processor, memory and hard disk (2GB of virtual memory). Throughout the simulation process, sim-outorder will collect performance statistics, such as cache hit rate and cycle per instruction (CPI), and display the information collected at the end of the simulation.

The SimpleScalar tool set also contains a number of simpler yet useful simulators, such as sim-fast, a simple processor functional simulator that does not have any error checking; sim-safe, a sim-fast equivalent with error checking capabilities; sim-cache, a simple cache simulator and sim-bpred, a branch predictor simulator.

Due to the nature of this work, we must briefly discuss how sim-outorder handles cache/memory access latencies. Sim-outorder was designed as a superscalar processor which has both instruction and data level 1 (L1) cache, optional separated or unified instruction and data level 2 cache and a main memory module.

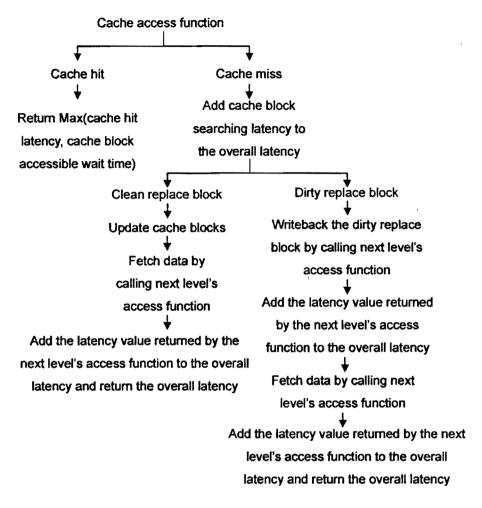

Access to each of the above mentioned components is modeled by calling the corresponding access latency calculation function in the simulator. For cache accesses, the level 1 cache latency calculation function (L1 latency function) will perform all cache access activities and return an integer value that can accurately represent the cache access latency in processor clock cycles.

If the data being requested is found in the cache, the L1 latency function will compare the cache hit latency with the time when the cache block is accessible (when the block is completely loaded from the next level) and return the bigger of the two values. In case of cache miss where accesses to the next level of the hierarchy (writeback and data loading) are required, the L1 latency function will update the cache blocks and call the next level's latency calculation function. Such a calling sequence will end when one of the following scenarios is reached – the requested data is found in any subsequent level or the data is not found in all cache levels and access to memory is needed. Once the cache miss situation is being properly serviced by calling the appropriate access functions, the L1 latency function will sum up all the latencies returned by the subsequent level latency calculation functions and return the sum as the latency of such cache access.

Figure 2.1: SimpleScalar cache access function work flow

Upon receiving the cache access latency, sim-outorder will generate a pipeline event. Pipeline event is a data structure which contains a register field and a time field. The register field in the pipeline event represents the destination of the data being loaded from or the source of the data being written to the cache. The time field is used to represent the clock cycle when the data loading or data writing is finished. It contains the value of T + latency of the cache access, where T is the clock cycle when the processor requests for the cache access. The pipeline event will be added to sim-outorder's event queue, which will be checked by sim-order in every simulated processor clock cycle. When the recorded clock cycle of the time field is reached,

the pipeline event will be deleted by sim-outorder. The instructions that are utilizing the register specified by the pipeline event will then be considered as ready to be executed by the processor.

Figure 2.2 shows the function calling sequence of one particular cache access. In this example, sim-outorder accessed certain data from data L1 cache by calling the L1 cache access function (function A). The access generated a cache miss in L1 and a writeback is required. Function A then called the L2 cache access function (function B) to writeback the replacing block. The writeback block was found in the L2 cache, therefore function B could simply update the L2 cache's content and return a latency to function A as part of the total access latency.

Figure 2.2: SimpleScalar cache and memory access function sample calling sequence L1 data loaded, return latency L1 Cache miss, L1 Cache miss, write back load data L1 cache access function (A) Cache hit, return L2 miss, clean block, load data L2 data loaded latency return latency L2 cache access function (B) Return latency Memory access function (C) time

After the writeback, function A must load data from the L2 cache, which caused a second call to function B. Unfortunately, that data load had also caused a cache miss in the L2 cache. This time, the L2 cache has a clean block and no writeback is needed. Therefore, function B must make a memory access by calling the memory access function (function C). At the end of function C's execution, the latency of loading the data from memory was calculated. This value would then be returned to function B and function A as part of the total accessing latency. Eventually, function A would sum up the writeback and data loading latencies and return the value to sim-outorder.

It is important to note that there exist several limitations in sim-outorder's memory hierarchy design. Firstly, when a writeback occurs, regardless it happens in the L1 or L2 cache, sim-outorder has an infinitely large write buffer with no access latency to temporarily store the cache block being written back. Hence, all cache and memory write actions will have an unrealistic latency of zero clock cycles.

Memory access latency = latency of first data column + (total amount of column to be accessed - 1) x latency of remaining column

In addition, sim-outorder's memory access latency calculation is relatively simple – the total memory access latency is equal to the latency of the first data column (including Tcmd, Trp, Trcd, Tcas, Tcwd and first column transmission) plus the latency of transmitting the remaining data columns multiplied by total amount of columns minus one (for the first column). From this formula, one can easily notice that sim-outorder's memory model is only valid when an outdated close page policy is used. Also, sim-outorder assumes memory accesses are always being scheduled to

be far apart, therefore no memory access will post any burden to the data bus and causes future accesses to wait for the current access to finish.

Lastly, as all component access functions must return an exact latency to sim-outorder, it is impossible to implement a memory module which supports access reordering. This is because memory access reordering requires all accesses to be added and sorted within a queue first. Therefore the memory module cannot calculate the access latency until the access order is confirmed.

To conclude, we have discussed some internal details of the SimpleScalar Simulator tool set. We hope that this information will allow one to easily understand the operation of the SimpleScalar Similator and the design of our cache filter and memory module. In the next chapter, we will discuss our page interleaved DDR3 memory module for the SimpleScalar Simulator.

# Chapter 3

# The Page Interleaved DDR3 Memory Module for the SimpleScalar Simulator

In this chapter, we will first discuss the software design of the page interleaved DDR3 memory performance simulation model (will be referred as memory model) for the SimpleScalar simulator. Second, we will describe the operation of the model. At the end of the chapter, we will also simulate the system.

The remainder of this chapter will be organized as follows:

- The software modeling of the memory model (Section 3.1);

- The operation of the memory model (Section 3.2);

- Simulation and discussion (Section 3.3).

## 3.1 The software modeling of the memory model

To properly design the memory model, we did a study of the memory address format and the virtual memory address space (hard disk) of sim-outorder. As mentioned in chapter 2, sim-outorder models a 32bit computer. The virtual address space, or the hard disk, of this computer is 2GB in size (address starts from hexadecimal 0x000000000 to 0x7fffffff, according to the memory.c from the simulator's source files). This address range is perfectly addressable with 32bits because the hexadecimal range of 32bits starts from 0x00000000 to 0xffffffff. Therefore, sim-outorder represents memory addresses with a md\_addr\_t enumerated data type (user defined data type), which is C language's unsigned int (unsigned integer) type. And if one also studies the machine definition of sim-outorder (machine.h), he/she

will notice that the virtual memory page size is defined as 4096 bytes (4KB).

We made two important decisions before we began the programming. First, we decided to directly map the 2GB of virtual memory space into 2GB of physical memory space with 4KB per memory row/page. This decision will greatly simplify the design of our memory model. Second, we decided to remove the infinite write buffer out of sim-outorder because of its unrealistic size and its zero access latency. In this context, sim-outorder must now wait for all cache/memory writebacks to complete and include the writeback latency in the latency calculations.

Our memory model has two components – the data and functional component. The data component, to be discussed in section 3.1.1, is the data structures that represent the memory hardware in the simulator. The functional component, covered in section 3.1.2, is used to describe the operation of the memory model.

#### 3.1.1 The data components of the memory model

The data component of the memory model is written in the memory.h source file of SimpleScalar. It defines the new data structures which are necessary for the memory model to operate properly. It includes:

- modification to the mem\_t data structure;

- a new channel\_t data structure;

- a new bank\_t data structure.

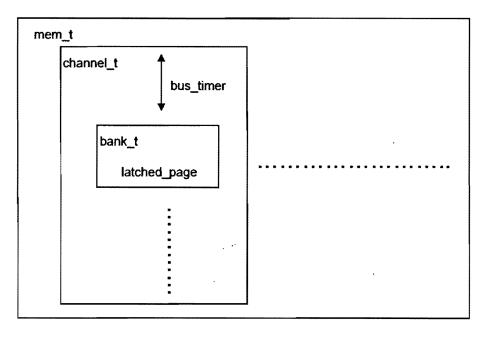

Figure 3.1: Graphical representation of the mem t data structure

#### Modification to the mem t data structure

A number of new data members were added to the mem\_t data structure. The most noticeable addition is a channel\_t pointer called channel. Channel is a pointer to a dynamically allocated array of channel\_t data structures. This array of channel\_t is used to represent one or multiple memory channels (the model can support up to two channels at this point).

Two floating point values known as mem\_to\_cpu\_clk and cpu\_to\_mem\_clk were also introduced to allow fast conversion between processor clock and memory clock. Given the clock speed of the processor and memory bus from the user input, the memory model will store the result of processor clock divided by the memory bus clock to mem\_to\_cpu\_clk. The cpu\_to\_mem\_clk, on the other hand, will hold the result of memory bus clock divided by the processor clock. To convert a value from memory clock to processor clock, the simulator can simply multiply the value with

the mem\_to\_cpu\_clk variable. A processor clock can also be converted easily by multiplying the value with the cpu to mem clk variable.

Following the floating point values are several 64bit integer values (C language's long long type):

- access\_count: a statistical value to store the total amount of memory access;

- unoverlaped\_fp\_read\_clk and unoverlaped\_fp\_write\_clk: statistical values to store the total amount of unoverlapped fast page read/write delay in processor clock (overlapped delay will be discussed in section 3.2);

- unoverlaped\_filtered\_read\_clk and unoverlaped\_filtered\_write\_clk: unused statistical values for debugging;

- unoverlaped\_random\_read\_clk and unoverlaped\_random\_write\_clk: statistical

values to store the total amount of unoverlapped random read/write delay in

processor clock.

Finally, there is a list of 32bit integer values (C language's int type) added to the mem t data structure to store:

- the data bus width in bytes (bus\_width);

- the total amount of memory channels (channels);

- bank –the total amount of banks per channel (bank);

- the column access strobe latency in memory clock cycles (Tcas);

- the row to column delay latency in memory clock cycles (Trcd);

- the row precharge latency in memory clock cycles (Trp);

- the burst length of the memory model (Tburst, a fixed value of 8 for DDR3);

- the write recover time in memory clock cycles (Twr);

- the rank to rank switching time and the data bus write to read switching time in memory clock cycles (Trtrs);

- the command duration time in memory clock cycles (Tcmd);

- the column write delay in memory clock cycles (Tcwd);

- the column to column delay in memory clock cycles (Tccd);

- the size of a bank(bank size);

- the memory mapping, only page interleaving is supported in the current implementation and other memory mapping can be added in the future (map type);

- the memory type, only DDR3 is supported in the current implementation but SDRAM can also be supported with minor changes to the code (mem\_type).

#### The channel t data structure

A new channel\_t data structure was introduced to represent a memory channel. The most important data member of the data structure is a bank\_t (to be discussed later) pointer. Same as the channel\_t pointer found in the mem\_t data structure, the bank\_t pointer points to a dynamically allocated bank\_t array to represent the collection of banks within a memory channel.

Following the bank\_t pointer is a SimpleScalar enumerated mem\_cmd data type variable known as previous\_command. According to the memory.h source file, the mem\_cmd enumerated data type is a flag to represent read or write memory commands/activities. The previous\_command variable was added to represent the previous bus activity, which is important for memory access latency calculations (to be discussed in section 3.2).

Two 32bit integer values, prev\_burst and prev\_accessed\_bank, were added to handle different memory access situations (to be discussed in section 3.2) during the latency calculation. The prev\_burst value keeps the amount of processor time taken to make the previous data transmission. The prev\_accessed\_bank holds the previous accessed bank number/array index. Also, it is important to note that the C language uses pointer arithmetic to access the array elements, therefore the indexes starts from 0 to size of the array – 1.

Finally, there is also a list of 64bit integer values from the channel\_t data:

- bus\_timer: the value recorded by this variable represents the processor cycle when the data bus of this memory channel will become idle.

- cmd\_timestamp: this value records the processor cycle when the last memory access command was issued by the memory controller.

- burst\_timestamp: a value used to represent the processor cycle when the last data transmission began.

- access\_count: a statistical value to record the total amount of memory access to the memory channel.

- actual\_transfer: a statistical value to keep the total amount of data columns being transferred by the memory channel.

- row\_hit: a statistical value to count the total amount of row hit happened in the memory channel.

- fp\_reads and fp\_writes: two statistical values to record the total amount of fast page read / write access to the memory channel.

- random\_reads and random\_writes: two statistical values to record the total amount of random read/write access to the memory channel.

- channel\_unoverlaped\_fp\_read\_clk and channel\_unoverlaped\_fp\_write\_clk: two

statistical values to hold the total amount of unoverlapped fast page read / write

delay in processor cycles.

- channel\_overlaped\_fp\_read\_clk and channel\_overlaped\_fp\_write\_clk: two

statistical values to record the total amount of overlapped fast page read / write

delay in processor cycles (overlapped delay will be discussed in section 3.2).

- channel\_unoverlaped\_random\_read\_clk and channel\_unoverlaped\_random\_

write\_clk: two statistical values to keep the total amount of unoverlapped random

read / write latency in processor cycles.

- channel\_overlaped\_random\_read\_clk and channel\_overlaped\_random\_write\_clk:

two statistical values to keep the record of the total amount of overlapped

random read / write latency in processor cycles.

- filtered\_reads, filtered\_write, channel\_overlaped\_filtered\_read\_clk, channel\_overlaped\_filtered\_write\_clk, channel\_unoverlaped\_filtered\_read\_clk and channel\_unoverlaped\_filtered\_write\_clk: unused statistical values for debugging purposes.

# The bank\_t data structure

The bank\_t data structure was defined to represent a memory bank of the memory model. There are only two values stored in the data structure – the latched\_page and the ras\_timestamp. The latched\_page variable is an unsigned integer value to represent the previously opened row of the memory bank. The ras\_timestamp is the record of the processor cycle when the last row precharge happened to the memory bank.

# 3.1.2 The functional components of the memory model

The functional component of the memory model was implemented in the memory.c source file. It has a number of functions and we categorized them into three classes: setter functions to initialize the values of the data components; memory access latency function to define how the memory model should operate and helper functions to aid latency calculations. In this sub-section, we will list and briefly describe the functions.

#### **Setter functions**

There are six setter functions to allocate and initialize the memory model's data structures, they are:

- set\_mem\_size: a function that dynamically allocates the channel\_t and bank\_t

data structure arrays and calculates the size of each memory bank based on the

user specified amount of memory channel/s and bank/s per channel.

- set\_bus\_width: a function that takes the user inputted memory data bus width (in bytes) and initializes the mem\_t data structure's bus\_width variable.

- set\_clk: this function takes the user inputted value for processor clock and memory data bus clock and compute the mem\_t data structure's mem to cpu clk and cpu to mem clk variables.

- set\_map: a function that takes the user inputted value for memory mapping and initializes the mem\_t data structure's map\_type variable. We intended to allow bank interleaving and cache line interleaving mode to be added in the future as extensions to the work, but in the current implementation, only page interleaving is supported.

Note: Some of the functions will have detailed explanation in section 3.2 as they are closely related to the operation of the memory model.

- set\_type: this function sets the mem\_type variable of the mem\_t data structure

with the user inputted value. This function was added to allow future memory

model extensions such as SDRAM and DDR4 to be added with minor code

modification.

- set\_latency: this function sets the following latencies with the user inputted values: Tcas, Trcd, Trp, Tras, Tburst, Twr, Trtrs, Tcmd, Tcwd and Tccd [2].

#### Memory access latency calculation function

The memory access latency function (memory\_access\_latency) was implemented to calculate the latency of a memory access, based on the current state of the mem\_t data structure. (refer to section 3.2.3 for more detail).

#### Helper functions

We have also defined some helper functions to aid latency calculations:

- max: max is a function to compare two integer values and return the bigger value of the two.

- is\_latched: given a starting address, its corresponding channel and bank, this

function returns a non-zero value if the address generates a row hit (the row of

the starting address is the same as the row being latched by the given channel's

bank), zero otherwise.

- get\_mem\_page: given a starting address, this function consults the page table and returns the physical memory page/row number which the address is located at (refer to section 3.2.2 for more detail).

- get\_mem\_actual\_bank: based on the page/row number received from get\_mem\_page, this function returns the physical bank number which contains the page (refer to section 3.2.2 for more detail).

get\_mem\_channel and get\_mem\_bank: these two functions will take the physical bank number returned by get\_mem\_actual\_bank and calculate the channel array index and bank array index of the mem\_t data structure respectively (refer to section 3.2.2 for more detail).

# 3.2 The operation of the memory model

In this section, we will discuss various aspects related to the operation of the memory model. These aspects include the overlapped memory access scheduling, memory addressing and most importantly, the memory access latency calculation.

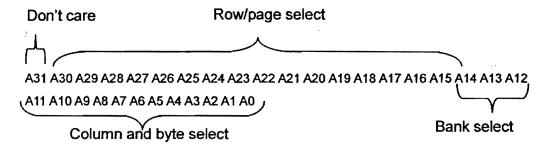

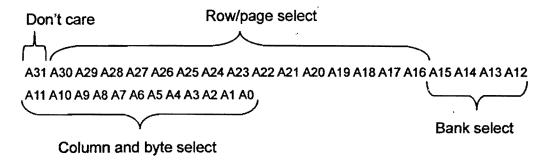

# 3.2.1 Overlapped memory access scheduling

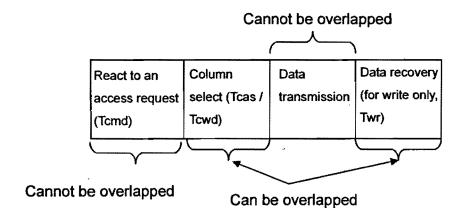

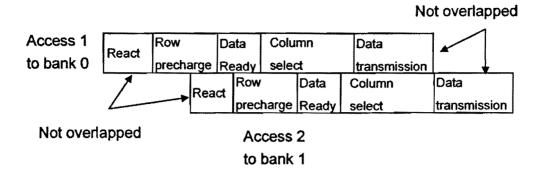

Back in section 3.1.1, several statistical variables from the mem\_t and channel\_t data structures to record the overlapped and unoverlapped access latencies were introduced. These latencies are related to a specific memory access scheduling technique known as the overlapped memory access scheduling [2]. In high speed memory systems with multiple banks, memory accesses can be pipelined into different phases. The phases are: react to an access request (Tcmd), row precharge (Trp), data ready (Trcd), column select (Tcas or Tcwd), data transmission and data recovery (Twr, for write only).

If the newly requested memory access is not reading from/writing to the same memory bank as the previous access, the memory controller can schedule the new access to start processing, up to the column selecting phase, before the previous access is completed (an example is shown in Figure 3.4). This type of scheduling is overlapped memory access scheduling as part of the memory accesses are being

overlapped. This is possible because row precharging and column selecting actions will not affect the previous access as they are utilizing different memory banks. But it is important to note that the command reaction and the actual data transmission can not be overlapped within a memory channel because each memory channel has only one data and command bus for data and command transmission.

Figure 3.2: The overlappable and unoverlappable phases of a random memory access

Figure 3.3: The overlappable and unoverlappable phases of a fast page memory access

Figure 3.4: Overlapped memory access scheduling example

# 3.2.2 Memory addressing

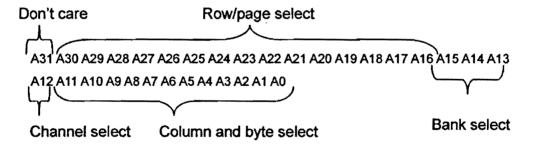

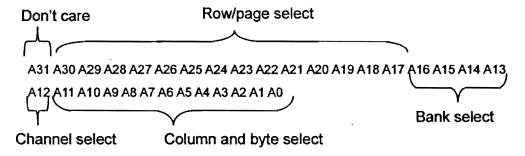

According to the DDR3 standards, a memory channel has at least 8 banks. With our memory model supporting 2GB of single and dual channel memory with up to 16 banks per channel, the memory address has the following formats:

# Dual channel, 8 banks per channel:

Figure 3.5: 32bit dual channel 8 bank memory address format

# Dual channel, 16 banks per channel:

Figure 3.6: 32 bit dual channel 16 bank memory address format

# Single channel, 8 banks:

Figure 3.7: 32 bit single channel 8 bank memory address format

# Single channel, 16 banks:

Figure 3.8: 32 bit single channel 16 bank memory address format

In our simulator, the decoding in the software can be achieved by either the logical approach (bit masking) or the mathematical approach (integer division and modulo). The benefit of the logical approach is the ease of implementation, but it is more restrictive as it requires the programmer to hard-code the bit masks. Keeping the future expendability of the simulator in our mind, we decided to take the mathematical approach and implemented the get\_mem\_page, get\_mem\_actual\_bank, get mem channel and get mem bank functions.

Upon receiving a memory address, the memory model decodes the address by first calling the get\_mem\_page function. This function has the following function signature:

unsigned int get mem\_page(struct mem\_t \*mem, md\_addr\_t addr);

The mem variable is a mem\_t pointer, which points to sim-outorder's mem\_t data structure. The second parameter, addr, is the target memory address to be translated into page/row number.

The get\_mem\_page function takes the requested address and search for the physical page number from the page table. The page number is formed by dividing the memory address with the page size (4096 Bytes). If the page is not found from the page table, the get\_mem\_page function will divide the value and return the result as the physical page number. Note that the physical page number is unique across the memory space, the memory model can simply take the physical page number as the row identifier with the mathematical approach.

With the physical page number available, the memory model calculates the physical bank number where the address located at with the get\_mem\_actual\_bank function. This function has the following function signature:

int get\_mem\_actual\_bank(struct mem\_t\* mem, md\_addr\_t addr);

The addr value is the memory address that needs to be converted to a physical bank number.

The get\_mem\_actual\_bank function takes the remainder of the division between the physical page number and the multiplication result of total amount of channel and amount of banks per channel.

Physical bank number = physical page number MOD (total amount of channels \*

total amount of banks per channel)

Since page interleaving distributes memory rows/pages in a zigzag manner across the banks and channels, he memory model must further process the physical bank number with the get\_mem\_channel and get\_mem\_bank functions to obtain the channel number and the bank number of the channel.

The get\_mem\_channel function has the following function signature:

int get\_mem\_channel(struct mem\_t\* mem, int bank);

The get\_mem\_channel function calculates the channel number by taking the remainder of the physical bank number divided by the total amount of channels.

Channel number = physical bank number MOD total amount of channels

Note: The bank variable is the physical bank number returned by the get\_mem\_actual\_bank function.

Similarly, the get mem bank function has the following function signature:

int get mem bank(struct mem t\* mem, int bank);

The get\_mem\_bank function calculates the bank number of the channel by dividing the physical bank number with the total amount of channels.

Bank number of a channel = physical bank number / total amount of channels

We have included the following address conversion example with 4 memory channel and bank configurations to prove that our mathematical memory address decoding method is correct for all memory configurations:

Suppose the memory address to be accessed is 366882:

The binary form of 366882 is:

#### 000000000000101100110010010010

Following the bit naming convention from Figure 3.7, for single channel 8 banks:

The column and bank select bits are A11 to A0, which are "100100100010";

The bank select bits are A14 to A12, which are "001";

The row select bits are A30 to A15, which are "000000000001011".

Therefore, we expect this address belongs to bank 1.

Using our mathematical approach:

Physical page number = address / page size (4KB)

= 366882 / 4096 = 89

Note: the mathematical approach uses the C language's integer division and modulo operations.

Therefore both the division result and the remainder will be integers.

Physical bank number = physical page number MOD (total amount of channel \*

total amount of banks per channel)

= 89 MOD (1 \* 8) = 89 MOD 8 = 1

Channel number = physical bank number MOD total amount of channels

= 1 MOD 1 = 0

Bank number = physical bank number / total amount of channels

= 1/1 = 1

By applying the mathematical approach to the single channel 8 bank scenario, the result is bank 1. Therefore we can conclude that the result of mathematical approach matched the logical approach's result.

# Single channel 16 banks:

The column and bank select bits are A11 to A0, which are "100100100010";

The bank select bits are A15 to A12, which are "1001";

The row select bits are A30 to A16, which are "000000000000101".

Therefore, we expect this address belongs to bank 9.

Using our mathematical approach:

Physical page number = address / page size (4KB)

= 366882 / 4096 = 89

Physical bank number = physical page number MOD (total amount of channel \*

total amount of banks per channel)

= 89 MOD 16 = 9

Channel number = physical bank number MOD total amount of channels

= 9 MOD 1 = 0

Bank number = physical bank number / total amount of channels

= 9/1 = 9

By applying the mathematical approach to the single channel 16 bank scenario, the result is bank 9. The result of our mathematical approach is matching the logical approach's outcome again.

#### Dual channel 8 banks:

The column and bank select bits are A11 to A0, which are "100100100010";

The channel select bit is A 12, which is "1";

The bank select bits are A15 to A13, which are "100";

The row select bits are A30 to A16, which are "000000000000101".

Therefore, we expect this address belongs to channel 1's bank 4.

Using our mathematical approach:

Physical page number = address / page size (4KB)

= 366882 / 4096 = 89

Physical bank number = physical page number MOD (total amount of channel \*

total amount of banks per channel)

= 89 MOD (2\*8) = 89 MOD 16 = 9

Channel number = physical bank number MOD total amount of channels

= 9 MOD 2 = 1

Bank number = physical bank number / total amount of channels

= 9/2 = 4

By applying the mathematical approach to the dual channel 8 bank scenario, the result is channel 1's bank 4. Therefore mathematical approach is also valid with the dual channel 8 bank configuration.

#### Dual channel 16 banks:

The column and bank select bits are A11 to A0, which are "100100100010";

The channel select bit is A 12, which is "1";

The bank select bits are A16 to A13, which are "1100";

Therefore, we expect this address belongs to channel 1's bank 12.

Using our mathematical approach:

Physical page number = address / page size (4KB)

= 366882 / 4096 = 89

Physical bank number = physical page number MOD (total amount of channel \*

total amount of banks per channel)

= 89 MOD (2 \* 16) = 89 MOD 32 = 25

Channel number = physical bank number MOD total amount of channels

= 25 MOD 2 = 1

Bank number = physical bank number / total amount of channels

= 25 / 2 = 12

Finally, by applying the mathematical approach to the dual channel 16 bank scenario, the result is channel 1's bank 12, which is matching our expected results. Through the proving process similar to mathematic induction, we conclude that our mathematical memory address decoding method is correct for all memory configurations.

Note: For the remainder of this document, we will refer to each of the memory latencies mentioned in section 3.1.1 by their short form (e.g. command duration time = Temd)

# 3.2.3 The memory access latency function

The memory\_access\_latency function models the memory operations, calculates the latency of each access and returns the value to sim-outorder. The function signature of memory\_access\_latency is shown below:

unsigned int memory\_access\_latency(struct mem\_t\* mem, int chunks, md\_addr\_t addr, enum mem cmd cmd, tick t now);

The mem parameter is a mem\_t pointer which points to the mem\_t data structure of sim-outorder. The second parameter, chunks, is the total amount of bytes the processor/cache is requesting for the memory access (in sim-outorder, it is the L2 cache block size since the L2 cache is the only cache that requests for memory access). The addr parameter is the first address which the processor/cache is requesting. The last parameter, now, is the processor cycle when the processor/cache requested for the memory access.

# The algorithm behind the memory access latency function

Before the description of the algorithm begins, one must note that the latency value returned by memory\_access\_latency is not simply the sum of the timing parameters (Tcmd, Trp, Trcd, Tcas, Tcwd and data transmission), but a latency relative to the 'now' parameter. That is, the value returned by the function can be significantly larger than the sum of those timings. This is caused by the fact that when the processor/cache requests for a memory access, the memory model can either be idle or busy servicing the pervious access/s. If the memory is servicing another access, it must wait for the previous access to complete before servicing the current access.

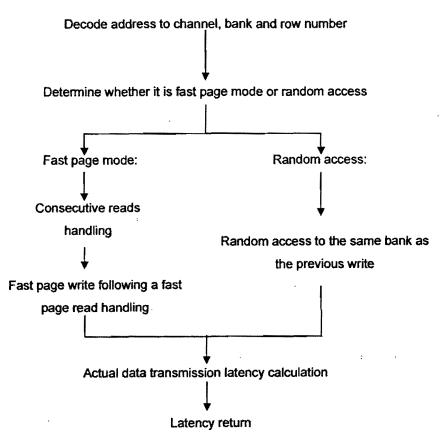

The most important goal of the memory\_access\_latency function (latency function) is to calculate the earliest possible starting processor cycle (start time) for the memory access requested by the processor/cache. When the latency function is called, it will first call the get\_mem\_actual\_bank, get\_mem\_bank, get\_mem\_channel and is\_latched functions to determine whether the access is a random type or fast page type.

Once the access type is determined, the latency function will check whether the access is the first memory access of the simulation (bus\_timer = 0). If so, the start time can simply be set as "now" and the access type will be limited to random access (the first access of a simulation has to be random access. Also, when the mem\_t data structure is initialized, the latched row/page of all memory banks is set as row 0, so we must override the result of the is latch function).

If the access is not the first access of the simulation, the latency function compares the value of the "now" parameter with the channel's previous command start time (cmd\_timestamp + Tcmd) and takes the larger value as the temporary start time. This is because an access cannot start earlier than the previous access. Note that the temporary start time will be increased (shifted further away from "now") as the function handles other situations.

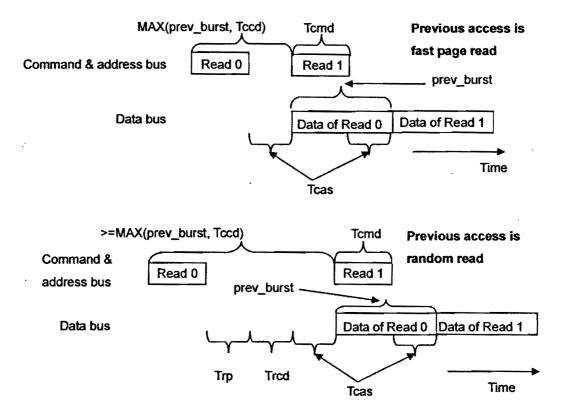

If the access type was previously determined as *fast page mode*, the latency function will store the sum of the corresponding timing parameters (Tcmd + Tcas for read OR Tcwd for write) to an integer variable "latency" and detect the following situations:

#### Consecutive reads

If the previous access is a read operation and the current access is also a read, the function will first compare the value of the previous data transmission time (prev\_burst from channel\_t data structure) and the column to column delay (Tccd) and store the larger value of the two values to a temporary variable known as "temp". The latency function will then ensure the minimum distance between the current read's start time and the previous read's start time is "temp" by incrementing the temporary start time of the current access. This action allows sufficient time for the memory to complete the data transmission and column selection.

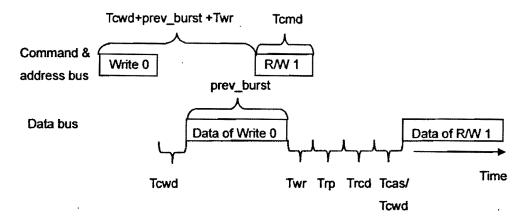

Figure 3.9: Consecutive read timing (current access is fast page read)

## Fast page write following a fast page read

If the previous access is a fast page read and the current access is a write, the latency function must ensure the timing distance between the previous read and the current write is Tcas + Trtrs + Tcwd + prev\_burst. Note that the Trtrs is added as a timing bubble to eliminate the conflict with the internal data movement of the read access.

Figure 3.10: Write following a fast page read timing (current access is fast page write)

If the latency function determined the access type is random access, the function will store the sum of the corresponding timing parameters (Tcmd + Trp + Trcd + Tcas for read OR Tcwd for write) to the "latency" variable and record the latched row/page to the bank's latched\_page variable. Also, if the latency function determines the current memory access is the first access of the simulation, it will skip the following start time calculation and jump to the actual data transmission latency calculations.

Because random accesses require a row precharge, the latency function must check the last ras\_timestamp of the bank. If the timing difference between temporary start time and the last ras\_timestamp (temporary start time - ras\_timestamp) is less than the value of the Tras of the mem\_t data structure, the latency function will increment the temporary start time with the value: Tras - (temporary start time - ras\_timestamp).

## Random access to the same bank as the previous write

After handling the Tras timing requirement, the latency function checks whether the previous access was accessing the same memory bank and the access was a write. If so, the memory must allow a minimum timing distance of Twr to allow the row latch to write the updated values back to the memory cells.

Figure 3.11: Random access to the same bank as the previous write timing

When the latency function finishes calculating the temporary start time of the current access, it will begin the actual data transmission latency calculations and record the followings:

- The bank number of the current access to the prev\_bank variable of the channel\_t

data structure;

- The temporary start time of the current access to the cmd\_timestamp variable of

the channel\_t data structure and to the ras\_timestamp of memory bank (if row

precharge needed);

- The current access command (Read or Write) to the previous\_command variable

of the channel\_t data structure;

- The time when data transmission begins (cmd\_timestamp + "latency") to the burst\_timestamp variable of the channel\_t data structure;

#### Actual data transmission latency calculation

The actual data transmission latency calculation starts by dividing the "chunks" parameter with the mem\_t data structure's bus\_width variable to obtain the total amount of data columns to be transmitted. Once the total amount of data columns is determined, the latency function will divide the amount by two and store the result to a temporary variable known as access\_transfer (DDR3 memory can transmit twice per memory clock and transmit one data column per transmission).

At this point, the latency function is still in terms of memory clock cycles. Therefore the latency function will convert the result to processor clock cycles by multiplying the values ("latency" and access\_transfer) with mem\_t's mem\_to\_cpu\_clk variable. With every value converted to processor clock cycle, the latency function will store the value of access\_transfer to the channel's prev\_burst variable for future latency calculations. The latency function will also store the value of start time + "latency" + access\_transfer to the bus\_timer variable of the channel because the data bus will be busy until the newest memory access (the current access) finishes.

Finally, the last action of the latency function is to calculate the memory access latency that is relative to the "now" parameter. This is completed by returning the value of bus timer – "now".

Figure 3.12: memory\_access\_latency function work flow

# 3.3 Simulation and discussion

In this section, we will perform a memory channel and bank test to verify our memory module's behavior under different memory channel and bank settings. In this test, we will use the gcc benchmark from the SPEC CPU 2000 benchmark suite for the simulations and monitor the system performance and memory row hit rate under the following memory configurations:

- 1 channel 4 banks;

- 1 channel 8 banks;

- 2 channels 2 banks (4 banks in total);

- 2 channels 4 banks (8 banks in total);

- 2 channels 8 banks (16 banks in total).

Note that we will set all of the simulation settings, except the cache and memory related settings, with the default settings of sim-outorder. Also, our cache settings will be consistent among each sub-section to allow precise comparison between data points. Finally, as mentioned in section 3.1, our custom version of sim-outorder does not include the write buffer and memory access reordering capabilities.

# Simulation settings

Table 3.1: Simulation settings for channel and bank test

| Instruction L1 cache size                         | 32KB                |

|---------------------------------------------------|---------------------|

| Data L1 cache size                                | 32KB                |

| L1 cache latency                                  | 1 processor clock   |

| L2 cache size                                     | IMB                 |

| L2 cache latency                                  | 10 processor clocks |

| Cache block size                                  | 64B                 |

| L1 cache set associativity                        | 4                   |

| L2 cache set assocaitivity                        | 8                   |

| Custom DDR3 memory model's memory bus speed (MHz) | 800 (DDR3 1600)     |

| Amount of memory banks                            | 4, 8                |

| Amount of memory channels                         | 1,2                 |

| Tcas, Trcd, Trp, Tras (memory clocks)             | 7, 7, 7, 21         |

| Trtrs, Tcwd, Tcmd, Twr, Tccd (memory              | 1, 7, 1, 5, 4       |

| clocks)                                           |                     |

| Our DDR3 memory model's processor clock (MHz)     | 3200                |

Note: To verify the statistical values generated by our custom sim-outorder, we have also included a sample simulation output file verification in appendix A.2 on page 127.

# Row hit rates and row hit improvement

#### Row hit rates

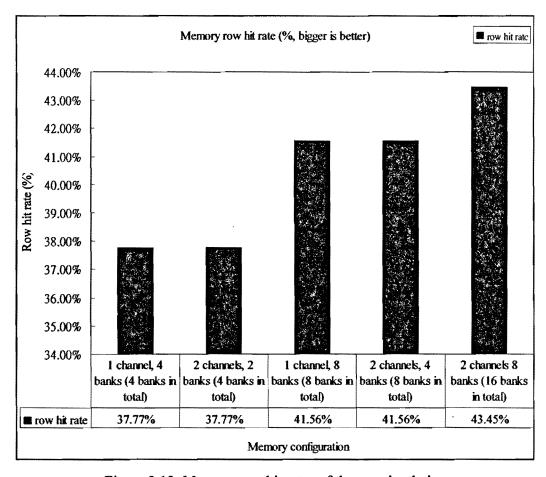

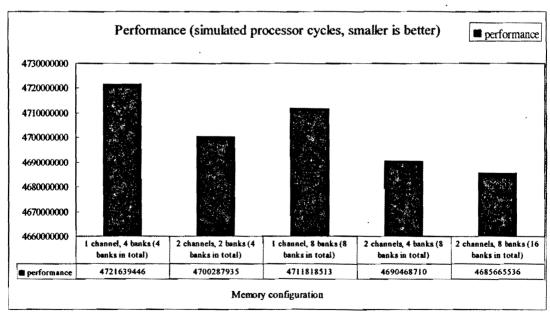

Figure 3.13: Memory row hit rates of the gcc simulation

Note: Please note that there has never been any DDR3 memory being manufactured with only 2 and 4 memory banks. Therefore, the simulations with 2 and 4 memory banks are never intended to reflect real world memory performance; instead, they are only used to illustrate the behavior of the memory row hit rate when the total amount of memory banks is being doubled. Finally, when considering the row hit rates of the multi channels setups, we must take the average row hit rate across the channels as the overall memory row hit rate.

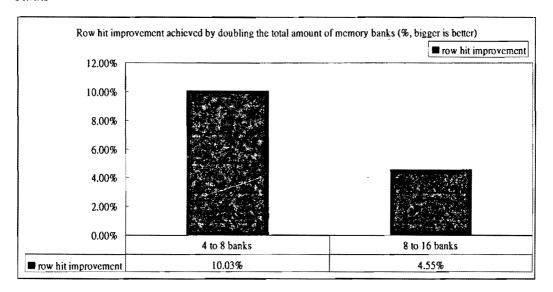

Memory row hit rate improvement achieved by doubling the total amount of memory banks

Figure 3.14: Row hit improvement when total amount of memory banks is doubled From the row hit rate plot, one can notice the followings:

- The row hit rate improvement is not sensitive to the total amount of memory channels;

- The row hit improvement of doubling the total amount of memory banks (from 1 channel 4 banks OR 2 channels 2 banks to 1 channel 8 banks OR 2 channels 4 banks respectively) is consistent.

- The row hit rate improvement tends to drop as the total amount of memory banks increase.

The first and the second facts are the most important findings to prove our memory module is able to generate consistant results amoung different memory configurations - regardless the total amount of memory channels, if the total amount of memory banks is fixed, the memory row hit rate and memory row hit improvement should be consistent because the application's degree of locality is constant.

To explain the third finding, one can consider the multi bank main memory as an index of a set associative cache where the total amount of memory banks is the set associativity and each row latch is a cache block. If one keeps increasing the associativity or the memory bank count, it will eventually reach the limit of the set associative or multi bank design where additional set / bank will not benefit the overall hit rate. Therefore the row hit rate improvement will not double as the total amount of memory banks doubles. Instead, the row hit rate improvement should be a function of total amount of memory banks and the application's degree of locality. Hence it should converge to a value as the total amount of available row latches reaches the limit of the program's memory row request limit.

# Simulated performance and performance comparison under different memory configurations

Simulated performance

Figure 3.15: gcc simulated performance

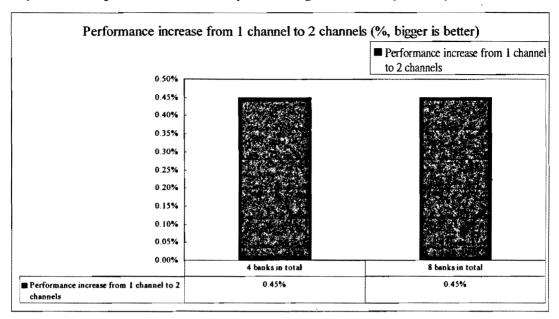

# Performance improvement achieved by increasing the amount of memory channels

Figure 3.16: gcc performance improvement achieved by increasing the amount of memory channels

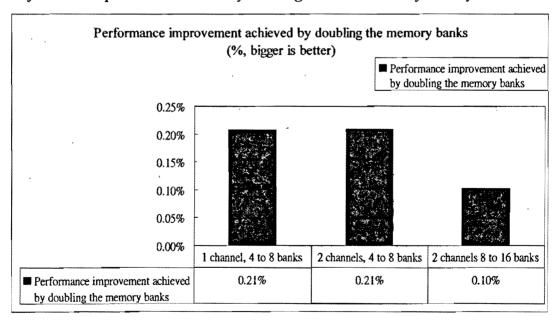

# Performance improvement achieved by doubling the total amount of memory banks

Figure 3.17: gcc performance improvement achieved by doubling the total amount of memory banks

From the performance plots, we have made the following observations:

- The performance gain of adding an additional memory channel is much bigger than doubling the amount of total memory banks;

- Regardless of the total amount of channels, the performance gain of doubling the total amount of memory banks from 4 to 8 is consistent;

- The benefits of doubling the total amount of memory banks are diminishing if one compares the improvement from 4 to 8 banks and from 8 to 16 banks.

The first finding can be considered as the benefit of an extra memory data bus. With an additional memory data bus, the average amount of access to each data bus is reduced. Therefore, the average amount of memory access wait time caused by incomplete previous memory accesses can be reduced, yielding better performance than simply doubling the total amount of memory banks per memory channel.

The second and third observations are, once again, proofs of the relationship between the total amount of memory banks and the limit of the multi memory bank design. As the row hit rate of the configurations with a total 4 memory banks should be consistent, one should expect to see the same amount of performance improvement achieved by doubling the total amount of memory banks, regardless the amount of memory channels present in the system. Also, due to the fact that there exists a row hit improvement limit in the multi memory bank design, it is reasonable to have decaying performance benefit of as we continue doubling the total amount of memory banks.

To conclude, we have designed and tested our DDR3 memory model for the SimpleScalar simulator which is capable of producing consistent simulation results under different simulation configurations. Our DDR3 memory model has the following feature set:

- Support up to 2 memory channels and 16 memory banks;

- Support any reasonable input of processor clock speed, memory bus speed and memory latencies;

- Generate consistent results amount different memory configurations.

# Chapter 4

# The Cache Filtering Algorithm for Least Frequently

# **Used Data**

In this chapter, we will propose the cache filtering algorithm for least frequently used data (cache filter algorithm). This algorithm allows the cache to identify and filter out rarely used and non-previously used memory addresses.

The remainder of this chapter will be organized as follows:

- The background;

- The baseline system's memory hierarchy characteristics;

- The cache filtering algorithm and the components;

- Simulation and discussion.

# 4.1 The background

Our cache filtering algorithm builds on the basics of two patented works. The first work, Cache Filtering Method and Apparatus [21], provided us important insights about how does the memory row hit signal can be used to identified previously used memory rows/pages and addresses. And the second work, Methods and Apparatus for Accelerating Retrieval of Data from a Memory System with Cache by Reducing Latency [22], had given us a hint about the possibility of using a small buffer to hold non-previously used and rarely used data. After serious considerations and modifications to the two works, we were able to combine them together and harness their strengths.

Our cache filtering algorithm makes use of a small buffer to store the filtered cache blocks and determine whether a cache block is frequently or previously used by checking:

- the content of the buffer AND

- the memory row/page hit signal generated by the memory controller

# 4.2 The baseline system's memory hierarchy characteristics

We decided to take the simulated system from section 3.3 as our baseline system to implement the cache filtering algorithm. Therefore we will assume our baseline system to have the follow memory hierarchy characteristics:

- 2 level cache hierarchy (separated instruction L1 cache and data L1 cache);

- No write buffer;

- No memory access reordering.

# 4.3 The cache filtering algorithm and its components

To ensure the data being fetched to the cache hierarchy are frequently/previously used, we will only allow data to be fetched to the cache hierarchy from the following sources:

- the L2 cache (only applicable to the L1 cache);

- the filter buffer;

- an opened memory row/page.

The remaining access types that are not allowed to enter the cache hierarchy stored in the filter buffer. These accesses include:

- fetches that causes a miss in all L1 cache, L2 cache, filter buffer and memory rows/pages;

- writebacks from data L1 cache to L2 cache that causes a L2 cache miss;

- all L2 writebacks.

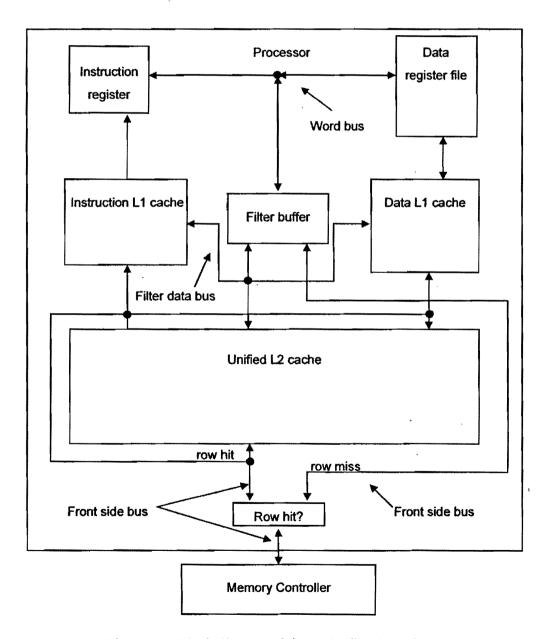

Figure 4.1: Block diagram of the cache filtering scheme

Figure 4.1 shows the block diagram of the cache filtering scheme. This diagram shows the major components of the cache filtering algorithm: instruction register, data register file, instruction L1 cache, data L1 cache, L2 cache and the filter buffer.

# 4.3.1 The instruction register (IR) and data register file (DRs)