16980487

# FIVE-LEVEL NPC INVERTER FED BY DUAL 18-PULSE RECTIFIER FOR HIGH-POWER DRIVES

by

**Zhongyuan Cheng**

### Bachelor of Engineering, Xi'an Jiaotong University, China

A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

**Master of Applied Science**

in the Program of

**Electrical and Computer Engineering**

Toronto, Ontario, Canada, 2005

©(Zhongyuan Cheng) 2005

. . . .

#### UMI Number: EC53010

#### All rights reserved

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

# UMI®

UMI Microform EC53010 Copyright 2008 by ProQuest LLC All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

# Author's Declaration

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholar research.

and the state of the second states

an production in the second second

ii

. .

S ...

# **Borrower's Page**

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

| Name | Address  | Signature | Date      |

|------|----------|-----------|-----------|

|      | ·        |           |           |

|      |          |           |           |

|      |          |           |           |

|      |          |           |           |

|      |          |           |           |

|      |          |           |           |

|      |          |           |           |

|      |          |           |           |

|      |          |           |           |

|      |          |           |           |

|      |          |           |           |

|      |          |           |           |

|      | <u> </u> |           |           |

|      |          |           |           |

|      |          | ·····     |           |

|      |          |           |           |

|      |          |           | <u> </u>  |

|      |          |           |           |

|      |          |           | 1         |

|      |          |           |           |

|      | <u> </u> |           | <u> </u>  |

|      |          |           | +         |

|      |          |           | 1         |

|      |          |           |           |

|      |          |           | <u> -</u> |

|      |          |           |           |

|      |          |           |           |

# Five-Level NPC Inverter Fed by Dual 18-Pulse Rectifier for High-Power Drives

Master of Applied Science

2005

Zhongyuan Cheng Electrical and Computer Engineering Ryerson University, Canada

## ABSTRACT

This thesis focuses on the topology of multi-pulse rectifiers and the modulation technique of multilevel inverters for high-power medium voltage drives. A dual 18-pules rectifier topology is proposed. The topology achieves harmonic performance of 36-pulse rectifiers by using relatively simple 18-pulse transformers. It can also neutralize the 5<sup>th</sup> and 7<sup>th</sup> harmonics caused by unbalanced secondary windings. Moreover, a novel space vector modulation (SVM) algorithm with flexible three-segment switching sequence is proposed for multilevel inverters. It features: 1) minimized device switching frequency, 2) lower weighted total harmonic distortion due to the increase of the inverter sampling frequency, and 3) easy implementation thanks to the simplified sequence design. The algorithm is applicable to various multilevel inverter topologies.

Theoretical analyses and computer simulations are carried out for the proposed topology and algorithm. The harmonic performance is verified by experiments on a 10kVA 5-level NPC/H-bridge inverter fed by a dual 18-pulse rectifier.

iv

# ACKNOWLEDGEMENTS

The work presented in the thesis was carried out at the Laboratory of Electric Drive Research and Application (LEDAR) at Ryerson University.

First of all, I would like to thank Professor Bin Wu for his continuous and paramount support and help during the period when I studied at Ryerson. The precious advices and numerous discussions triggered insightful research and enhanced my academic knowledge and scientific inspiration.

I am grateful to Professor Richard Cheung, Professor David Xu, Dr. Congwei Liu and all the fellow students at LEDAR for their support and friendly atmosphere. My appreciation also goes to Mr. Jim Koch for his help in preparing the gating boards, and Mr. Murat Kaya for his assistance in the experiment.

My sincere gratitude is extended to the engineers of the Power Electronic Group of Rockwell Automation Canada for the beneficial discussions and technical meetings.

I would like to share the joy of achievements with my families, my wife Susan and our little Claire. I am very grateful for my dear wife's long-time understanding and support.

•

V

# TABLE OF CONTENTS ADDIS TO DEPOS

.

| CHAPTER 1 INTRODUCTION                                                                                                                                          | 1  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 Overview                                                                                                                                                    | 1  |

| 1.2 Multi-Pulse Rectifiers                                                                                                                                      | 2  |

| 1.3 Multilevel Inverters                                                                                                                                        | 5  |

| 1.3.1 NPC Inverters<br>1.3.2 NPC/H-Bridge Inverters                                                                                                             | 7  |

| 1.4 High-Power MV Drives                                                                                                                                        |    |

| 1.5 Space Vector Modulation of Multilevel Inverters                                                                                                             | 11 |

| 1.5.1 SVM for Two-Level Inverters<br>1.5.2 The Application of SVM for Multilevel Inverters                                                                      | 14 |

| 1.6 Motivation and Objective                                                                                                                                    |    |

| 1.7 Thesis Organization                                                                                                                                         |    |

| CHAPTER 2 DUAL 18-PULSE RECTIFIER                                                                                                                               | 19 |

| 2.1 Principle of Harmonic Cancellation                                                                                                                          |    |

| 2.2 Reduction of Secondary Windings                                                                                                                             |    |

| 2.3 Dual-18 Pulse Rectification                                                                                                                                 | 24 |

| 2.3.1 Topology<br>2.3.2 Harmonic Cancellation                                                                                                                   |    |

| 2.4 Applications                                                                                                                                                |    |

| <ul> <li>2.4.1 Configuration of the DC Output</li> <li>2.4.2 Harmonic Neutralization Between Two Drives</li> <li>2.4.3 Other Application Concerns</li> </ul>    |    |

| 2.5 Simulation: Waveforms and Spectra                                                                                                                           |    |

| 2.5.1 Ideal Transformers                                                                                                                                        |    |

| 2.6 Summary                                                                                                                                                     |    |

| CHAPTER 3 SPACE VECTOR MODULATION                                                                                                                               |    |

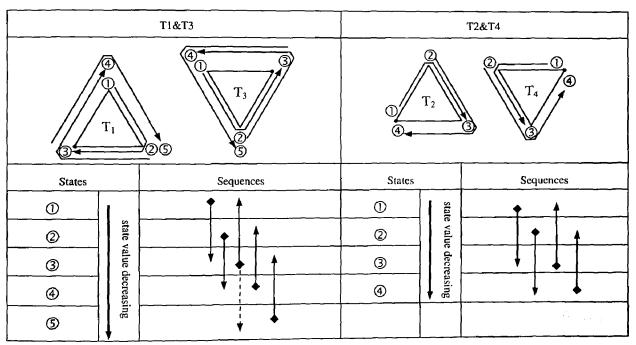

| 3.1 Simplification of Switching Sequence Design                                                                                                                 |    |

| <ul><li>3.1.1 Switching Sequence Reproduction</li><li>3.1.2 Sequence Design by Triangle Types</li></ul>                                                         |    |

| 3.2 Seven-Segment SVM for NPC/H-Bridge Inverters                                                                                                                | 40 |

| <ul><li>3.2.1 Selection of the Redundant Switching States.</li><li>3.2.2 Design of Seven-Segment Switching Sequence.</li><li>3.2.3 Typical Waveforms.</li></ul> |    |

| 3.3 SVM with Flexible Three-Sgement Sequence                                                                                                                    |    |

| <ul><li>3.3.1 Split Sequence and Inverter Sampling Frequency</li><li>3.3.2 Extra Switchings</li></ul>                                                           |    |

-

.

| 3.3.3 Design of Three-Segment Switching Sequence                                    |     |

|-------------------------------------------------------------------------------------|-----|

| 3.3.3.1 Principle of Minimization of Device Switching Frequency                     |     |

| 3.3.2 Arrangement of Switching Sequence                                             | 53  |

| 3.3.3.3 Selection of the First Leading State                                        |     |

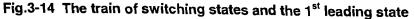

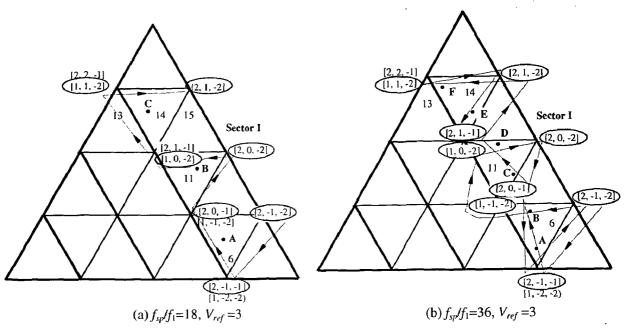

| <ul><li>3.3.4 Examples of Three-Segment Sequence</li><li>3.3.4 Simulation</li></ul> |     |

| 3.4 Comparative Study                                                               |     |

|                                                                                     |     |

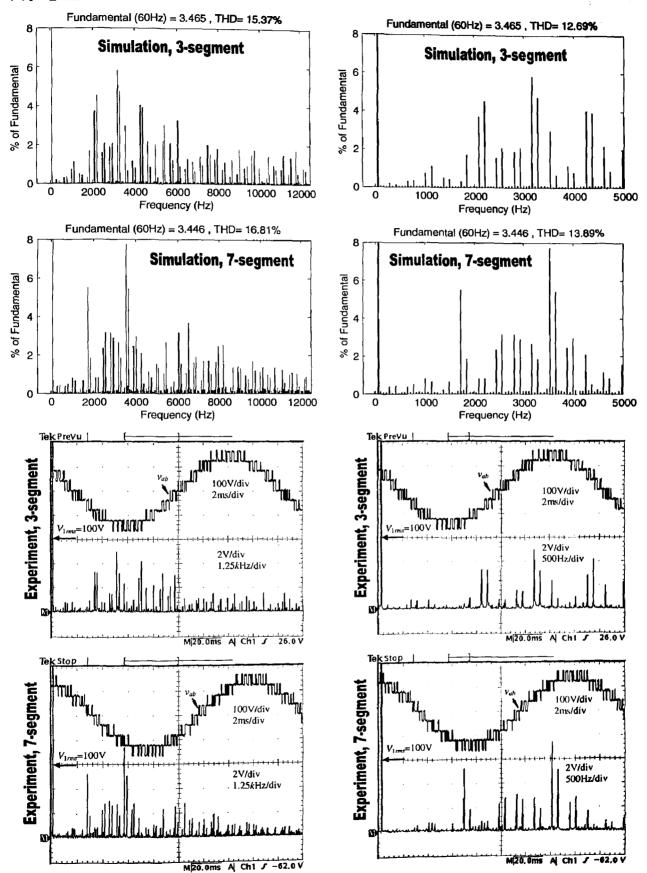

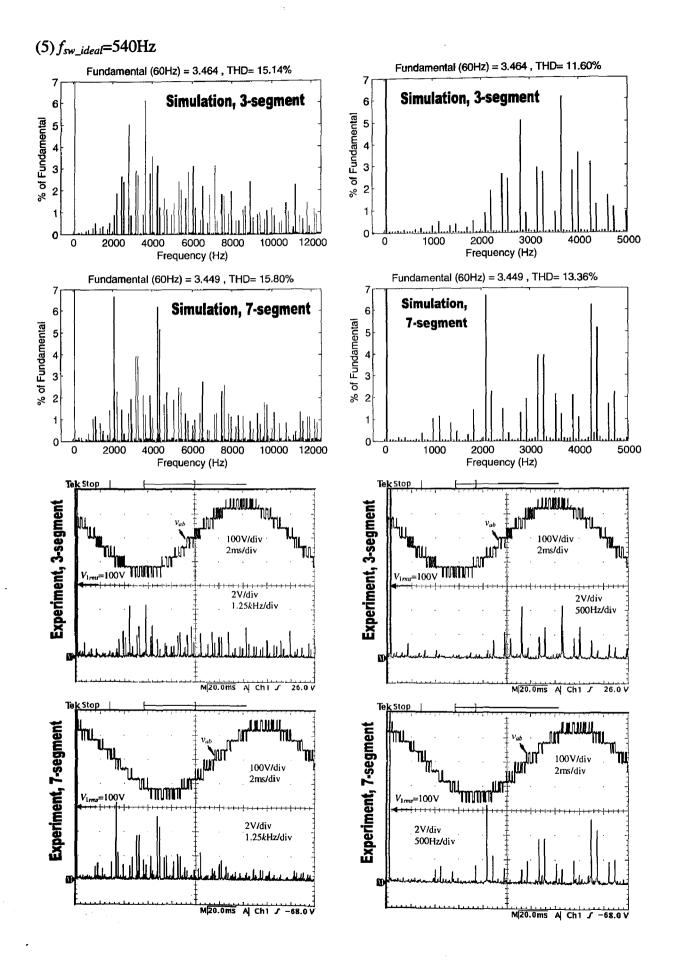

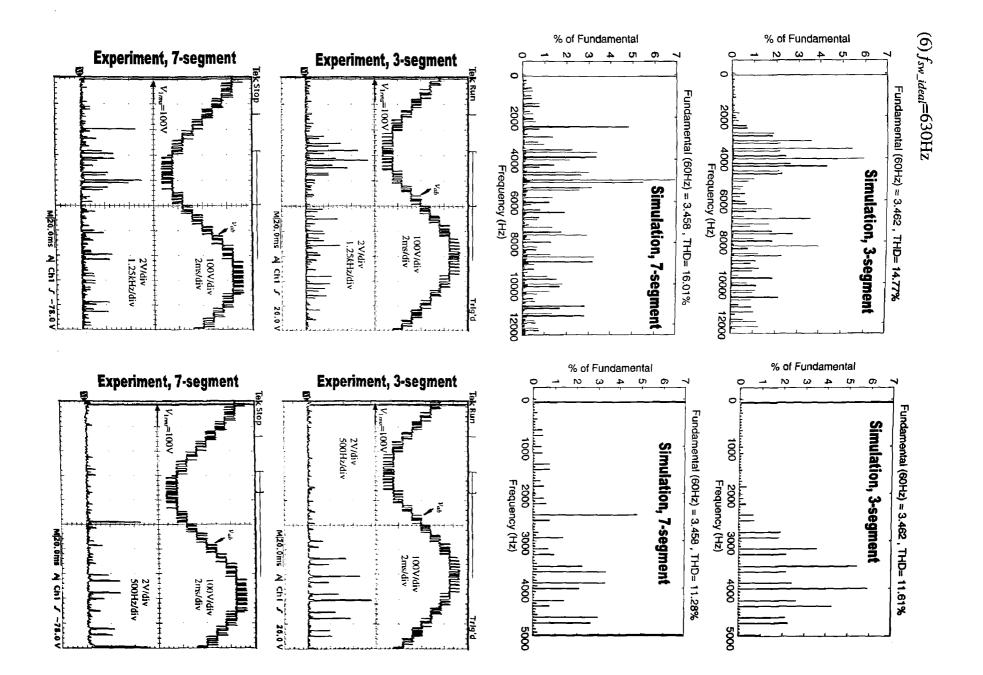

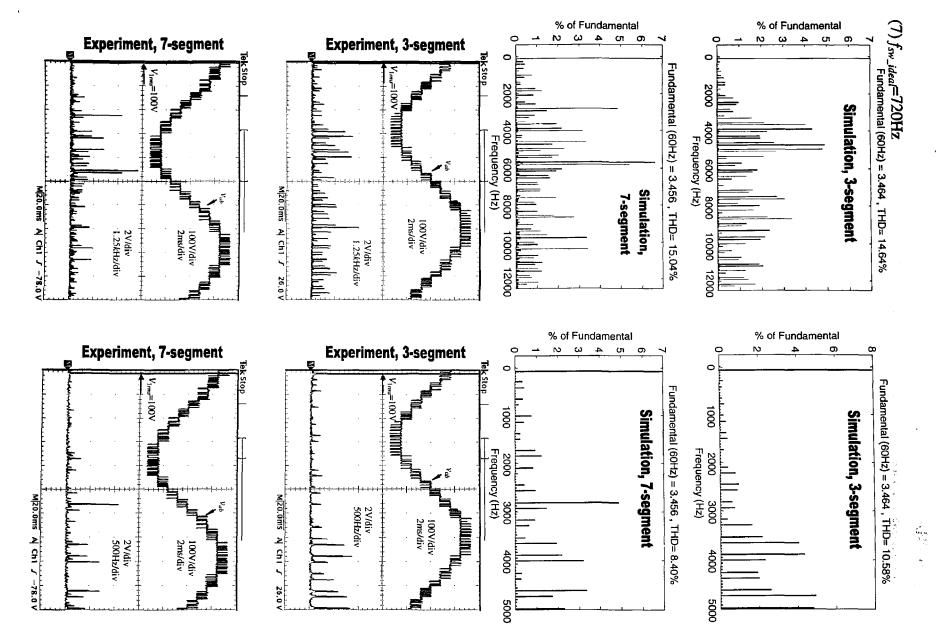

| 3.4.1 Simulation Conditions<br>3.4.2 Waveforms                                      |     |

| 3.4.3 Spectra, THD and WTHD                                                         |     |

| 3.4.4 Gating Pattern and Device Switching Frequency                                 | 63  |

| 3.5 Application of 3-Segment SVM to 9-Level Inverters                               |     |

| 3.6 Summary                                                                         |     |

| CHAPTER 4 EXPERIMENTS                                                               | 67  |

| 4.1 Experiment Setup                                                                |     |

| 4.1.1 System Configuration                                                          |     |

| 4.1.2 Planning and Testing of the Transformers                                      | 70  |

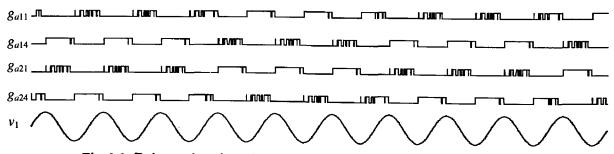

| 4.1.3 State Decoder for NPC/H-Bridge.                                               |     |

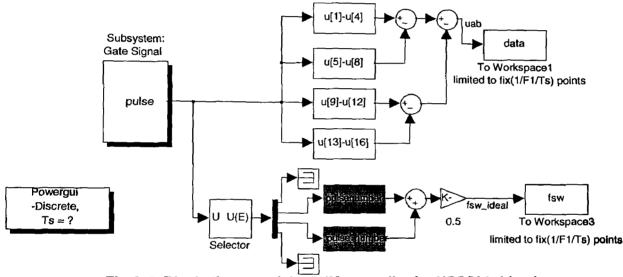

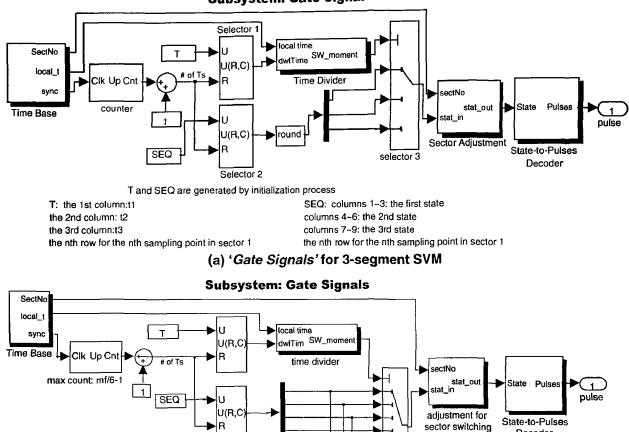

| 4.1.4 Simulink/RTI Model for the Controller                                         | 74  |

| 4.2 Experiment Results                                                              | 75  |

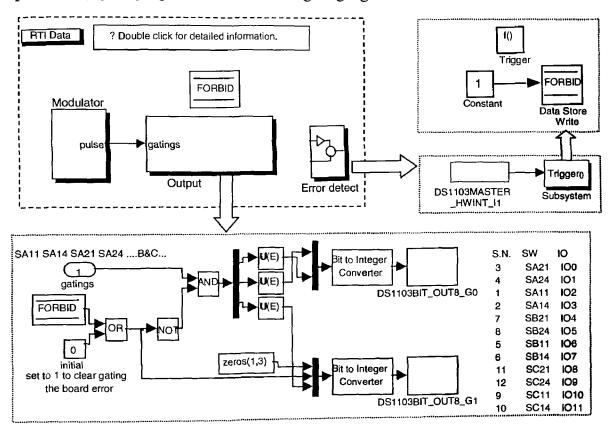

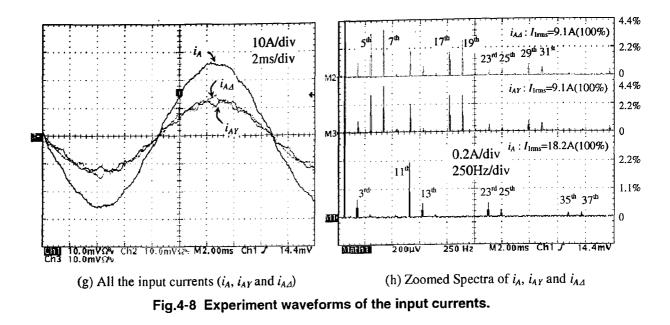

| 4.2.1 Input Current of the Rectifier                                                | 75  |

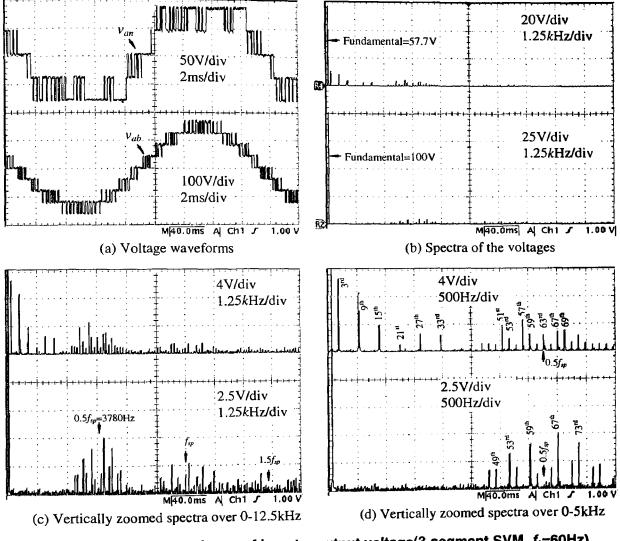

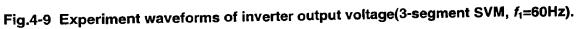

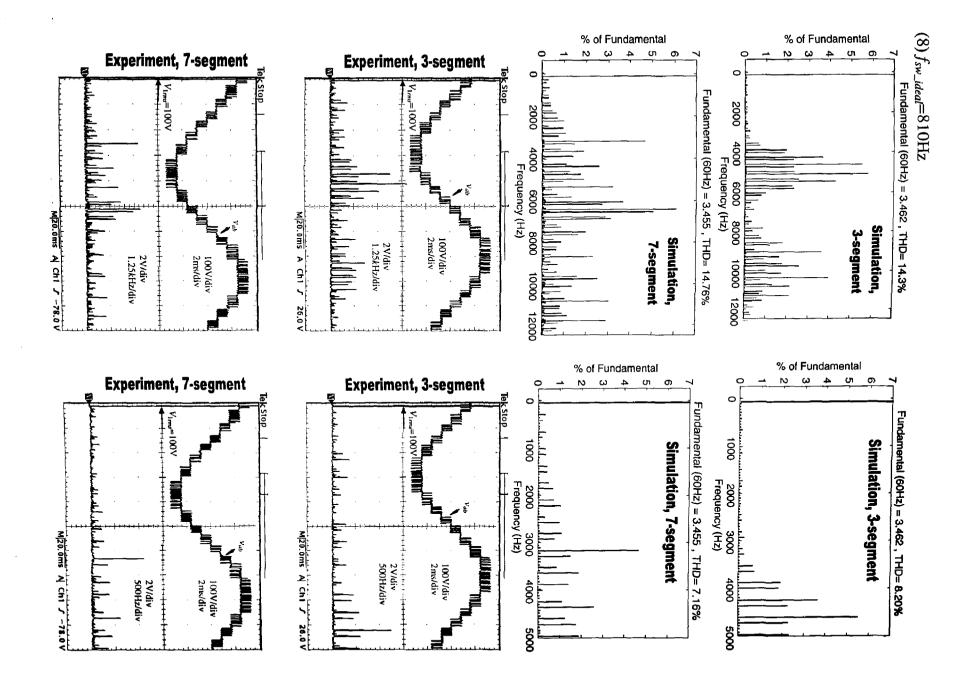

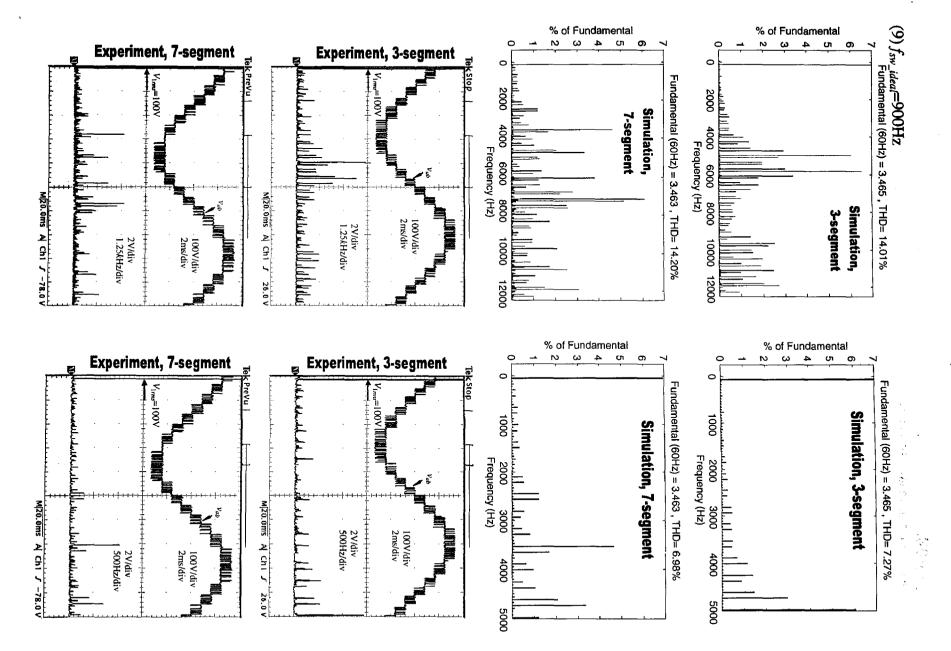

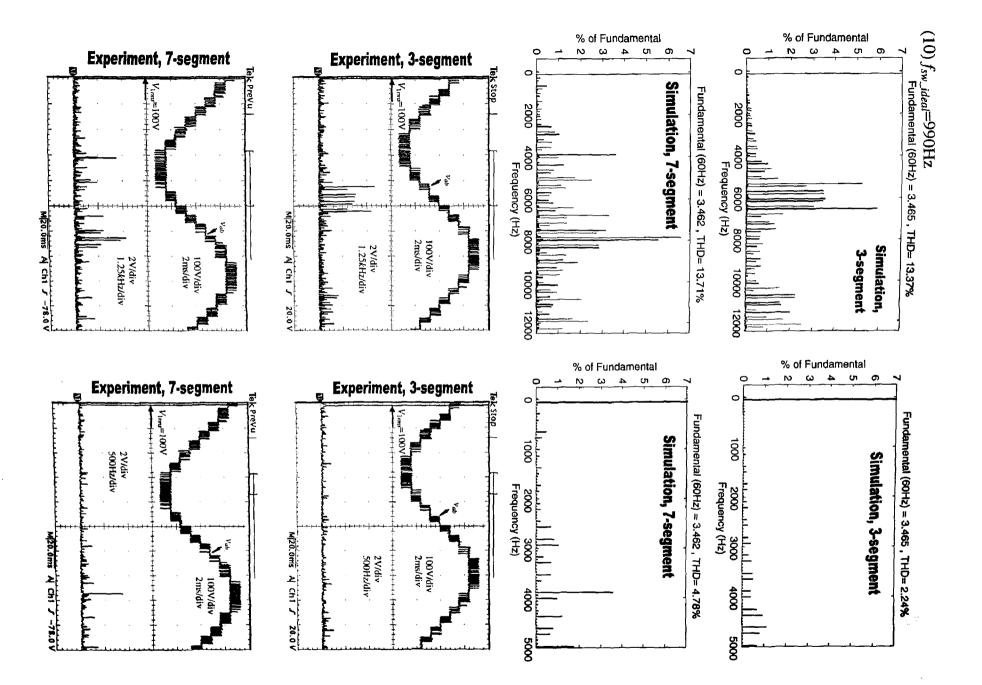

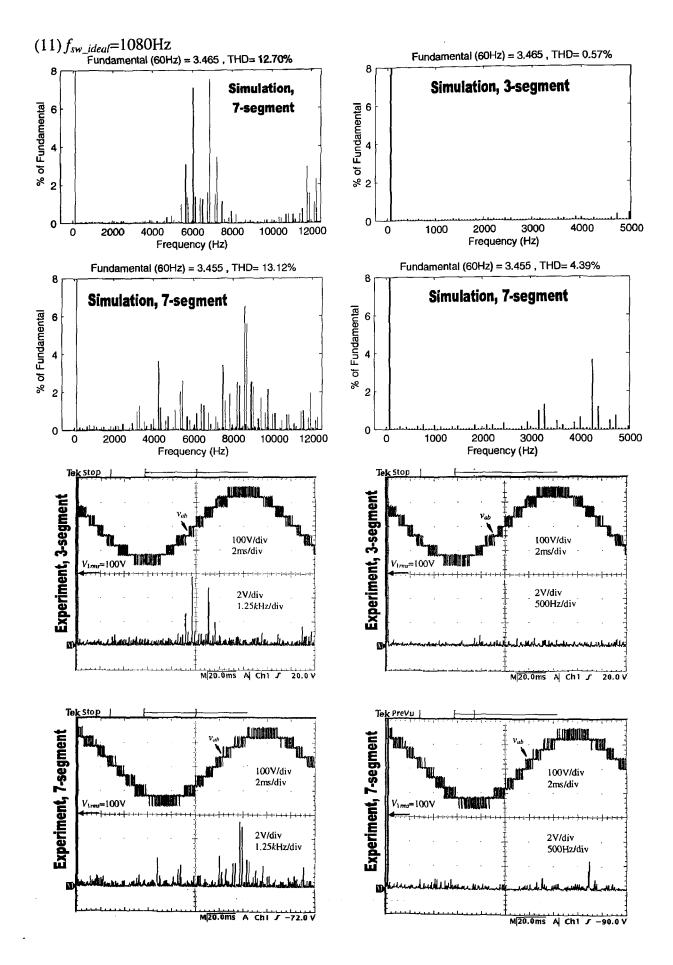

| 4.2.2 Output voltage of the Inverter                                                | 78  |

| 4.3 Summary                                                                         |     |

| CHAPTER 5 CONCLUSIONS                                                               | 83  |

| APPENDIX                                                                            | 87  |

| 1. SVM computation in hexangular coordinates                                        |     |

| 2. Simulink models of SVM algorithms                                                |     |

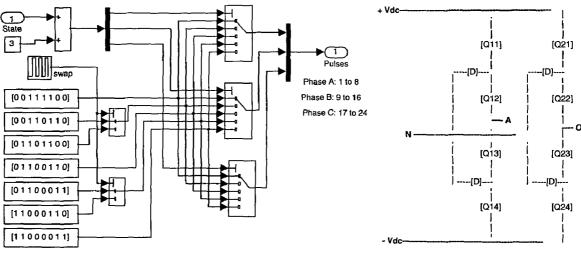

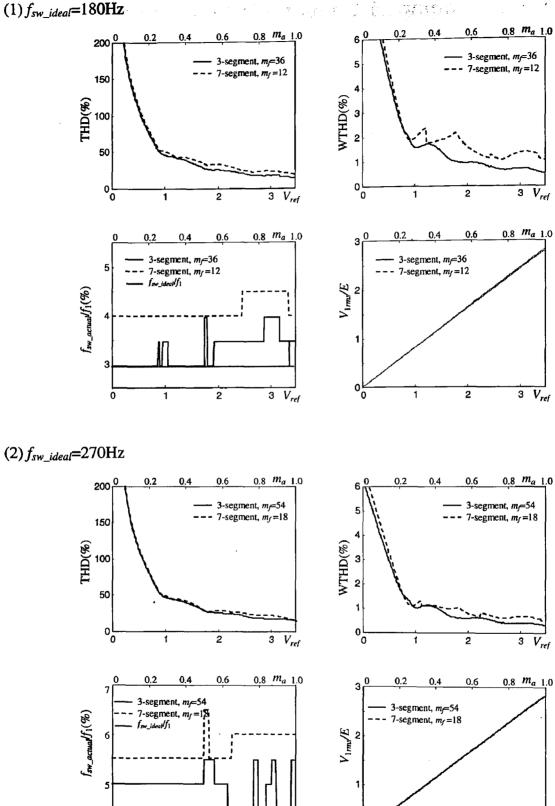

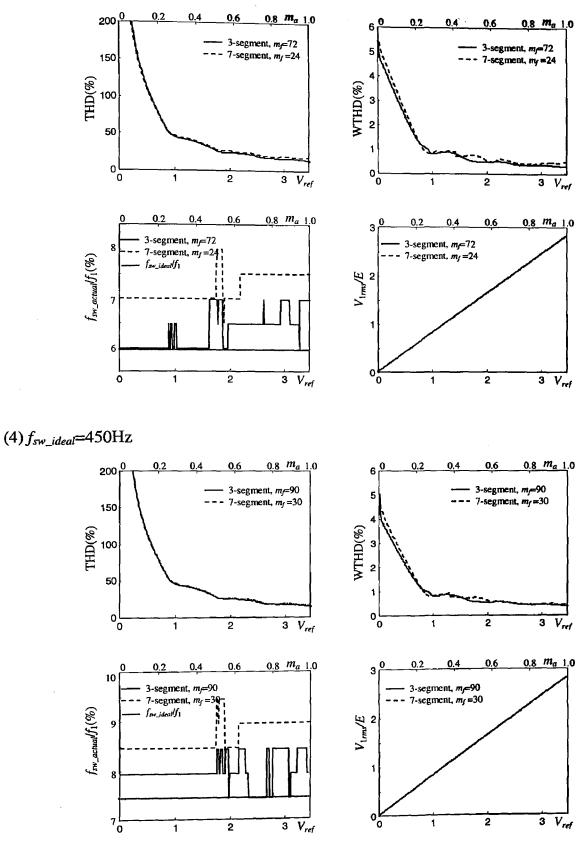

| 3. Performance comparison for various $m_a$ and $f_{sp}$                            |     |

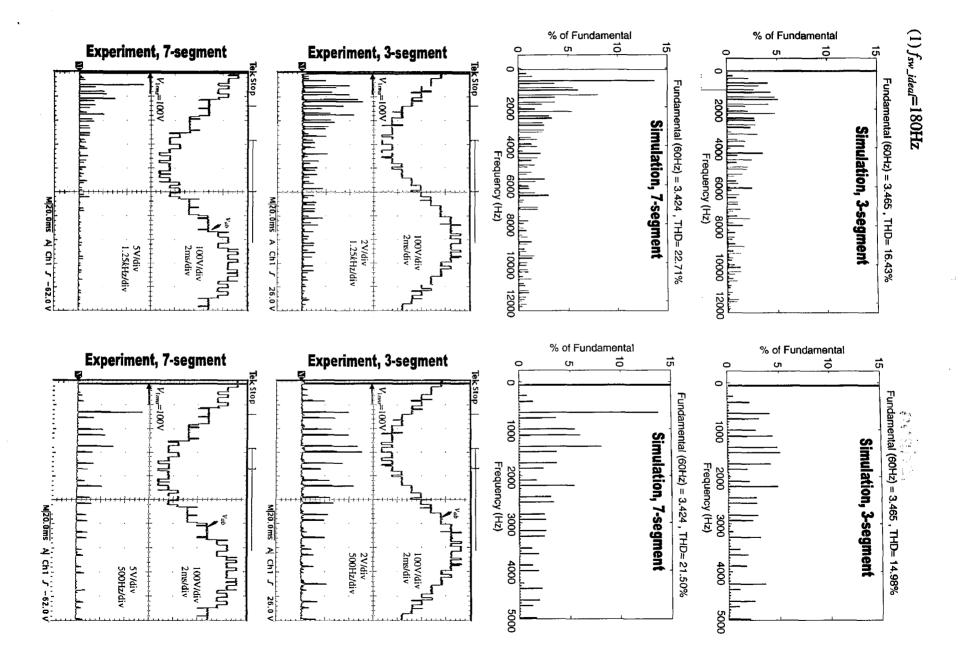

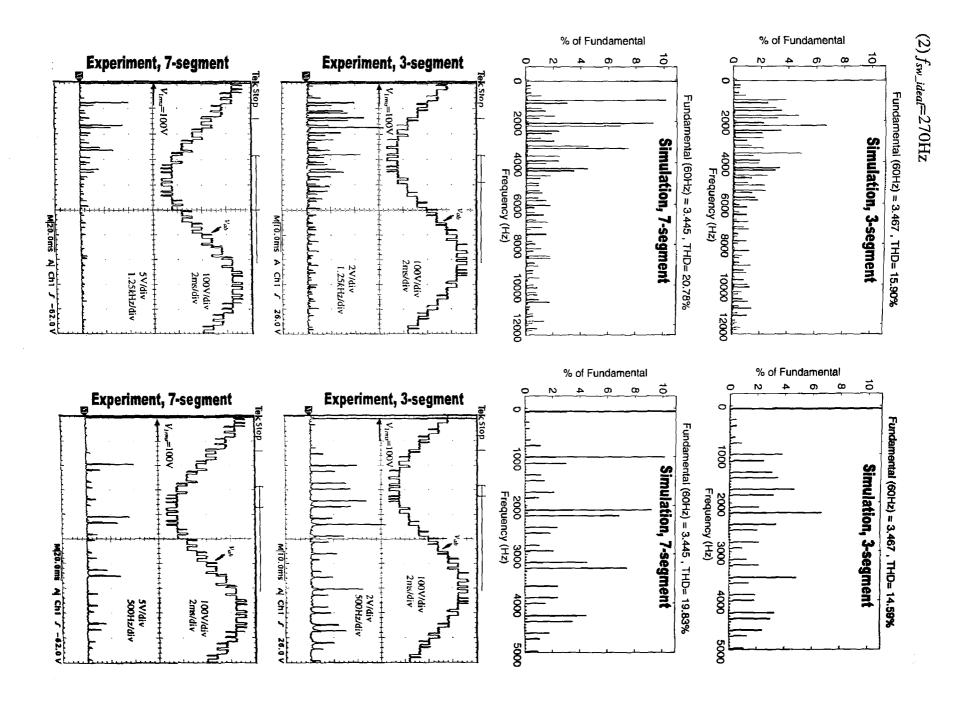

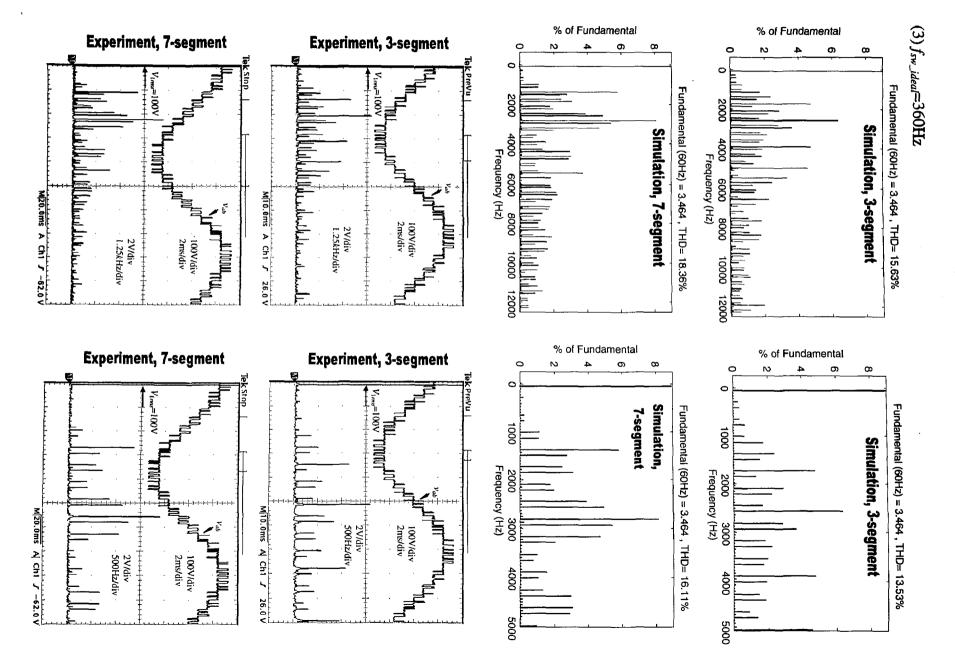

| <ol> <li>Spectra comparison</li> </ol>                                              |     |

| 4. Spectra comparison                                                               |     |

| REFERENCE                                                                           | 117 |

• ,

# LIST OF FIGURES

~

.

-

•

a e contra que la significa a traca fina e su co

٠

•

| Fig.1-1 General topology of MV motor drives.                                       | 1  |

|------------------------------------------------------------------------------------|----|

| Fig.1-2 Topology of 12-pulse rectifier                                             |    |

| Fig.1-3 Current waveforms and spectra of 12-pulse rectifier                        |    |

| Fig.1-4 Topology of 18-pulse rectifier                                             |    |

| Fig.1-5 Three-level NPC inverter                                                   |    |

| Fig.1-6 Five-level NPC/H-bridge inverter.                                          |    |

| Fig.1-7 Topology of MV drives fed by 5-level CHB inverter                          |    |

| Fig.1-8 Topology of 7-level CHB inverter fed MV drives                             |    |

| Fig.1-8 Topology of 5-level NPC/H-bridge inverter fed MV drive                     |    |

|                                                                                    |    |

| Fig.1-10 Circuit diagram and vector plot of a 2-level inverter.                    | 12 |

| Fig.2-1 Circuit model of a 6-pulse rectifier fed by a PST                          |    |

| Fig.2-2 Topology of 36-pulse 5-level NPC/H-bridge inverter fed drive.              |    |

| Fig.2-3 Topology of dual 18-pulse rectifier                                        |    |

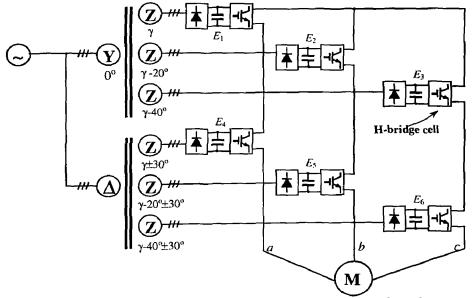

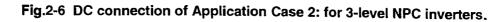

| Fig.2-4 DC connection of Application Case 1: for 5-level CHB inverters.            |    |

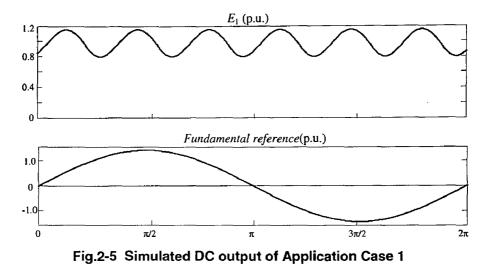

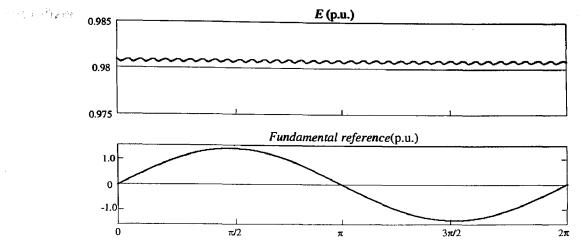

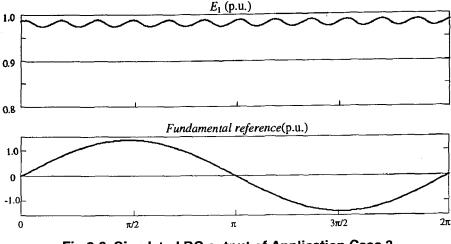

| Fig.2-5 Simulated DC output of Application Case 1                                  |    |

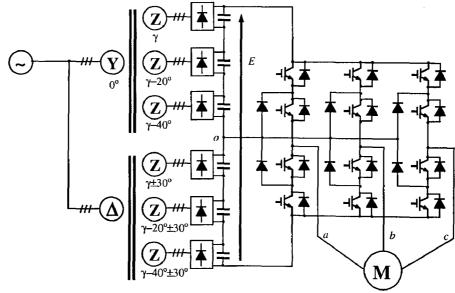

| Fig.2-6 DC connection of Application Case 2: for 3-level NPC inverters             |    |

| Fig.2-7 Simulated DC output of Application Case 2                                  |    |

| Fig.2-8 DC connection of Application Case 3: for 5-level NPC/H-bridge inverters.   |    |

| Fig.2-9 Simulated DC output of Application Case 3                                  |    |

| Fig.2-10 Matching two 18-pulse drives for harmonic cancellation.                   |    |

| Fig.2-11 Circuit diagram of dual 18-pulse rectifiers for simulation.               |    |

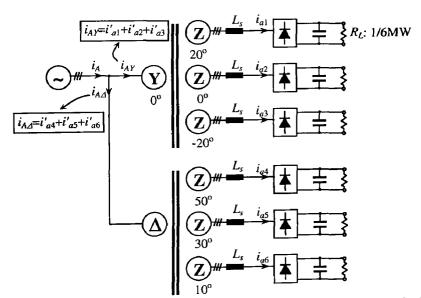

| Fig.2-12 Simulated current waveforms.                                              |    |

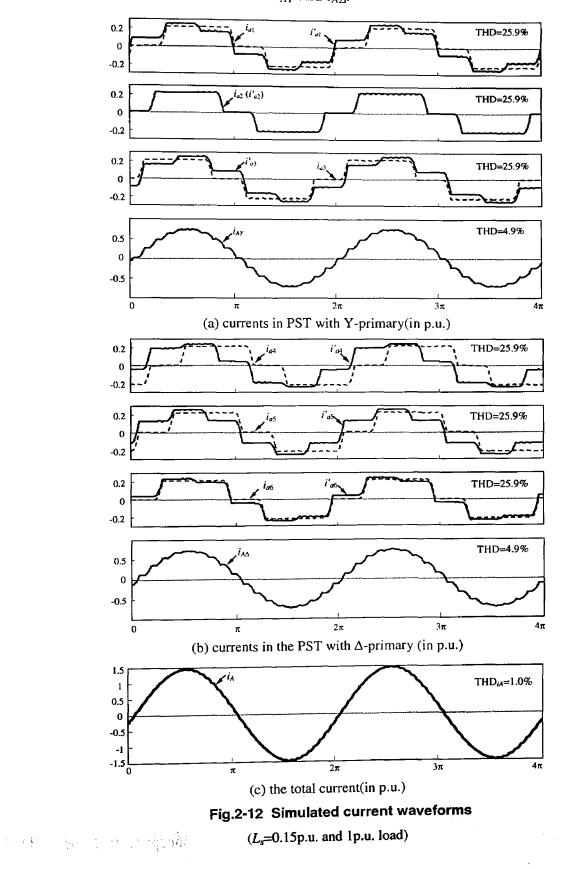

| Fig.2-13 Simulated spectra of the currents                                         |    |

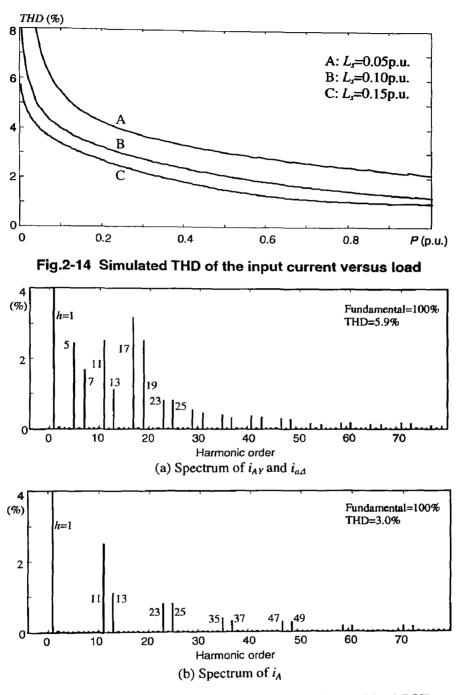

| Fig.2-14 Simulated THD of the input current versus load                            |    |

| Fig.2-15 Simulated spectra of the currents of non-ideal PSTs                       |    |

|                                                                                    |    |

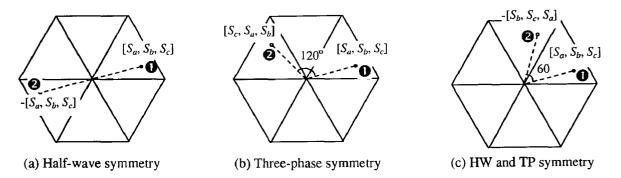

| Fig.3-1 Waveform symmetry represented by switching states.                         |    |

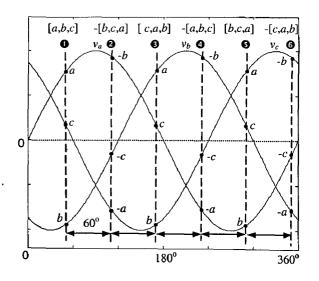

| Fig.3-2 Waveform presentation of the 60° symmetry                                  |    |

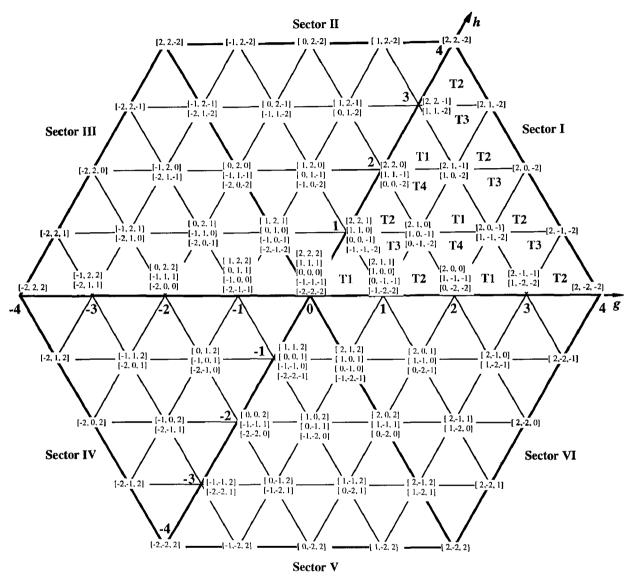

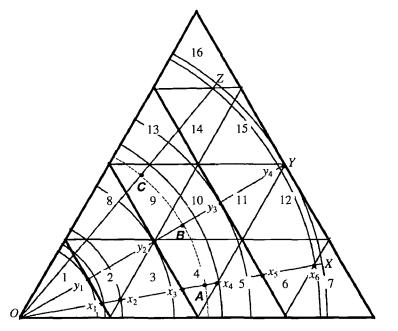

| Fig.3-3 The vector plot of 5-level inverters                                       | 40 |

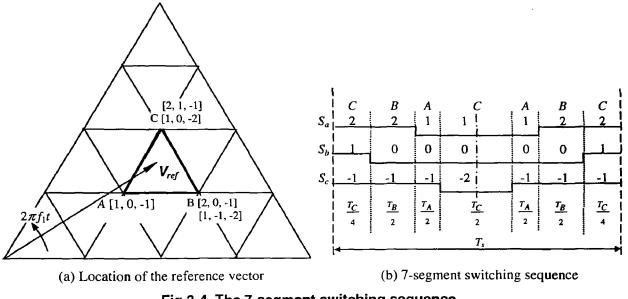

| Fig.3-4 The 7-segment switching sequence                                           | 41 |

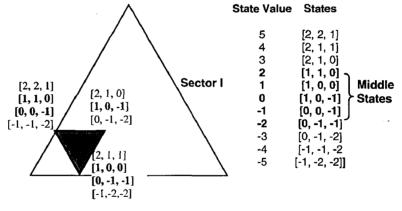

| Fig.3-5 Middle switching states                                                    | 42 |

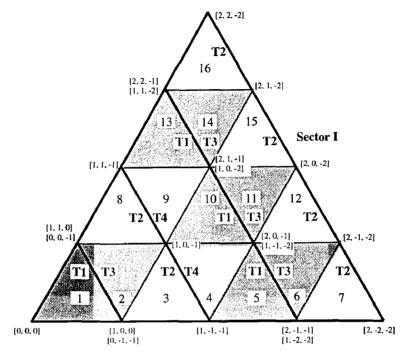

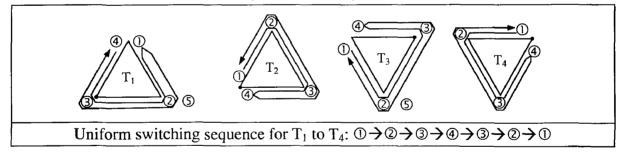

| Fig.3-6 Sector I with only middle states                                           | 44 |

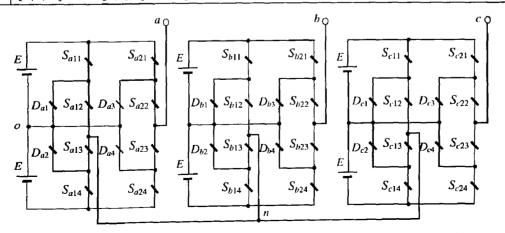

| Fig.3-7 Sketch topology of the NPC/H-bridge inverter with isolated DC sources      | 45 |

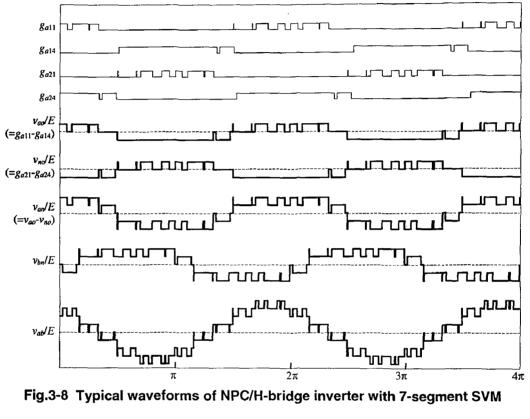

| Fig.3-8 Typical waveforms of NPC/H-bridge inverter with 7-segment SVM              | 46 |

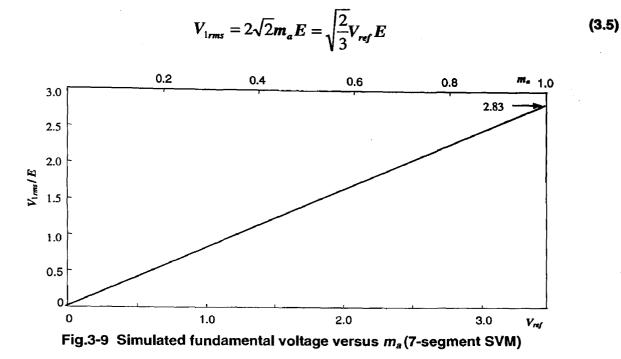

| Fig.3-9 Simulated fundamental voltage versus $m_a$ (7-segment SVM)                 |    |

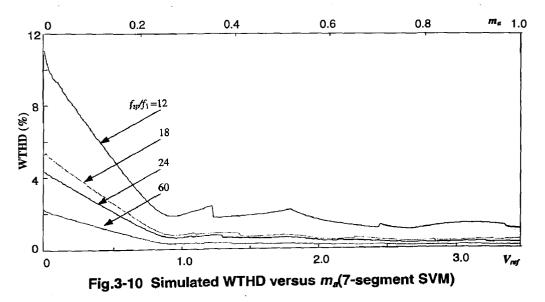

| Fig.3-10 Simulated WTHD versus m <sub>a</sub> (7-segment SVM)                      |    |

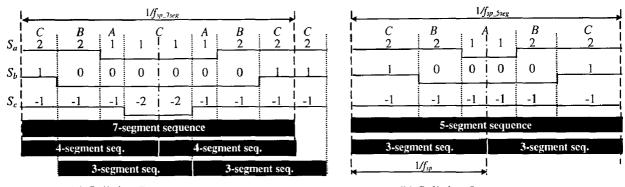

| Fig.3-11 Splitting switching sequences                                             |    |

| Fig.3-12 Boundaries of extra switching patterns of 7-segment SVM $(f_{sp}/f_1=18)$ |    |

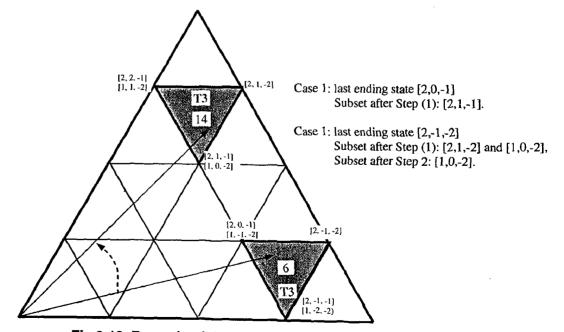

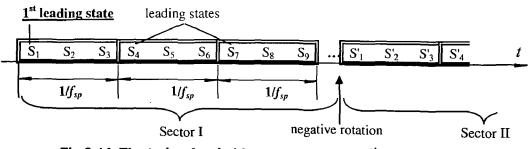

| Fig.3-13 Example of the selection of leading state                                       | 52         |

|------------------------------------------------------------------------------------------|------------|

| Fig.3-14 The train of switching states and the 1 <sup>st</sup> leading state             |            |

| Fig.3-15 Examples of 3-segment sequence                                                  |            |

| Fig.3-16 Typical waveforms of NPC/H-bridge inverter with 3-segment SVM                   | 57         |

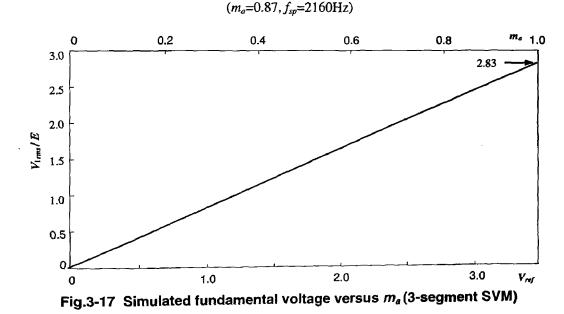

| Fig.3-17 Simulated fundamental voltage versus $m_a$ (3-segment SVM)                      |            |

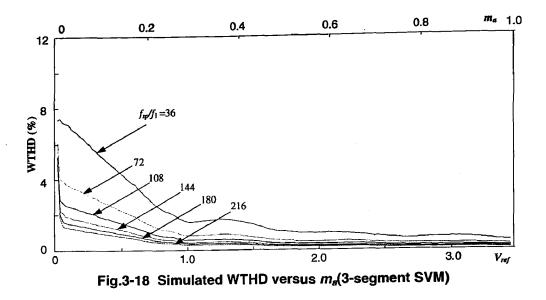

| Fig.3-18 Simulated WTHD versus m <sub>a</sub> (3-segment SVM)                            |            |

| Fig.3-19 Simulated voltage waveforms of NPC/H-bridge inverter with 7-segment SVM         | 59         |

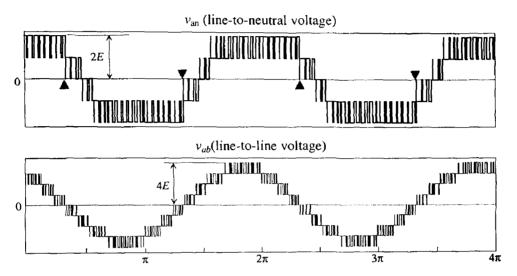

| Fig.3-20 Simulated voltage waveforms of NPC/H-bridge inverter with 3-segment SVM         |            |

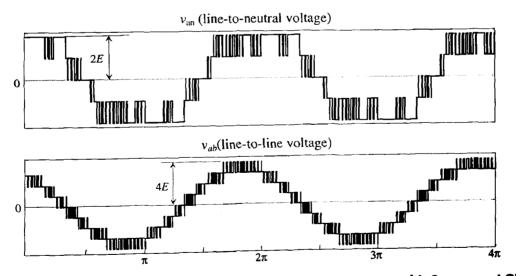

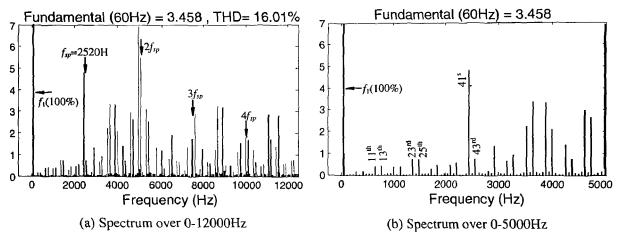

| Fig.3-21 Simulated spectra of line voltage of NPC/H-bridge inverter with 7-segment SVM   |            |

| Fig.3-22 Simulated spectra of line voltage of NPC/H-bridge inverter with 3-segment SVM   |            |

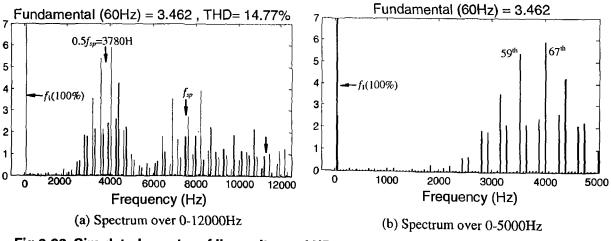

| Fig.3-23 Comparison of THD versus m <sub>a</sub>                                         |            |

| Fig.3-24 Comparison of WTHD versus m <sub>a</sub>                                        |            |

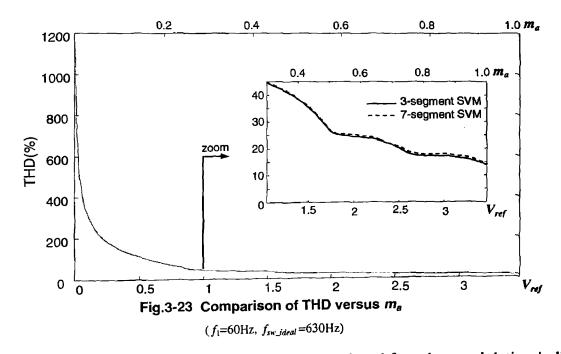

| Fig.3-25 Gating pattern of 7-segment SVM                                                 | 62         |

| Fig.3-26 Gating pattern of 3-segment SVM                                                 | 62         |

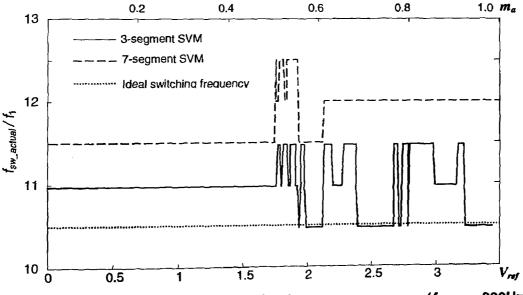

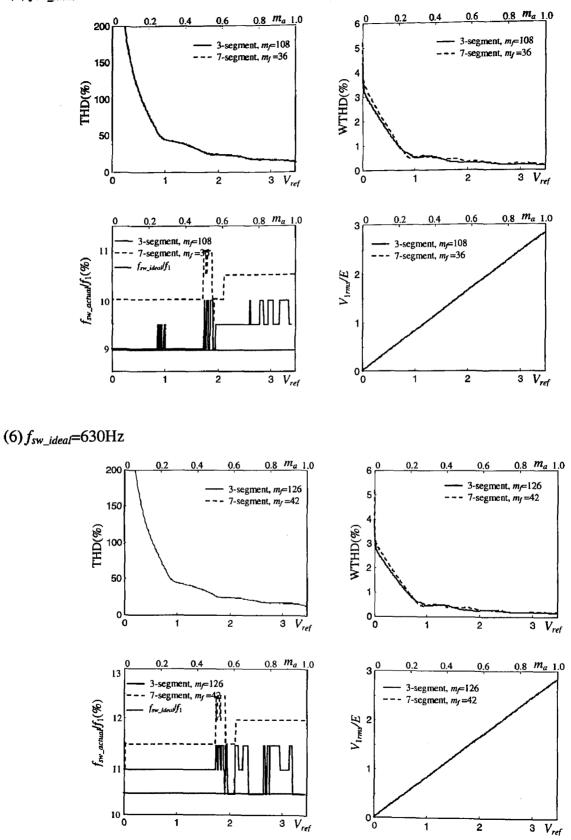

| Fig.3-27 Actual average device switching frequency versus $m_a$ ( $f_{sw_ideal}$ =630Hz) | 63         |

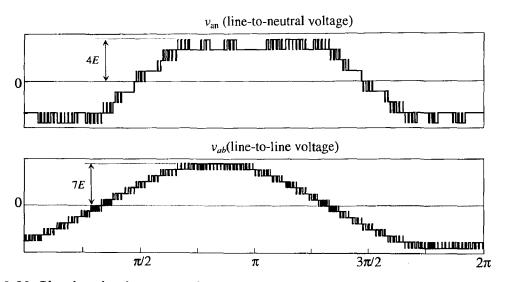

| Fig.3-28 Simulated voltage waveforms of 9-level CHB inverter with 3-segment SVM          | 64         |

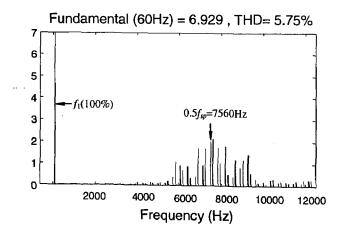

| Fig.3-29 Simulated spectra of line voltage of 9-level CHB inverter with 3-segment SVM    | 64         |

|                                                                                          |            |

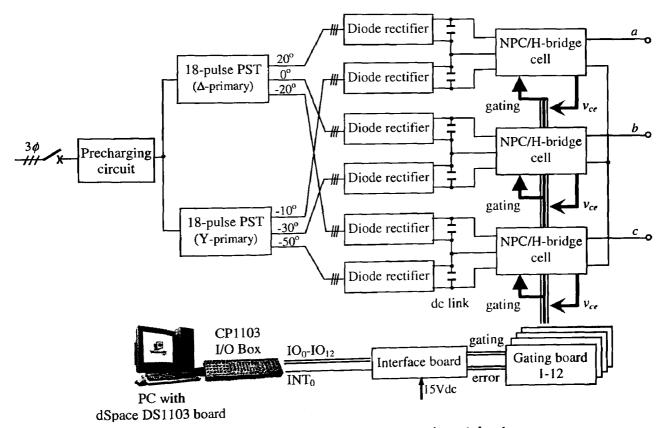

| Fig.4-1 System block diagram of the experimental setup                                   | 67         |

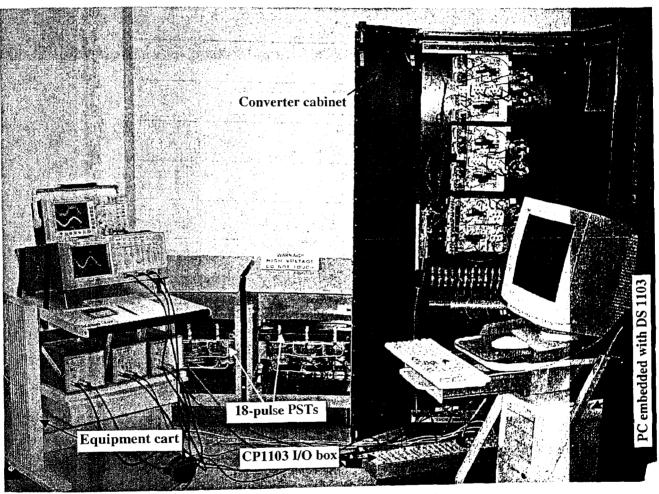

| Fig.4-2 Photo of the experiment setup                                                    | 69         |

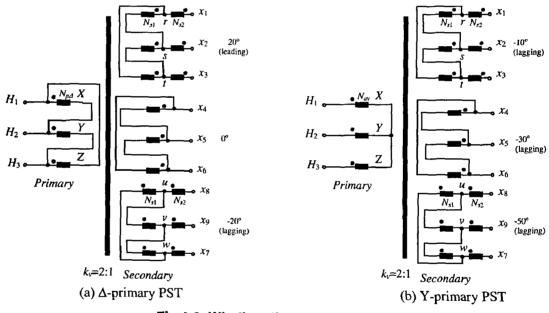

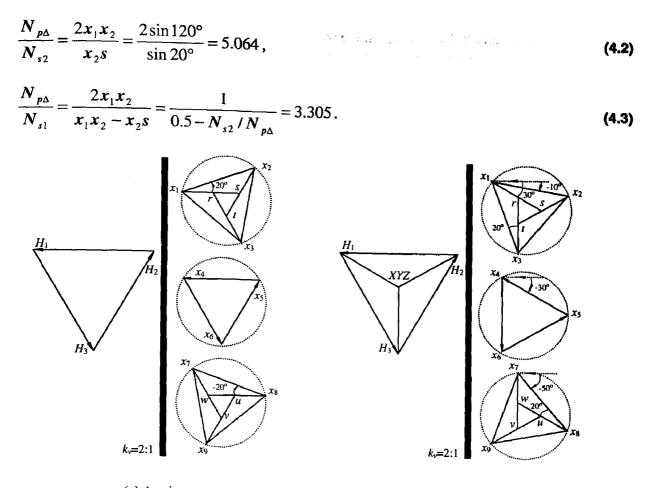

| Fig.4-3 Winding diagram of the PSTs                                                      | 70         |

| Fig.4-4 Phasor diagram of the PSTs                                                       | <b>7</b> 1 |

| Fig.4-5 Phase A of the NPC/H-bridge inverter.                                            | 73         |

| Fig.4-6 Balanced gating signals by swapping decoding schemes.                            | 74         |

| Fig.4-7 Block diagram of Simulink/RTI model of the inverter controller                   |            |

| Fig.4-8 Experiment waveforms of the input currents                                       | 78         |

| Fig.4-9 Experiment waveforms of inverter output voltage(3-segment SVM, $f_1$ =60Hz)      |            |

| Fig.4-10 Experiment waveforms of inverter output voltage (7-segment SVM, $f_1$ =60Hz)    | 80         |

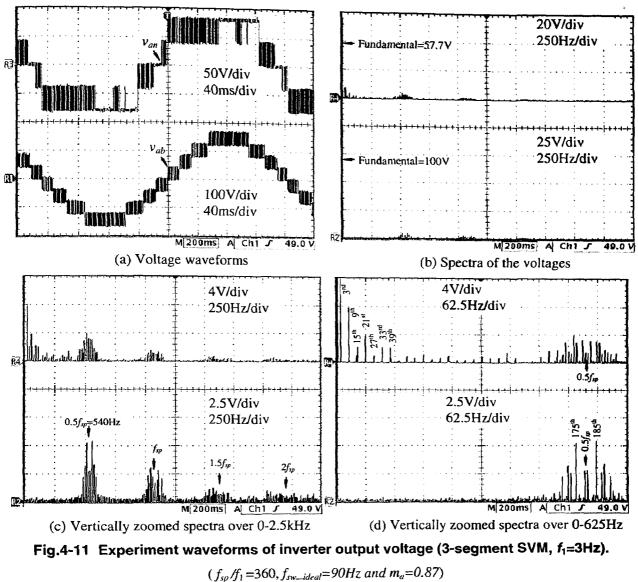

| Fig.4-11 Experiment waveforms of inverter output voltage (3-segment SVM, $f_1$ =3Hz)     | 81         |

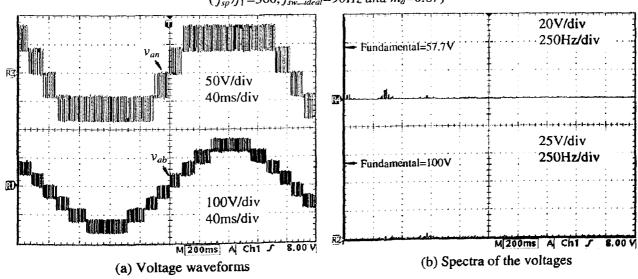

| Fig.4-12 Experiment waveforms of inverter output voltage (7-segment SVM, $f_1$ =3Hz)     | 82         |

|                                                                                          |            |

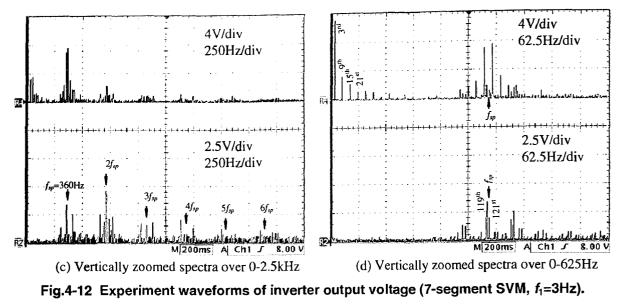

| Fig.A-1 Coordinate transformation from rectangular to hexangular system                  |            |

| Fig.A-2 Identification of the nearest three vectors.                                     |            |

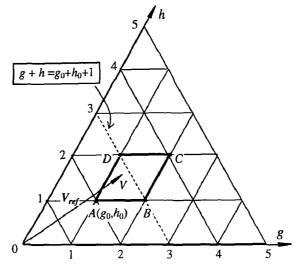

| Fig.A-3 Diagram for dwell time calculation.                                              |            |

| Fig.A-4 Block diagram of the SVM controller for NPC/H-bridge inverter                    |            |

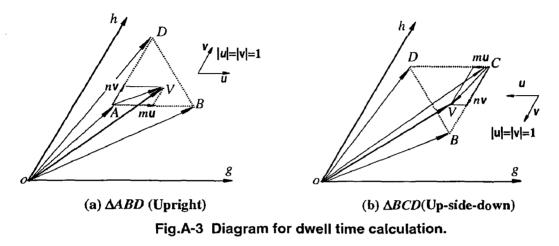

| Fig.A-5 Subsystem 'Gate Signals'                                                         |            |

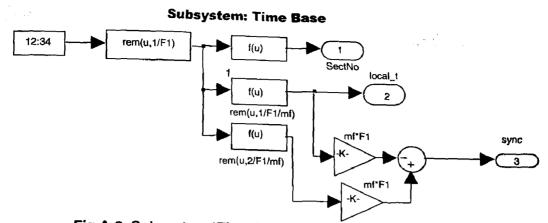

| Fig.A-6 Subsystem 'Time Base' (for 3-segment and 7-segment).                             |            |

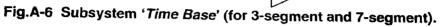

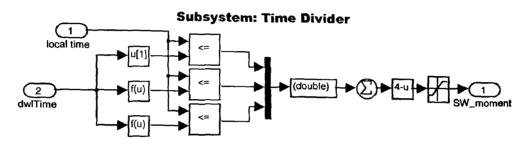

| Fig.A-7 Subsystem 'Time Divider'.                                                        | 95         |

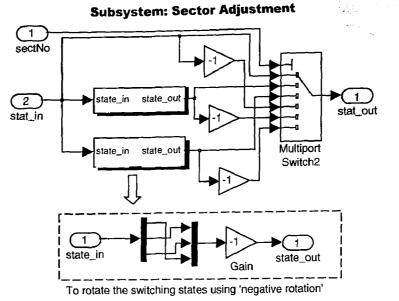

| Fig.A-8 Subsystem 'Sector Adjustment' (for 3-segment and 7segment)                       | <b>9</b> 6 |

| Fig.A-9 Subsystem 'State to Pulse Decoder' (for 3-segment and 7segment).                 | 96         |

|                                                                                          | •          |

.

ix

ا المحمد المحمدين الترجي المن المحمد. المحمد المحمد المناصف المحمد المحمد المحمد المحمد المحمد المحمد المحمد ال

| Variable Format | Meaning                                                      |

|-----------------|--------------------------------------------------------------|

| F               | CAPITALS: peak AC, rms AC or average DC value                |

| f               | LOWER CASE: instantaneous value                              |

| [., ., .,]      | SQUARE BRACKETS: switching states                            |

| (., ., .,)      | PARENTHESES: coordinate triple, 3-phase instantaneous values |

| AB              | BOLD CAPITALS: vector with tail A and tip B                  |

| f               | BOLD LOWER CASE: vector                                      |

Generic Variable Usage Conventions

: 7

## Specific Variable Definitions

| Variable                                          | Meaning                                                                                                               |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| a, b, c, o                                        | inverter output terminals; transformer secondary terminals                                                            |

| (a, b, c)                                         | three phase variables                                                                                                 |

| A, B, C                                           | transformer primary terminals                                                                                         |

| С                                                 | DC link capacitance                                                                                                   |

| $D_A, D_B, D_C, D_D$                              | duty cycles                                                                                                           |

| $E, E_1, E_2, E_3$                                | step voltage; isolated DC voltages                                                                                    |

| $f_1$                                             | fundamental frequency                                                                                                 |

| fextra                                            | extra switching frequency                                                                                             |

| f <sub>inv_sp</sub>                               | inverter sampling frequency (the center frequency of the 1 <sup>st</sup> sideband in spectra of line-to-line voltage) |

| $f_{sp}$                                          | sampling frequency of space vector modulation algorithms                                                              |

| fsw_actual                                        | actual average device switching frequency                                                                             |

| fsw_ideal                                         | ideal average device switching frequency                                                                              |

| (g, h)                                            | hexangular coordinates                                                                                                |

| $(g_0, h_0)$                                      | hexangular coordinates of the base vertex                                                                             |

| h                                                 | harmonic order                                                                                                        |

| <i>i</i> <sub>1</sub> , <i>i</i> <sub>2</sub>     | currents of different secondary windings of PSTs                                                                      |

| <i>i</i> ′ <sub>1</sub> , <i>i</i> ′ <sub>2</sub> | induced currents of $i_1$ , $i_2$                                                                                     |

| $i_A, i_B, i_C$                                   | 3-phase currents at the primary side                                                                                  |

| $i_a, i_b, i_c$                                   | 3-phase currents at the secondary side                                                                                |

| $i_{aY}(i_{a\Delta})$                             | instantaneous current of Y (Δ) windings                                                                               |

| $i'_{aY}(i'_{a\Delta})$                           | instantaneous current of Y ( $\Delta$ ) windings referred to the primary side                                         |

| Ices                                              | collector-emitter cut-off current of IGBTs                                                                            |

| $i_r$ , $i_s$ , $i_t$                                                  | secondary coil currents of zigzag transformers          |

|------------------------------------------------------------------------|---------------------------------------------------------|

| $i_X, i_Y, i_Z$                                                        | primary coil currents of zigzag transformers            |

| k_v                                                                    | primary to secondary voltage ratio                      |

| $L_s$                                                                  | total mains-side inductance                             |

| ( <i>m</i> , <i>n</i> )                                                | local coordinates in the vector plot                    |

| m <sub>a</sub>                                                         | amplitude modulation index                              |

| m <sub>f</sub>                                                         | normalized sampling frequency of SVM                    |

| $N_1, N_2, N_p, N_{p\Delta}, N_{p\gamma}, N_{s1}, N_{s2}$              | number of turns                                         |

| <i>p</i>                                                               | number of pulses                                        |

| $R_s$                                                                  | total mains-side resistance                             |

| S                                                                      | state value; switching function; power capacity         |

| $[S_a, S_b, S_c]$                                                      | 3-phase switching states                                |

| S <sub>ao</sub> , S <sub>no</sub>                                      | switching states of NPC arms                            |

| $T_{a}, T_{b}, T_{0}$                                                  | dwell times                                             |

| THD                                                                    | total harmonic distortion                               |

| $T_s$                                                                  | sampling period $(T_s=1/f_{sp})$                        |

| <i>u</i> , <i>v</i>                                                    | unit vectors                                            |

| <b>V</b> <sub>1</sub> , <b>V</b> <sub>2</sub> ,, <b>V</b> <sub>7</sub> | stationary vectors of 2-level inverters                 |

| $V_{lrms}(V_{hrms})$                                                   | rms value of the fundamental (h <sup>th</sup> harmonic) |

| V <sub>1rms_max</sub>                                                  | maximum rms value of the fundamental                    |

| $(v_a, v_b, v_c)$                                                      | 3-phase voltages                                        |

| V <sub>ab</sub>                                                        | line-to-line voltage                                    |

| Van                                                                    | phase A voltage with respect to the 3-phase neutral n   |

| v <sub>ao</sub> (v <sub>no</sub> )                                     | voltage of NPC arm with respect to the DC neutral       |

| V <sub>d</sub>                                                         | DC link voltage; rectifier output voltage               |

| V <sub>ref</sub>                                                       | reference vector                                        |

| V <sub>ref</sub>                                                       | magnitude of the reference vector                       |

| $(\nu_{\alpha}, \nu_{\beta})$                                          | coordinates of $(\alpha, \beta)$ plane                  |

| <i>w</i>                                                               | number of secondary windings                            |

| WTHD                                                                   | weighted THD                                            |

| $\Delta S$                                                             | total state value change                                |

| δ                                                                      | phase shift angle                                       |

| δS                                                                     | phase state value change                                |

| γ                                                                      | arbitrary angle                                         |

| θ                                                                      | argument of the reference vector                        |

| ω                                                                      | angular frequency                                       |

# **CHAPTER 1 INTRODUCTION**

#### 1.1 Overview

High-power medium voltage (MV) motor drives have been used increasingly in industry and there is still much room for the growth because only 3% of the currently installed MV motors are controlled by drives<sup>[1]</sup>.

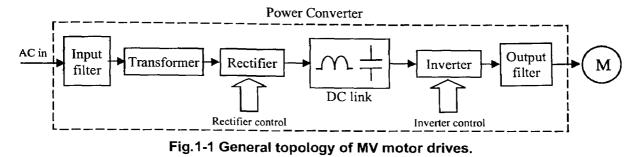

Fig.1-1 shows the block diagram of an MV motor drive. The AC power drawn from the utility is converted by the power converter and supplies the motor in whatever voltage, current and frequency necessary to achieve the desired mechanical performance. The converter includes the optional input/output filters, the transformer, the rectifier, the DC link and the inverter. The DC link may be a group of capacitors if the inverter is voltage source based, or reactor if it is current source based. The transformer normally has multiple phase-shifted secondary windings and accounts for a significant part of the drive cost. Depending on whether it is an active or passive rectifier, the converter may or may not have the rectifier control, but it always has the inverter control. The inverter control is important for the drive to generate desirable waveforms for the motor.

The technical requirements and challenges of MV drives mainly come from the following origins<sup>[1]</sup>: the power quality requirements of the utility, the inverter design and control, the requirements of the interface with the motor, and system requirements of the drives.

To meet the utility-side power quality requirements, phase-shifting transformers (PSTs) and multi-pulse rectifiers are used more and more often to limit the line current distortion and

improve the power factor<sup>[1]-[7]</sup>. At the inverter stage, the multilevel topology provides good opportunities to generate high-quality waveforms and to increase the inverter voltage to MV level (up to 6kV) with limited device voltage ratings<sup>[1][5][9]-[18]</sup>.

While taking advantage of the harmonic cancellation, the better-shaped output waveforms, and the higher inverter voltage brought by multi-pulse rectifiers and the multilevel inverters, one should keep in mind that high-pulse PSTs are expensive and the control of multilevel inverters are very complex.

The thesis focuses on the simplification of the front-end topology and the improvement of the modulation techniques of multilevel inverters.

#### **1.2 Multi-Pulse Rectifiers**

The term 'multi-pulse' probably comes from the multiple humps per fundamental cycle in the rectifier output. For a conventional 3-phase rectifier there are 6 humps thus it is in fact a 6-pulse rectifier. Similarly we have other multi-pulse rectifiers, such as 12-, 18- and 24-pulse rectifiers. For convenience, the PST powering a p-pulse rectifier is called a <u>p-pulse</u> transformer or p-pulse PST in the thesis.

The motivation of the adoption of multi-pulse rectifiers is to meet the harmonic regulations set by IEEE Standard 519-1992<sup>[8]</sup> and its European counterpart IEC 1000. For example, the current distortion limit set by IEEE 519-1992 for power converters is 5% of the maximum demand load current (15- or 30-minute demand), which can not be achieved by 6-pulse rectifiers.

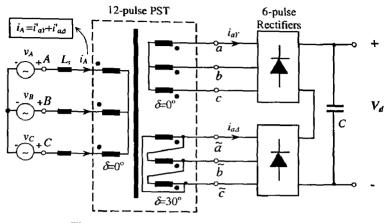

The simplest multi-pulse rectifier for harmonic cancellation is the 12-pulse rectifier shown in Fig.1-2. There are two 6-pulse diode rectifiers whose DC outputs are connected in series. The rectifiers are powered by the two secondary windings of a 12-pulse PST. One of the secondaries is in Y-connection, the other in  $\Delta$ . If the phase angle of the primary line-to-line voltage is used as the reference, the phase-shifting angle of the Y-secondary is  $\delta=0^{\circ}$  and that of the  $\Delta$ -secondary is  $\delta = 30^{\circ}$ . The secondary terminal currents,  $i_{aY}$  and  $i_{a\Delta}$ , are referred to the primary as  $i'_{aY}$  and  $i'_{a\Delta}$ , the sum of which is the primary current  $i_A$ .

Fig.1-2 Topology of 12-pulse rectifier

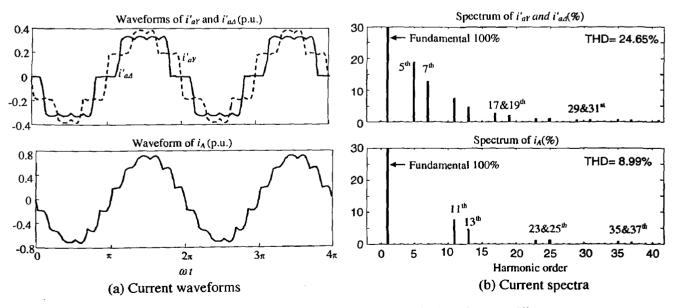

Some of the harmonics in  $i'_{aY}$  can neutralize those of  $i'_{a\Delta}$ , leading to lower THD of  $i_A$ . Fig.1-3(a) shows the waveforms of  $i'_{aY}$ ,  $i'_{a\Delta}$  and  $i_A$  when the DC load is 0.5p.u., the total supply-side inductance  $L_s=0.15$  p.u. The waveform of  $i_A$  is more sinusoidal than both of  $i'_{aY}$  and  $i'_{a\Delta}$ . Fig.1-3(b) shows the spectra of the currents. Currents  $i'_{aY}$  and  $i'_{a\Delta}$  have the same spectra, but some of the harmonic contents are 180° out of phase and cancel each other. As a result, these harmonics, such as 5<sup>th</sup>, 7<sup>th</sup>, 17<sup>th</sup> and 19<sup>th</sup>, disappear in the spectra of  $i_A$ . The THD of  $i_A$  is about 9%, compared to 25% of  $i'_{aY}$  and  $i'_{a\Delta}$ .

Fig.1-3 Current waveforms and spectra of 12-pulse rectifier

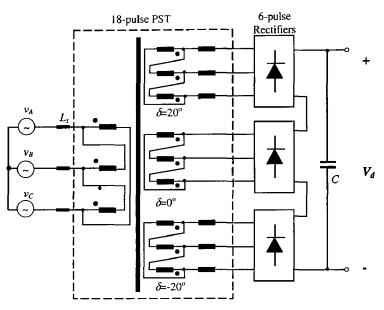

Harmonic cancellation can be further enhanced by PSTs with higher number of pulses. Fig.1-4 shows the typical topology of an 18-pulse rectifier. There are 3 identical 6-pulse rectifiers power by a PST with 3 secondaries. The secondaries of the PST are connected in  $\Delta$  or extended- $\Delta$ , producing phase-shifting angles of 20°, 0° and -20° respectively. Similar to the case of 12-pulse rectifier, some harmonic contents are absent in the spectrum of primary current and the lowest order harmonic is now the 17<sup>th</sup>.

Fig.1-4 Topology of 18-pulse rectifier

| $h_p$ | 5 <sup>th</sup> | 7 <sup>th</sup> | 11 <sup>th</sup> | 13 <sup>th</sup> | 17 <sup>th</sup> | 19 <sup>th</sup> | 23 <sup>rd</sup> | 25 <sup>th</sup> | 29 <sup>th</sup> | 31 <sup>st</sup> | 35 <sup>th</sup> | 37 <sup>th</sup> | 41 <sup>st</sup> | 43 <sup>rd</sup> | 47 <sup>th</sup> | 49 <sup>th</sup> |

|-------|-----------------|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| 12    | canc            | elled           | not ca           | ncelled          | canc             | elled            | not car          | ncelled          | cance            | elled            | not ca           | ncelled          | cance            | elled            | not car          | ncelled          |

| 18    |                 | canc            | elled            |                  | not car          | ncelled          |                  | canc             | elled            |                  | not car          | ncelled          |                  | can              | celled           |                  |

| 24    |                 |                 | canc             | elled            |                  |                  | not car          | ncelled          |                  |                  | cance            | lled             |                  |                  | not car          | ncelled          |

| 30    | Cancelled       |                 |                  |                  |                  |                  | not can          | celled           |                  |                  | cance            | elled            |                  |                  |                  |                  |

| 36    | Cancelled       |                 |                  |                  |                  |                  |                  |                  | not car          | ncelled          |                  | can              | celled           |                  |                  |                  |

| Note  | e: h:           | the ha          | rmonic           | order            |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |

Table 1.1 Harmonic cancellation patterns of multi-pulse rectifiers

Generally, for a *p*-pulse rectifier, the harmonics lower than  $(p-1)^{st}$  order can be cancelled. Table 1.1 summarizes the cancellation patterns<sup>[1]</sup>. Larger *p* results in better cancellation. For rectifier with 5% per unit (p.u.) supply-side inductance and 0.80 p.u. load current , the input current THD is about 35% for 6-pulse rectifiers, 9% for 12-pulse, 3.8% for 18 pulse and 1.7% for 24-pulse<sup>[1][2]</sup>. It can be expected that higher-pulse rectifiers have even better performance. Multi-pulse rectifiers are commonly used in high-power converters, especially for multilevel converters, which is to be introduced in the next section.

# **1.3 Multilevel Inverters**

Multilevel inverters are used to meet the requirements coming from the motor side. As mentioned before, one of the major advantages of multilevel inverters is the high inverter voltage they can achieve. The inverter voltage is decided by the voltage ratings of the switching devices. The majority of the MV drives from 1MW to 4MW work at 3.3kV to 6.6kV voltage levels. However, the voltage ratings of the switching devices are often limited. For MV drives they are often rated at 6kV for GTO/GCT, 1.7kV, 2.5kV, 3.3kV, 4.5kV or 6.5kV for IGBTs.

There are generally three methods for higher inverter voltage: connecting devices in series, using switching devices with higher voltage rating, or adopting multilevel topology. The first method can be used only when the problem of dynamic voltage sharing has been efficiently solved. Otherwise it should be avoided. The choice of the second and third methods is really a complicated compromise of the cost, reliability and availability. Given limited device voltage ratings, the most effective solution to higher inverter voltage is multilevel topologies.

Other benefits coming with multilevel topology include lower output THD, lower dV/dt which is beneficial to the motor and increased EMC. However these features are not in the scope of the thesis and will not be discussed in detail.

#### **1.3.1 NPC Inverters**

Among the other multilevel topologies, the 3-level neutral point clamped (NPC) topology, which was first proposed by Nabae et al<sup>[12][14]</sup>, has been widely used.

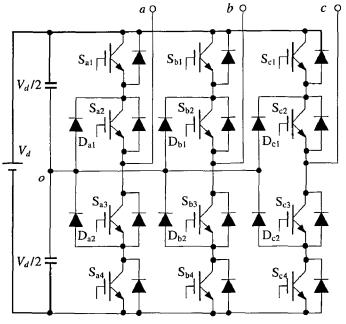

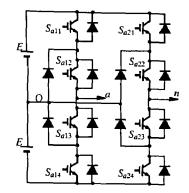

Fig.1-5 shows the topology of the NPC inverter, where only one DC source  $V_d$  is needed. Two capacitors are used to split the DC voltage and provide a neutral point o. Each phase contains 4 active switches,  $S_{k1}$  to  $S_{k4}$ , and 2 clamping diodes  $D_{k1}$  and  $D_{k2}$ , k=a, b or c. The 4 switches are controlled as two complementary pairs. For example, switches  $S_{a1}$  and  $S_{a3}$ ,  $S_{a2}$  and  $S_{a4}$  are complementary pairs. Each phase can be connected to three potentials:  $+V_d/2$ , 0 or  $-V_d/2$ .

Fig.1-5 Three-level NPC inverter

The maximum *rms* value of the fundamental of the line-to-line voltage  $V_{1rms_max}$  is the same as that of the 2-level inverters. For SPWM modulation, it is

$$V_{1rms_{max}} = 0.5 \frac{\sqrt{3}}{\sqrt{2}} V_d = 0.61 V_d$$

(1.1)

Compared to 2-level inverters, the main feature of NPC inverter is that it can achieve higher inverter voltage. This is because the maximum voltage for each device in the NPC topology is  $V_d/2$ , while it is  $V_d$  in a 2-level topology. For example, if the motor voltage is 2.3kV, the DC link voltage can be calculated to be around 3.3kV. For 2-level topology it requires switching devices rated at around 6.6kV, which hits the 6.5kV upper limit of device voltage ratings (for IGBT) in the market place. If the 3-level NPC topology is used, each switching device blocks only 1700V. Less expensive 3.3kV devices can be used without series connection. For 3.3kV IGBTs, the highest inverter voltage of the NPC topology can achieve is 2.3kV. If the inverter voltage is more than 2.3kV, for example 3.3kV, the device voltage rating should be more than 5.4kV in the NPC topology. However the voltage of the MV drives is often higher than 2.3kV, with most of them being at 4.16kV level. For the inverters with 4.16kV output voltage, the device rating will be more than 6.8kV for the NPC topology. In other words, if the motor voltage exceeds 2.3kV, the 3.3kV IGBT-base NPC topology can not be used.

#### 1.3.2 NPC/H-Bridge Inverters

NPC/H-bridge inverters is designed for inverter voltage higher than 2.3kV. It can achieve up to 4.16kV inverter voltage with 3.3kV IGBTs.

Fig.1-6 Five-level NPC/H-bridge inverter.

Fig.1-6 shows the topology of an NPC/H-bridge inverter. Each phase is an NPC/H-bridge cell composed by two NPC arms. The 4 switches of each NPC arm operate similarly to the NPC inverters. Every phase is powered by an isolated DC source, which is split into halves by capacitors. The NPC arms are 3-level and the difference of the two arms, which is the phase voltage, has five voltage levels:  $V_d$ ,  $V_d/2$ , 0,  $-V_d/2$  and  $-V_d$ .

Each active switching devices must block  $V_d/2$  forward voltage, the same as that of NPC inverters. However the output voltage is doubled in comparison with 3-level NPC topology. For NPC/H-bridge inverters with SPWM modulation, the maximum *rms* value of the fundamental  $V_{1rms}$  max is:

$$V_{\rm irms_max} = \frac{\sqrt{3}}{\sqrt{2}} V_d = 1.22 V_d$$

(1.2)

Let's consider the 4.16kV inverter with the NPC/H-bridge topology. The required DC link voltage is now 3.4kV and the device voltage will be of the same level. Thus 3.3kV IGBTs can be used without devices in series.

Another feature of the NPC/H-bridge topology is that it potentially needs only three isolated DC sources. However this feature is not exploited in MV drives because the PSTs used for multi-pulse rectifiers also provide multiple isolated DC sources, leading to fixed neutral potential and avoiding neutral voltage deviation.

The five-level NPC/H-bridge inverters were studied by some researchers and marketed by manufactures. The NPC/H-bridge topology was reported to be used as single phase inverter by C. M. Wu et. al. in 1999<sup>[19]</sup> and was first granted patent to a manufacturer in 2000<sup>[20]</sup>. The topology was then used in high-power drives at 3.3kV and 4.2kV levels<sup>[6]</sup>.

To summarize, Table 2.1 compares the NPC and NPC/H-bridge topologies. It can be concluded that if 3.3kV IGBTs are used, the NPC topology is for drives up to 2.3kV and the NPC/H-bridge topology is for drives up to 4.16kV.

| Item<br>Topology | Voltage<br>levels |                         | Max gain<br>(V <sub>1rms_max</sub> /V <sub>d</sub> ) | # of<br>IGBTs | 1 0 | # of isolated<br>DC source | Max inverter<br>voltage with<br>3.3kV IGBT |

|------------------|-------------------|-------------------------|------------------------------------------------------|---------------|-----|----------------------------|--------------------------------------------|

| NPC              | 3                 | $V_d/2$                 | 0.61                                                 | 12            | 6   | 1                          | 2.3kV                                      |

| NPC/H-bridge     | 5                 | <i>V<sub>d</sub></i> /2 | 1.22                                                 | 24            | 12  | 3                          | 4.16kV                                     |

Table 1.2 Comparison of NPC and NPC/H-bridge inverters

8

## 1.4 High-Power MV Drives

As was mentioned in Section 1.1, the high-power MV drives must meet the challenges and requirement coming from both the utility side and the motor side. According the requirements from the utility side, drives should draw less harmonic current and operate at near unit power factor<sup>[1]</sup>. On the other hand, the motor side requires waveforms with desired amplitude and frequency with lower harmonics and lower dV/dt. To satisfy the motor's requirements, high-power MV drives are often fed by multilevel inverters, which are powered by multi-pulse rectifiers at the front-end.

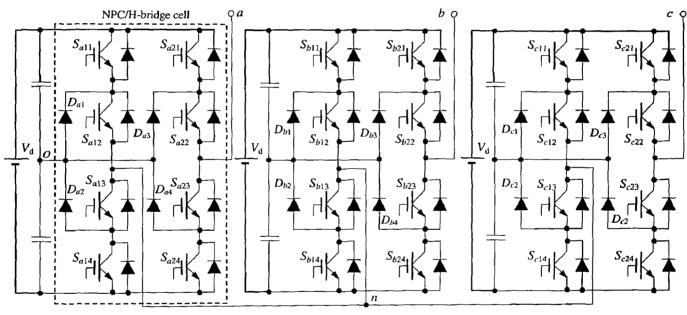

Fig.1-7 shows the topology of a drive system fed by a 5-level cascaded H-bridge (CHB) inverter<sup>[21]</sup>. Each phase contains two H-bridge cells (shown in the dashed circle) in series. Each H-bridge cell is powered by a 6-pulse rectifier. The two rectifiers of the same phase are powered by two secondary windings with 30° phase shift from each other, forming a 12-pulse rectifier. The PST has altogether 6 secondary windings, supplying three 12-pulse rectifiers.

Fig.1-7 Topology of MV drives fed by 5-level CHB inverter

To achieve even lower current THD and higher the drive voltage, more complicated topologies are used in industry. Fig.1-8 shows the topology of an MV drive fed by 7-level CHB inverter<sup>[5]</sup>. Each phase contains three H-bridge cells, which are connected to three 6-

pulse rectifiers powered by the secondary windings with 20° phase shift from each other, forming 18-pulse rectification. The PST has altogether 9 secondary windings.

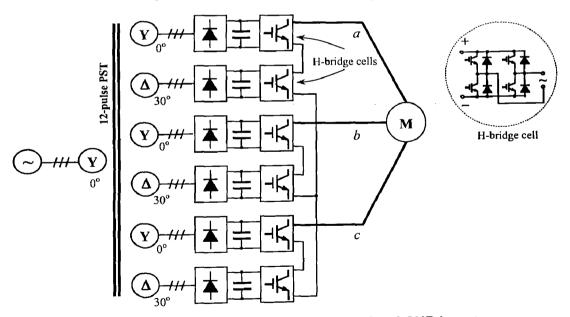

Fig.1-9 Topology of 5-level NPC/H-bridge inverter fed MV drive

Fig.1-9 shows the topology of an MV drive fed by 5-level neutral point clamped (NPC) H-bridge inverter<sup>[6]</sup>. Each bridge is power by a 24-pulse rectifier, which is used to achieve less

than 3% input current THD. The PST now has 12 secondary windings, every four of which are combined to power the 24-pulse rectifier. There are altogether 12 rectifiers and 6 groups of DC links capacitors. Table 1.3 is the number of the major parts used by the topology.

Table 1.3 Parts count table of the 5-level NPC/H-bridge drive powered by 24-pulse rectifier

| Items       | secondary<br>windings | 3-phase diode DC-link<br>rectifiers capacitors |   | Active switches | Clamping diodes |

|-------------|-----------------------|------------------------------------------------|---|-----------------|-----------------|

| Parts count | 12                    | 12                                             | 6 | 24              | 12              |

The choice of the number of pulse and the number of voltage levels depends on the numerous factors under the economic constraints, such as the input current THD requirements, the rated voltage of the drive, the topology of the inverter and the voltage rating of the devices. The more pulses, the higher number of secondary windings. The higher number of voltage levels, the more complicated control for the inverter.

# **1.5 Space Vector Modulation of Multilevel Inverters**

The control of the multilevel inverter is one of major challenges for MV motor drives. The modulation scheme developed in two lines: sinusoidal PWM (SPWM) and space vector modulation (SVM). SVM has been studied extensively studies since its birth in the mid 1980s. Researches have shown that SVM is equivalent in everyway to the more traditional SPWM<sup>[22]-[24]</sup>. Adjusting one parameter in SVM is equivalent to adjusting other parameter in SPWM. For example, adjusting the modulation index or the carrier frequency in SPWM is equivalent to adjusting the modulus of the reference vector or sampling frequency in SVM. The major benefit of SVM is the explicit identification of pulse placement as an additional degree of freedom that can be exploited to achieve harmonic performance and inverter gains<sup>[24]</sup>. Furthermore SVM is commonly recognized as a favourable PWM scheme for digital implementation<sup>[1][10][24]</sup>.

# 1.5.1 SVM for Two-Level Inverters

The principle of space vector modulation will be briefly introduced using a 2-level

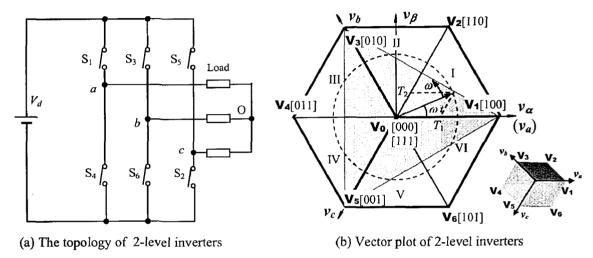

inverter as an example<sup>[1]</sup>. Fig.1-10 shows the circuit diagram and the vector plot of a 2-level inverter. In Fig.1-10(a) there are 6 switches, S<sub>1</sub> to S<sub>6</sub>, producing 8 switching combinations. For example, if switches  $S_1$ ,  $S_2$  and  $S_3$  are turned on, the three phase voltages with reference to the negative DC bus will be  $v_a=V_d$ ,  $v_b=V_d$  and  $v_c=0$ , i.e.  $(v_a, v_b, v_c)=V_d*(1,1,0)$ . We use the triple [1,1,0], which is called <u>switching state</u>, to represent this situation. Similarly the switching states can be found for the other 7 combinations, as listed in Table 1.4.

Fig.1-10 Circuit diagram and vector plot of a 2-level inverter.

Now set up a Cartesian 3-D space in Fig.1-10(b) with three axes  $v_a$ ,  $v_b$  and  $v_c$  perpendicular to each other and draw all the 8 points representing the switching states shown in Table 1.4. The small cubic block in the diagram is for better comprehension of the 3-dimensional vector plot. If the vector plot is viewed as 3-D, the switching states are in fact the coordinates. The 8 points represent the 8 <u>space vectors</u>  $V_0$  to  $V_7$ .

| Table 1.4 | Space vector, switching states and on-state switches |

|-----------|------------------------------------------------------|

|-----------|------------------------------------------------------|

| On state Switches | S <sub>1</sub> , S <sub>3</sub> , S <sub>5</sub> | S <sub>2</sub> , S <sub>4</sub> , S <sub>6</sub> | $S_1, S_2, S_6$    | $S_1, S_2, S_3$ | S <sub>2</sub> , S <sub>3</sub> , S <sub>4</sub> | S <sub>3</sub> , S <sub>4</sub> , S <sub>5</sub> | S <sub>4</sub> , S <sub>5</sub> , S <sub>6</sub> | S <sub>1</sub> , S <sub>5</sub> , S <sub>6</sub> |

|-------------------|--------------------------------------------------|--------------------------------------------------|--------------------|-----------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| Switching State   | [1,1,1]                                          | [0,0,0]                                          | [1,0,0]            | [1,1,0]         | [0,1,0]                                          | [0,1,1]                                          | [0,0,1]                                          | [1,0,1]                                          |

| Space Vector      | Vo                                               | V <sub>7</sub>                                   | $\boldsymbol{V}_1$ | V <sub>2</sub>  | V <sub>3</sub>                                   | V <sub>4</sub>                                   | V <sub>5</sub>                                   | V <sub>6</sub>                                   |

The space vectors is then projected on a plane. For three-phase balanced system, we have the constraint:

$$v_a + v_b + v_c = 0$$

.

(1.3)

which is in fact the equation of plane through the origin and with a normal direction (1,1,1), i.e. the plane parallel to the shaded triangle and thru the origin in Fig.1-10(b). The plane is called <u>vector plane</u>. By projection, the images of the three axes are  $120^{\circ}$  away from each other. The images of the 8 space vectors are called <u>stationary vectors</u>. Vectors  $V_0$  and  $V_7$  have the same image, the origin, thus are called <u>zero vectors</u>. The switching states representing the same image are <u>redundant switching states</u>. The images of  $V_1$  to  $V_6$  are located at the vertices of a hexagon, which can be divided into 6 sectors. The vector plane can be meshed by the triangles using the tips of stationary vectors as vertices.

On the other hand, we need only two axes to form the basis of a plane, which means the three-phase voltage can be represented by a two-phase vector. The *Forward Clarke Transformation* can be used for such a purpose<sup>[1]</sup>:

$$\vec{V}(t) = v_{\alpha}(t) + jv_{\beta}(t) = \frac{2}{3} [v_{a}(t)e^{j0} + v_{b}(t)e^{j2\pi/3} + v_{c}(t)e^{j4\pi/3}].$$

(1.4)

By using the transformation, the stationary vector can be calculated for each switching state. For example, for the switching state [1,1,0], the three phase voltages with respect to the negative DC bus are:  $v_a(t)=V_d$ ,  $v_b(t)=V_d$  and  $v_c(t)=0$ . Using Eq.(1.4), we have the vector:

$$\vec{V}(t) = \frac{2}{3} [v_a(t)e^{j0} + v_b(t)e^{j2\pi/3} + v_c(t)e^{j4\pi/3}] = \frac{2}{3} V_d e^{j\pi/3}.$$

(1.5)

If we normalize it by  $2V_d/3$ , it is exactly  $V_2$ .

While the stationary vectors represent the switching combinations, the three-phase voltage can be represented by a rotating vector, whose magnitude stands for the amplitude of the phase voltage and the angular speed stands for the frequency. The rotating vector is called as <u>reference vector</u> ( $V_{ref}$ ). Once the plane is meshed by stationary vectors, the reference vector can be approximated by the stationary vectors. If the reference stays at a location for a period of  $T_s$ , we can use adjacent stationary vectors, generally the nearest three-vectors (NTVs), to produce the same amount average. In Fig.1-10(b) the reference vector is located in Sector I, the sampling period  $T_s$  can be split among  $V_0(V_7)$ ,  $V_1$  and  $V_2$  based on the so-called voltsecond balance:

$$T_1 = T_s m_a \sin(-\theta + \pi/3),$$

(1.6)

$$T_2 = T_s m_a \sin \theta, \tag{1.7}$$

$$T_0 = T_s - T_1 - T_2. \tag{1.8}$$

where  $m_a$  is the amplitude modulation index,  $m_a = \sqrt{3}V_{ref} / V_d$ ,  $T_1$ ,  $T_2$  and  $T_0$  are the time segment assigned to  $V_1$ ,  $V_2$  and  $V_0(V_7)$  respectively, which are called <u>dwell times</u>.

The general procedure of implementing SVM is:

(a) calculate the switching states of the stationary vectors and mesh the vector plane;

(b) define the switching sequences for each triangle;

(c) identify the NTVs;

(d) calculate the dwell times;

(e) generate gating signal by decoding the switching states in the timed switching sequence.

#### **1.5.2 The Application of SVM for Multilevel Inverters**

The application of SVM for multilevel inverters is much more complicated than for 2- or 3-level inverters. The main reason is that there are large number of redundant switching states and stationary vectors for multilevel inverters<sup>[1][25][26][27]</sup>. Almost every step in the procedure of using SVM such as identification of the NTVs, the calculation of the dwell times, and the design of the switching sequences becomes computation-intensive and troublesome. Fortunately, the computational burden for the identification of NTVs and calculation of the dwell times is significantly lessened thanks to the contributions of many researchers. One of these is the application of hexangular coordinate system<sup>[25]</sup>.

However, there are still some other problems to be solved related to switching sequence design. The problems can be divided into the selection of redundant switching states and the

optimization of the schedule of the sequence, both of which are tedious and tough work for multilevel inverters. Earlier studies showed that it is reasonable to constrain the choice of redundant states to the 'middle states', which limits the number of switching states to 4 or 5 for each triangle<sup>[26][27]</sup>. Even with this simplification, the switching sequence design is still a major concern for optimal performance: better THD profile and lower switching loss<sup>[1]</sup>.

Harmonic reduction is the first concern of switching sequence design. For high-power MV motor drives, the switching frequency is often relatively low (about 500Hz) in the consideration of the switching loss<sup>[1]</sup>. The lower device switching frequency brings negative side-effects to the spectrum of the output voltage. If the first sideband of the spectrum is too close to the fundamental frequency, lower order harmonics such as 5<sup>th</sup> and 7<sup>th</sup>, will be great headaches. It is desirable if the switching sequence can be properly designed so that the centre of the first sideband is shifted to higher frequency.

The second concern is the reduction of the switching loss. For multilevel inverters, the complexity of the vector plot often makes extra switchings inevitable. Extra switchings are the switchings that don't contribute to the **inverter sampling frequency**, which is defined as the centre of the 1<sup>st</sup> sideband in the spectrum of the line-to-line voltage. Because high-power converters often work at lower switching frequencies, extra switching is a painful waste.

Other concerns include easy implementation. For multilevel inverters, the switching sequence design must be done for each case (triangle), which results in a complex look-up table. This case-study-based design can be improved by a rule-based design, where the selection of the switching state and the arrangement of switching sequence are implemented in real time according to some simple rules.

Moreover, waveform symmetry should also be taken into account. Although it seems that half-wave symmetry is not a big issue for MV motor in most cases, it is critical for rectifiers because the even order harmonics are strictly regulated by IEEE 519-1992, which set the limits of even harmonic to a quarter of those of odd harmonics.

15

#### 1.6 Motivation and Objective

As mentioned earlier, there are numerous technical challenges and requirements for MV high-power motor drives. Two of them will be addressed in the thesis.

والمناطقة متيكم بأخبرة فخاصيهم والرواد

The first challenge is how to simplify the topology of the rectifier and to achieve friendlier converter-to-utility interface. As introduced in Section 1.2, multi-pulse rectifiers are often the solution to the reduction of the current THD. However, the more pulses of the rectifier, the more complicated the PST. This is why rectifiers of more than 30-pulse are not used in practice.

The second challenge is how to effectively apply SVM to multilevel inverters with desirable THD profile at relatively lower switching frequency. The key issue here is how to efficiently design the switching sequence. Conventionally, switching sequence design is done by predefining the sequence for each triangle in the vector plot. This is a manual job and is really a tedious one for multilevel converter.

In brief, the effort devoted to the rectifiers for high-power drives is targeted to:

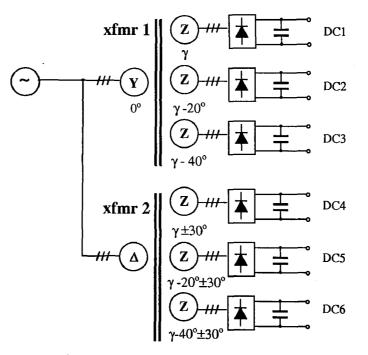

(1) the simplification of the PST. The topology shown in Fig.1-9 is used as the starting point of the simplification. The standard 18-pulse PST will be used in place of the complex 24-pulse PST. Meanwhile the number of secondary windings is reduced by half, thus the number of DC links and rectifiers can be reduced by half accordingly.

(2) the improvement of harmonic cancellation. The topology in Fig.1-9 features 24-pulse harmonic cancellation. It will be improved to 36-pulse cancellation with reduced secondary windings. The principle can also be used for harmonic cancellation between two different drives or for extra opportunities for harmonic cancellation when the PSTs are non-ideal.

The work on the switching sequence of SVM is intended to achieve the following objectives:

(3) the improvement of THD profile by increasing the inverter sampling frequency.

16

(4) the decrease of the device switching frequency by reducing the extra switchings.

(5) easy sequence design and implementation by rule-based design and mechanism of sequence reproduction. The rule-based design makes the algorithm is applicable to other multilevel inverters.

(6) Waveform symmetry which enables the algorithm to be used for active rectifiers.

## **1.7 Thesis Organization**

The work of the thesis is organized into 5 chapters.

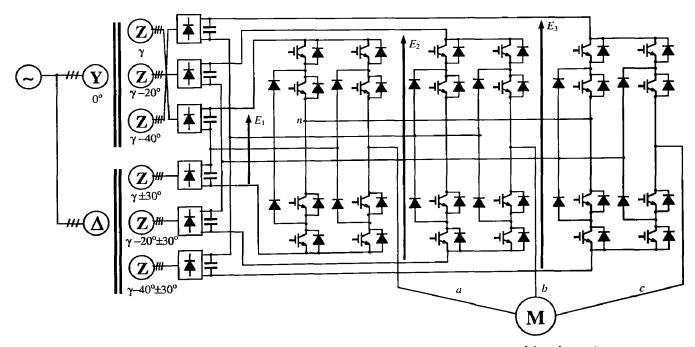

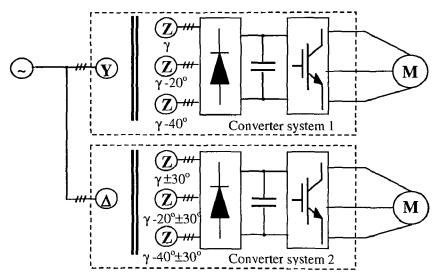

Following the introduction of Chapter 1, Chapter 2 deals with the front-end of the MV motor drives, i.e. multi-pulse rectifiers, for which the dual 18-pulse rectifier is proposed. The dual 18-pulse rectifier features 36-pulse harmonic cancellation with simple 18-pulse PSTs, fewer secondary windings, rectifier bridges and DC capacitors, compared with the 24-pulse rectification shown in Fig.1-9. Theoretical analysis and computer simulation was given to verify the above features.

For the inverter stage, emphasis of Chapter 3 is laid on the control of the multilevel inverters, i.e. the space vector modulation algorithms, for which a flexible 3-segment SVM algorithm is put forward. Compared to conventional 7-segment SVM schemes, the proposed algorithm achieves higher inverter sampling frequency, lower device switching frequency, easy sequence design and digital implementation. The algorithm is also applicable for other high-level inverters or active rectifiers which require half-wave symmetry. The performance of the algorithm is verified by extensive computer simulations in comparison with the 7-segment SVM.

The experimental verification is given in Chapter 4, in which the experimental setup is introduced and experimental results are discussed in association with the simulations.

Chapter 5 is the conclusions which can be drawn from the research in the thesis.

Other supporting materials and more detailed waveforms are attached in the appendices.

<sup>2</sup> A. C. W. Lee, Applied and the gravity of paragraphic condition and the second states and the second states of the second states and the second stat

# **CHAPTER 2 DUAL 18-PULSE RECTIFIER**

Multi-pulse rectification is used extensively by manufacturers to reduce the harmonics drawn from the utility. Phase-shifting transformers (PSTs) are the key to the harmonic reduction. Because multilevel rectifiers for high-power drives often require multiple isolated DC sources, thus PSTs with multi secondary windings are frequently found in the literatures. However PSTs with higher pulse numbers are too complicated to be manufactured due to the large number of secondary windings which must be wound with precise phase-shift angles. The highest number of pulses ever seen in practice is 30-pulse. The chapter discusses the possibility to reduce the number of secondary windings and to enhance the harmonic cancellation. A dual 18-pulse rectifier, which utilizes simple 18-pulse PSTs to achieve 36-pulse harmonic cancellation, is proposed for high power MV drives<sup>[13]</sup>.

Fig.2-1 Circuit model of a 6-pulse rectifier fed by a PST.

### 2.1 Principle of Harmonic Cancellation

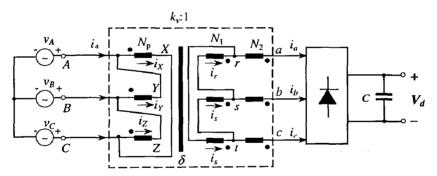

First look at a general case: a six pulse rectifier shown in Fig.2-1, where the rectifier is fed by a phase-shifting transformer. The primary winding is connected in  $\Delta$  and the secondary in extended- $\Delta$ , producing a phase shift angle  $\delta$ :

$$\delta = \angle v_{ab} - \angle v_{AB} \tag{2.1}$$

----

Assume the primary to secondary voltage ratio is  $k_v$ , and  $N_p$ ,  $N_1$  and  $N_2$  are the numbers of turns as shown in Fig.2-1. To achieve the phase shift angle  $\delta$ , the turns ratios should be<sup>[1]</sup>:

$$\begin{cases} \frac{N_p}{N_1} = \frac{k_v \sin 120^\circ}{\sin \delta} \\ \frac{N_p}{N_1 + N_2} = \frac{k_v \sin 120^\circ}{\sin(120^\circ + \delta)} \end{cases}$$

(2.2)

Assume the secondary terminal currents are:

$$\begin{cases} i_{a} = \sum_{h=1,5,7...}^{\infty} \hat{I}_{h} \sin h \omega t \\ i_{a} = \sum_{h=1,5,7...}^{\infty} \hat{I}_{h} \sin h (\omega t - 120^{\circ}) \\ i_{a} = \sum_{h=1,5,7...}^{\infty} \hat{I}_{h} \sin h (\omega t + 120^{\circ}) \end{cases}$$

(2.3)

where  $\hat{I}_{h}$  is the magnitude of the  $h^{\text{th}}$  harmonic, and  $\omega$  is the fundamental angular frequency. These terminal currents flow through the extended coils ( $N_2$ ). The currents through the secondary  $\Delta$ -coils ( $N_1$ ) are  $i_r$ ,  $i_s$  and  $i_t$  as shown in the figure. All these six currents will be induced in the primary winding inversely proportional to the turns ratios. Thus the coil currents of the primary are

$$\begin{cases} i_{X} = \frac{N_{1}}{N_{p}}i_{r} + \frac{N_{2}}{N_{p}}i_{a} \\ i_{Y} = \frac{N_{1}}{N_{p}}i_{s} + \frac{N_{2}}{N_{p}}i_{b} \\ i_{z} = \frac{N_{1}}{N_{p}}i_{r} + \frac{N_{2}}{N_{p}}i_{c} \end{cases}$$

(2.4)

Specifically the primary terminal current of phase A is:

$$i_A = i_X - i_Y \tag{2.5}$$

. .

Substituting Eq.(2.4) into Eq.(2.5) yields:

$$\dot{i}_{A} = \frac{N_{1} + N_{1}}{N_{p}} \dot{i}_{a} - \frac{N_{2}}{N_{p}} \dot{i}_{c}.$$

(2.6)

Applying Eqs.(2.2) and (2.3) to Eq. (2.6), we have:

$$i_{A} = \frac{1}{k_{v} \sin 120^{\circ}} \sum_{h=1,5,7,.}^{\infty} \hat{I}_{h} [\sin h\omega t \sin(120^{\circ} + \delta) - \sin h(\omega t + 120^{\circ}) \sin \delta]$$

$$= \frac{1}{k_{v} \sin 120^{\circ}} \sum_{h=1,5,7,.}^{\infty} \hat{I}_{h} [\sin((h+1)\cdot 60^{\circ}) \sin(h\omega t + (h-1)\cdot 60^{\circ} - \delta) - \sin((h-1)\cdot 60^{\circ}) \sin(h\omega t + (h+1)\cdot 60^{\circ} + \delta)]$$

$$= \frac{1}{k_{v}} \sum_{\substack{h=6k+1\\k=0,1,2,...}}^{\infty} \hat{I}_{h} \sin(h\omega t - \delta) + \frac{1}{k_{v}} \sum_{\substack{h=6k-1\\k=1,2,3,...}}^{\infty} \hat{I}_{h} \sin(h\omega t + \delta)$$

(2.7)

A general conclusion can be drawn from Eq.(2.7): when the secondary voltage is shifted by  $\delta$  with respect to the primary, the secondary terminal current can be referred to the primary terminal in a way such that:

- (1) The positive-sequence harmonics are phase-shifted by  $-\delta$ ;

- (2) The negative-sequence harmonics are phase shifted by  $\delta$ ;

- (3) The magnitudes are scaled by the same ratio.

| curre                                                                                  | h                       | 1 <sup>st</sup> | 5 <sup>th</sup> | 7 <sup>th</sup> | 11 <sup>th</sup> | 13 <sup>th</sup> | 17 <sup>th</sup> | 19 <sup>th</sup> | 23 <sup>rd</sup> | 25 <sup>th</sup> | 29 <sup>th</sup> | 31 <sup>st</sup> | 35 <sup>th</sup> | 37 <sup>th</sup> |

|----------------------------------------------------------------------------------------|-------------------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| Original (°)                                                                           | <i>i</i> 1              | 0               | 0               | 0               | 0                | 0                | 0                | 0                | 0                | 0                | 0                | 0                | 0                | 0                |

|                                                                                        | <i>i</i> 2              | -15             | -75             | -105            | -165             | -195             | -255             | -285             | -345             | -15              | -75              | -105             | -165             | -1 <b>9</b> 5    |

|                                                                                        | <i>i</i> 3              | -30             | -150            | -210            | -330             | -30              | -150             | -210             | -330             | -30              | -150             | -210             | -330             | -30              |

|                                                                                        | <i>i</i> 4              | -45             | -225            | -315            | -135             | -225             | -45              | -135             | -315             | -45              | -225             | -315             | -135             | -225             |

| Referred ( <sup>0</sup> )                                                              | <i>i</i> ′ <sub>1</sub> | -22.5           | 22.5            | -22.5           | 22.5             | -22.5            | 22.5             | -22.5            | 22.5             | -22.5            | 22.5             | -22.5            | 22.5             | -22.5            |

|                                                                                        | <i>i</i> ′2             | -22.5           | <b>-6</b> 7.5   | -112.5          | -157.5           | -202.5           | -247.5           | -292.5           | 22.5             | -22.5            | -67.5            | -112.5           | -157.5           | -202.5           |

|                                                                                        | <i>i</i> ′3             | -22.5           | -157.5          | -202.5          | -337.5           | -22.5            | -157.5           | -202.5           | 22.5             | -22.5            | -157.5           | -202.5           | -337.5           | -22.5            |

|                                                                                        | i'4                     | -22.5           | -247.5          | -292.5          | -157.5           | -202.5           | -67.5            | -112.5           | 22.5             | -22.5            | -247.5           | -292.5           | -157.5           | -202.5           |

| Cancelled?                                                                             |                         | no              | yes             |                 |                  |                  |                  | no Yes           |                  |                  |                  |                  |                  |                  |

| $i_1$ : the current in the 22.5° secondary; $i_2$ : the current in the 7.5° secondary; |                         |                 |                 |                 |                  |                  |                  |                  |                  |                  |                  |                  |                  |                  |

Table 2.1 The phase angles of the harmonic of 24-pulse PST

$i_3$ : the current in the -7.5° secondary;  $i_4$ : the current in the -22.5° secondary;

The above conclusions can be used to analyze the harmonic cancellation pattern of multipulse rectifiers. Let's take the 24-pulse rectifier as an example. Assume the 4 secondary windings are phase-shifted by 22.5°, 7.5°, -7.5° and -22.5° with respect to the primary. Using the above results we can quickly figure out the phase angles of the referred currents of each harmonic. For instance, the phase angles of the 5<sup>th</sup> harmonic at the secondaries are 0°, 5\*(-15°), 5\*(-30°) and 5\*(-45°) respectively. When they are referred to the primary, the phase

angles are:  $0^{\circ}+22.5^{\circ}$ ,  $-75^{\circ}+7.5^{\circ}$ ,  $-150^{\circ}-7.5^{\circ}$ ,  $-225^{\circ}-22.5^{\circ}$ , i.e.  $22.5^{\circ}$ ,  $-67.5^{\circ}$ ,  $-157.5^{\circ}$  and  $-247.5^{\circ}$ . Because they are referred with the same ratio, the referred currents with  $22.5^{\circ}$  and  $-157.5^{\circ}$  angles are  $180^{\circ}$  out of phase and cancel each other. It is the same for the other two. The phase angles of all the harmonics in the referred currents are listed until the  $37^{\text{th}}$  in Table 2.1, from which we can find the lowest harmonic in the primary current is the  $23^{\text{rd}}$ .

#### 2.2 Reduction of Secondary Windings

The performance of harmonic reduction is decided by the number of pulses. From Fig.1-7, Fig.1-8 and Fig.1-9, the number of secondary windings, *w*, is half of the number of pulses for H-bridge-based multilevel converters. For example, the 12-pulse PST has 6 secondary windings and the 24-pulse PST has 12. Can it be reduced or reconfigured for simplicity and better performance?

Now, because each secondary produces 6-humps per fundamental cycle in the DC output, theoretically, for a *p*-pulse PST, the ideal number of secondary windings *w* is

For MV motor drives, the choice of the pulse number p depends on: 1) the input current harmonic requirements and, 2) the number of DC supplies needed by the inverter.

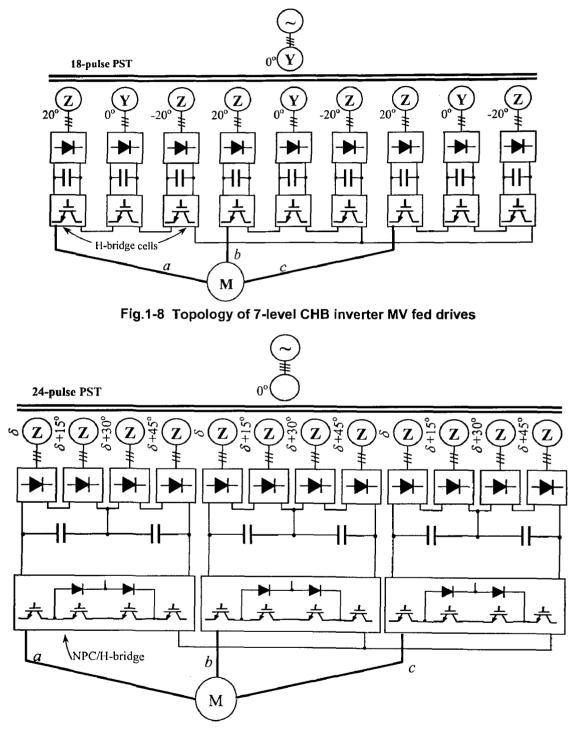

Obviously the actual number of secondaries in Fig.1-7, Fig.1-8 or Fig.1-9 is three times the number predicted by Eq.(2.8). The number of secondaries in Fig.1-7 and Fig.1-8 cannot be reduced because of the number of isolated DC sources required by the inverter. However, it could be reduced for the topology of Fig.1-9 where the number of secondaries is more than the number of required DC sources. It should be noted that even though the secondaries in Fig.1-7 and Fig.1-8 can not be reduced, according to Eq.(2.8), the number of pulses can be expected to be tripled for better harmonic cancellation. For example, the PST in Fig.1-7 has 6 secondary windings, thus 36-pulse harmonic cancellation can be achieved theoretically.

Now let's focus on Fig.1-9. We have two alternatives to reconfigure the rectifier: to triple

22

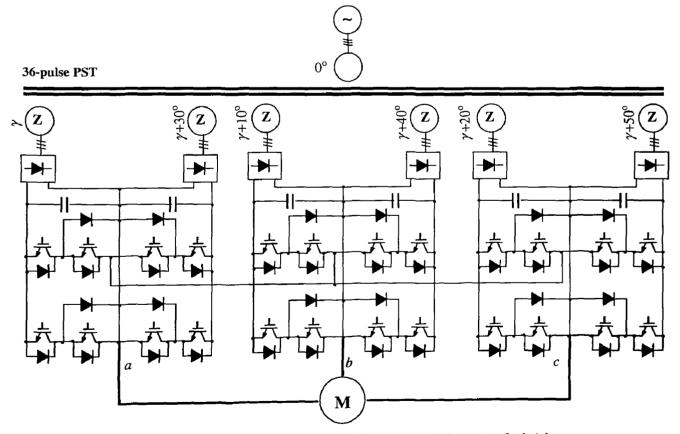

the pulse number or to reduce the secondary number. With 12 secondaries, 72-pulse harmonic cancellation could be expected. However 72-pulse harmonic cancellation is not practical from both the viewing points of the PST manufacturing and IEEE 519-1992 harmonic requirements. Because only 6 DC sources are needed for fixed neutral point potential, the number of secondaries can be halved, leading to a 36-pulse configuration (Fig.2-2), where the secondaries are shifted by  $10^{\circ}$  from each other and  $\gamma$  is any angle that is practically meaningful.

Table 2.2 compares the major features of the 36-pulse rectifier and 24-pulse rectifiers in Fig.1-9. Obviously the topology of Fig.2-2 achieves better harmonic cancellation and uses fewer secondary windings although the ripple in the DC may be larger than that of Fig.1-9.

Now the problem is that 36-pulse PSTs are too complex for manufacturing. The problem can be solved by the proposed dual 18-pulse rectification.

Fig.2-2 Topology of 36-pulse 5-level NPC/H-bridge inverter fed drive.

| Item<br>Topology   | # of secondaries | # of rectifiers and caps | Lowest dominant<br>harmonic | # of ripples in DC<br>per cycle |

|--------------------|------------------|--------------------------|-----------------------------|---------------------------------|

| 24-pulse (Fig.1-9) | 12               | 12                       | 23                          | 24                              |

| 36-pulse (Fig.2-2) | 6                | 6                        | 35                          | 12                              |