# 615672128

# SELF-RESTORATION MECHANISM FOR RUN-TIME RECONFIGURABLE DATA-STREAM PROCESSORS

by

Irina Terterian, B.Sc., B.Ed.,

State University of Georgia,

Tbilisi, 1978

A thesis

presented to Ryerson University in partial fulfillment of the requirement for the degree of Master of Applied Science in the program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2004

© Irina Terterian, 2004

### UMI Number: EC52979

#### All rights reserved

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

# UMI®

UMI Microform EC52979 Copyright 2008 by ProQuest LLC All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

I hereby declare that I am the sole author of this thesis.

and Angel and Angel and Angel

en de la constante de la const La constante de la constante de

and the former and the former of the second

in a sure of the second se

ter e construction de la constru

: . . .

I authorize Ryerson University to lend this thesis to other institution or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

. . .

ii

.

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

| Name     | Signature | Address  | Date                                  |

|----------|-----------|----------|---------------------------------------|

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          | · · · · · · · · · · · · · · · · · · · |

|          |           |          |                                       |

| ·        |           |          |                                       |

|          |           |          |                                       |

| <u> </u> |           | <u> </u> |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           | <u> </u> |                                       |

|          |           | ·····    |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

|          |           |          |                                       |

# Self-Restoration Mechanism for Run-Time Reconfigurable Data-Stream Processors

Irina Terterian, Master of Applied Science, 2004 Electrical and Computer Engineering, Ryerson University

#### ABSTRACT

The cost of a hardware failure in high-performance computing systems is usually extremely high because of the system stall where billions of operations can be lost within one second. Thus, implementation of self-restoration mechanisms is one of the most effective approaches to keep system performance on a required level.

The project presents a new approach, which allows retaining the performance of the Run-Time Reconfigurable stream processing system on its maximum level. This becomes possible by development of multi-level self-restoration mechanism that consists of: restoration by FPGA-scrubbing, restoration by FPGA-slot replacement and restoration with optimum performance degradation. All above levels of restoration procedure were developed and tested on reconfigurable computing platform based on XILINX Virtex FPGA. Analysis of achieved results of the developed mechanism shows a very fast restoration of functionality and dramatic increase of lifetime of FPGA based computing platforms. Acknowledgements

The author would like to thank her supervising professor, Dr. Vadim Geurkov, for providing his guidance, knowledge and support. The author would also like to thank the members of the review committee for their participation. The author would like to thank the National Science and Engineering Research Council of Canada (NSERC) for providing funding support for this research project in the form of multiple grants to my supervising professor. The author would like to thank Ontario Graduate Scholarships (OGS) for funding this research through a scholarship.

s'

### Table of Contents

| 1. INTRODUCTION                                | 1 |

|------------------------------------------------|---|

| 1.1. Motivation                                |   |

| 1.2. Major principles of the proposed approach | 3 |

| 1.3 . Original Contributions                   | 4 |

| 1.4 . Thesis Organization                      | 6 |

|                                                |   |

| 2. REVIEW OF RECONFIGURABLE COMPUTING PLATFORMS    | 9   |

|----------------------------------------------------|-----|

| 2.1 Instruction level reconfigurable architectures | 0   |

| 2.2 Task level reconfigurable architecture1        | . 1 |

| 2.3 Segment level reconfigurable architecture1     | 2   |

# 3. RADIATION TOLERANCE OF THE RCP ......14

- 3.1 Radiation Damage of the Semiconductor Devices......14

- 3.2 Radiation Effects on Field Programmable Technologies ......17

| 20 | 4. FAULT DETECTION AND RECOVERY IN FPGA DEVIC |

|----|-----------------------------------------------|

| 21 | 4.1 Fault detection and location              |

| 25 | 4.2 Fault recovery                            |

| ORGANIZATION OF MULTI-TASK RECONFIGURABLE STREAM<br>PROCESSOR WITH SELF- ASSSEMBLING MUCRO-ARCHITECTURE34 | ŀ |

|-----------------------------------------------------------------------------------------------------------|---|

| 5.1 Organization of Virtual Hardware Components (VHC)                                                     | 5 |

| 5.2 Application Specific Virtual Processor assembling procedure                                           | B |

| 5.3 Re-configurable Parallel Stream Processor Architecture Organization42                        |

|--------------------------------------------------------------------------------------------------|

| 6. MECHANISM FOR ASVP SELF-RESTORATION47                                                         |

| 6.1 VHC scrubbing                                                                                |

| 6.2 CLB-column (slot) replacement50                                                              |

| 6.3. ASVP functional restoration with performance degradation                                    |

| 6.3.1. ASVP restoration with minimum restoration time                                            |

| 6.3.2. ASVP restoration with minimum performance degradation53                                   |

| 7. IMPLEMENTATION OF THE ELEMENTS OF SELF_RESTORATION<br>MECHANISM AND ANALYSIS OF THE RESULTS63 |

| 7.1 Test Platform63                                                                              |

| 7.2 Implementation of procedures for restoration without performance degradation                 |

| 7.3. Implementation of procedures restoration with performance degradation69                     |

| 7.3.1 Specifications for ASVP: "Hamming Distance Calculator" 70                                  |

| 7.3.2. Hamming Distance Calculator Architectural Representation 72                               |

| 7.3.3 Performance Estimation Model74                                                             |

| 7.3.4. Architecture-to-Task Optimization for Hamming Distance                                    |

| Calculator76                                                                                     |

| 8. CONCLUSIONS AND FUTURE WORK | 82 |

|--------------------------------|----|

| REFERENCES                     | 89 |

| LIST OF ACRONYMS               |    |

# List of Tables

Table 5.1: Code of associated ASVP

Table 5.2: VHC-core address conversion table

Table 7.1: Experimental results of functional restoration time and acceleration of

functional restoration comparing with entire FPGA re-programming

# List of Figures

•

| Figure 4.1 A simplified architecture of Adaptive Re-Configurable Platform 21    |

|---------------------------------------------------------------------------------|

| Figure 4.2 Architecture of a Field Programmable Gate Array                      |

| Figure 4.3 A covering Graph for a fault tolerant FPGA                           |

| Figure 4.4 Testing Programmable Logic Blocks                                    |

| Figure 5.1 Structure of partially reconfigurable Xilinx "Virtex" FPGA device37  |

| Figure 5.2 Micro-architecture of a Virtual Hardware Component                   |

| Figure 5.3 Data Flow Graph of stream processing task                            |

| Figure 5.4 ASVP architecture assembled in the FPGA from pre-compiled VHCs       |

| reflecting task DFG41                                                           |

| Figure 5.5 Architecture of Re-configurable Parallel Stream Processor (RPSP) for |

| multi-task & multi-mod workload43.                                              |

| Figure 5.6 Code of a task = Code of associated ASVP45                           |

| Figure 5.7 VHC# to VHC-core address conversion table45                          |

| Figure 6.1 VHC replacement using spare CLB-slots                                |

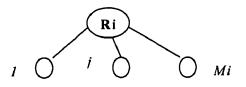

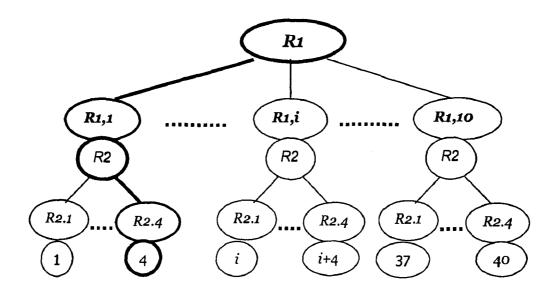

| Figure 6.2 Graphical presentation of a Virtual Hardware Component - R i, j54    |

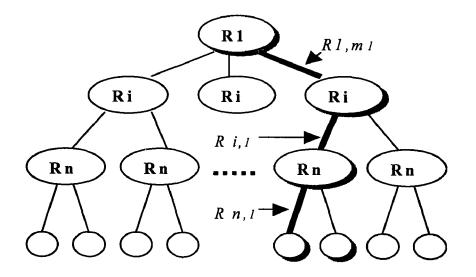

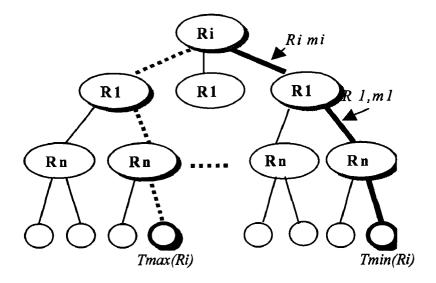

| Figure 6.3 Architecture Configurations Graph                                    |

| Figure 6.4 ACG hierarchic arrangement56                                         |

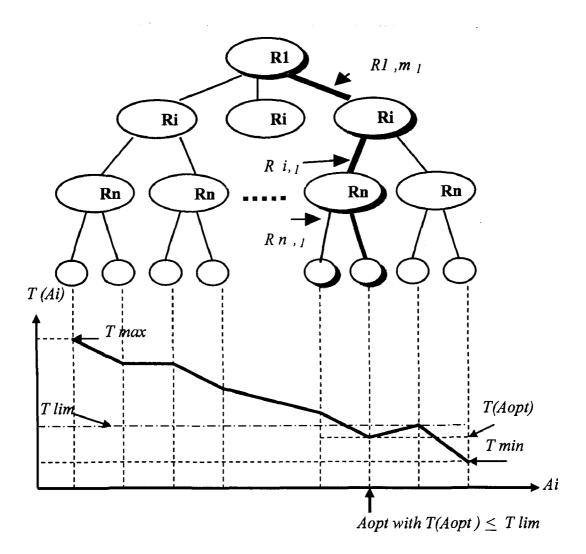

| Figure 6.5 Selection of the optimal variant of ASVP processing architecture on  |

| the partially arranged ACG58                                                    |

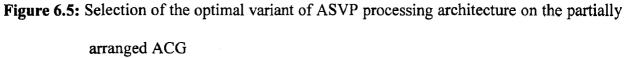

| Figure 6.6 Architecture Configurations Graph and performance diagram associated |

| to ASVP variants60                                                              |

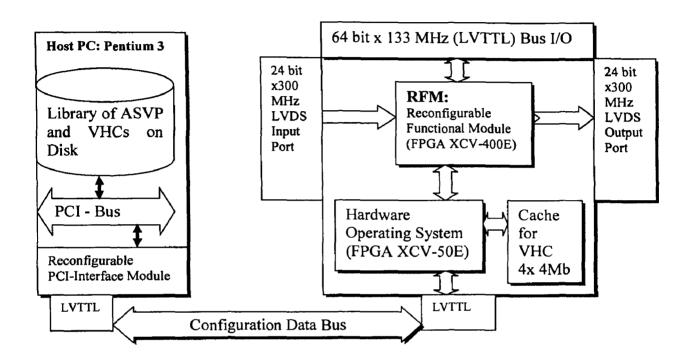

r An Tari Andrea an Angela Figure 7.1: Block diagram of the Reconfigurable Parallel Stream Processor Figure 7.2: Reconfigurable Parallel Stream Processing platform

Figure 7.3: Reconfigurable PCI-interface Module

Figure 7.4: VHC with corrupted interconnection on its micro-architecture

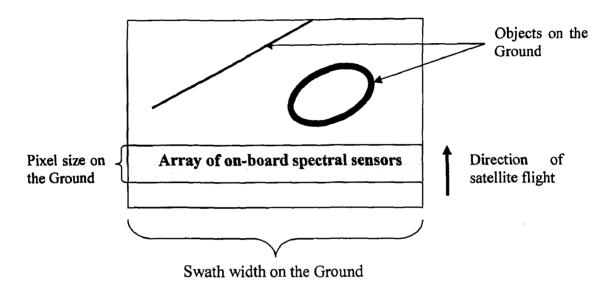

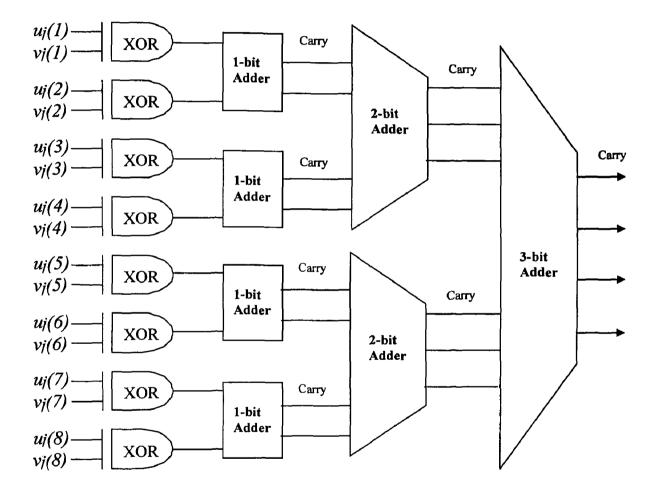

Figure 7.5: Spectral scanning on the Earth surface by the array of spectral sensors

Figure 7.6: Data Flow Graph for Hamming Distance Calculation

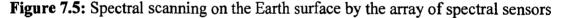

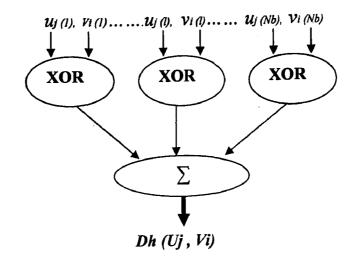

- Figure 7.7: Schematic diagram of resource **R1**, Variant **R1**,1: 8- XOR channels & 8-bit

- Figure 7.8: Architecture Configurations Graph (ACG) for HD-calculator variants Adder

- Figure 7.9: Hamming distances pipeline computational process of spectral and code vectors on the variant of calculator presented in Figure 5.2

xi

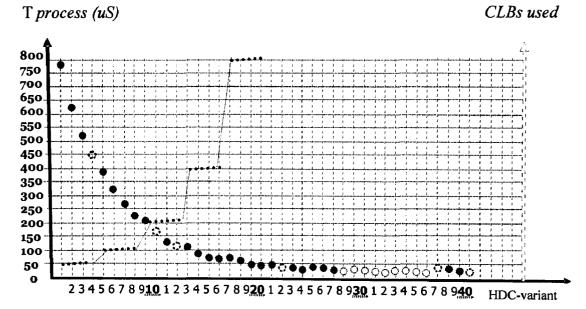

Figure 7.10: Arrangement of architecture variants of Hamming Distance

Calculator in order to values of data processing time.

her handle states of

#### **CHAPTER 1**

na ing mga salah na pilan alam para salah sa Salah sala

#### INTRODUCTION

#### **1.1 Motivation**

In many areas of application: video and image processing systems, high-speed communication, digital TV and audio broadcasting, data encryption and compression, multimedia and DSP the major requirement is processing of high volume of streamed data with very high performance. Recently, these performance requirements are in a range of 10-100 Giga bits per second. Usually, for all of the above areas of application the Application Specific Processors (ASP) are used. Most of these computing systems based on Application Specific Integrated Circuits (ASIC) are logic devices with a *fixed architecture* optimized for tasks algorithm and data structure. Within recent decade, the complexity of ASICs has increased in orders. That is why the probability of hardware fault in ASIC based computing platforms also has increased. On the other hand, in many applications such as: aerospace, nuclear power stations, military and some others the data-stream processing systems must reliably perform their functions in radiation intensive environment. The usual approaches of increasing system reliability based on modular or information redundancy as well as shielding technique is very expensive and power consumable. Simultaneously in most of the mission critical applications such as: satellite platforms, process control equipment in nuclear power stations, planetary exploration systems, earth orbital stations and many military applications hardware failure of even one system gate (out of millions) can cause incredible damage or even lost of very expensive systems. Even in most of commercial stream

processing systems such as Digital Video Broadcasting (DVB) and Digital Audio Broadcasting (DAB) every minute of broadcasting interruption costs many thousands of dollars.

The promising approach to increase system reliability for complex and mission critical computing systems is utilization of reconfigurable computing systems based on Field Programmable Array (FPGA) devices. This approach assumes ability to configure the application optimized processing micro-architecture by programming logic functions and on-44 chip interconnections into special Static Random Access Memory (SRAM) incorporated to .() the FPGA as a circuit configuration memory unit. This ability gives this system a unique feature for restorating its functionality simply by re-programming a configuration file into the configuration SRAM. In the case when one or more logic gates are damaged, micro-C architecture can be redesigned to avoid faulty logic gates and loaded then into the FPGA. Thus, this approach allows restoration or even modification of system functionality by remote reprogramming of the FPGA's configuration SRAM. However, several problems still 411 exist for the FPGA based computing platforms. Firstly, configuration SRAM itself can be съ., affected by radiation and / or power instability. Secondly, it can take a lot of time for redesigning on-chip micro-architecture avoiding faulty logic cells. In many practical applications long restoration time means complete mission fault.

i,

्र**ा**

Instead, in this paper the novel approach for restoration of the FPGA based reconfigurable computing system is presented. This approach allows self-restoration of onchip processing micro-architectures of stream processing logic circuits within very short period of time (hundreds of microseconds). A multi-level self-restoration mechanism developed in the capacity of this project can itself make decision what kind of restoration

procedure has to be implemented to: a) minimize restoration time, b) minimize logic resources, c) minimize performance degradation if, there is no other way to restore functionality of a system.

### 1.2 Major principles of the proposed approach

The proposed approach is based on the following major principles:

- 1. Utilization of partially reconfigurable FPGA devices as a component base of proposed self-restoration mechanism. This type of FPGA devices allows reconfiguration of small portions of on-chip logic circuitry without any interruption of data processing in the rest of FPGA device.

- 2. Utilization of Run-Time Reconfigurable computing platform as a system base of proposed self-restoration mechanism. This type of a computing platforms allows utilization of one part of system logic resources to restore other part of (damaged) logic without suspending of all computational processes running on a system.

- 3. Implementation of proposed method of self-assembling of processing microarchitectures on a base of the pre-compiled Virtual Hardware Components (VHC). This approach allows dynamic on-chip assembling of Application Specific Virtual Processors (ASVP). ASVP is a logic circuit with microarchitecture optimized for algorithm and data structure of a task to be

3

n we want the desired the second

executed. On the other hand, if any hardware fault occurs restoration can be performed by virtual re-assembling of ASVP micro-architecture.

- 4. Organization of self-restoration mechanism as multi-level procedure. This approach reflects nature of possible hardware faults occurring in the SRAM based FPGA devices. Multi-level organization allows to react on each type of possible reasons with respective restoration procedure. Multi-level organization of self-restoration also reflects internal conditions in the FPGA. There can only be two possible situations: there are spare logic resources or all off them are in use. In case when there is no spare logic resources in the FPGA self-restoration procedure reaches the highest possible level of restoration restoration with performance degradation.

- 5. Incorporation of Architecture-to-Task Optimization System (ATOS) automated high-level architectural synthesis mechanism for optimization of the restored micro-architecture to the task algorithm and data structure reflecting limitations of available logic resources.

All of the above principles that are embedded into the proposed self-restoration mechanism allowed reaching very high cost-reliability, cost-performance parameters and increase system lifetime of high-performance parallel stream processing systems working in harsh and radioactive intensive environment.

#### **1.3 Original Contributions**

$\pm 1$

A ..

67.1

The thesis presents a new approach for self-restoration mechanism and methods for its implementation in Run-Time Reconfigurable data-stream processing systems based on

partially reconfigurable Field Programmable Gate Array devices. This approach allows fast and effective restoration of system functionality after temporary and permanent hardware faults. Temporary hardware faults in the SRAM based FPGA devices usually are caused by radiation effects (e.g. SEU - Single Event Upset). However, permanent hardware faults can be caused by: hidden manufacturing defects, corrosion, time-dependant dielectric breakdown, etc. The proposed self-restoration mechanism being multi-level is adaptive to the type of a hardware failure because it can apply strategies of different levels of restoration. For example, it tries first to recover from the fault assuming that fault is temporal. However if, after certain attempts fault still exists mechanism jumps to the next level of restoration using logic replacement procedures. It can happen that all spare logic resources are already in use when permanent hardware fault is detected. In this case, mechanism would jump to the level of restoration with performance degradation. On this level mechanism selects the best configuration of stream processing micro-architecture with minimum performance degradation.

In this regard the major contributions are as follows:

- Development of logic replacement technique based on re-addressing of Virtual Hardware Components to the spare slots in the partially reconfigurable FPGA devices (Xilinx Virtex-E, Virtex-2 and Virtex-2Pro families of FPGAs). This technique was presented in [1].

- Development of method for optimization performance degradation in case of a restoration of functionality with limited logic / routing resources. This method was presented in [2].

- Analysis of radiation effects which can cause hardware failure in SRAM based FPGA devices and possible mitigation techniques for this effects. On a base of this analysis the complete multi-level hardware restoration mechanism was developed and presented in [3].

- Modeling and simulation of major elements of the proposed self-restoration mechanism were performed using ALTERA MAX Plus II and XILINX ISE 6.2i

CAD systems. Results were presented in [3] and [4].

- Implementation and testing of major elements of the proposed self-restoration mechanism in the RTR Multi-Stream Processor AGORA-2 (Adaptive Group Organized Reconfigurable Architecture). Results were presented in [2], [3] and [4].

- Modeling of prototype of Hamming Distance Calculator with ability of restoration with optimum performance degradation. Analysis of results was utilized for preliminary study for development process of the new generation of on-board computing platform for Canadian satellite RADARSAT-2.

#### **1.4 Thesis Organization**

् इन

The thesis consists of eight Chapters. The rest of the thesis paper is organized as follows:

- Chapter two consists of the literature overview and classification of major types of existing reconfigurable computing systems. This chapter gives background on run-time reconfigurable computing platforms.

- The third chapter presents analysis of radiation factors that can cause hardware fault in the semiconductor devices. Also, a special section in this chapter gives literature survey on radiation effects in the SRAM based FPGA devices.

- Chapter four encompasses the analysis of existing methods of hardware fault detection, location and restoration based on extensive literature survey. This study was very important because it allows utilization of some existing methods of hardware fault detection and location. This component of fault tolerance for FPGA based computing platforms was not a target for this project. However, without understanding fault detection and location methods and procedures it would be difficult to develop fault restoration procedures.

- Chapter five describes architecture organization of multi-task reconfigurable stream processor with self-assembling micro-architectures of application specific computing circuits. This chapter gives background information for computing platform where the proposed self-restoration mechanism can be implemented. Self-assembling procedure and its application for self-restoration of the Application Specific Virtual Processor is also described in details in this chapter.

- Chapter six gives the overview of the proposed method. It consists of a full

description of all components of the proposed self-restoration mechanism.

Interaction between different levels of the self-restoration mechanism is also

described. In this chapter the method of restoration with performance degradation

also is presented. This chapter gives also background on architectural synthesis

method used for the developed method of restoration.

- The implementation and analysis of test results are presented in Chapter seven. Brief description of test platform is given, as well as comparative analysis of test results of FPGA scrubbing and logic replacement procedures comparing with the existing approaches. The detailed explanation of Hamming Distance Calculator

(HDC) prototype implementation with ability for restoration with performance degradation is also presented in deep details. Analysis of results of modeling of prototype behavior also is given.

• Finally, conclusions and description of future work is given in the Chapter eight.

Ę

### **CHAPTER 2**

### **REVIEW ON RECONFIGURABLE COMPUTING PLATFORMS**

Recently more and more research and development groups and organizations working in the area of high-performance computing systems start to use Field Programmable Gate Array (FPGA) devices as a component base of their systems. Since 1995, number of types of FPGA-based computing platforms (R&D stage) had doubled [5]. The reason is that in many applications where the performance of a software implementation is not sufficient and the high expense and long design time of Application Specific Integrated Circuits (ASICs) cannot be afforded, FPGA devices has provided a very cost-effective solution. These new types of microprocessor-free architectures based only on reconfigurable devices are becoming more and more popular solution for high-performance computing platforms. Main areas of application for these platforms are digital signal processing, image processing and pattern recognition, digital video/ audio broadcasting and communication, high-performance data acquisition and control systems, compression / decompression and encryption / decoding devices.

Broadly all FPGA-based computing systems can be divided on two big categories:

- 1. Statically configurable systems and

- 2. Run-time reconfigurable systems.

The first approach is normally used for rapid prototyping and small production, where development of ASICs is too expensive and time-to-market is very short.

Run-time reconfigurable systems allow reuse of FPGA hardware during the lifetime of the task in the system. This gives a rise to a powerful computing paradigm where one or more reconfigurable hardware components can serve as a virtual hardware space, similar in principle to virtual memory. Several architectural approaches were proposed and implemented in different reconfigurable computing platforms within the recent decade.

From system architecture viewpoint, run-time reconfigurable computing systems can broadly be classified into three categories associated with the level of computational process where re-configuration takes place:

1) Instruction level;

2) Task level and

3) Task segment level.

#### 2.1 Instruction level reconfigurable architectures

These systems are based mostly on Dynamically Programmable Gate Array (DPGA) devices [6] and allow reuse DPGA parts (often called frames) for different instructions. This reconfiguration could be done in a very short time and allow implementation of a custom instruction set. The reconfigurable device in these systems usually tightly coupled with the processor to be used as the accelerator for computationally intensive and repetitive segments of a program. There are many examples of such systems [7], [8] and [9]. The Hybrid RISC reconfigurable architectures, where reconfigurable component is a part of CPU [9] and [10] also can be associated with this class of architectures. An advantage of this type of reconfigurable accelerators is that being implemented into common general purpose computing architectures they can dramatically increase CPU performance. However this performance still is limited by performance of a microprocessor coupled with FPGA. This microprocessor now becomes responsible for management of the reconfigurable component

and synchronization of two parallel processes in the microprocessor itself and in FPGAbased accelerator. It increases amount of extra control hardware or decrease performance of the microprocessor. Another disadvantage of this type of systems appears in a multiprocessing environment. Cost-performance parameters are very poor because of limitations for reconfigurable resource sharing among the processors due to the tight coupling.

#### 2.2 Task level reconfigurable architectures

This type of systems usually contains a collection of configurable processing elements (functional units) communicating via a network of configurable switches. The architecture of these systems has to be configured for the task. There is a big number of systems that fall in this category: RaPid [ 11], NAPA [ 12 ], Splash-2 [ 13 ] and many others. This type of architecture allows achieving very high performance because the data-flow graph of the task can be completely "covered" by hardware specifically tuned for task operations. However, the time for compiling a system can be very long and consequently it is very difficult or even impossible to employ these systems in applications where fast dynamic recompilation in real-time needed.

Another performance limitation comes from the communication network. Three main concepts were used in this type of systems: a) direct (point-to-point) connections between FPGA-based functional units (usually pipeline connections [11], [13]). This type of connectivity gives minimum propagation delay for the data transfer; b) crossbar switches (switching networks) [14], [15]. This type of connectivity gives higher propagation delay than direct connections, because signals have to pass a multi-stage multiplexing units; c) system buses usually used as a message passing networks for multi-processing

reconfigurable systems [16], [17]. Information transfer rate is the lowest comparing with previous types of interconnections but cost-effectiveness is usually much better.

#### 2.3 Segment level reconfigurable architectures

These types of reconfigurable computing systems are based on the idea that a task can be divided on several segments when the processing time of each segment is equal or higher than FPGA reconfiguration time. In this type of systems the first temporal partition receives input data, performs computation and stores the intermediate result into on-board memory. FPGA-based functional unit is then reconfigured for the next segment, which computes results based on intermediate data from previous partition. Such temporally partitioned systems are called Run-Time Reconfigured (RTR) systems [18], [19]. RTR-systems allow to "program" cost-performance parameters. If it is necessary to reach maximum performance, all segments of the task can be mapped in different FPGA-based functional units. If performance requirements are low, task segments can be performed one after another on one functional unit. Thus, the concept of RTR systems allows achieving very high level of costefficiency. Another big advantage of this type of systems is that reliability of the system can be very high. If system architecture contains many uniform RTR modules and fault occurs in one module within task processing, system can eliminate fault module by reconfiguration. In worst case it can cause reduction of performance if no spare modules are available. Time delay in this case is equal to the segment processing time plus module configuration time and is in matter of tens of milliseconds. Thus, there is a direct relationship between performance and reliability for such type of systems when the module fault causes only performance reduction but not a fault of all system.

Proposed research was concentrated on the Run -Time Reconfigurable-computing systems because of high cost-performance and performance-reliability characteristics.

### CHAPTER 3

### **RADIATION TOLERANCE OF THE RCP**

One of the major problems for FPGA based computing systems as well as any other semiconductor devices is radiation tolerance. To mitigate this problem usually a special radiation hardened devices have to be utilized. However, high cost of such devices increases system price dramatically. Furthermore, radiation hardened semiconductor devices still have limited lifetime. Instead, as an alternative the recovery mechanisms can be implemented. This approach is conceptually impossible to implement in regular logic devices due to the lack of hardware flexibility. However, it is possible to implement it in reconfigurable logic, especially in SRAM based FPGA devices. To investigate this possibility of radiation effects in semiconductor devices including FPGA, the literature research was conducted.

#### 3.1 Radiation Damage of the Semiconductor Devices

The operation under radiation of any semiconductor devices depends on the near perfection of the crystalline lattice to prevent defects that can trap charge carriers and lead to incomplete charge collection. Any extensive exposure of semiconductor devices, however, ensures that some damage to the lattice will take place because of the disruptive effects of the radiation passes through the crystal. While the energy that goes into the creation of electron-hole pairs leads to fully reversible processes that leave no damage, non-ionizing energy transfers to the atoms of the crystal lead to irreversible changes. The effects tend to be relatively minor for lightly ionizing radiation (beta particles or gamma rays) but can become quite significant under typical conditions of use for heavy charged particles. For example, prolonged exposure of silicon surface p-n junction to heavy ions or fission fragments will lead to measurable increase in the leakage current [20].

The radiation-induced damage can be classified into the two categories of bulk and surface effects. The most fundamental type of bulk radiation damage is the Frenkel defect, produced by the displacement of an atom of the semiconductor material from its normal lattice site. The vacancy left behind, together with the original atom now at an interstitial position, constitutes a trapping site for normal charge carriers. These are sometimes called point defects to distinguish them from more complex "clusters" of crystalline damage that are formed along the track of a primary "knock-on" atom if sufficient energy is transferred. Gamma rays and electrons with energy of a few MeV or less create only point defects, whereas heavy charged particles of equivalent energy are generally more damaging because they also form clusters. The number of Frenkel defects produced by a fission fragment is estimated to be about 100-1000 times greater than that produced by an alpha particle. At the other extreme, an incident electron or beta particle requires a minimum of about 145 keV to produce a defect, and very little damage is observed for electrons whose energy is much below 250 keV. The severity of damage to be anticipated is therefore a strong function of the nature of the radiation involved. Some minor annealing of the radiation damage can occur over long periods of time, but for all intents and purposes, the damage is permanent [21]. The increase in leakage current appears to be more directly related to surface effects and also contributes to increase in leakage current fluctuation. In devices such as silicon MOS-FET that include oxide passivity layers, the surface effects are closely related to the ionization created within the oxide and its trapping at interfaces. For penetrating radiation including

gamma rays or neutrons, the damage is generally distributed throughout the device and the direction of incidence of the radiation has little effect. For electrons or charged particles, however, the orientation with respect to the silicon wafer is important. Irradiation of the front (or gates) surface of totally depleted MOS-FET requires exposures that are several orders of magnitude less than those needed to produce the same effects by irradiation of the back (or aluminum) contact.

For silicon surface p-n junction various data have been published on the integrated flux of charged particles required to produce a significant deterioration in p-n junction performance. Although subject to a great deal of variability, depending on the specifics of each experiment, serious changes appear to take place for irradiations of about  $10^{14}$  fast electrons/cm<sup>2</sup>,  $10^{12}$  to  $10^{13}$  protons/cm<sup>2</sup>,  $10^{11}$  alpha particles/cm<sup>2</sup>, and about  $3 \times 10^{8}$  fission fragments/cm<sup>2</sup>. Exposure to fast neutron fluxes of about  $3 \times 10^{11}$  neutrons/cm<sup>2</sup> and gamma rays doses of about  $10^{6}$  R are also sufficient to lead to significant performance degradation

An effect known as *type inversion* has been observed to occur in high resistively *n*-type silicon after prolonged exposure to fast neutrons or high-energy particles with integrated fluency of about  $10^{13}$ /cm<sup>2</sup>. The effective concentration of donors gradually decreases with exposure, until a transition to *p*-type behavior is observed. Some models for this change postulate the radiation-induced formation of deep acceptor levels, close to the center of the band gap, that become electrically active when voltage is applied to p-n junction. The device may continue to function after the inversion with the same polarity of applied voltage, but eventually the growing concentration of acceptors raises the voltage level required for full depletion to levels beyond those causing breakdown.

1

### 3.2 Radiation Effects on Field Programmable Technologies

Field programmable gate array (FPGA) devices, used in spacecraft electronics, have grown in size (number of logic gates) over the past few years. Manufacturers of FPGA take different technological and architectural approaches that directly affect radiation performance. After analyzing current technologies and architectures and their radiation effects implications we can consider as following:

- There are basic radiation effects on semiconductor devices as was described in the paragraph 3.1, radiation damage of the semiconductor devices. The radiation start to directly affect the Single Event Upset (SEU) performance with threshold LET far beyond 60 MeV-cm<sup>2</sup>/mg and total dose more than 400 krad(Si).

- 2. There is limitation for MOS-FET devices with the dielectric layers in the active area of device. This layer accumulates the electrical charge with the radiation dose. During exposure to ionizing radiation, electron-hole pairs are formed in the insulating silicon oxide layer immediately below the gate. If a positive bias voltage is applied to the gate during the exposure period, there is a tendency for these charges to separate. The electrons will move toward the gate, and the holes toward the SiO<sub>2</sub>-Si interface where they tend to be trapped and form a fixed positive charge. The effect of this charge is to cause a shift to more negative values in the threshold gate voltage, and the amount of this voltage shift is a reasonably linear measure of the integrated dose. The higher the bias voltage, the greater will be the fraction of the charges collected, resulting in higher no stability. If the MOSFET structures have an effective area of less than 0.1 mm<sup>2</sup> and oxide thickness of 100nm it shows sensitivities in the range of 10-1000 mV/Gy. With a

readout capable of measuring changes of the order of 0.5 mV, the corresponding minimum measurable dose would be  $5 \times 10^{-2}$  Gy (5 rad) to  $5 \times 10^{-4}$  Gy (50 mrad). MOSFET designs with very thin oxide layers and low threshold voltage can achieve radiation stability. It can reach SEU performance for total dose more than 300 krad and threshold LET 65MeV-cm<sup>2</sup>/mg.

3. There is technological and architectural "noise". Manufacturers update their designs and continue to shrink the fabrication process. As the result it is difficult to understand the causes of changing radiation characteristics. Sometimes change of technology can lower SEU performance for total dose less than 3 krad and threshold LET 5MeV- cm<sup>2</sup>/mg. The racing for the Commercial-Off-The-Shelf (COTS) devices to be used in a radiation environment leads to very complicate situation. Several studies performed to determine the affect of design and process on total dose capability of commercial parts and gain additional insight into the devices' total dose limitation [24, 25] had little success. When quick radiation test can not be performed during the manufacturing, the very nature of radiation stability requires carefully selected architecture of the device and very stable technological process. We have reasons to believe that radiation stable FPGA will be fabricated on special foundry in the very near future. The research group from NASA and Actel Corporation has the same vision and shifted the research efforts to the development of new software to improve the SEU performance of a flip-flop, exploiting the configurable nature of FPGA technology, untill radiation - proof FPGA will be available. 4. There are radiation-proof technologies MNOS (Metal-Nitride-Oxide-Semiconductor) -

ę.

1

EPROM devices and radiation stable MNOS-FET devices on an insulating silicon nitride

substrate. It has been found [22] that under an irradiation of 1000 krad in these devices was not produced inversion layer in the silicon and no leakage current was observed.

5. Recently XILINX Inc. has developed the Vertex QPRO family of radiation hardened FPGA devices for space and satellite applications with up to 1,124,022 system gates (96 frames x 64 CLBs per frame) and guaranteed total ionizing doze to 100 KRad(si) with latch-up immune to LET = 125 MeV cm2 / mg [23].

The Appendix C "Radiation in Space Environment" describes some particles and their properties important for radiation effects for semiconductor devices. It also gives definitions and conversion units in irradiation physics used above.

에 있는 것 같아요. 이 가지 않는 가 같아요. 이 것 같아요. 이 같아요.

a service and the service of the ser In the service of the

n 1999) An the Antonio Charles and Anto

.

an an tha an an Araba Araba an Arab

#### **CHAPTER 4**

#### FAULT DETECTION AND RECOVERY IN FPGA DEVICES

Another aspect to be considered was fault tolerance of RCP-based on-board computing systems. Conceptually, the uniform organization of all levels of system hierarchy of RCP hardware such as:

a) logic gates in Common Logic Blocks (CLBs),

b) CLBs in FPGAs

c) memory cells in ROM and SRAM-devices

allows simple replacement of faulty elements (system gates, memory cells, etc.). This conceptual possibility needs to be researched more deeply for the development of reliable run-time diagnostic and recovery mechanisms.

The objective of the research is development of methods and hardware/software means, which being incorporated into the RCP would increase its fault tolerance. These methods should provide high reliability and small time for tolerating faults, and the corresponding means should have small hardware/software overhead. We will break this task into three subtasks:

- 1. Fault detection,

- 2. Fault location and

- 3. Fault recovery

Each of these subtasks will contribute to the above-mentioned characteristics of fault tolerance.

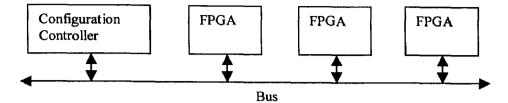

The simplified architecture of the On-Board RCP is presented in Figure 4.1. The Configuration Controller (CC) supplies configuration sequence to the RCP.

Figure 4.1: A simplified architecture of the Adaptive Re-Configurable Platform

#### 4.1 Fault detection and location

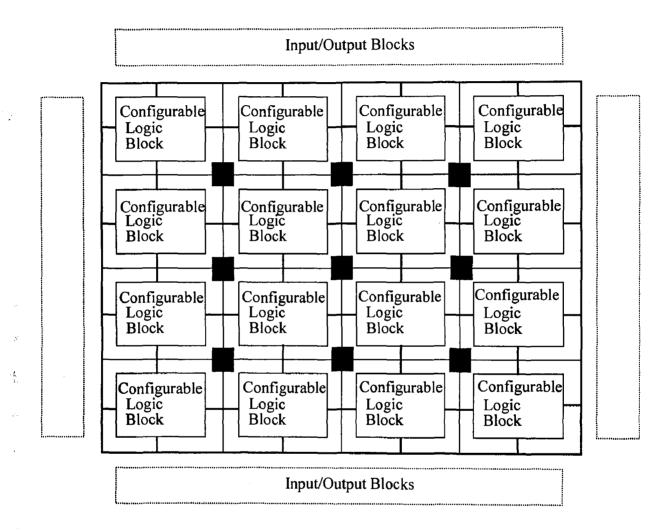

Fault detection in FPGA devices directly depends on internal organization of FPGA micro-architecture. This micro-architecture consists of a number of Configurable Logic Blocks (CLBs) interconnected by wires and switch boxes with each other and to the Input/Output Blocks (IOBs). The simplified architecture is shown on Figure 4.2. The CLB contains logic function generators, flip-flops (latches), and a number of multiplexers and associated circuitry. Wires within the FPGA are connected through pass transistors. The pass transistor is turned on or off by loading a binary value into the configuration SRAM cell connected to its gate. The CLBs contain function generators, which are also made up of SRAMs. A function generator has a Look-Up Table (LUT) made out of SRAM cells, together with some addressing circuitry. The LUT can be used for implementing combinational logic or as a RAM.

For an FPGA-based Reconfigurable system, faults can occur in the logic blocks (LUTs, CLBs, etc) and in switches that provide connection between the different logic blocks. A typical fault in a logic block may be a stuck-at fault in any LUT location. A typical interconnect fault may be a stuck-at fault in the configuration SRAM cell whose content turns a pass transistor on or off, providing interconnection between two leads. Both of these types of faults are equally important. From the test point of view, it is now widely admitted that FPGAs cannot be considered as classical digital ASICs [35].

Classical test approaches fail when applied on FPGA. In the recent published works, different test aspects are considered: Boolean testing of FPGA [25, 26, 28], BIST for FPGA

$\mathcal{O}$

[25, 26], I<sub>DDQ</sub><sup>1</sup> testing of FPGA [27], diagnosis of FPGA [29]. Because of the complexity of FPGA testing, usually each paper targets a specific FPGA part: the interconnect in [26, 28,30], the logic cells in [25, 27], the memory cells in [32, 33, 34],

the logic interconnect interface. Indeed, FPGAs appear as very complex circuits and these works use a classical divide and conquer approach.

In [25 -34] authors try to generate a *manufacturing oriented* test procedures. In [35], the *application oriented* test procedure is proposed, which can be used by an FPGA user. In this procedure, the user does not need to test the complete FPGA. He is only interested in testing the part of the FPGA used for his specific application. Test pattern generation in such case can be significantly accelerated. The paper targets only logic cells of an FPGA.

In [24] authors address the fault location problem for the FPGA logic blocks. Testing the logic blocks of Reconfigurable FPGA devices has been studied by many researchers [36-38]. Testing interconnect switches was discussed in [28, 39]. Techniques to locate faulty FPGA interconnects are described in [29, 40]. The technique, discussed in [38] requires a fixed number of reconfiguration sessions. It reconfigures some of the logic blocks as pattern generators or response analyzers, while testing the other blocks and vice-versa. The technique does not use any knowledge of the application that was implemented in the FPGA. Hence, it requires a set of configurations that cover all the faults under consideration for all possible configurations. This technique is extended in [41] for diagnosis to locate the faulty logic blocks in an FPGA.

<sup>&</sup>lt;sup>1</sup>  $I_{DDQ}$  is the quiescent current consumed by an FPGA. If two gate's outputs (or interconnects) are connected (bridging fault) then placing opposite logic values on those outputs will lead to the increase in  $I_{DDQ}$ . This current can be measured for every possible bridging fault, which allows testing the FPGA [Error! Reference source not found.].

The method discussed in [42] can be used to locate multiple faults in an FPGA. The basic idea is similar to that of [41]. Typically, a part of the FPGA is reconfigured to test another part and vice-versa. For example, the FPGA is divided into three sets of CLBs and each set tests another set according to a diagnostic graph. The test time in this method depends on the number of faults and is independent of the array size. The techniques in [41] are based on BIST.

Another application independent diagnostic technique is presented in [43]. The technique consists of two steps: horizontal diagnostic and vertical diagnostic. These two steps identify the row and column respectively that contain a faulty CLB. The C-testability concept [44] is used to improve this technique such that the test time is independent of the array size.

All the techniques mentioned in [28, 29, 36-44] are application independent and can be used for both production test and field test. However, when diagnostic is needed for an FPGA that implements a fixed application, the diagnostic procedure can be accelerated by using the design information rather than testing for all possible configurations [24]. In [24], the authors focus on combinational logic. A novel aspect of the technique is the way the concept of pseudo-exhaustive BIST has been applied for fault-location purposes. Another novelty of the approach lies in the fact, that the routing structure of a CLB is not altered. This is important feature, because typically designs mapped to FPGAs are routing-limited. Also, modifying the existing routing configuration during each fault location step is time consuming. Another advantage of this technique is that, with partially Reconfigurable FPGAs, while the circuit under consideration is being diagnosed, the remaining part of the system whose inputs are not connected to the outputs of this circuit can still be operational.

And the state of the second

24

nn a se na st

the second second second second second

In [45] distinction is made between configuration-independent testing and configuration-dependent testing. In configuration-independent testing, no assumptions are made about the way in which the user will configure the FPGA. The goal is to maximize the fault coverage for all possible configurations.

Configuration-independent testing is done when the FPGA is manufactured. Configuration-dependent testing, on the other hand, involves testing that a *particular* FPGA configuration is fault free. Higher fault coverage (for the particular configuration) can be achieved with less test time. The approach described in [45] is a configuration-dependent test technique for interconnects. Configuration-independent test techniques for interconnects [27-29, 37, 46] has the following drawbacks:

- 1. Time it takes to develop the diagnostic test necessary to locate the faults

- 2. Time to develop test configurations that provide a high coverage

- 3. Time to run the tests

and the second secon

The configuration-dependent test technique test method of [45] addresses all of the above problems. The method detects and locates all stuck-at and bridging faults in the interconnect switches for particular FPGA configuration. This is done by modifying the original configuration by only changing the logic function of the CLBs to form test configurations that can be used to quickly test the interconnect (the "walking-1" approach). A systematic procedure is applied to the original configurations are chosen in such a way that the "walking-1" approach can be used to detect and locate all stuck-at and bridging faults in the interconnect with a small set of test vectors. Since only the logic

functions of the CLBs are changed, time-consuming placement and routing is avoided. The process of generating the test configurations and test vectors is fully automated and very fast.

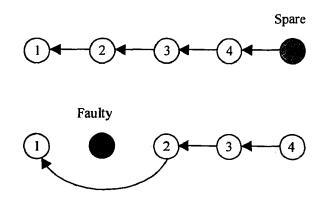

### 4.2 Fault recovery

If the fault has been detected and located, then it can be tolerated in a way described in [47]. Each primary cell u in the FPGA is assigned a cover cell, which can be reconfigured to replace it in the event that cell u becomes faulty. Primary cells are assigned to cover other primary cells in a chain-like manner, with a spare cell covering the last primary cell in the chain (Figure 4.3). These chains are defined to be along either rows or columns of the array, with a spare cell at the end of each row or column. In order for a cell to cover another cell, first, the cover cell must be able to duplicate the functionality of the dependant cell. This is easy in an FPGA, since all cells are identical.

**Figure 4.3:** A covering graph for a fault tolerant FPGA with four primary cells and one spare cell. Reconfiguration in the covering graph after cell # 2 becomes faulty.

Second, the cover cell must be able to duplicate the connectivity of the dependant cell with respect to the rest of the array. The method of ensuring connectivity is described in [47].

Each net connected to a cell must also include a cover (reserved) segment bordering the cover cell. These cover segments allow the logical connectivity to be maintained. The reconfiguration procedure assumes that cover segments necessary for reconfiguration around a faulty cell are provided by the routing tools and included in the initial configuration data that is loaded serially. Channel segments reserved for use in reconfiguration do not add extra parasitic delay to nets in a non-reconfigured array, since they are connected only when needed. No re-routing is necessary in the event of a fault.

In their fault tolerant technique, Kumar at al. used adaptive customization to avoid defective sections and artificially enhance a programmable gate array's yield [48]. Their technique was strictly off-line and fault tolerance was achieved by bypassing faulty programmable logic cells at the time the circuit was initially mapped to the FPGA. They described a two-step process to achieve defect tolerance: test of an un-programmed device to locate defective components and program the device to avoid the defective portions. They presented heuristics for adaptively programming an FPGA in the presence of faults.

Hatori at al. introduced redundancy as a fault tolerant method for FPGAs [49]. Their method used specialized selector circuitry to reconfigure FPGA circuits in the presence of faults. Similar to methods used for fault tolerance in SRAMs, an additional column of programmable logic blocks is added to the FPGA. In the event that a logic block was faulty, all functions mapped to the column where the faulty block was located were shifted toward the spare column. All subsequent columns of functions between the column with the faulty block and the spare column were also shifted toward the spare column. They did not detect faults, only reconfigure around them. Since they eliminated an entire column for one fault,

their fault tolerance was low, and they estimated a performance degradation of 5%. This was an off-line technique.

$\epsilon_{\rm M}$

Ē,

$\mathbb{I}_{\theta}$

Durand and Piquet proposed a fault tolerant FPGA architecture with the ability to repair itself in the presence of faults [50]. They used a special multiplexer with repair and self-diagnosis capabilities. Their special circuitry was capable of detecting logic failures during runtime, and the architecture had a limited capability to reconfigure itself dynamically. Their fault tolerant technique allocated two extra columns of cells, and in the event that a fault was detected, they bypassed the faulty column by shifting toward the spare column. Since the author's reported that more than complete logic redundancy was required for their method, the area overhead for fault tolerance exceeded 50%.

Narasimhan at al. developed an of-line fault tolerant technique for FPGAs or Wafer Scale Integrated Arrays [51,52]. They use a pebble shift algorithm to reconfigure around faulty blocks. Their method is flexible, since it is not limited to one fault per row, column or tile. Howard and Tyrrell described ideas for increasing yield on FPGAs [53]. Their idea was to insert extra bypassing columns or rows into the FPGA. They looked at both removing an entire row (column), if it contained a fault and removing only the faulty block from the row. Their methods were strictly for yield enhancement and the faults were bypassed at the time the configuration for the FPGA was downloaded. They also introduced global long lines to reduce the performance hit associated with reconfiguration.

Kelly and Ivey used redundancy to tolerate faults in applications mapped to FPGAs [54]. Their technique used a shift method to reconfigure in the presence of faults. They incorporated a reconfiguration switch and used normal place and route tools for mapping

circuits to FPGAs. A step-based switch configuration algorithm was used to configure the special switches around faulty elements. This technique was also off-line.

Cuddapa and Corba used Xilinx SRAM based FPGAs to demonstrate the fault tolerant capabilities of FPGAs [55]. In their study, they randomly picked logic blocks to be faulty. Then they reconfigured the circuit around these faults using commercially available tools. The main contributions of their work were an algorithm to determine fault coverage of a design and a definition of the fault recovery rate for any given design implemented in SRAM-based FPGAs. Additionally, they demonstrated that fault recovery was possible on FPGAs by other than modular redundant methods. This technique was off-line and did not include fault detection.

Hanchek and Dutt developed a method to increase FPGA yield [47,56]. Their method uses node covering and reserved routing resources to replace the functionality of faulty cells. One row (column) of cells is reserved for spares. If a cell in any given column (row) goes bad, the functionality of all cells in the column (row) from the faulty cell to the spare is shifted toward the spare cell. Spare routing resources are used to eliminate overhead of re-routing the updated circuit placement. Relative to covering interconnect faults, they use a similar idea where spare interconnect resources are allocated as a grid, and when a fault occurs, it is replaced by an extra segment or grid of segments. The main advantage of this method is that it is very fast. Since the spare resources have already been allocated to cover a limited number of faults, the reconfiguration time is linear with respect to the number of faults. The main problem of this method is limited fault tolerance, namely only one cell per column (row). If two faults were found in the same row, this method breaks down. Mahapatra and Dutt proposed a method that dynamically allocates interconnect resources to bypass faulty cells after faults have been located [57]. If the new required segments conflict with the current usage of routing tracks, the layout is incrementally modified to make room for the new segments. This method is dynamic only with respect to the interconnect resources, as the spare cells are statically allocated.

Emmert and Bhatia developed a fault tolerant technique for incrementally reconfiguring FPGA mapped circuits around faulty programmable resources [58, 59]. They used minimax grid matching, to match faulty PLB locations to unused spare PLB resources. Then they incorporated a shift methodology to shift PLBs between the faulty PLB and its matched spare location toward the spare location. For interconnect faults they introduced the idea of an embedded incremental router to route around faulty interconnect resources. The router uses the read/write capability of the FPGA configuration memory to rip-up and reroute without a netlist. While their method for reconfiguring around faulty PLBs was applied to the Xilinx FPGA, their fault tolerant technique for interconnects was applied to an artificial FPGA architecture, not to a commercial FPGA.

Lach et al. developed a low-overhead on-line fault tolerant system [60]. Their basic approach was to partition a design into a number of tiles. Each tile was allocated one spare PLBs. In the event a fault in a tile was found, the spare PLB was used to replace the faulty PLB by using a precompiled replacement configuration. Several replacement configurations were stored for each tile. In the event that a fault was detected, the configuration associated with that fault was downloaded. The main drawbacks of this method are static spare allocation and low tolerance, typically limited to one fault per tile. If multiple faults occur in close

proximity (within a tile), this method breaks down. There is no ability to draw spares from other tiles to cover several faults in a single tile.

Fault tolerance in a system relies on spare resources to replace the faulty ones. Spare resources lead to area overhead and degradation in the system performance. In all of the above-mentioned works, spare resources are statically allocated prior to fault occurrence. But static allocation may not provide sufficient resources in an area affected by multiple faults, while resources in areas not affected by faults will be wasted. Efficient spare usage is critical in long-life missions, which must be terminated when one more fault occurs in an area where all spares have been used. The regular structure of FPGAs and their inherent redundancy enable the implementation of low-cost fault-tolerant techniques. Since a typical design uses only a portion of the logic and interconnect resources of the FPGA, the unused resources can provide spares to be used to replace the faulty ones.

On-line testing that occurs concurrently with the normal system operation is essential in high-availability systems that may not be taken off-line for testing, and whose operation should be interrupted as little as possible. In such systems, fault diagnosis and reconfiguration must be accomplished very fast. On-line testing typically relies on modular redundancy and on information redundancy used in coding techniques.

One problem with conventional on-line testing is that it detects only faults that affect the current operation performed in the system. New faults, however, are equally likely to occur in spare resources or in the currently unused portion of the operational part of the system. Thus to guarantee a reliable operation, the on-line test must completely check all the system resources, including spares.

A novel on-line fault-tolerant approach for CLBs of an FPGA is presented in [61]. The approach employs the Self-Testing AReas (STARs) of the FPGA that are off-line and under test, while the rest of the device is on-line, continuing normal system operation. Partial run-time reconfigurations via the boundary scan interface of the FPGA allow the test configuration used by STARs to be downloaded without any impact on the system operation. After testing of a STAR has been completed, the STAR moves to a new location, which is implemented by a sequence of pre-computed partial reconfigurations and assures that the entire FPGA will be eventually tested. If faulty CLB is detected, spare one from a STAR will replace it. Every working CLB has a spare one. The configuration that replaces the working CLB with the spare one is pre-computed.

Most previous methods described in literature are for off-line fault tolerance and used for manufacturing yield improvement. In contrast with them, the proposed approach removes these limitations.

Reconfiguration process in a system is controlled by a module external to the FPGAs (typically this is embedded microprocessor having some storage for the various FPGA configurations). The tasks of this processor are also extended to controlling the test, diagnosis, and fault-tolerance functions, including their associated reconfigurations.

þ

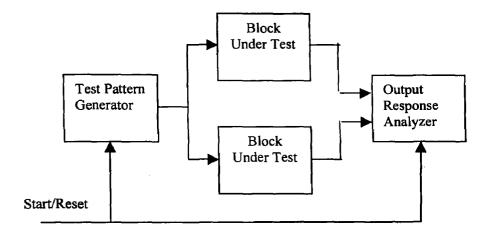

STAR is configured as several disjoint regions with independent BIST structures. Every such structure (Figure 4.3) is composed of a Test Pattern Generator that applies pseudo-exhaustive test patterns to two identically configured programmable logic Blocks Under Test (BUTs), whose outputs are compared by an Output Response Analyzer. The BUTs are repeatedly configured for testing in all their programmable modes of operation.

Once the BUT has been completely tested, the next pair of BUTs is tested in all of their modes of operation.

The cost of the approach is significantly lower than replicated modular redundancy.

Figure 4.4: Testing Programmable Logic Blocks.

An energy of the courty structure and the second second second and the second of the second example in the second uter and the second · .. ·

# CHAPTER 5

# ORGANIZATION OF MULTI-TASK RE-CONFIGURABLE STREAM PROCESSOR WITH SELF-ASSEMBLING MICRO-ARCHITECTURE

In most of industrial data-stream processing systems (e.g. video-surveillance, videorecognition, digital video-broadcasting and digital communication systems, etc.) it is required to process multiple streams of data with very high rate (GB/s). The usual approach is implementation of application specific integration circuits (ASICs) or Field Programmable Gate Array (FPGA) devices were application specific processor core (ASPC) is loaded [62]. This approach seems cost-effective when ASIC or ASPC architecture is designed for one specific application (task).

However, there are several disadvantages associated with this approach. One of the main problems associated with ASICs is lack of hardware flexibility and inability for modification of its micro-architecture if any change of processing algorithm is required or hardware bug is found. Generally, FPGA utilization can mitigate this problem. However, FPGA by its nature requires much more logic resources (configuration SRAM, routing switches, look-up table logic etc.) than ASIC for the same application [63]. On the other hand, in most of real applications multiple streams should be processed in parallel and processing algorithms can vary in different processing modes. ASIC and ASPC approach assumes that all processing architectures for all tasks and their modes should be stored in the ASIC or FPGA in the form of real hardware. However, in most of real applications:

a) Not all tasks are initiated at the same time in the multi-task workload and

b) Only one mode from many can be requested for each task,

Thus, if all application processing architectures are presented in a form of real hardware a lot of logic resources and power will be wasted because of non-active hardware. To solve this problem the concept of run-time re-configurable (RTR) systems can be implemented. RTR approach discussed in Chapter 2, assumes utilization of FPGA devices with partially reconfigurable micro-architecture [63], [64]. This approach allows loading into the FPGA only that processing core, which is needed for the task and task mode going to be activated. However, in the existing RTR computing platforms each processing core has to be developed and pre-compiled using CAD system associated with utilized FPGA family (e.g. ISE Foundation for Xilinx FPGA devices). Instead, in [66] was proposed an approach where Application Specific Virtual Processor (ASVP) can be assembled on-chip by uniformed "LEGO" blocks. These LEGO blocks are cores, which were called Virtual Hardware Components (VHC). Furthermore, this approach assumes that the ASVP assembling procedure is fully automated because it should be performed during hundreds of microseconds without any influence of designer / system operator.

Thus, the process of creation of ASVP micro-architecture is organized as *self-assembling procedure*. Same procedure can be activated when any hardware fault is detected in any of ASVP running in the FPGA. In this case any damaged Virtual Hardware Component can be restored by scrubbing procedure [65] or re-loaded to another available slot of the FPGA. That is why RTR computing platform based on above concept allows creation of a universal computing platform with self-assembling micro-architecture for parallel acquisition, processing and transmitting (via high-bandwidth network) multiple data-streams where each data-stream task can be initiated, terminated and re-loaded without interruption of other data-stream execution and / or data transmission processes.

### 5.1 Organization of Virtual Hardware Components (VHC)

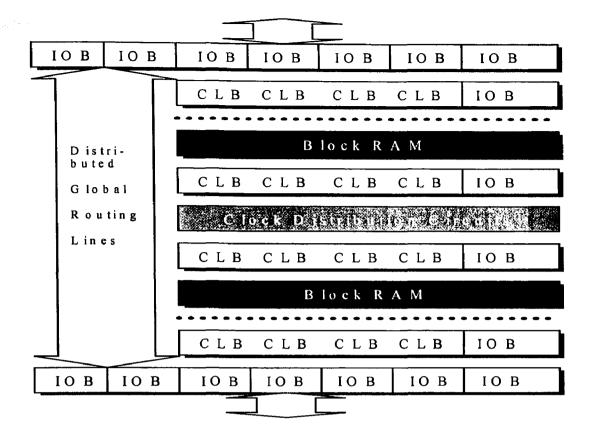

Most of the data-stream processing architectures can be represented as a pipeline reflecting the structure of Data-Flow Graph (DFG) [62]. Considering the structural organization of different FPGA families we found that the best candidate for these requirements was Xilinx "Virtex" family of partially re-configurable FPGA devices [64]. The structure of "Virtex" FPGA consists of (Figure 5.1):

a fizie in

- 1) Arrays of CLBs (Configurable Logic Blocks),

- 2) Arrays of IOBs (Input Output Blocks),

- 3) SRAM memory blocks (*Block RAM*),

- 4) Clock logic resources (DLLs, etc.) and

- 5) Routing resources.

.

These resources can be configured into one or more data-paths for one or more pipelined data-stream processors. The configuration can be done by loading configuration data file into the Configuration SRAM, which programs logic functions of Look-Up-Table (LUT) of each CLB and interconnections between logic, I/O, clock and memory resources. The configuration data file for entire FPGA device can be divided into smaller configuration data files for partial FPGA reconfiguration. Each small configuration data file can represent a Virtual Hardware Component (VHC) to be downloading into addressable FPGA slots (CLB-columns).

Figure 5.1: Structure of partially reconfigurable Xilinx "Virtex" FPGA device

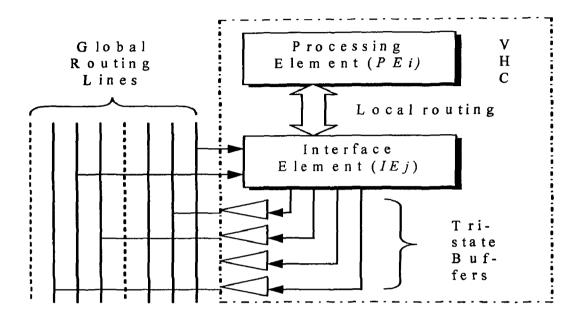

The micro-architecture of VHC consists of two major parts (Figure 5.2):

a) Processing Element (PE): Adder, Multiplier, FFT, etc.

b) Interface Element (IE): 8-bit, 16-bit, 32-bit, etc.

Xilinx "Virtex" FPGA structure allows loading of VHC partially, because partial reconfiguration for this family of FPGAs allows addressable configuration of each frame (part of a CLB-column). As was shown in "Virtex" FPGA device data sheet [63] the special tri-state buffers (T-buffers) can be implemented to connect or disconnect Virtual Hardware Components (VHCs) to the Global Routing Lines. Those T-buffers can be dedicated to specific global routing lines. Thus, each VHC, which contains the Interface Element with T-

buffers associated with specific global routing lines, will be connected to those lines but initially tri-stated at the initial architecture loading state.

Figure 5.2: Micro-architecture of a Virtual Hardware Component (VHC)

## 5.2. Application Specific Virtual Processor assembling procedure

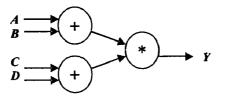

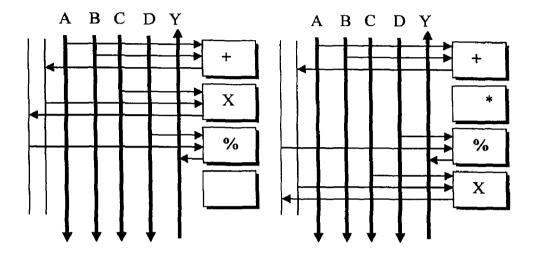

Architectural synthesis of application specific processor normally is based on application (task) algorithm analysis, creation of the Data Flow Graph (DFG), architectural optimization based on DFG and data-path synthesis [66]. As a result, a complete processing architecture described in one of Hardware Description Languages (VHDL, AHDL or Verilog) is usually compiled to be implemented in the ASIC or FPGA. Instead, the approach of *self-assembling* of task optimized Application Specific Virtual Processor (ASVP) inside the partially re-configurable FPGA using pre-compiled sub-cores – VHCs was implemented. This is similar to "Port Map" procedures in Hardware Descriptive Language but in on-chip level. To illustrate this concept let us consider the following example. Let us assume that the task requires to process four streams of data A, B, C and D. These streams should be processed as follows:

$$Y = (A + B) * (C + D)$$

In this case task algorithm can be represented by the Data Flow Graph (DFG) shown in Figure 5.3. To simplify the case, in our example we will not consider scheduling and binding procedures and assume that the DFG should be mapped in hardware "as is".

Figure 5.3: Data Flow Graph of stream processing task

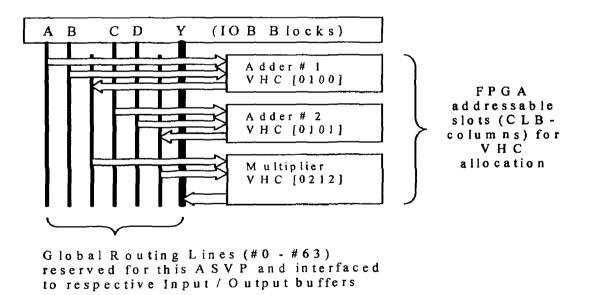

To assemble any micro-architecture by VHCs – we have to have the library of available VHCs. Because Virtual Hardware Components (VHCc) are pre-compiled cores (configuration data files for certain FPGA device), each VHC has to be located in VHC-memory in certain location. The VHC-identifier consists of two parts: Processing Element Type Identifier (PETID) and Interface Element Type Identifier (IETID). Based on this ID-information, the requested VHC can be retrieved from VHC-library and loaded into the FPGA to the selected slot (addressed CLB-column). All above operations such as: getting VHC from the library assigning available FPGA slot for the VHC and loading VHC to the FPGA has to be done by special hardware unit - Hardware Operating System (HOS). HOS structure will be described in the Section 5.3. In our example (Figure 5.3) we need two

adders and one multiplier. Let us assume that 8-bit adder has PETID = 01 and 8-bit multiplier PETID = 02. Let us also assume that Interface Element with two groups of input lines connected to Global Routing Lines (Figure 5.2) with numbers from 0 to 7 and from 8 to 15 and with output tri-state buffers (T-buff) connected to Global Routing Lines (GRL) with numbers from 16 to 23 has IETID= 00. Similar, Interface Element with IETID=01 will have two groups of 8-bit inputs connected to GRL #24 - #39 and output T-buffs connected to GRL #40 - #47. Interface Element with IETID =12 has two groups of input lines connected to GRL #16 - #23 and #40 - 47 and 16 output T-buffs connected to GRL #48 - #63. Thus, VHCs, which should be requested to create Application Specific Virtual Processor for our task will have the following ID:

a) Adder #1: [0100] for (A+B) - operation,

b) Adder #2: [0101] for (B+C) -operation,

c) Multiplier: [0212] for Y calculation.

Other components, which have to be provided for ASVP configuration, are the following:

a) External interface: Input / Output buffers,

b) Internal link routing and

c) Clock routing scheme.

All this components are usually task-specific and should be combined to the fixed part of ASVP architecture. Thus, for task Ti we will have fixed part of ASVP[i] architecture – Afix[i]. Now we can consider complete process of ASVP creation in the partially reconfigurable FPGA. This process consists of the following steps:

1. Hardware Operating System (HOS) receives a request for task activation and loads fixed part of ASVP optimized for this task,

- 2. HOS receives the mode of data processing and retrieves from special table list of VHCidentifiers to be loaded into the FPGA,

- 3. Using ID-Address Conversion Table, HOS generates one after another, addresses of each VHC-configuration data files,

- Each VHC-core HOS stores in the VHC-loading buffer. Then, HOS concatenates the FPGA-slot address to the VHC-core and creates configuration bit-stream for this Virtual Hardware Component,

- 5. Bit-stream of the selected component, HOS loads to the FPGA into selected slot,

6. When all components are loaded, HOS initiates data processing. For our example ASVP architecture is shown in Figure 5.4: Let us assume that mode of task has to be switched from Mode 1: Y = (A+B)\*(C+D) to Mode 2: Y = (A+B)/(C+D)

Figure 5.4: ASVP architecture assembled in the FPGA from pre-compiled VHCs reflecting

task DFG (Figure 5.3)

In our case only Multiplier should be replaced by Divider with the same Interface Element. So, if Divider's PETID = 04 the VHC ID=[0412]. This replacement can be done very fast. In our experiments we measured time for replacement of one CLB-column VHC equal to 140 uS (for Xilinx XCV-400E, 50MHz parallel load). This was 142 times faster than if complete ASVP is replaced by re-configuration of entire FPGA. More detailed these results are discussed in the Chapter 7. We would like to mention that the process of VHC replacement in existing ASVP architecture looks like automated plug-in operation of virtual component in Virtual Bus. Thus, the mode switching in the proposed approach can be done not by switching between existing hardware modules (Multiplier and Divider) but by re-configuring same logic resources (CLB) in short period of time (hundreds of microseconds). This reconfiguration time for many applications is close to switching time. However, reconfiguration allows dramatic minimization of hardware resources and associated cost, dimensions, weight and power consumption. Comparison with regular FPGA-based systems will be discussed in Chapter 7.

. (.

1:

### 5.3 Re-configurable Parallel Stream Processor Architecture organization

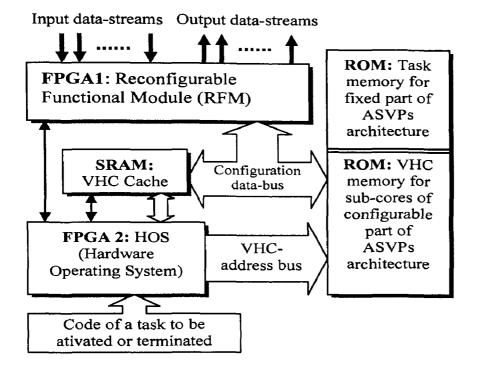

Re-configurable Parallel Stream Processor (RPSP) architecture, adaptable for the multitask and multi-mode workload includes the following major components shown in Figure 5.5

a) <u>Re-configurable Functional Module</u> (RFM) based on partially re-configurable FPGA contains all necessary circuits: power regulators, line buffers, etc. This module is a field of uniform logic resources that can be configured to a number of task-optimized data-stream processors.

b) <u>VHC memory</u> based on ROM (Read Only Memory) contains configuration data files for all available Virtual Hardware Components to be utilized in all modes of all tasks in workload.

Figure 5.5: Architecture of Re-configurable Parallel Stream Processor (RPSP) for multi-task and multi-mode workload

- c) <u>Task memory</u> based on ROM (Read Only Memory) stores the configuration data files of the fixed part of architecture {Afix[i]} for all tasks in the workload.

- d) <u>VHC cache</u> based on SRAM (Static Random Access Memory) stores all VHC cores that can be used for active tasks (loaded in RFM).

- f) <u>Hardware Operating System</u> (HOS) based on FPGA performs the following major functions: i) Task initiation and termination; ii) Mode switching by loading respective set

of VHCs to certain slots of RFM; iii) Data-streams switching and interface control; vi) RFM diagnostic and restoration functions.

The proposed architecture allows significant minimization of hardware resources for processing multi-task workload when each task can work in multiple modes of operation. Our approach is based on the fact that "density" of data processing structure (e.g. application specific processing circuits) is much higher in a form of configuration data files rather than in a form of real hardware logic. It can be "squeezed" even more when configuration data file for an entire Application Specific Processor is assembled from "LEGO"-type component cores (VHC in our terminology) It is possible because of utilization of the same component cores in different ASVP. Thus, the architecture of RPSP contains hierarchy of memory units reflecting above concept:

- i) Non-volatile memory for fixed and re-configurable parts of ASVP's architectures,

- ii) Cache for VHCs to be used for active ASVPs and

- iii) Configuration SRAM in the Functional Module itself.

Let us consider the process of task activation under the HOS control. Firstly, HOS receives the code of the application (task) to be activated (Figure 5.5). Task code = ASVP code which contains of:

i) Code of fixed part of ASVP architecture,