# NOTE TO USERS

This reproduction is the best copy available.

# HARDWARE SOFTWARE CO-SYNTHESIS OF HETEROGENEOUS HYPERCUBE ARCHITECTURES FOR FAULT TOLERANT EMBEDDED SYSTEMS

by

Jacob Levman, BASc, Toronto, September 17th 2004

#### A thesis

presented to Ryerson University

in partial fulfillment of the

requirement for the degree of

Master of Applied Science

in the program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2004

© Jacob Levman 2004

UMI Number: EC52963

## INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform EC52963 Copyright 2008 by ProQuest LLC.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 E. Eisenhower Parkway PO Box 1346 Ann Arbor, MI 48106-1346 Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

# Hardware Software Co-Synthesis of Heterogeneous Hypercube Architectures for Fault Tolerant Embedded Systems

Jacob Levman,

Masters of Applied Science, 2004,

Electrical and Computer Engineering,

Ryerson University

#### Abstract

The hardware-software co-synthesis of an embedded system's architecture involves the partitioning of a system specification into hardware and software modules so as to meet various non-functional requirements. A designer can specify many non-functional requirements including cost, performance, reliability etc. In this thesis, we present an approach to the hardware-software co-synthesis of embedded systems targeting hypercube topologies. Hypercube topologies provide a flexible and reliable architecture for an embedded device with multiple processing elements. To the best of our knowledge, this is the first time that hypercube topologies have been supported in a co-synthesis algorithm. The co-synthesis approach presented here supports the following features: 1) input in the form of an acyclic periodic task graph with real-time constraints, 2) the pipelining of task graphs, 3) the use of a heterogeneous set of processing elements, 4) Support for fault tolerance through our newly developed group based fault tolerance technique. The co-synthesis algorithm has been applied to two case studies to demonstrate its efficacy.

## Acknowledgements

The author would like to thank his two supervising professors. Dr. Gul Khan and Dr. Javad Alirezaie, for providing their guidance, knowledge and support. The author would also like to thank the members of the review committee for their participation. The author would like to thank the National Science and Engineering Research Council of Canada (NSERC) for providing funding support for this research project in the form of multiple grants to my supervising professors. The author would like to thank Ontario Graduate Scholarships (OGS) for funding this research through a scholarship. The author would also like to thank Canadian Microelectronics Corporation (CMC) for providing the ARM rapid prototyping platform that was used in the case studies of this thesis.

## Dedication

I would like to dedicate this thesis to my wife whose drive to accomplish is inspiring. Without her love and support I would not be where I am today.

## Table of Contents

| 1. INTRODUCTION                                   | 1  |

|---------------------------------------------------|----|

| 1.1 Overview                                      | 1  |

| 1.2 Original Contributions                        | 3  |

| 1.3 Thesis Organization                           | 4  |

| 2. DESIGN OF EMBEDDED SYSTEMS                     | 6  |

| 2.1 Introduction to Hardware-Software Co-Design   | 6  |

| 2.2 Hardware-Software Partitioning                | 16 |

| 2.2.1 Standard Approach                           | 17 |

| 2.2.2 Partitioning Granularity                    | 18 |

| 2.2.3 Dynamic Programming                         | 21 |

| 2.2.4 Fault Tolerance                             | 22 |

| 2.3 Hardware-Software Co-Synthesis                | 25 |

| 2.4 Hypercube Architectures                       | 28 |

| 3. CO-SYNTHESIS FOR HYPERCUBE SYSTEMS             | 33 |

| 3.1 Introduction                                  | 33 |

| 3.2 Fault Tolerance at the Task Graph Level       | 38 |

| 3.2.1 Overview                                    | 38 |

| 3.2.2 Task Based Fault Tolerance                  | 39 |

| 3.2.3 Cluster Based Fault Tolerance               | 40 |

| 3.2.4 Group Based Fault Tolerance                 | 44 |

| 3.2.5 Task Graph Based Fault Tolerance Comparison | 49 |

| 3.3 Pipelined Scheduler                           | 51 |

| 3.4 Device Expansion                              | 57 |

| 3.5 Communication Link Integration                | 62 |

| 4. IMPLEMENTATION AND EXPERIMENTAL RESULTS        | 68 |

| 4.1 Parallel MPEG-2 Decoding                      | 68 |

| 4.2 Parallel Block Matching                | 75  |

|--------------------------------------------|-----|

| 4.3 Discussion of Experimental Results     | 93  |

| 5. CONCLUSIONS AND FUTURE WORK             | 98  |

| REFERENCES                                 | 10  |

| Appendix A – Prototype Device Code Listing | 103 |

## List of Tables

| Table 3.1: Fault Tolerance Comparison Data                                   | 30 |

|------------------------------------------------------------------------------|----|

| Table 4.1: Processing Element Utilization of Design Space for MPEG Decoding  | 72 |

| Table 4.2: Processing Element Utilization of Design Space for Block Matching | 86 |

| Table 4.3: Generated Motion Vectors                                          | 92 |

# List of Figures

| Figure 2.1: Traditional Design                                                 | 8  |

|--------------------------------------------------------------------------------|----|

| Figure 2.2: Hardware-Software Co-Design                                        | 10 |

| Figure 2.3: Hardware-Software Co-Synthesis                                     | 12 |

| Figure 2.4: A 4D Hypercube                                                     | 29 |

| Figure 2.5: Example Hypercube Architecture                                     | 32 |

| Figure 2.6: Example Hierarchical Architecture                                  | 32 |

| Figure 3.1: Hypercube Co-Synthesis Algorithm Flow                              | 37 |

| Figure 3.2: Task Based Fault Tolerance Example                                 | 40 |

| Figure 3.3: Cluster Based Fault Tolerance - Input & 1 Iteration                | 42 |

| Figure 3.4: Cluster Based Fault Tolerance – 2 & 3 Iterations                   | 43 |

| Figure 3.5: Cluster Based Fault Tolerance – Final Clustering                   | 43 |

| Figure 3.6: Final Added Assertion Tasks After Clustering                       | 44 |

| Figure 3.7: Group Based Fault Tolerance - Input & 1 Iteration                  | 47 |

| Figure 3.8: Group Based Fault Tolerance – 2 & 3 Iterations                     | 47 |

| Figure 3.9: Group Based Fault Tolerance – Final Grouping                       | 48 |

| Figure 3.10: Final Added Assertion Tasks After Grouping                        | 48 |

| Figure 3.11: Randomly Generated Task Graph (Graph #1)                          | 51 |

| Figure 3.12: Hypercube Co-Synthesis Scheduler                                  | 54 |

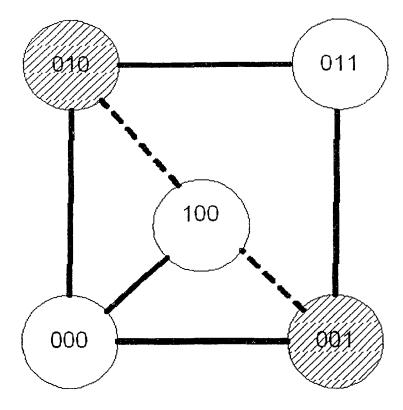

| Figure 3.13: Binary Naming for Hypercube Nodes                                 | 63 |

| Figure 3.14: Non-Symmetrical 3-D Hypercube                                     | 66 |

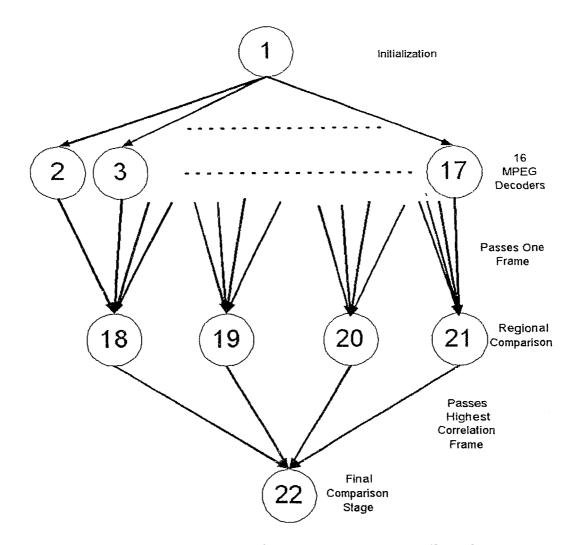

| Figure 4.1: Parallel MPEG Decoding: Functional Task Graph                      | 69 |

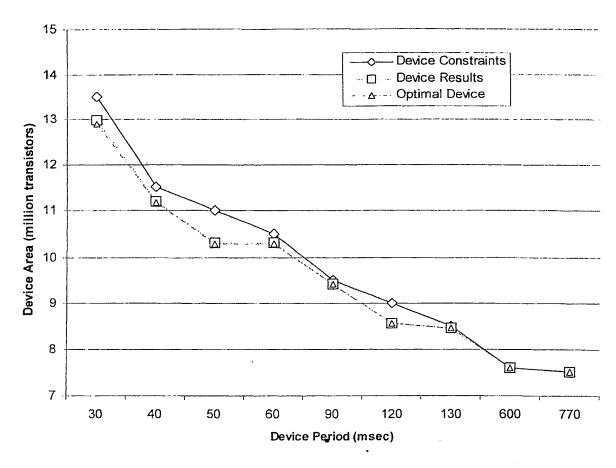

| Figure 4.2: Design Space Exploration of Parallel MPEG Decoding                 | 71 |

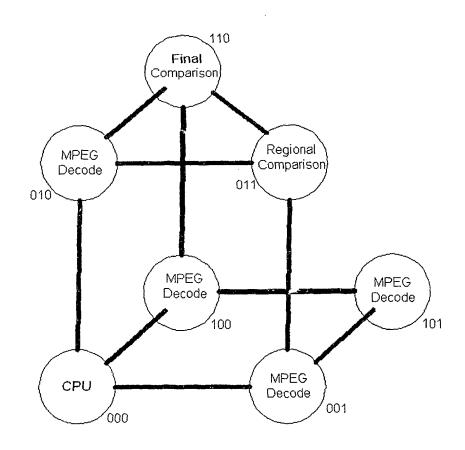

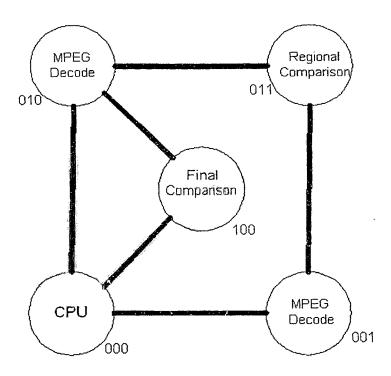

| Figure 4.3: Parallel MPEG Decoding: Architecture for 1 <sup>st</sup> Test Case | 73 |

| Figure 4.4: Parallel MPEG Decoding: Architecture for 2 <sup>nd</sup> Test Case | 74 |

| Figure 4.5: Parallel MPEG Decoding: Architecture for 5 <sup>th</sup> Test Case | 75 |

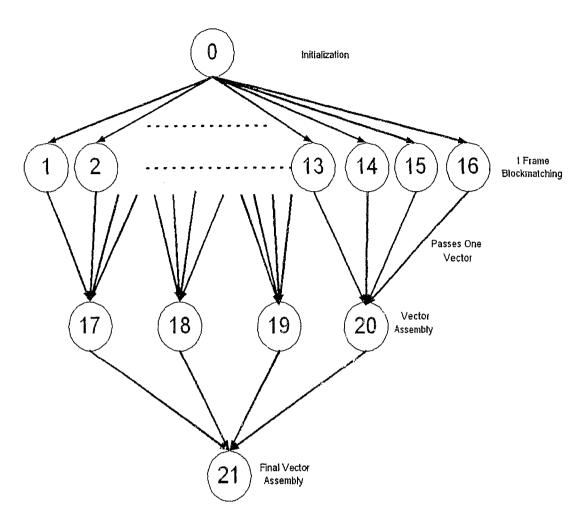

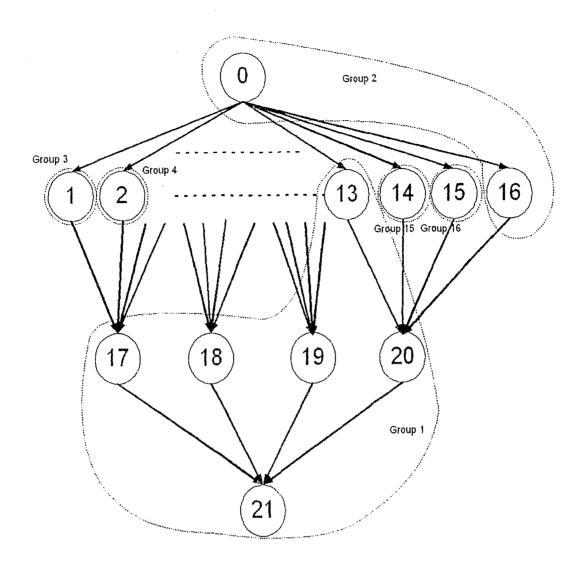

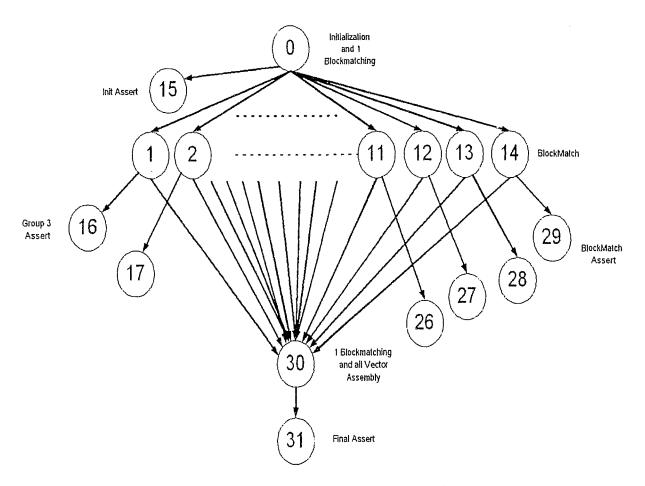

| Figure 4.6: Block Matching: Functional Task Graph                              | 77 |

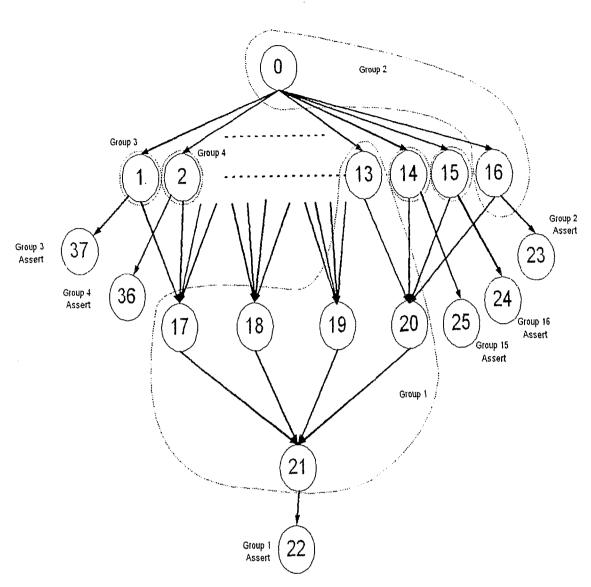

| Figure 4.7: Block Matching Task Graph: GBFT Grouping                           | 78 |

| Figure 4.8: Block Matching Task Graph with Added Assertion Tasks               | 79 |

| Figure: 4.9: Block Matching: Final Resultant Task Granh                        | 80 |

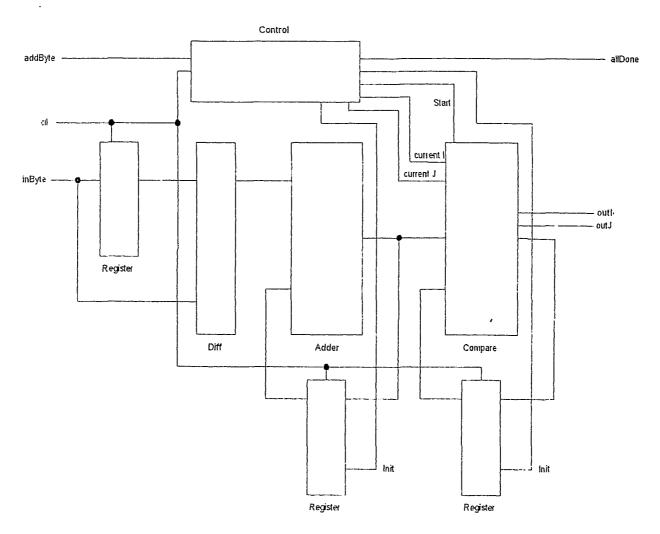

| Figure 4.10: Block Match Circuit Design                          | 81 |

|------------------------------------------------------------------|----|

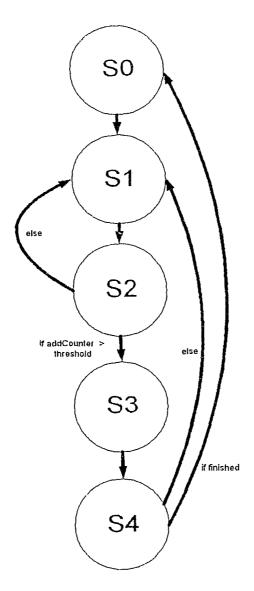

| Figure 4.11: Block Match State Machine                           | 83 |

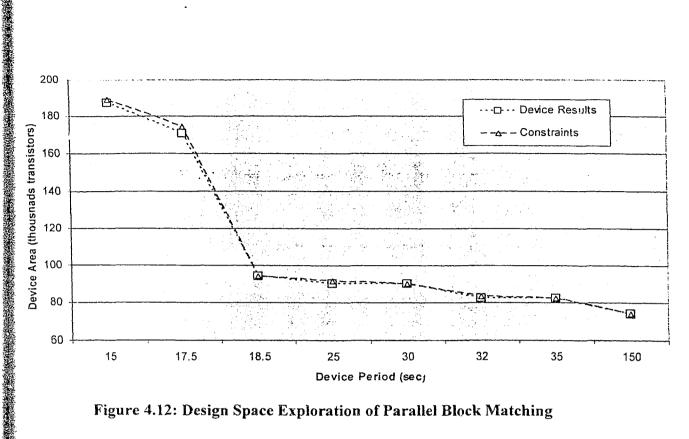

| Figure 4.12: Design Space Exploration of Parallel Block Matching | 85 |

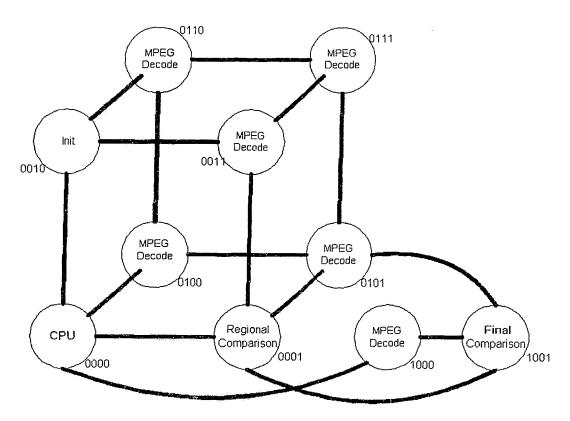

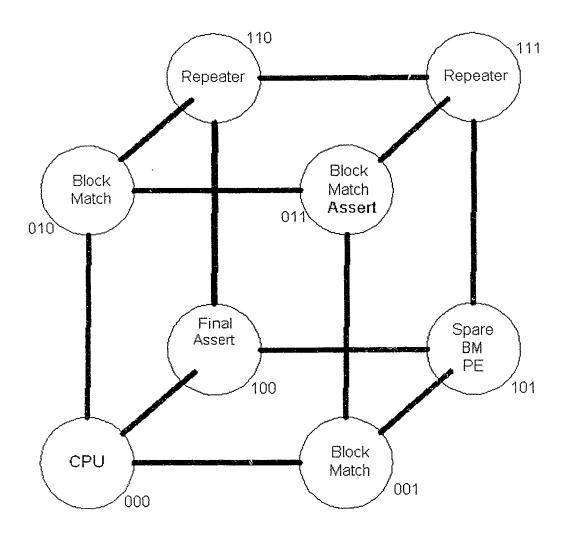

| Figure 4.13: Final Prototype Device Architecture                 | 89 |

| Figure 4.14: Reference Image                                     | 90 |

| Figure 4.15: Input Image                                         | 91 |

| Figure 4.16: Macroblock Identification                           | 91 |

## Glossary of Acronyms

CAD - Computer Aided Design

GBFT - Group Based Fault Tolerance

CBFT - Cluster Based Fault Tolerance

TBFT - Task Based Fault Tolerance

CPU - Central Processing Unit

ASIC - Application Specific Integrated Circuit

FPGA – Field Programmable Gate Array

MPEG - Motion Picture Experts Group

PE – Processing Element

IP - Intellectual Property

SW - Software

HW - Hardware

VHDL – Very high speed integrated circuit Hardware Description Language

## CHAPTER 1

## INTRODUCTION

### 1.1 Overview

The average Canadian equates the idea of a computer with a desktop or laptop. In actuality, the definition of a computer is much broader. It is estimated that in the average Canadian's home there are 30 to 40 embedded systems. Television, audio systems, refrigerators, telephones, temperature controls and stoves all use embedded computers. Embedded computers also play an integral role in many of the assisted devices that aid disabled individuals in performing daily activities, e.g. power wheelchairs and communication devices. Additionally, many embedded devices are responsible for protecting human life; embedded computers control modern medical instrumentation, airplanes, air traffic control systems, anti-lock breaking systems (ABS) and even the "fasten your seatbelt" light on the dashboard of your car. By many estimates, embedded devices account for 99% of worldwide computers while desktops and laptops account for just 1%. Embedded computers are small-scale application-specific computing devices. Embedded computers already permeate our society and their growth is expected to continue indefinitely.

It is common knowledge that technological developments are producing increasingly efficient and compact computers. This applies to embedded computers as well. The

more powerful and complicated the components of an embedded device, the more difficult it is for a computer engineer to produce a product that meets safety, performance, cost and power consumption requirements within a reasonable amount of time. The production of the high performance embedded devices of the future will require tools and formal methods to aid engineers in system design and development.

The research presented in this thesis is centred around the development of computer aided design (CAD) software tools that will be used to aid in the design and development of future embedded devices. Essentially, an engineer will tell the CAD tool what the desired device should be capable of doing; the tool will analyze the given information and recommend a reliable and efficient design. This can aid a product engineer in developing systems that are far more reliable, cost, time and power efficient. Reliability is key for the development of safety-oriented devices that are responsible for protecting human life. Minimal production cost is important for ensuring the final products are accessible to all people regardless of socio-economic status. Similarly, decreased labour costs as a result of more expedient design, results in a cheaper product. Finally, minimizing a device's power consumption is essential to reducing energy costs, both financial and environmental. These CAD tools will aid in the development of new devices that will continue to play a central role in our lives.

Within electrical and computer engineering, embedded systems research is in its infancy. This makes it an exciting field to work in as it provides unique and novel

opportunities. It is also attractive due to its broad range of applications (aerospace, automotive, communications etc.). Developing these software tools can be technically challenging and thus intellectually rewarding.

## 1.2 Original Contributions

This thesis presents a new hardware-software co-synthesis tool to aid in the design and development of high performance embedded devices. The proposed approach focuses primarily on computationally intensive computing systems requiring high levels of fault tolerance. A full hardware-software co-synthesis approach is presented with comparisons to a fully exhaustive technique. Implementation results are also provided in order to further demonstrate the algorithm's efficacy.

The major contributions of this thesis are as follows:

- Development of a hardware-software co-synthesis algorithm capable of generating hypercube architecture based embedded devices

- Development of group based fault tolerance (GBFT), a technique designed to efficiently add support for fault tolerance in embedded systems at the task graph level

- Comparative analysis between the newly developed GBFT algorithm and other existing methods

- Comparative analysis between the co-synthesis algorithm presented here and

the optimal case

- Implementation of a security/navigation device in simulation in order to demonstrate the efficacy of the co-synthesis algorithm

- Implementation of a parallel block matching device in order to demonstrate the efficacy of the co-synthesis algorithm

- Prototype construction of the block matching case study

## 1.3 Thesis Organization

This thesis consists of five chapters. The second chapter encompasses a survey of hardware-software co-design, and a thorough survey of hardware-software partitioning and co-synthesis. Chapter 2 also includes background on hypercube architectures. These two chapters are intended to provide the basic understanding of the design issues of hardware-software embedded systems and to survey the existing research in this field.

The third chapter is the main component of this thesis. It consists of a full description of all of the components of the co-synthesis algorithm. These include group based fault tolerance, a pipelined scheduling technique, a method for adding processing elements to the current system design, placing existing processing elements within a hypercube topology and synthesizing all required communication links.

The fourth chapter describes the two case studies implemented in order to demonstrate the algorithm's efficacy. The first case study performs the decoding of parallel MPEG-2 video streams and compares the algorithm's results with that of an exhaustive technique. The second case study performs parallel block matching and a final prototype device is constructed. The fourth chapter also includes a discussion of the experimental results obtained from both of the case studies. The fifth chapter concludes this thesis.

## CHAPTER 2

## DESIGN OF EMBEDDED SYSTEMS

## 2.1 Introduction to Hardware-Software Co-Design

This section surveys hardware software co-design. Hardware-software co-design is an active area of research that involves the development of tools and methodologies to aid in the design of embedded computer systems. Embedded computers are processing devices used in areas as diverse as wireless communications, medical instrumentation, transportation and food preparation. Although these fields are widely different, the embedded device components of the products share common design techniques. This is an outline of hardware-software co-design: a method for designing and developing an embedded computer device. The motivation behind co-design is that both hardware and software components should be addressed simultaneously in order to ensure that the final device meets cost, performance, reliability and power consumption goals.

Separate software and hardware design methods have been the subject of a great deal of research over the years [21, 41]. However, the design of both hardware and software as a joint venture remains an area of rapidly growing research. Most of the embedded systems research has been stimulated by the development of fairly inexpensive high performance microprocessors [8]. When embedded processors were

exclusively small and responsible for the execution of minimal amounts of software, simple techniques were more than sufficient to create devices that satisfied performance and functional goals within a reasonable time to market. With the number of transistors on a chip increasing exponentially, embedded devices have the potential to utilize far more sophisticated circuits and architectures [48]. The embedded engineer requires CAD tools to aid in the design and development of embedded computers and to predict implementation costs.

The rest of the subsection introduces the motivation behind hardware-software codesign of embedded systems. Additionally, it intends to introduce the various components of the hardware-software co-design process.

## **Co-Design Overview**

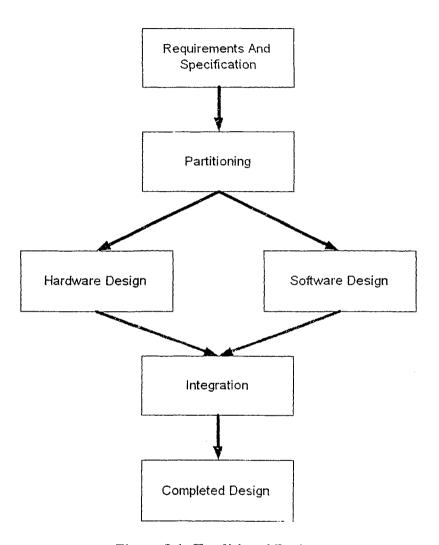

The embedded system design process will vary considerably with respect to the type of product under development. However, commonalities can be identified and the ability to abstract hardware and software components to the same level is greatly exploited in hardware-software co-design. The traditional approach to the design of an embedded computer system is to enforce hardware-software partitioning at an early stage. This results in well-defined design tracks for both the hardware and software components. The major weakness in traditional embedded systems design

lies in the early partitioning process. A graphical overview of the traditional design approach is provided in Figure 2.1 below.

Figure 2.1: Traditional Design

One of the major flaws of such an approach is the inability of the design and development flow to correct mistakes made in the partitioning phase. If during integration, an embedded systems engineer discovers that the product will not meet

various non-functional requirements (performance, power consumption, etc.), the cost imposed on re-evaluation of the design will be extremely high.

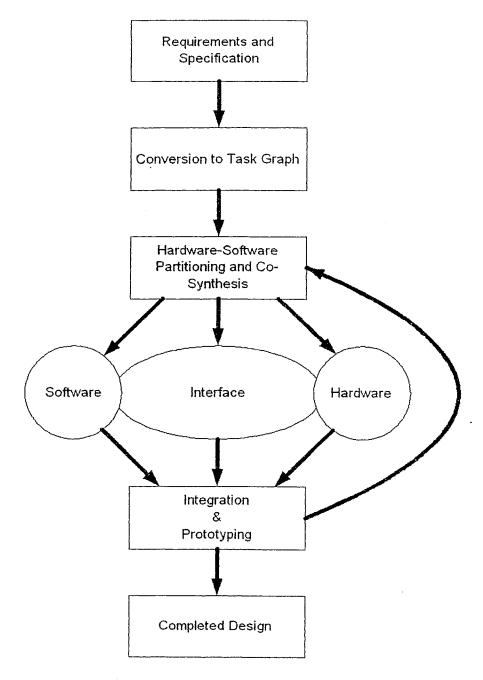

The hardware-software co-design process begins with the creation of device requirements, which leads to a formal specification. Both functional and non-functional requirements such as performance, cost and power consumption are specified. This can then be converted into a standardized system description or specification. Embedded system specification requires detailed models to aid in the abstract description of component functionality. Abstract modeling that does not differentiate between hardware and software is known as co-specification. Further research into the high level modeling of embedded devices would be greatly beneficial.

It is common for this standardized description to be converted into a task graph format. Hardware-software partitioning is performed on this task graph. Partitioning is concerned with assigning an execution location (software or hardware) to each task. After partitioning, co-synthesis is performed and typically, the co-synthesis and partitioning phases are closely knit. Co-synthesis is broken down into the assignment, allocation and scheduling phases. Finally, the generated software, hardware and interface modules are integrated. Feedback in the design process can occur at system integration by returning to the partitioning phase, thus allowing the designer to refine the given solution. At integration, the overall system can be evaluated for functional and non-functional requirements by using hardware software

co-simulation. Co-simulation allows for both hardware and software components to be tested congruently. A visual overview of the co-design process is provided in Figure 2.2.

Figure 2.2: Hardware-Software Co-Design

## **HW/SW Partitioning**

The partitioning process is concerned with deciding what system functionality will be implemented as hardware and what will be implemented as software. Typically, an embedded device will need to meet a number of non-functional requirements. These would often include performance, price, reliability and power consumption. With more components implemented in hardware, system price and power consumption will increase. However, with a large number of components implemented in software, system performance and reliability can degrade. It is important to balance the selection of hardware and software components to ensure that all system requirements are met. Significant research has been conducted with respect to partitioning algorithms in order to automate the process of obtaining an efficient hardware-software layout for an embedded device.

## **HW/SW Co-Synthesis**

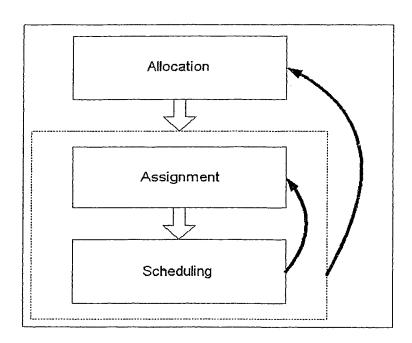

Hardware-software co-synthesis of an embedded device is the process by which the hardware-software architecture of the system is automatically derived to satisfy multiple goals. These goals can include factors such as cost, performance and power consumption. Hardware-software co-synthesis is inseparable from the process of

partitioning. The hardware-software co-synthesis design flow consists of three main components: allocation, assignment and scheduling. Allocation is concerned with selecting the number and type of communication links and processing elements in the system. The assignment component is concerned with the mapping of tasks to processing elements. The scheduling component is concerned with the timing of task execution and communications. Typically, the partitioner will iteratively adapt its hardware mappings based largely on the results of the scheduler. The scheduler is typically the final phase of co-synthesis. A visual overview of a common approach to co-synthesis is provided in Figure 2.3.

Figure 2.3: HW/SW Co-Synthesis

#### HW/SW Co-Simulation

High performance embedded system components can be extremely complex. It is difficult to develop comprehensive analytic systems to model the performance of an embedded device that consists of complicated components. Concurrently simulating components with differing behavioural models is referred to as co-simulation. Typically, a co-simulation environment will model multiple components, both software and hardware. This can be a difficult task as software simulation consists of modeling a processor executing a series of instructions. However, hardware simulation can consist of modeling something completely different, such as an analog or digital circuit. In an embedded device it is common for the execution of application specific integrated circuits to depend on commands issued by one of the system's processors. One should note that co-simulation requires the hardware simulator to react to input from the software simulator and vice versa.

A number of co-simulation tools have been developed. One of the most well-known co-simulation tools is Seamless from Mentor Graphics. Seamless allows the user to tie in various hardware and software simulators. Seamless coordinates the communications between simulators to ensure that the overall behaviour reflects that of an embedded device. Although Seamless performs as an effective co-simulation tool, it can also be applied for hardware-software co-verification [44].

### **HW/SW Co-Verification**

The complexity of embedded systems prevents the designer from relying on traditional validation techniques such as simulation and testing. These techniques are insufficient to properly verify the correctness of such a system. To address this problem, new formal verification methods are needed to overcome the limitations of traditional validation techniques.

Multiple methods have been developed for performing hardware-software coverification. A common approach involves the use of a Petri-net based representation of embedded systems, as in the system named PRES [9, 10]. The PRES model proves the correctness of an embedded system by determining the truth of computation tree logic and timed computation tree logic. These research projects make use of model checking to prove the correctness of embedded systems and have used an automatic teller machine server to demonstrate the feasibility of their approach. Another approach developed by Hsiung involves the use of linear hybrid automata and employs a simplification strategy to address the state-space explosion that occurs in the formal verification of complex systems [26].

Presently, our knowledge of the joint hardware-software design process is far more limited than that of either of the two separately. While embedded systems development can be performed as separate processes of hardware and software

design, this route can be far more challenging when attempting to meet various price and performance recomments. Additionally, this design path has a tendency to result in more error prone and outside to difficulties in embedded system verification.

Research into system modeling is a key element to our understanding of hardware-software co-design. While many abstract models for embedded system components exist, there is a lack of accurate models to address the detailed characteristics of these components. Embedded systems are always being developed with various performance and cost metrics in mind. In order to properly meet those requirements, it is essential to develop a thorough understanding of modeling that includes both the intricacies of a component as well as its high level properties.

In the current embedded systems market, designers and developers can mostly produce devices that meet requirements within a reasonable amount of time. However, soon the utilization of sophisticated hardware-software co-design techniques will be required in order to meet future device demands. As advanced processors and ASICs become less expensive, the need for tools to aid the design and development process will increase dramatically in order to ensure the development of high quality devices with a minimum time to market.

## 2.2 Hardware-Software Partitioning

Hardware-software partitioning is the process by which the various components of an embedded computer's functionality are placed in either hardware or software. The motivation behind the partitioning process is to produce a reliable embedded device that meets performance, cost and power consumption requirements.

The partitioning process is a subset of hardware-software co-design. Computer components suitable for use in embedded devices have increased in ability and complexity dramatically in recent years. The job of an embedded systems engineer involves selecting appropriate components and integrating them to produce an embedded device. The rapid increase in both complexity and performance of these components has resulted in an increase in the difficulty of component selection and integration. These difficulties have fuelled demand for tools and design methodologies to aid in the creation of embedded devices that are comprised of both hardware and software components.

The typical embedded system design approach is significantly restrictive. The main flaw revolves around the lack of design flow after system integration and prototyping. If the system is integrated and an expensive prototype is produced, further design changes can be extremely costly. These further design changes may have to occur if prototyping reveals that the system will not meet non-functional requirements (such as performance).

This subsection's goal is to introduce the reader to the motivation behind hardware-software partitioning for embedded devices. Additionally, this subsection intends to introduce the reader to the existing research in hardware-software partitioning.

### 2.2.1 Standard Approach

The partitioning process is concerned with deciding which system functionality will be implemented as hardware and which will be implemented as software. It is important to balance the selection of hardware and software components to ensure that all system requirements are met. Significant research has been conducted with respect to partitioning algorithms in order to automate the process of obtaining an efficient hardware-software layout for an embedded device.

The standard approach to hardware-software partitioning involves the use of a heuristic to prioritize a task set. This prioritization aids in the determination of task mapping (to hardware or software). Often much of the job of the partitioning algorithm researcher is simply to develop an effective heuristic that will result in an optimal partitioning algorithm.

The earliest partitioning algorithms proposed, began by implementing all components in software and proceeded to move components to hardware implementations until various system requirements were optimized [18]. Other early approaches proposed to implement all components in hardware and to proceed to move components to software until system requirements were met [22]. A more recent approach involves making an educated guess with reference to whether a given task should first be mapped to software or to hardware [6]. Afterwards, the algorithm would iteratively attempt re-mapping tasks from their original locations until requirements are satisfied. These techniques and versions thereof are still in use. In all cases the approach is similar, the algorithm attempts a default or initial configuration, analyzes its effectiveness and iteratively alters the current layout if non-functional requirements are not met. Other techniques to aid in the heuristics for partitioning decisions include linear integer programming [38], simulated annealing [40] and petri-nets [19].

第一個人工工作、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代、1995年代

### 2.2.2 Partitioning Granularity

Granularity defines the size of system components that can be implemented in either hardware or software. A partitioning algorithm that operates at a high level of granularity (also referred to as coarse-grained) uses only large blocks of system functionality to be implemented on any given processing element (PE). It can be beneficial for a large segment of functionality to be implemented on the same PE. This is particularly evident in larger scale distributed embedded devices, where

dividing a high grained system into smaller components and then mapping them across the system can yield an unnecessarily high communication overhead. This occurs when tightly coupled components are "spread out" throughout the system. Using the granularity that is specified by the programmer of an application is often referred to as a high level of granularity. Gupta and DeMicheli developed an approach to the coarse grained hardware-software partitioning problem [23]. They present a partitioning procedure to identify potential hardware and software components of a system. Their technique also utilizes the Olympus Synthesis System for digital design [39] for the synthesis of dedicated hardware within their system. Yen and Wolf have also developed an approach to the coarse grained partitioning problem [52]. They present an automatic iterative improvement technique for simultaneously performing concurrency optimization and hardware-software tradeoffs. By considering both concurrency and hardware-software tradeoffs, their approach is able to identify cost/performance points that may not have been identified otherwise.

A partitioning algorithm that operates at a low level of granularity (also referred to as fine-grained) will often divide an embedded system's functionality into extremely small components. Fine-grained partitioning algorithms have the disadvantage that separating system functionality on such a small scale can dramatically increase communication overheads, which has the effect of decreasing system performance. Some systems use this approach when they are dealing with partially re-configurable processors (processors whose IP cores can be modified during the design process).

Fine-grained systems can provide a better solution than coarse-grained algorithms because they are more flexible in terms of mapping the correct computationally intensive components to the appropriate processing elements. Fine-grained systems reduce the potential negative effect of having to deal with a poorly defined system functional specification. A fine-grained system can refine the design on such a small scale that some will take one single computationally intensive CPU instruction and treat it as a separate task [1]. It is common for tasks (individual components that can be mapped to hardware) to be called base blocks when dealing with fine grained partitioning. Ernst et al. have developed a heuristic approach to the fine grained hardware-software partitioning problem [18]. They have developed an iterative partitioning process which is based on hardware extraction and is controlled by a cost function. This technique is in use in the COSYMA system [40]. Knudsen and Madsen have also presented an approach to the fine grained partitioning problem [30]. This approach uses dynamic programming to solve both the problems of system execution time and hardware area constraints. This technique is in use in the LYCOS system [38].

Finally, there is one research project known that involves merging these two ideas of varying granularity [24]. This concept is known as flexible granularity. Depending on the characteristics of the specific application and the system's non-functional requirements, the selected granularity can span from a low level of base blocks all the way to the user-defined functions. This approach is intended to overcome the shortcomings of both of the previous approaches. This work also includes estimation

methodologies adapted to different levels of granularity, which help to determine the final system granularity.

## 2.2.3 Dynamic Programming

Dynamic programming is a technique ideal for problems where calculating all possible outcomes is not computationally feasible. This makes dynamic programming well suited to the partitioning problem, which can be extremely computationally intensive. Typically, a dynamic solution is recursive and iterative in nature.

Dynamic programming problems can always be divided into stages where a decision will be required at each stage. Typically there are a number of states associated with each stage. Decisions made at one stage will alter the current state into a new state in the next stage. The decision made at a given state does not depend on the decisions made in the previous state. It can be seen that dynamic programming extends itself easily to hardware-software partitioning which can be approached as a recursive, iterative, state based problem. Often a dynamic programming solution will effectively process a task graph and improve algorithm execution speed by avoiding testing infeasible combinations.

Shrivastava et al. [45] have used dynamic programming to develop an algorithm that can effectively solve the partitioning problem with extremely fast execution times. Chang and Pedram [5] have also used dynamic programming to determine the solution to the coarse-grained partitioning problem of a generic task graph. Knudsen and Madsen [31] have used dynamic programming to determine the solution to the fine-grained partitioning problem.

### 2.2.4 Fault Tolerance

Fault tolerance is a large area of computing, whereby computational devices are developed which must meet various mission critical and safety critical requirements. These types of systems are common in aerospace and biomedical applications. Fault tolerant computing has been a large area of study [46], however, incorporating some of these ideas into hardware-software partitioning is an extremely young discipline.

東京である。まである。これでは、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前には、19年前に

It is common in the development of fault tolerant devices to incorporate a system's fault tolerant components late in the design process. This often creates a significant overhead in terms of implementation cost. Incorporating fault tolerance at an earlier stage of design is likely to be very beneficial in reducing this overhead. This line of reasoning has sparked research in incorporating fault tolerance into earlier phases in the design process, such as hardware-software partitioning.

Fault tolerant hardware-software partitioning generally involves adapting the partitioning process to automatically accommodate systems requiring fault tolerance. The most predominant work in this field is that of Dave and Jha [13]. These researchers have developed a system that will input a functional task graph specification and perform task clustering for fault tolerance. Their system will choose an error recovery topology that is optimized to use a small number of extra processing elements. Additionally, Bolchini et al. [4] have developed a partitioning algorithm that incorporates fault detection capabilities. This may not be as robust as full fault tolerance, however fault detection is relevant as it is a subset of fault tolerance.

Presently, our knowledge of the joint hardware-software design process is far more limited than that of either of the two separately. While embedded system development can be performed as a separate process of hardware and software design, this route can be far more challenging when attempting to meet various price and performance requirements. Additionally, this design path has a tendency to result in more error prone products due to a lack of formalism in design methods.

Hardware-software co-design is a burgeoning field of research and one of its most active subsets is hardware-software partitioning. Partitioning is the process of deciding what functional system components will be implemented as hardware and what will be implemented as software. Effective hardware-software partitioning is

essential for creating embedded devices that meet non-functional requirements such as performance, power consumption and cost.

Since hardware-software partitioning has begun to flourish as a field of research, greatly varying approaches to the problem have been taken. Researchers have attempted to tackle many issues and incorporate many varying ideas. The concept of varying degrees of granularity allows an algorithm to separate a system's functionality into components of various size. Dynamic programming is an iterative, recursive technique that has been effectively incorporated into approaches to partitioning. Fault tolerance is an extremely important issue, especially in embedded systems, and partitioning approaches have been developed to incorporate these abilities.

In the current embedded systems market, designers and developers can mostly produce devices that meet requirements within a reasonable amount of time. However, soon the utilization of sophisticated hardware-software co-design techniques will be required in order to meet future device demands. As advanced processors and ASICs become less expensive, the need for tools to aid the design and development process will increase dramatically in order to ensure the development of high quality devices with a minimum time to market. Hardware-software partitioning will be an integral component of these tools.

### 2.3 Hardware-Software Co-Synthesis

An embedded system's architecture is typically determined by the intuition of a design engineer. This process adds time to the development cycle and sometimes results in architectures that do not meet non-functional requirements. It can also result in an over-designed architecture with excessive hardware that results in overly expensive devices. Consequently, incorporating hardware-software co-synthesis in design automation tools is essential for producing optimal devices with an accelerated The hardware-software co-synthesis problem is concerned with determining optimal hardware and software architectures. This involves the selection of processors (CPUs), application specific integrated circuits (ASICs) and communication links in order to produce a device that meets non-functional requirements. The co-synthesis problem typically involves the selection of the quantity and type of processing elements and communication links (allocation), task assignment from a task graph to processing elements and confirmation of whether the system meets requirements (usually through scheduling). A task graph is a collection of tasks and communication dependencies that describe device functionality. The allocation and scheduling phases are known to be NP-complete [20, 33], thus determining an optimal solution in the co-synthesis phase can be extremely computationally intensive.

This work is motivated by the need to automate the embedded system design process while simultaneously producing high quality devices. The research presented in this

thesis is further aimed at producing high performance fault tolerant embedded systems. Embedded applications that would particularly benefit from high levels of fault tolerance include aerospace, medical instruments and high performance telecommunication systems. In fact, it is believed that within the next two or three decades probes will be sent to orbit nearby stars [34]. Such embedded devices would be responsible for considerable system control and measurement instrumentation in addition to unparalleled fault tolerance requirements.

The primary focus of most of the co-synthesis research problem has concentrated on the simplistic single processor and ASIC architecture [3, 6, 18, 28]. Some approaches assume more complicated architectures, such as two CPUs and hardware-accelerated circuitry [37]. Various approaches have been attempted that involve moving tasks from hardware to software or vice versa in order to meet the system requirements. In the co-synthesis of distributed systems, target architectures can incorporate multiple processors, ASICs or FPGAs (field programmable gate arrays). Two main techniques have been utilized to handle the co-synthesis of distributed systems: the optimal and heuristic approaches.

The optimal approach can be divided into three sections: exhaustive, mixed integer linear programming, and constraint solving. The exhaustive approach is characterized by attempting all possible mappings to provide an optimal solution. It can be very computationally intensive and is only suitable for smaller systems. D'Ambrosio and Hu have presented an exhaustive technique for hardware-software

partitioning [11]. However, their approach is limited to single processor architectures and ignores the communication overhead. A hardware-software partitioning technique using mixed integer linear programming is presented by Prakash and Parker [42]. The execution time of this technique is prohibitive for large task graphs. Moreover, this approach is limited to bus based architectures or pre-determined point-to-point interconnection topologies. A constraint solving approach has been presented by Kuchcinski in the JaCoP system that concentrates on scheduling and resource assignment [32].

The heuristic-based co-synthesis approach can be divided into two methods: constructive and iterative. The iterative scheme is characterized by having an initial solution, which is iteratively improved. Kirovski and Potkonjak presented an iterative algorithm that includes power as a cost function but their approach ignored the inter-task communication time [30]. Other iterative techniques have been developed [25] but they are limited in that they allow for only one type of communication link. Li and Wolf have presented an iterative co-synthesis algorithm capable of synthesizing memory hierarchies for bus architecture topologies [36]. MOGAC is an iterative approach to the co-synthesis problem that uses genetic algorithms [16]. Experimental results show that for large systems MOGAC suffers due to large execution times. Wolf has also presented an iterative approach to the co-synthesis problem producing generic device architectures [47]. Generic device architectures can be tuned to a particular application, but it can also result in disorganized and difficult to understand designs as the interconnection topology may

not conform to an established architecture. The constructive heuristic method is characterized by building the solution step by step, where the final output is not available until the algorithm terminates. Constructive co-synthesis algorithms are presented in the COSYN [15] and COFTA [13] systems. Bakshi and Gajski have also presented a constructive partitioning approach that supports pipelining at varying degrees of granularity [2]. Although their approach allows the addition of multiple software processors, it does not account for the hardware cost of adding each CPU. All of the above co-synthesis algorithms support distributed embedded systems but none have utilized hypercube topologies as a target architecture.

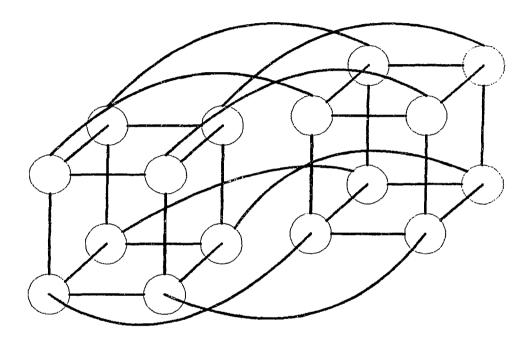

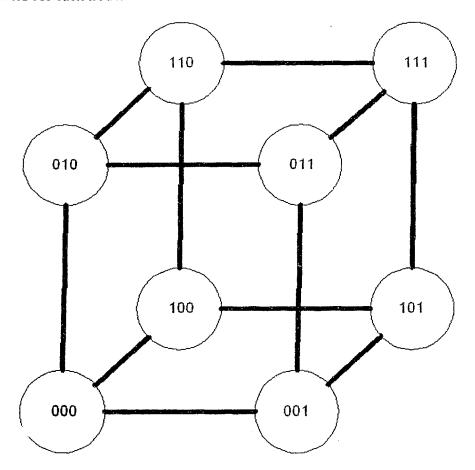

# 2.4 Hypercube Architectures

Hypercube topologies are useful for high performance embedded systems and have a number of advantages over other architectures [12, 27, 35, 43]. Hypercube nodes represent processing elements (PE) and a link between nodes represents a communication interface (serial, parallel, Ethernet link, etc.). Hypercube topologies are very flexible, versatile and generic. Figure 2.4 shows a hypercube network of degree four, constructed from two 3D hypercubes. The high level of interconnectivity in a hypercube architecture results in a system that is suited to fault tolerance. Additionally, hypercube systems support high performance computation while limiting the communication overheads and/or bottlenecks associated with large-scale systems consisting of many PEs. These features make hypercube architectures

an excellent choice for multiple PE embedded systems that need to couple fault-tolerance with complex computation. Additional advantages of hypercube architectures include topologies with small diameters and high levels of symmetry. Finally, routing in hypercube networks is well researched and efficient routing algorithms are available [29].

Figure 2.4: A 4D Hypercube

The main disadvantage of hypercube topologies is their poor upward scalability. It can be a difficult and complex process to add nodes to a hypercube network. This criticism applies more directly to hypercube computer systems, which are likely to be reconfigured and expanded regularly. It is uncommon for a distributed embedded device that has already been manufactured to require any additional processing

elements. Such a circumstance could be used in reconfigurable space systems. Another disadvantage of hypercube systems is the large number of communication links, but additional links support fault tolerance. These communication links and their interfaces to the processing elements result in a significant cost overhead. However, it should be noted that this research targets high performance fault-tolerant embedded devices. As a result, the associated cost to produce systems that meet the flexibility, reliability and performance requirements of demanding applications is knowingly accepted.

Many co-synthesis methods for distributed embedded systems target varying architectures. Hypercube topologies can be considered a superset of a number of other hierarchical architectures. Topologies such as mesh, torus, binary and quad trees can be partially represented by suitable sized hypercube topologies. Binary trees have even been embedded in incomplete hypercube systems [51]. A hierarchical architecture (e.g. tree topology) is one of the most prevalent system targets in the high performance distributed co-synthesis research projects [13, 14].

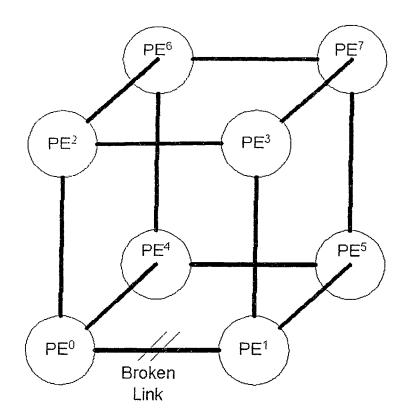

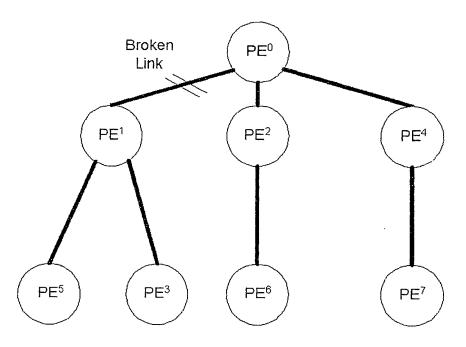

Much of the work on automatic architecture generation in co-synthesis algorithms for distributed embedded systems has concentrated on hierarchical topologies [14]. Although hierarchical systems can be adapted to enhance their fault tolerant capabilities [13], a comparison of the two architectures is provided to illustrate the capabilities of hypercube topologies. Consider a 3D hypercube with eight processing elements presented in Figure 2.5. If the communication link between PE<sup>0</sup> and PE<sup>1</sup>

fails, the device could still operate correctly by routing messages along alternate channels (e.g.  $PE^0 \rightarrow PE^4 \rightarrow PE^5 \rightarrow PE^1$ ). System performance would decrease as communication between nodes connected by a faulty link (e.g.  $PE^0 - PE^1$ ) would take longer (three transfers instead of one). However, most importantly, the system will continue to function. Now consider a possible hierarchical architecture implementation of the same embedded device shown in Figure 2.6. If the equivalent communication link (connecting  $PE^0$  and  $PE^1$ ) fails,  $PE^1$ ,  $PE^3$ , and  $PE^5$  of the embedded device would cease to function as they cannot communicate with any of the other PEs. This would result in a catastrophic system failure. The benefits over alternative architectures were a major motivation for developing the first hardware-software co-synthesis algorithm targeting hypercube topologies.

Figure 2.5: Example Hypercube Architecture

Figure 2.6: Example Hierarchical Architecture

### **CHAPTER 3**

# CO-SYNTHESIS FOR HYPERCUBE SYSTEMS

### 3.1 Introduction

A constructive co-synthesis approach that targets a hypercube topology as the final system architecture is presented. The algorithm uses a library of processing elements (PEs) including processor cores (CPUs) and application specific integrated circuits (ASICs), which provides relevant data such as hardware area requirements and performance information. The library can consist of many CPU types and ASICs. The library also provides information related to various types of communication links available with their interconnectivity costs. The algorithm takes in a task graph representing the functionality of the device. The communication links are generic and the co-synthesis algorithm supports all types of communication links including serial, parallel, etc. The algorithm assumes that each PE in the hypercube system consists of either a CPU or an ASIC. In addition to this, each PE consists of some local memory for computational purposes and interface circuitry for communication links.

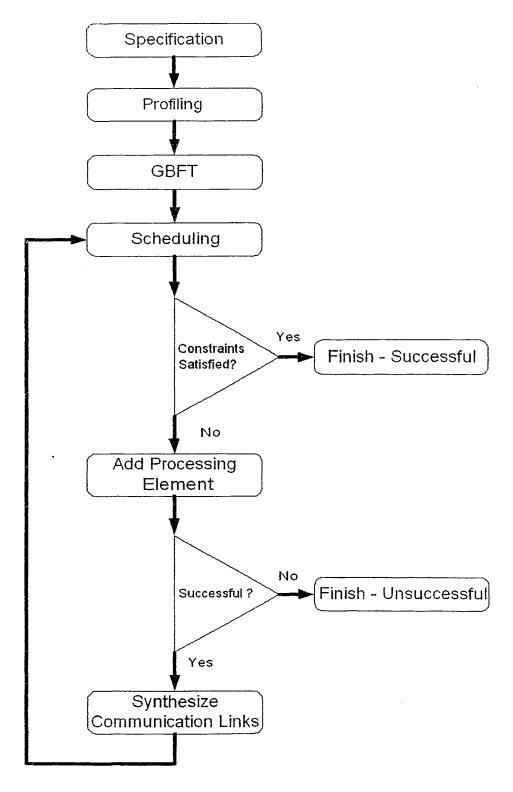

The constructive co-synthesis approach presented in this thesis is provided in Figure 3.1 and consists of six main steps:

- 1) **Specification:** Defining the required device functionality and performance and area requirements.

- Profiling: Evaluating each functional unit in the specification for performance and area utilization data.

- 3) Group Based Fault Tolerance (GBFT): A heuristic technique for adding fault tolerance to an embedded device at the task graph level.

- 4) **Scheduling:** A technique for evaluating the current device architecture for performance.

- 5) Add Processing Element: A heuristic technique for adding an additional processing element (CPU or ASIC) to the current device architecture.

- 6) Synthesize Communication Links: A technique for arranging the system's processing elements into a hypercube topology and synthesizing all connecting communication links.

The first phase of the approach is concerned with defining the device requirements. Although any specification language can be used, the experimentation presented in this thesis has been specified in C language. The second phase or the algorithm involves the profiling of the device specification. The specification is manually converted into task graph form. Each task in the task graph represents a functional section of the overall device. Each of these functional sections are timed for execution on each type of processor available in the library. Additionally hardware alternatives to the software implementation are developed and are profiled for both performance and area utilization. The profiling stage is complete once the software

and hardware timing data and the hardware area data have been collected for each task in the task graph.

The third phase is the group based fault tolerance (GBFT) method which is applied to the input task graph. This heuristic was developed to add a minimal fault detection mechanism to the system and to simplify fault recovery. The algorithm adds additional assertion and duplicate/compare tasks to the task graph. It minimizes the fault detection overhead by exploiting a task's error transparency and combining tasks into groups. The quantity and type of spare PEs in the final device is set by the user. If a fault is detected by one of the added tasks, an additional processing element is signaled to commence execution of the failed task group. This simple heuristic provides a low overhead method for performing node-fault detection and recovery.

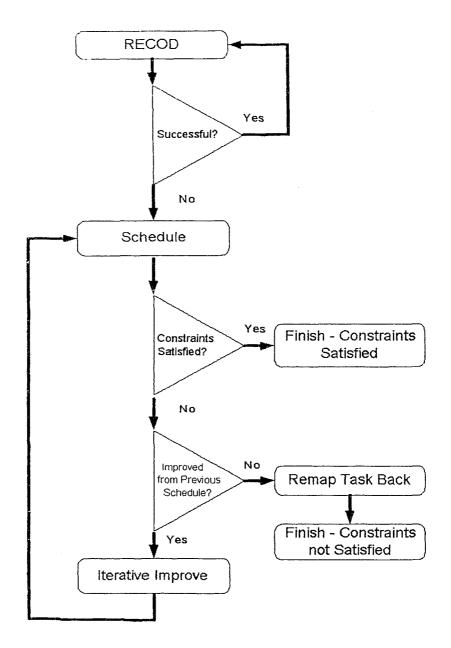

The fourth phase is the scheduling technique (see the "Scheduling" block in Figure 3.1). This heuristic method was developed to efficiently evaluate the current device architecture to determine if it meets performance requirements. In order to improve device throughput, the scheduling technique utilizes the established RECOD retiming heuristic to support pipelining of the task graph [7]. The scheduler accurately predicts overall device performance by scheduling tasks based on data dependencies. If the scheduler finds a task execution configuration that allows the current device architecture to meet performance requirements then the co-synthesis algorithm terminates successfully. If the scheduler is unable to schedule the task graph within device performance constraints the co-synthesis algorithm proceeds to the fifth phase.

The fifth phase is concerned with the addition of another processing element to the system (see the "Add Processing Element" block in Figure 3.1). This section of the co-synthesis algorithm analyzes the current device architecture, the current task mappings, each task's hardware/software performance data and each task's hardware area data to determine the ideal type of processing element to add to the current system. If this phase is successful in adding a processing element to the system, the co-synthesis algorithm proceeds to phase six. If this phase is unsuccessful in adding another processing element (unable to add more hardware while still meeting the device hardware area constraint) the co-synthesis algorithm terminates unsuccessfully and provides the user with the partial solution generated.

The sixth phase is concerned with arranging the system's processing elements within a hypercube configuration and synthesizing all of the communication links (see the "Synthesize Communication Links" block in Figure 3.1). This phase arranges all of the processing elements within a hypercube topology while attempting to keep PEs with high levels of intercommunication within close proximity of each other. Once all of the system's PEs have been arranged, communication links connecting the PEs are synthesized. Once this phase has completed, the co-synthesis algorithm proceeds to the scheduling phase.

Figure 3.1: Hypercube Co-Synthesis Algorithm Flow

# 3.2 Fault Tolerance at the Task Graph Level

#### 3.2.1 Overview

This subsection discusses the two main preexisting techniques for adding fault detection/tolerance at the task graph level. Additionally, section 3.2.4 presents an original contribution to task graph based fault tolerance techniques. In all cases fault detection is accomplished through the addition of fault detection tasks to the task graph. There are three types of tasks that any of the approaches presented may add to a task graph: assertion tasks, duplicate tasks and compare tasks. An assertion task will analyze another task's output in order to determine whether the generated results are erroneous. A duplicate task reproduces the same work as another task in the graph. Typically a duplicate task will utilize an alternative implementation to that used by the task it is duplicating. A compare task will examine the results of two tasks to detect any inconsistencies. The addition of an assertion task typically requires considerably less computational overhead than the addition of a duplicate and compare set. However, assertion tasks are not always feasible. For an assertion task to be used, error states must be able to be detected by analyzing the results. An example assertion task could be the analysis of a checksum or checking that the generated results lie within an expected range. Duplicate and compare tasks tend to require a much higher computational overhead. First the entire task's functionality needs to be duplicated and then both generated results need to be compared.

#### 3.2.2 Task Based Fault Tolerance

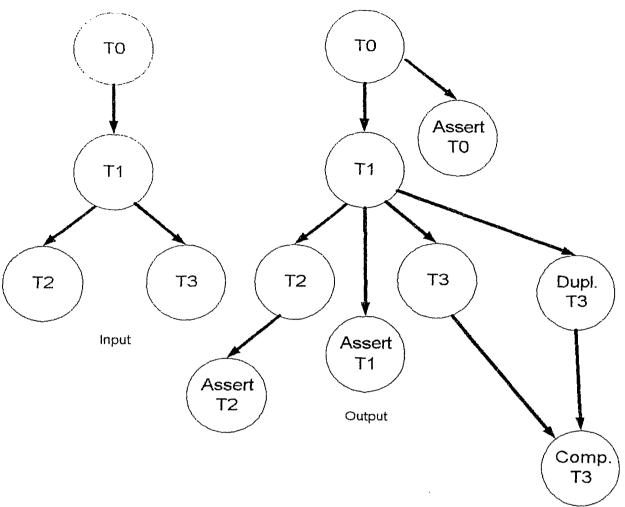

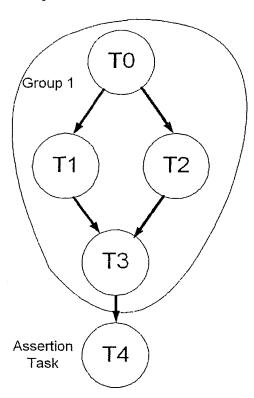

Task based fault tolerance (TBFT) was developed by Yajnik et al. [49]. Task based fault tolerance is a technique designed to add fault detection capabilities at the task graph level. In task based fault tolerance, some form of error detection must be performed for the results generated by each node in the task graph. Due to the significant difference in fault tolerant overhead, assertion tasks are favoured in the task based fault tolerance algorithm. If a given task is capable of supporting assertions then an assertion task is added. Duplicate and compare tasks are only added if assertions are unavailable for the given task. To demonstrate these concepts Figure 3.2 provides an example input task graph. Figure 3.2 also illustrates the resultant task graph after processing by the task based fault tolerance algorithm. Here all of the tasks in the graph support the use of assertion tasks for error detection with the exception of task T3. Task T3 has had duplicate and compare tasks added to provide support for fault detection.

Figure 3.2: Task Based Fault Tolerance Example

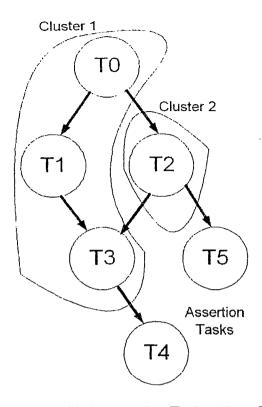

# 3.2.3 Cluster Based Fault Tolerance

Cluster based fault tolerance was developed by Dave and Jha [13]. This technique was developed as an extension of the ideas presented in the task based fault tolerance algorithm. Modifications were made to the approach in order to reduce the substantial fault tolerant overhead prevalent in task based fault tolerance. In cluster

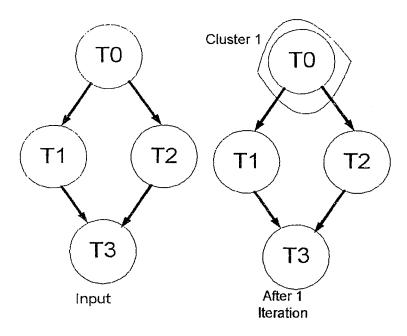

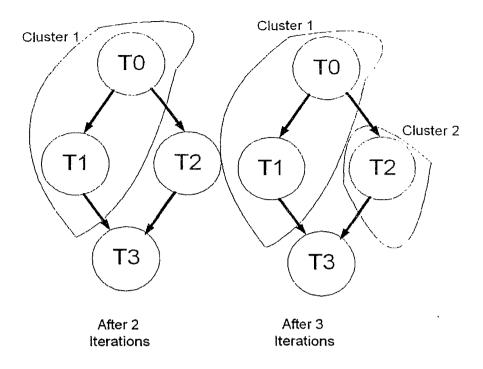

[13]. If a task provided with an erroneous input always produces an erroneous output then that task is said to be error transparent. This effect is exploited in their algorithm by grouping error transparent tasks into clusters which only require one assertion or duplicate/compare task. Figure 3.3 shows an example task graph input and the results generated by one iteration of the cluster based fault tolerance algorithm. Figure 3.4 shows the results after both 2 and 3 iterations of the algorithm. Figure 3.5 shows the final clusters for the given input task graph. After all of the tasks have been grouped into clusters, each cluster is given an assertion or duplicate/compare task to perform error detection. Figure 3.6 shows the final clustered task graph with the addition of error detecting assertion tasks. Each cluster is now treated as a single task in order to ensure that all tasks within a cluster are executed on the same processing element. In the example graph provided, all of the tasks are assumed to be error transparent.

The CBFT algorithm traverses a task graph based on task priority levels that favour tasks that are higher in the graph. The algorithm only allows one of a given task's children to be added to that task's cluster. Cluster based fault tolerance also introduces the concept of a maximum tolerated error detection time. If a large number of tasks were grouped into one cluster and an error occurs in the uppermost task, the error state would not be detected until all tasks in that cluster have completed execution. This may be undesirable as it will adversely affect performance. To avoid this problem, Dave and Jha have incorporated a user specified maximum tolerated error detection time into the cluster based fault tolerance algorithm [13]. The

algorithm will not group more tasks into one cluster if the sum of the software execution times of those tasks exceeds the user specified maximum error detection time. In the cluster based fault tolerance algorithm, if an error is detected on a given cluster, the entire functionality of that cluster is moved to a spare processing element and signaled to recommence execution.

Figure 3.3: Cluster Based Fault Tolerance - Input & 1 Iteration

Figure 3.4: Cluster Based Fault Tolerance – 2 and 3 Iterations

Figure 3.5: Cluster Based Fault Tolerance - Final Clustering

Figure 3.6: Final Added Assertion Tasks After Clustering

# 3.2.4 Group Based Fault Tolerance

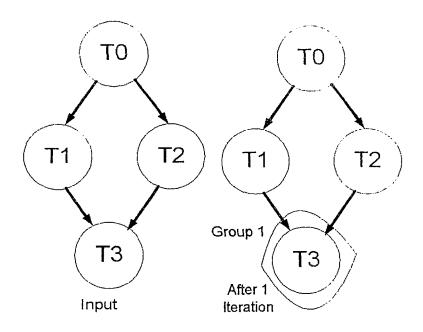

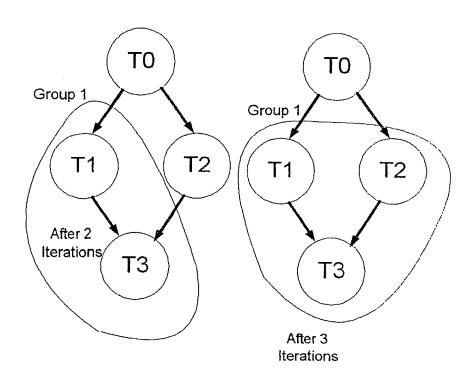

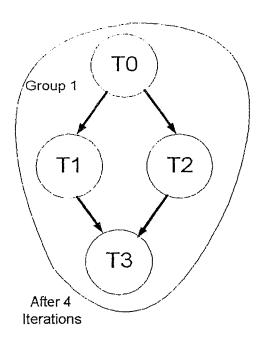

This section presents a new and original technique for adding fault detection and tolerance at the task graph level named group based fault tolerance (GBFT). This technique was developed as an extension of the ideas presented in both the task based fault tolerance [49] and cluster based fault tolerance algorithms [13]. Modifications were made to the approaches in order to reduce the fault tolerant overhead prevalent. This algorithm utilizes the concept of error transparency. Group based fault tolerance also uses the concept of a user specified maximum tolerated error detection time.

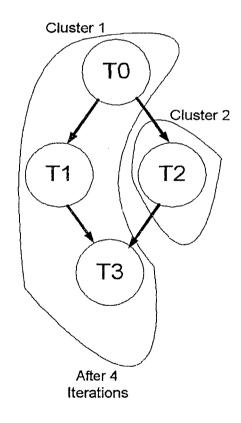

In group based fault tolerance, the task graph is traversed from the lowest nodes to the highest nodes. Each leaf node (bottom level node) is assigned to its own group. Each of the leaf's parents are analyzed to determine whether they can potentially be added to the given leaf's group. A parent is considered a possibility for grouping in its child's group if it is not already grouped and if adding it to its child's group will not violate the user imposed error detection timing constraint. Once the set of parents eligible for grouping have been assembled for a given task, the parents are iteratively added to the group in order of decreasing fault tolerant overhead. This process is ended if the addition of another parent task to the group will violate the user defined error detection constraint. If a task has no children, its fault tolerant overhead is set to its assertion overhead. If a task i does have children, its fault tolerant overhead is calculated to be:

max[assertion \_ overhead(children(i)) + Com(i, children(i))] + assertion \_ overhead(i) where,

assertion\_overhead(i) = the assertion overhead of task i children(i) = set of the child tasks of i Com(u, v) = communication time from task u to v across a communication link

Figure 3.7 shows an example task graph input and the results generated by one iteration of the group based fault tolerance algorithm. Figure 3.8 shows the results after both 2 and 3 iterations of the algorithm. Figure 3.9 shows the final groupings for the given input task graph. Finally, Figure 3.10 shows the final clustered task

graph with the addition of error detecting assertion tasks. A more complex example of GBFT based task groupings is provided in Figures 4.6, 4.7, 4.8 and 4.9 in section 4.2. After all of the tasks have been grouped, each group is given an assertion or duplicate/compare task to perform error detection. Each group is now treated as a single task in order to ensure that all tasks within a group are executed on the same processing element. In the example graph provided, all of the tasks are assumed to be error transparent. In the group based fault tolerance algorithm, if an error is detected on a given cluster, the entire functionality of that cluster is moved to a spare processing element and signaled to recommence execution.

The group based fault tolerance algorithm adds assertion and duplicate/compare tasks to a task graph. It does not add assertion or duplicate/compare tasks to perform checks on the fault detection tasks that it adds. If fault detection of faults occurring in the GBFT added tasks is wanted, then it must be added manually after the GBFT algorithm has completed execution.

Figure 3.7: Group Based Fault Tolerance - Input & 1 Iteration

Figure 3.8: Group Based Fault Tolerance – 2 & 3 Iterations

Figure 3.9: Group Based Fault Tolerance – Final Grouping

Figure 3.10: Final Added Assertion Task After Grouping

## 3.2.5 Task Graph Based Fault Tolerance Comparison

A comparison of the results of the group based fault tolerance algorithm with both the cluster based and task based techniques is provided in order to evaluate the newly developed GBFT technique. Thirteen random test cases were generated and the output of all three algorithms is compared. The test cases have varying task graph configurations and varying user defined tolerated error detection times. The outputted error detection information from each algorithm is compared. The data collected has been assembled in Table 3.1. Here the values under the GBFT, CBFT and TBFT columns are the counts of error detection tasks added to the task graph. The fewer number of error detection tasks added to a task graph results in a smaller fault tolerance overhead. A smaller fault tolerance overhead is desirable as it will yield a fault tolerant device that utilizes less hardware and/or less computation time.

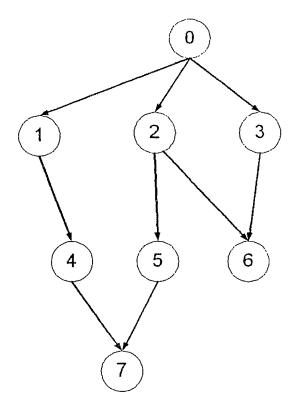

The first randomly generated task graph has been provided in Figure 3.11. Task graph 4 corresponds to the task graph from the MPEG decoding case study. The task graph can be found in Figure 4.1. Task graph 5 corresponds to the task graph from the block matching case study and can be found in Figure 4.6.

The information gathered in the table reveals that the group based fault tolerance technique yields a 18.75% improvement in fault tolerance overhead over the cluster

based fault tolerance technique and a 45.83% improvement over the task based fault tolerance technique.

Table 3.1: Fault Tolerance Comparison Data

| Task Graph # | Tolerated Error Detection Time (msec) | GBFT | CBFT | TBFT |

|--------------|---------------------------------------|------|------|------|

| 1            | 4                                     | 2    | 3    | 8    |

| 1            | 3                                     | 3    | 3    | 8    |

| 1            | 2                                     | 4    | 4    | 8    |

| 2            | 3                                     | 7    | 7    | 11   |

| 2            | 2                                     | 7    | 8    | 11   |

| 3            | 9                                     | 1    | 3    | 9    |

| 3            | 8                                     | 2    | 3    | 9    |

| 3            | 7                                     | 2    | 3    | 9    |

| 3            | 6                                     | 3    | 3    | 9    |

| 3            | 5                                     | 3    | 3    | 9    |

| 3            | 4                                     | 3    | 3    | 9    |

| 3            | 3                                     | 4    | 3    | 9    |

| 3            | 2                                     | 5    | 5    | 9    |

| 4            | 800                                   | 1    | 16   | 22   |

| 4            | 300                                   | 15   | 16   | 22   |

| 4            | 120                                   | 14   | 17   | 22   |

| 4            | 80                                    | 17   | 17   | 22   |

| 4            | 40                                    | 21   | 21   | 22   |

| 4            | 34                                    | 22   | · 22 | 22   |

| 5            | 150 000                               | 1    | 16   | 22   |

| 5            | 40 000                                | 13   | 16   | 22   |

| 5            | 30 000                                | 14   | 16   | 22   |

| 5            | 20 000                                | 15   | 16   | 22   |

| 5            | 15 000                                | 16   | 16   | 22   |

Figure 3.11: Randomly Generated Task Graph (Graph #1)

# 3.3 Pipelined Scheduler

The functionality described in this sub-section occurs in the "Scheduling" block in Figure 3.1. The effectiveness of a given architecture alternative is evaluated by obtaining a pipelined schedule that is executed in the algorithm's scheduling phase. A pipelined schedule with a minimum period P is an assignment of completion times of all tasks, F(v), such that for all tasks v in the system  $0 \le F(v) \le P$ . For a task v

with a data dependence e = (u, v), where u is a parent of v, the schedule time of v must honour the following equation:

$$F(v) \ge F(u) + v_{out} + C(u, v)$$

if PSMatch(u, v)

$F(v) \ge v_{cov}$

otherwise

where.

$v_{exec}$  = execution time of task v

C(u, v) = the overall communication time between mapped tasks u and

v (0 if no communication)

PSMatch(u, v) = true if tasks u and v are located on the same pipelined

stage, false otherwise

This definition requires that a task will not commence execution before receiving the required data from all parent tasks. The scheduler takes communication delays and resource usage into account when assigning tasks to processing elements. The algorithm utilizes the established RECOD retiming transformation to divide the task graph into multiple pipelined stages [6, 7].

The RECOD retiming transformation divides a task graph into multiple pipelined stages by inserting a cut-line which separates two tasks (parent and child) and defines the separation between two pipelined stages. The location of this cut-line is dependent on the parent and child's current pipeline stage, the parent and child's mapping, the length of the constraining path of the parent and the amount of information passed between the parent and child.

Initially, the RECOD transformation is repeatedly used to divide the task graph into a maximum number of pipelined stages. After performing the RECOD retiming transformation, the scheduler attempts to assign completion times to all tasks to satisfy device performance requirements. If unsuccessful, the algorithm attempts to improve the task allocations iteratively in order to minimize device communication overhead. A flow diagram of the scheduler's operation is provided in Figure 3.12.

Figure 3.12: Hypercube Co-Synthesis Scheduler

For the purposes of scheduling ("Scheduling" block in Figure 3.1), each task from the input task graph is assigned to one of the three sets, m, n and p. In order to specify the first set, pathLoadChild, pathLoadParent and pathLoad variable values are assigned to each task v. These values are defined as:

```

pathLoadChild(v) = v_{exec} + \max\{PSMatch(v, children(v)) * pathLoadChild(children(v))\}

pathLoadParent(v) = v_{exec} + \max\{PSMatch(v, parents(v)) * pathLoadParent(parents(v))\}

pathLoad(v) = pathLoadChild(v) + pathLoadParent(v) - v_{exec}

where,

PSMatch(u, v) = 1 \text{ if tasks } u \text{ and } v \text{ are located on the same pipelined}

stage, 0 \text{ otherwise}

children(v) = \text{set of the child tasks of } v

parent(v) = \text{set of the parent tasks of } v

```

As a result, a task v's pathLoad is the value of the heaviest loaded path containing task v.

The first set of tasks m is defined as:

```

∃ m AT → ( pathLoad(m) == max{pathLoad(AT)} )

where,

∃, →, and == represent there exists, such that and equivalent respectively

AT is the set of all tasks

```

Set m is the set of tasks that are located on the constraining path and are scheduled first. Set w consists of all the tasks having a path to m. The second set n, is defined as: n = w - m.

Set n consists of tasks that are ancestors of all the tasks of set m excluding the members of set m.

The final set p, is defined as: p = AT - m - n. Set p consists of the remaining ungrouped tasks and will be scheduled last.

These sets are used to prioritize the tasks for scheduling. The constraining path is the longest path through the graph in terms of the execution times of its tasks. When scheduling a task of set *m* that has unscheduled parents, the parents are scheduled first. Dividing tasks into these set configurations prioritizes tasks located on the constraining path. The tasks on the constraining path are most likely to adversely affect the target device performance and so the motivation is to schedule them first. If a system schedule is obtained that meets the performance requirements, the schedule function exits successfully, otherwise the scheduler attempts to improve iteratively. Excessive communications is a potential problem in hypercube topologies as they can slow down overall system performance by causing PEs to wait for data. When two tasks are located far from each other in the architecture, communication between them may require multiple hops. In order to alleviate this potential problem, the algorithm includes an iterative improver (as labeled in Figure 3.12) whose goal is to refine the task mapping. The value *commLevel* for each task is defined as:

$$commLevel(v, PE) = \sum Com(v, x) * Nh(v, x) + \sum Com(u, v) * Nh(u, v)$$

where,

Com(u, v) =communication time from task u to v across a communication link

N(u, v) = number of links (hops) that must be traversed to communicate between tasks u and v

$$x = children(v)$$

$$u = parents(v)$$

A task q is selected for re-mapping based on the following equation:

$$q = \arg\max\left[\frac{execTime(v, execLoc(v)) + commLevel(v, execLoc(v))}{execTime(v, APE) + commLevel(v, APE)}\right]$$

where,

$exec\ Loc(v)$  = the execution location (PE) of task v