# SUBTHRESHOLD FREQUENCY SYNTHESIS FOR IMPLANTABLE MEDICAL DEVICES

by

Tarek Khan

Bachelor of Engineering, Ryerson, 2007

A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Applied Science

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2010

$\bigodot {\rm Tarek}$ Khan 2010

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

#### Subthreshold Frequency Synthesis for Implantable Medical Devices

Master of Applied Science 2010

Tarek Khan

Electrical and Computer Engineering

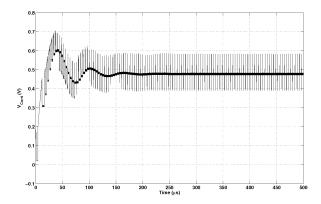

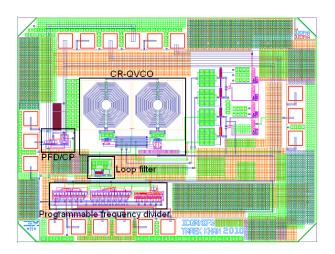

#### Ryerson University

In this thesis, several novel circuits for use in an ultra-low power integer-n frequency synthesizer operating in the 402 MHz to 405 MHz Medical Implant Communication Service spectrum have been proposed. The proposed designs include a current-reuse quadrature voltage-controlled oscillator, a novel subthreshold source-coupled logic D-latch with clear and preset functionality, a programmable frequency divider and phase/frequency detector based on the aforementioned D-latch, and a modified current-steering charge pump. A design methodology for low-power CMOS oscillators was proposed based on the MOS EKV model and  $g_m/i_d$  design methodology. The proposed designs were implemented using IBM CMRF8SF 130 nm CMOS technology and simulated using Cadence Spectre. Simulation results for the proposed current-reuse quadrature voltage-controlled oscillator and programmable frequency divider consume 420  $\mu$ W and 200  $\mu$ W respectively from a 0.7 V supply, a significant improvement compared to existing designs. The simulated phase noise of the proposed oscillator is -127.2 dBc/Hz at a 1 MHz offset. Measurement results from a fabricated prototype of the current-reuse quadrature verify the simulation results and serve as a proof-of-concept for the proposed design. The proposed designs were used to implement an integer-n frequency synthesizer and were submitted for fabrication. Simulation results show that the synthesizer consumes 635  $\mu$ W from a 0.7 V supply and has a locking time of 250  $\mu$ s.

### Acknowledgements

Although the research performed in this thesis was an individual effort on my part, there were many people who contributed in different ways to its completion.

First and foremost, I would like to thank my thesis supervisor Dr. Kaamran Raahemifar. Without providing me the opportunity to pursue graduate studies under his supervision, this thesis would not exist. The support, advice, and insight he provided was an instrumental part in the completion of this research.

I am eternally grateful to my parents, brother, grandmothers, aunts, uncles, cousins and all of my extended family who provided invaluable words of encouragement, unconditional support and faith in me and all of my endeavours, academic and otherwise. My family has always been understanding of my hectic workload and subsequent absence from many family gatherings during both my undergraduate and graduate studies.

My time in grad school was made much more memorable because of my friends Farnoos, Umair, Nima, Amin, and Dominic, as well as all the other grad students from ENG313. Even though we had many conversations about how agonizing and miserable life as a grad student is, it was those very conversations that made grad studies so enjoyable and entertaining.

The support engineers in the Electrical & Computer Engineering Department – Jason, Dan, Bruce and Luis – allowed me to have nearly free rein over the integrated circuits CAD tools and design kits. I never would have learned so much about how all the tools and kits come together had it not been for all the time I spent in ENG439. I hope that all the shell scripts and user guides I wrote have made the integrated circuit CAD tool environment in our department more user friendly for undergraduate students, graduate researchers, and faculty members. As well, the support engineers from The MOSIS Service, namely Zach and Glenn, and those at Cadence Design Systems, provided crucial help and support for troubleshooting and resolving issues with the IBM CMRF8SF design kit and Cadence EDA tools.

Finally the committee members for my thesis defence, Dr. James Smith, Dr. Vadim Geurkov and Dr. Farah Mohammadi for taking the time to read my thesis and provide comments from their unique perspectives.

## Dedication

To my late grandmother, Qamar Jabbar, who passed away in March 2010.

# Contents

| 1        | Inti | roduction 1                                                                                                                                                |

|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1  | Motivation                                                                                                                                                 |

|          | 1.2  | Medical Implant Communication Service                                                                                                                      |

|          |      | 1.2.1 Overview                                                                                                                                             |

|          |      | 1.2.2 Technical specifications 4                                                                                                                           |

|          |      | 1.2.3 Existing work $\ldots \ldots \ldots$ |

|          | 1.3  | Project objective and target applications                                                                                                                  |

|          | 1.4  | Contributions                                                                                                                                              |

|          | 1.5  | Organization of report                                                                                                                                     |

| <b>2</b> | Osc  | cillators and frequency synthesis 11                                                                                                                       |

|          | 2.1  | Overview                                                                                                                                                   |

|          | 2.2  | CMOS Oscillators                                                                                                                                           |

|          |      | 2.2.1 General considerations                                                                                                                               |

|          |      | 2.2.2 Negative- $g_m LC$ -tank oscillators                                                                                                                 |

|          |      | 2.2.3 Voltage-controlled oscillators 19                                                                                                                    |

|          |      | 2.2.4 Phase noise in oscillators                                                                                                                           |

|          |      | 2.2.5 Quadrature oscillators                                                                                                                               |

|          | 2.3  | PLLs and synthesizers                                                                                                                                      |

|          |      | 2.3.1 Simple phase-locked loop                                                                                                                             |

|          |      | 2.3.2 Charge-pump phase-locked loop                                                                                                                        |

|          |      | 2.3.3 Integer-N frequency synthesizer                                                                                                                      |

|          | 2.4  | Summary                                                                                                                                                    |

| 3        | Pro  | oposed work 37                                                                                                                                             |

|          | 3.1  | Design specifications                                                                                                                                      |

|          | 3.2  | Proposed CR-QVCO                                                                                                                                           |

|          |      | 3.2.1 Proposed low power VCO design methodology                                                                                                            |

|          | 3.3  | A ST-SCL programmable divider                                                                                                                              |

|          |      | 3.3.1 Proposed D-latch with clear and preset functionality                                                                                                 |

|   | 3.4            | A ST-SCL PFD, current-steering CP, and LF          | 52        |

|---|----------------|----------------------------------------------------|-----------|

|   | 3.5            | Summary                                            | 53        |

| 4 | $\mathbf{Res}$ | sults                                              | 55        |

|   | 4.1            | IBM CMRF8SF 130 nm CMOS Technology                 | 55        |

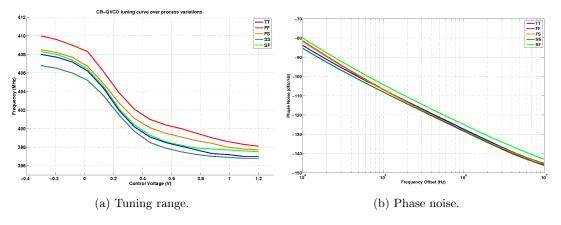

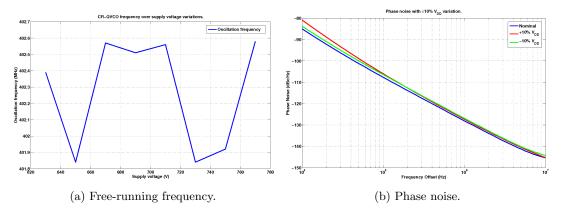

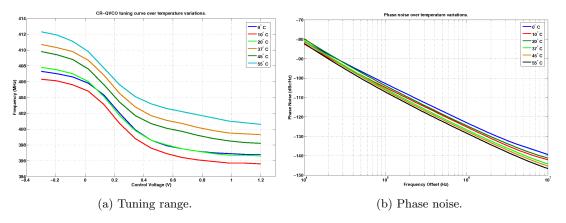

|   | 4.2            | Current reuse quadrature VCO                       | 55        |

|   |                | 4.2.1 Simulation                                   | 57        |

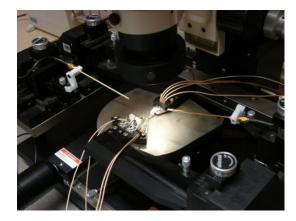

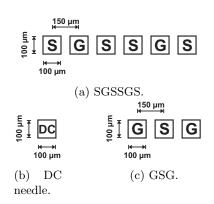

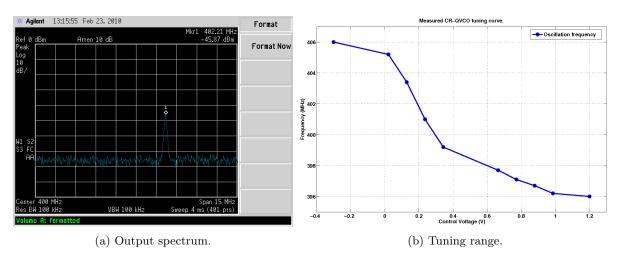

|   |                | 4.2.2 Measurement                                  | 59        |

|   |                | 4.2.3 Fabrication challenges                       | 60        |

|   | 4.3            | ST-SCL programmable divider                        | 61        |

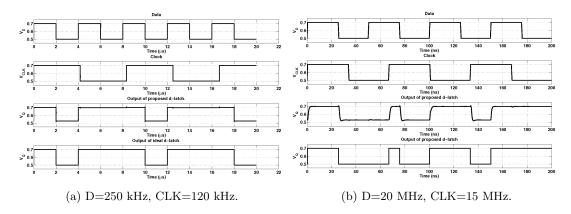

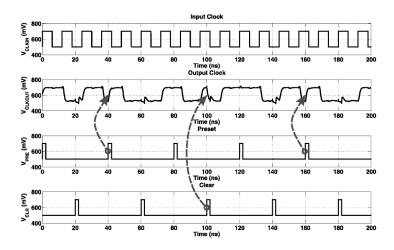

|   |                | 4.3.1 Clear/preset D-latch simulation              | 61        |

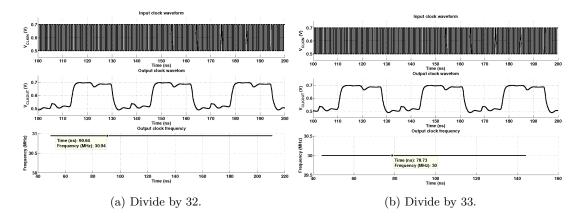

|   |                | 4.3.2 Dual-modulus prescaler simulation            | 62        |

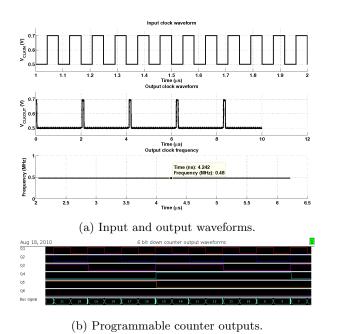

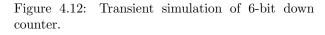

|   |                | 4.3.3 Programmable down counter simulation         | 62        |

|   |                | 4.3.4 Programmable divider simulation              |           |

|   | 4.4            | PFD, CP, and LF.                                   |           |

|   | 4.5            | 402 MHz to 405 MHz integer-n frequency synthesizer |           |

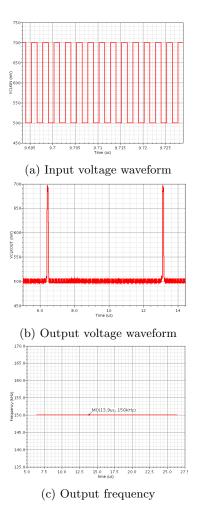

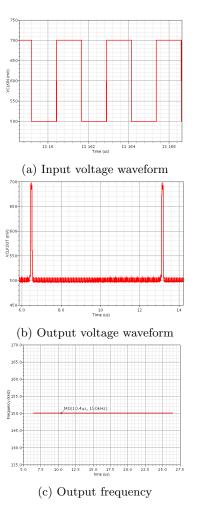

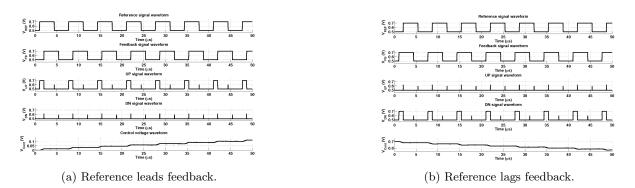

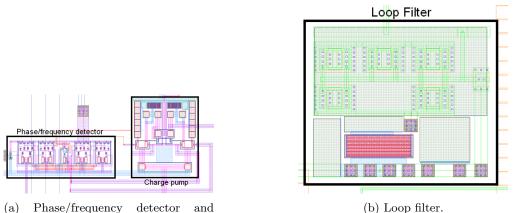

|   |                | 4.5.1 Simulation                                   |           |

|   |                | 4.5.2 Fabrication challenges                       |           |

|   | 4.6            | Summary                                            |           |

| 5 | Com            | nclusion and future work                           | <b>69</b> |

| 9 |                |                                                    |           |

|   | 5.1            |                                                    | 69        |

|   | 5.2            | Future work                                        | 70        |

| R | efere          | ences                                              | 86        |

# List of Tables

| 1.1 | MedRadio operating specifications                                                                              | 6  |

|-----|----------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Loop filter topologies.                                                                                        | 31 |

| 3.1 | Division ratios for integer-n frequency synthesizer with 300 kHz reference frequency                           | 46 |

| 3.2 | Division ratios for integer-n frequency synthesizer with new division ratios.                                  | 47 |

| 3.3 | Control bits for the swallow counter.                                                                          | 48 |

| 4.1 | Low power VCO design methodology input parameters.                                                             | 56 |

| 4.2 | Comparision of existing MICS VCOs                                                                              | 58 |

| 4.3 | Comparison of low power programmable dividers $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 65 |

| 4.4 | Power consumption of programmable divider components                                                           | 65 |

| A.1 | Approximation of normalized intrinsic capacitances in strong and weak inversion                                | 74 |

| A.2 | Parameters describing MOSFET transistor geometry                                                               | 74 |

| A.3 | Voltages                                                                                                       | 75 |

| A.4 | Currents                                                                                                       | 75 |

| A.5 | Conductances.                                                                                                  | 75 |

| A.6 | Capacitances                                                                                                   | 75 |

| A.7 | Other parameters.                                                                                              | 76 |

| A.8 | Normalizing parameters                                                                                         | 76 |

| A.9 | Normalizing parameters                                                                                         | 76 |

|     |                                                                                                                |    |

# List of Figures

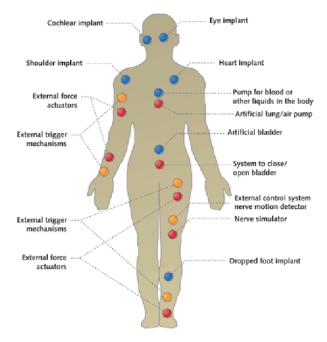

| 1.1  | Examples of patient health monitoring using implantable devices $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

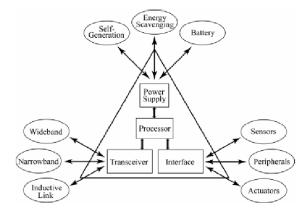

| 1.2  | General block diagram for an implantable medical device $\hfill \hfill \ldots \hfill \hfil$ | 3  |

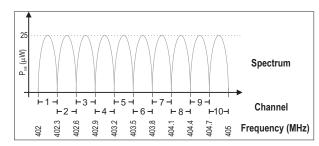

| 1.3  | Allocated frequency spectrum for Medical Implant Communication Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5  |

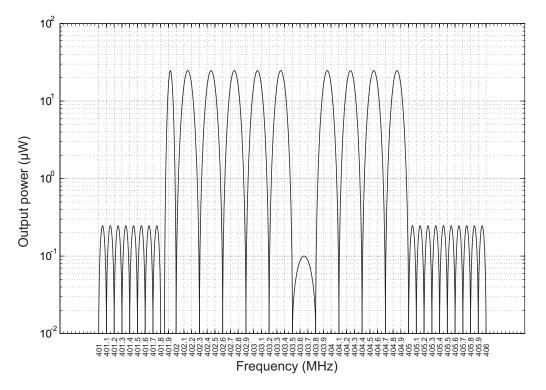

| 1.4  | Allocated frequency spectrum for Medical Device Radio<br>communication Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7  |

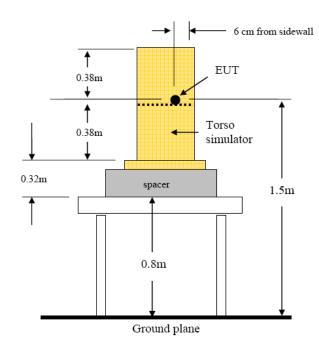

| 1.5  | MICS implant torso simulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8  |

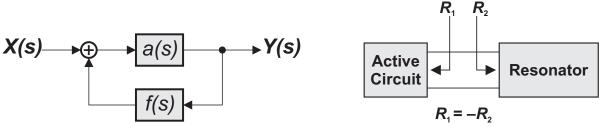

| 2.1  | Oscillator models.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12 |

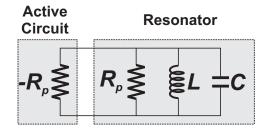

| 2.2  | LC resonator with loss compensation. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13 |

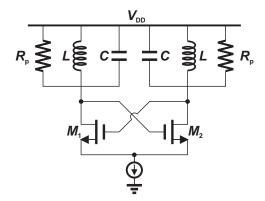

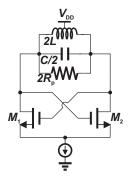

| 2.3  | Negative- $g_m LC$ -tank oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14 |

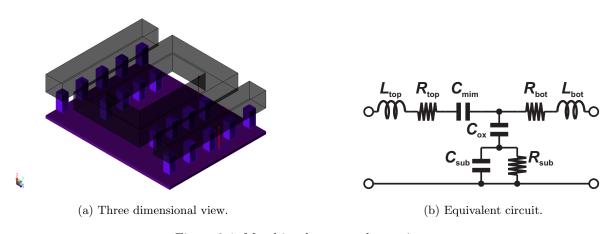

| 2.4  | Metal-insulator-metal capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16 |

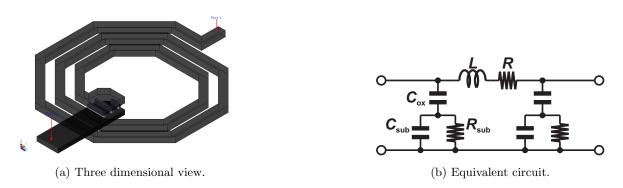

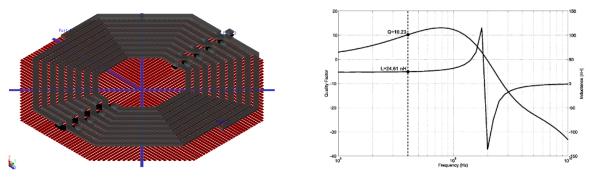

| 2.5  | Octagonal spiral inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16 |

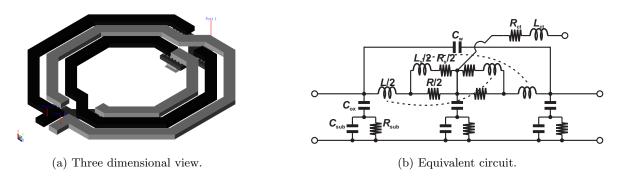

| 2.6  | Symmetric spiral inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17 |

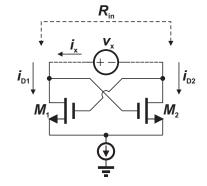

| 2.7  | Negative- $g_m$ <i>LC</i> -tank oscillator with merged tanks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17 |

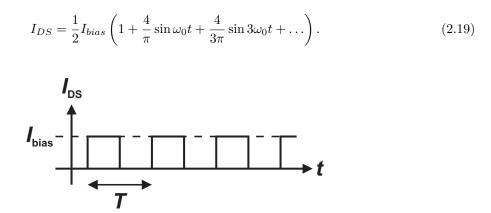

| 2.8  | Drain current for switching transistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18 |

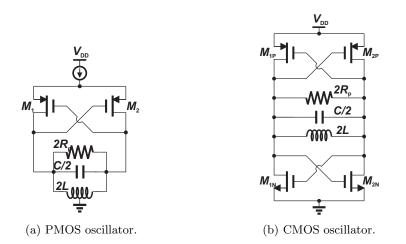

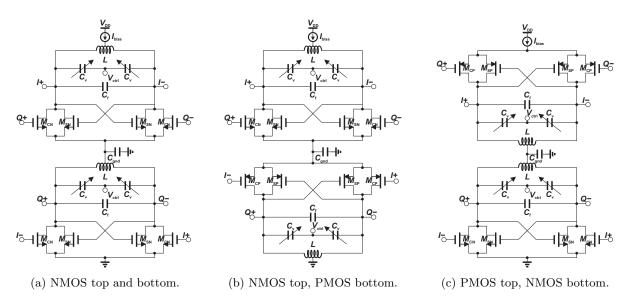

| 2.9  | Variations of the negative- $g_m$ topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18 |

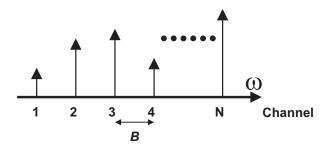

| 2.10 | Simple transceiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19 |

| 2.11 | Arbitrary spectrum for example transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19 |

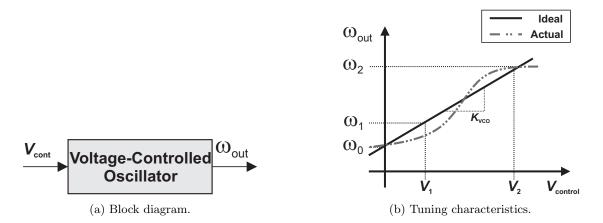

| 2.12 | Voltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20 |

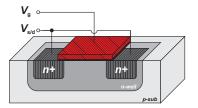

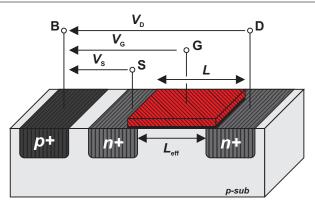

| 2.13 | Cross-section of MOS varactor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21 |

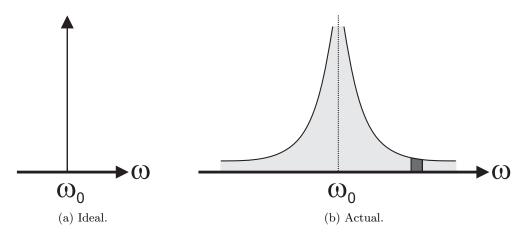

| 2.14 | Voltage-controlled oscillator output spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21 |

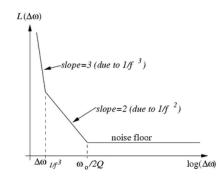

| 2.15 | Predicted phase noise spectrum.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22 |

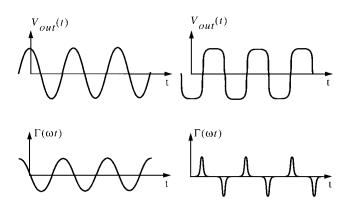

| 2.16 | Waveforms and ISFs for (a) a typical LC oscillator and (b) a typical ring oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24 |

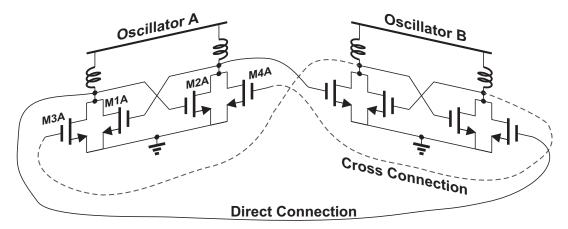

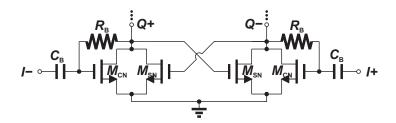

| 2.17 | Original quadrature $LC$ oscillator (omitting bias)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 24 |

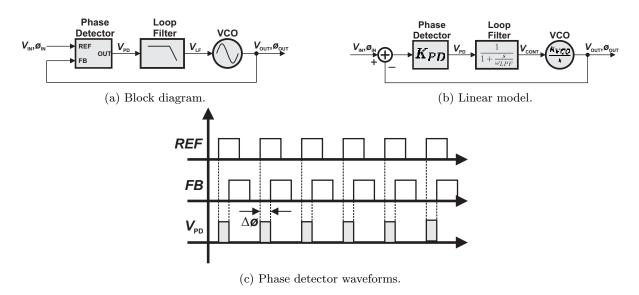

| 2.18 | Simple phase-locked loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27 |

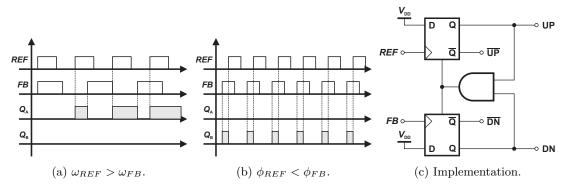

| 2.19 | Phase/frequency detector.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29 |

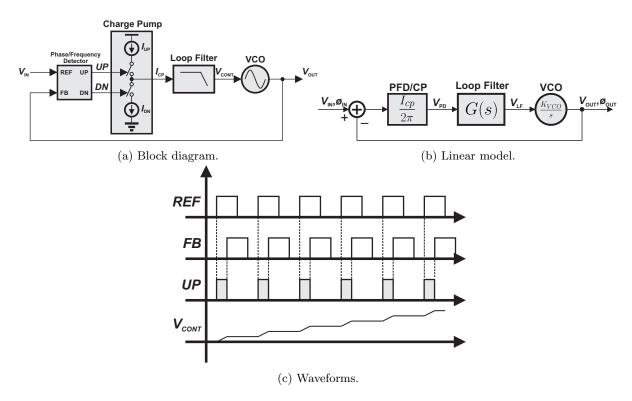

| 2.20 | Charge-pump phase-locked loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30 |

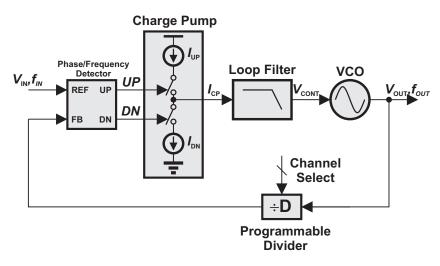

| 2.21 | Integer-n frequency synthesizer block diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32 |

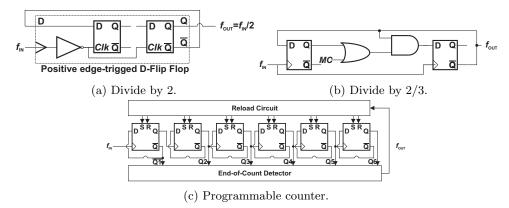

| 2.22 | Types of frequency dividers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32 |

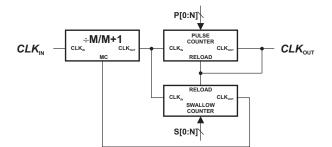

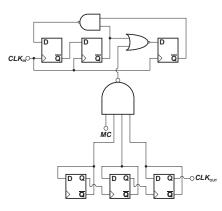

| 2.23 | Block diagram of programmable frequency divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33 |

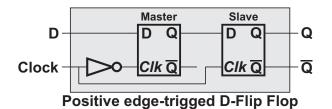

| 2.24 | Master-slave d-flip flop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

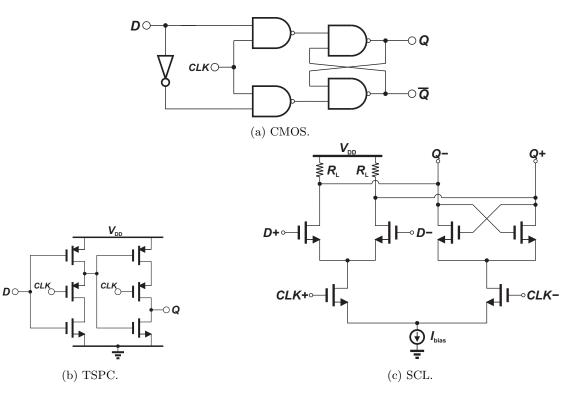

| 2.25 | Types of d-latches.                                                                                                                                                        | 34 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

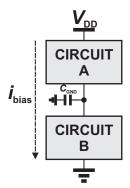

| 3.1  | Current reuse between two stacked circuits.                                                                                                                                | 38 |

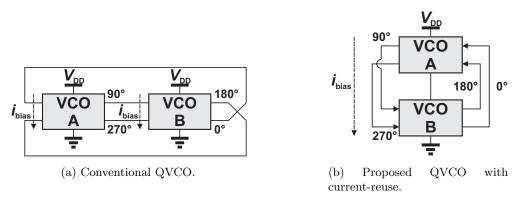

| 3.2  | Quadrature VCO block diagram.                                                                                                                                              | 39 |

| 3.3  | Possible topologies for the proposed CR-QVCO.                                                                                                                              | 40 |

| 3.4  | Modified oscillator core.                                                                                                                                                  | 41 |

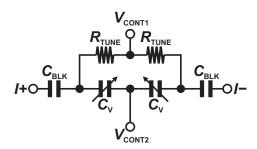

| 3.5  | Varactor frequency tuning circuit.                                                                                                                                         | 41 |

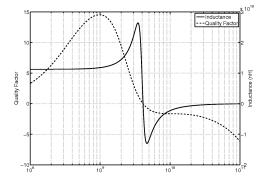

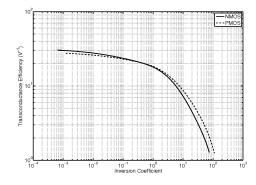

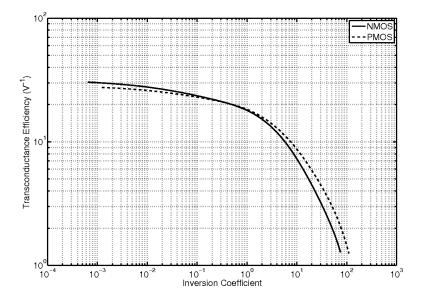

| 3.6  | Necessary graphs for proposed design methodology                                                                                                                           | 43 |

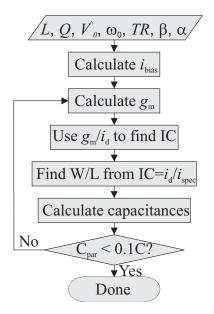

| 3.7  | Proposed VCO design methodology.                                                                                                                                           | 44 |

| 3.8  | Block diagram of pulse counter                                                                                                                                             | 48 |

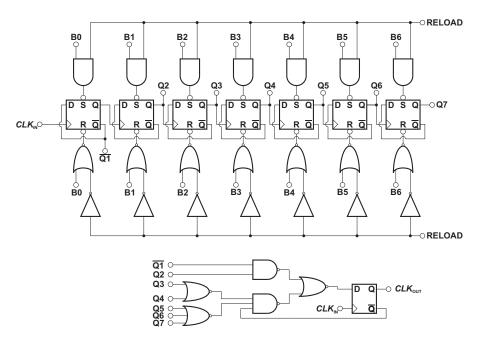

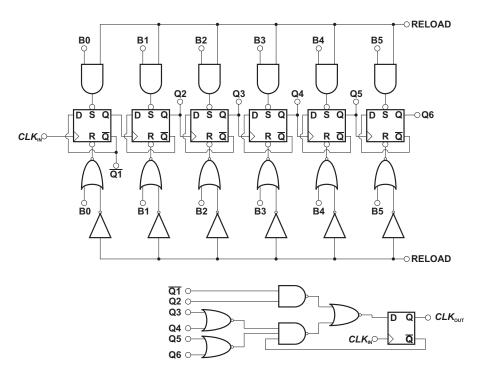

| 3.9  | Block diagram of swallow counter.                                                                                                                                          | 49 |

| 3.10 | Block diagram of dual modulus prescaler.                                                                                                                                   | 49 |

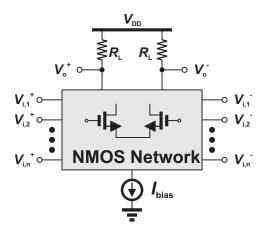

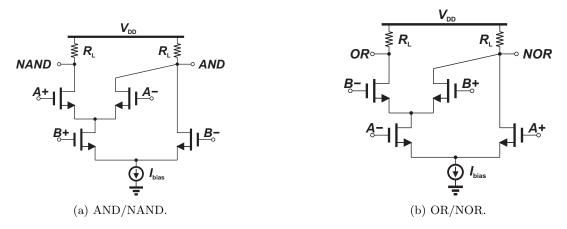

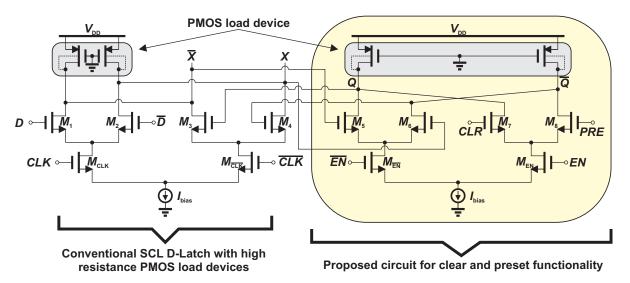

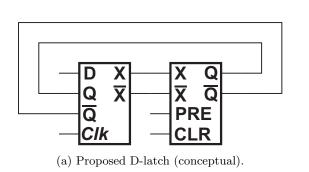

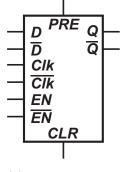

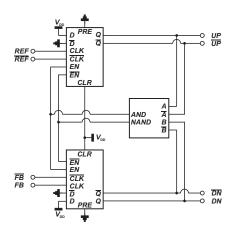

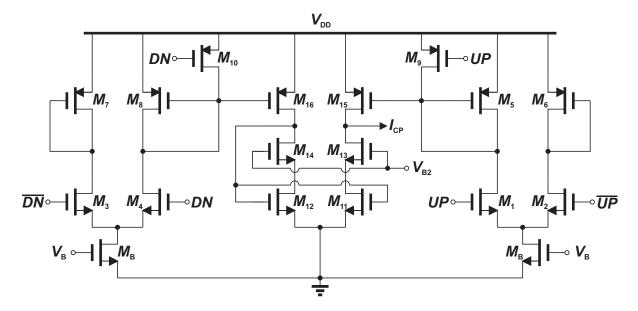

| 3.11 | General topology of an SCL gate.                                                                                                                                           | 50 |