### **Ryerson University** Digital Commons @ Ryerson

Theses and dissertations

1-1-2010

# Radio-Frequency Power Harvest And Remote Clock Frequency Calibration Of Passive Wireless Microsystems

Nima Soltani Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations

Part of the Electrical and Electronics Commons

#### Recommended Citation

Soltani, Nima, "Radio-Frequency Power Harvest And Remote Clock Frequency Calibration Of Passive Wireless Microsystems" (2010). Theses and dissertations. Paper 1762.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

# RADIO-FREQUENCY POWER HARVEST AND REMOTE CLOCK FREQUENCY CALIBRATION OF PASSIVE WIRELESS MICROSYSTEMS

by

Nima Soltani

A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Applied Science

in the Program of

Electrical Engineering

Toronto, Ontario, Canada, 2010

©Nima Soltani 2010

## Author's Declaration

| I hereby declare that I am the sole author of this thesis.                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.                                                                                     |

| I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research. |

#### Abstract

Radio-Frequency Power Harvest and Remote Clock Frequency Calibration of Passive Wireless Microsystems

Nima Soltani

Master of Applied Science

Departments of Electrical and Computer Engineering

Ryerson University

Toronto, Ontario, Canada 2010

This thesis deals with radio frequency power harvest and remote calibration of system clock of passive wireless microsystems. The proposed method of RF power harvesting utilizes a step-up transformer inserted between the antenna and voltage multiplier of passive wireless microsystems to perform both impedance transformation for power matching and voltage amplification prior to rectification. The series resistance of the primary winding is minimized while in the secondary winding, the shunt capacitive losses are minimized. The detailed analysis of the proposed method and simulation results from Spectre of Cadence Design Systems are presented. The proposed power-matching and gain-boosting network, together with voltage multipliers, has been implemented in TSMC-0.18..m 1.8V 6-metal CMOS technology with thick metal options. For the purpose of comparison, a LC power-matching and gain-boosting network with the identical voltage multiplier has also been implemented on the same chip. Measurement results demonstrate that the proposed transformer power-matching and gain-boosting technique greatly improves the power sensitivity and efficiency as compared with widely used LC matching approaches.

The proposed calibration method adjusts the frequency of the local oscillator of passive UHF wireless transponders to the desired values using an injection-locked phase-locked loop (IL-PLL). A new relaxation oscillator whose oscillation frequency is less sensitive to supply voltage fluctuation is also proposed. The power consumption of the

proposed IL-PLL is minimized by operating it the sub-threshold. A detailed analysis of non-harmonic injection locking of relaxation oscillators including locking and pulling dynamics is presented. A new integrating feedback is proposed to increase the lock range and hold the locked frequency in the absence of the injection signal. The proposed IL-PLL has been fabricated in TSMC-0.18 $\mu$ m 1.8V 6-metal 1-poly CMOS technology. The performance of the IL-PLL is validated using both simulation and measurement results. The measured power consumption of the IL-PLL with a 10 mV (640 pW) 1 MHz injection signal is 960 nW. The lock range of the IL-PLL is 30 KHz without integrating feedback and 400 KHz with integrating feedback. The frequency of the locked oscillator drifts over time at a rate of 5 Hz/ms when the external injection signal is removed.

## Acknowledgements

I wish to express my solemn gratitude to my supervisor, Professor Fei Yuan, for his relentless support and invaluable advice throughout this research. His vision has been a great source of inspiration and his insight has made possible the accomplishments herein.

I must also thank Natural Science and Engineering Research Council (NSERC) of Canada, CMC Microsystems, and Ryerson Faculty of Engineering for financing this research.

Finally, I would like to thank my family for their understanding and support throughout all my studies.

# Contents

| Intr | oduction 1                                                    |

|------|---------------------------------------------------------------|

| 1.1  | Background                                                    |

|      | 1.1.1 Architecture                                            |

|      | 1.1.2 Antenna                                                 |

|      | 1.1.3 Matching Network                                        |

|      | 1.1.4 Rectification                                           |

|      | 1.1.5 Modulation Backscatter/Load Modulation                  |

|      | 1.1.6 Demodulation                                            |

|      | 1.1.7 Wireless Link                                           |

| 1.2  | Motivations                                                   |

|      | 1.2.1 Challenges in Wireless Transfer of Power                |

|      | 1.2.2 Challenges in Data Communication                        |

| 1.3  | Objectives                                                    |

|      | 1.3.1 Efficient Power Harvesting                              |

|      | 1.3.2 Low-Power Fast Frequency Calibration                    |

| 1.4  | Contributions                                                 |

| 1.5  | Thesis Organization                                           |

| 1.6  | Chapter Summary                                               |

| Stat | e-of-the-Art                                                  |

| 2.1  | Power Harvester                                               |

| 2.2  | Clock Calibration                                             |

| 2.3  | Chapter Summary                                               |

|      | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>State<br>2.1<br>2.2 |

| 3 | $\mathbf{RF}$ | Power   | Harvesting                                                        | <b>27</b> |

|---|---------------|---------|-------------------------------------------------------------------|-----------|

|   | 3.1           | Introd  | luction                                                           | 27        |

|   | 3.2           | LC M    | atching Network                                                   | 28        |

|   |               | 3.2.1   | Power Matching                                                    | 29        |

|   |               | 3.2.2   | Power Efficiency                                                  | 31        |

|   |               | 3.2.3   | Voltage Gain                                                      | 34        |

|   |               | 3.2.4   | Numerical Results                                                 | 35        |

|   | 3.3           | Transf  | former Matching                                                   | 36        |

|   | 3.4           | Freque  | ency Tuning                                                       | 45        |

|   |               | 3.4.1   | Frequency Tuning of LC Impedance Transformation Network           | 46        |

|   |               | 3.4.2   | Frequency Tuning of Transformer Impedance Transformation Net-     |           |

|   |               |         | work                                                              | 46        |

|   | 3.5           | Measu   | rement Results                                                    | 47        |

|   | 3.6           | Chapt   | ger Summary                                                       | 50        |

| 4 | Free          | quency  | Calibration                                                       | 55        |

|   | 4.1           | Introd  | luction                                                           | 55        |

|   | 4.2           | Injecti | ion Locking                                                       | 56        |

|   |               | 4.2.1   | Free-Running Relaxation Oscillators                               | 56        |

|   |               | 4.2.2   | Relaxation Oscillators Under Injection                            | 57        |

|   |               | 4.2.3   | Locking Dynamics                                                  | 60        |

|   |               | 4.2.4   | Injection Pulling                                                 | 63        |

|   | 4.3           | Integr  | ating Feedback                                                    | 65        |

|   |               | 4.3.1   | Constructing an Integrating Feedback                              | 65        |

|   |               | 4.3.2   | Dynamics of Injection-Locked Relaxation Oscillator Without Inte-  |           |

|   |               |         | grating Feedback                                                  | 67        |

|   |               | 4.3.3   | Dynamics of Injection-Locked Relaxation Oscillator With Integrat- |           |

|   |               |         | ing Feedback                                                      | 68        |

|   |               | 4.3.4   | Noise Consideration                                               | 70        |

|   | 4.4           | Circui  | t Implementation                                                  | 71        |

|   |               | 4.4.1   | Relaxation Oscillator                                             | 72        |

|   |               | 4.4.2   | Integrating Feedback                                              | 74        |

|   |               | 4 4 3   | Power Consumption                                                 | 76        |

|   | 4.5 | Simula  | ation Results                                                        | 77 |

|---|-----|---------|----------------------------------------------------------------------|----|

|   |     | 4.5.1   | Injection Locking of Relaxation Oscillator without Integrating Feed- |    |

|   |     |         | back                                                                 | 78 |

|   |     | 4.5.2   | Injection Locking of Relaxation Oscillator with Integrating Feedback | 79 |

|   | 4.6 | Measu   | rement Results                                                       | 81 |

|   | 4.7 | Chapte  | er Summary                                                           | 83 |

| 5 | Con | clusion | as and Future Work                                                   | 93 |

|   | 5.1 | Summa   | ary                                                                  | 93 |

|   | 5.2 | Futuro  | Work                                                                 | 0/ |

# List of Tables

| 3.1 | Performance comparison of power harvesters | 51 |

|-----|--------------------------------------------|----|

| 4.1 | Performance summary of proposed IL-PLL     | 83 |

# List of Figures

| 1.1 | Architechture of a typical passive transponder device                                                                                                                        | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Popular antenna geometries for RFID's and passive transponders                                                                                                               | 3  |

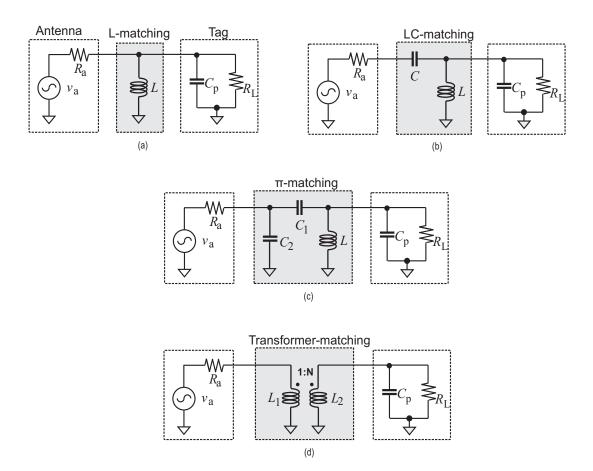

| 1.3 | A typical matching network used to matching the input impedance of the rectifier to the radiation impedance of the antenna.                                                  | 4  |

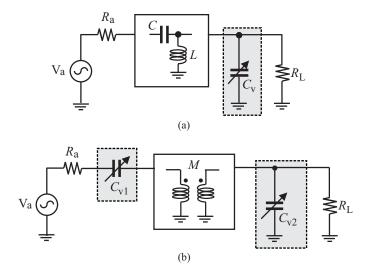

| 1.4 | Different matching network topologies for RF power harvesting. Transformer power matching circuit is proposed in this thesis                                                 | 5  |

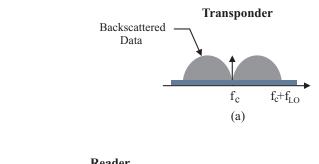

| 1.5 | Power spectrum of signals (a) at the transponder, (b) at the reader without subcarrier, and (c) at the reader with subcarrier                                                | 10 |

| 2.1 | Impedance transformation network ensures maximum transfer of power by creating passive voltage gain.                                                                         | 18 |

| 2.2 | Dickson charge-pump [16] and Nakamoto's dual half-wave rectifier [17] widely used for RF signal rectification and voltage boost in transponders                              | 19 |

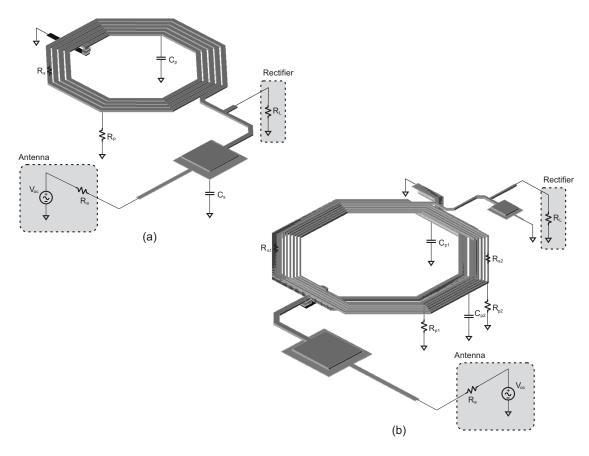

| 2.3 | (a), (b) and (c): Matching network topologies for RF power harvesting used in [12, 13] and [14] respectively. (d) Transformer power matching circuit proposed in this thesis | 20 |

| 2.4 | (a) RF power harvester proposed by [12, 13]. (b) Transformer power matching circuit proposed in this thesis                                                                  | 21 |

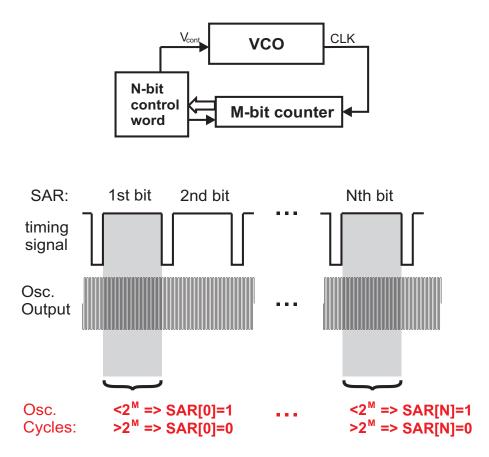

| 2.5 | The "Digital Timing Feedback Loop" frequency calibration system used in [70]                                                                                                 | 23 |

| 2.6 | The "Digital Timing Feedback Loop" frequency calibration system used in [70]                                                                                                 | 24 |

| 3.1 | Impedance transformation network for power matching and gain boosting.                                                                                                       | 29 |

| 3.2  | Power-matching and gain-boosting network using a shunt spiral inductor and a series MIM capacitor                                                                                                                                                                                                                                                                                                                                                                            | 30 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.3  | Simplified schematic of LC-based power-matching and gain-boosting network                                                                                                                                                                                                                                                                                                                                                                                                    | 32 |

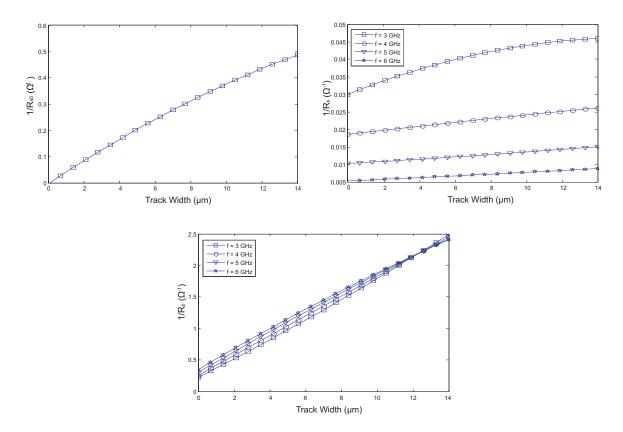

| 3.4  | Simulated dependence of the series and shunt resistive losses of a 5-turn octagonal inductor implemented in M6 of TSMC-0.18 $\mu$ m CMOS technology. The average imension of the inductor, i.e. $(d_{in}+d_{out})/2$ , where $d_{in}$ and $d_{out}$ are the inner and outer diameters of the inductor, respectively, is 200 $\mu$ m. (a) Series conductance at low frequencies. (b) Series conductance at high frequencies, and (c) Parallel conductance at high frequencies | 37 |

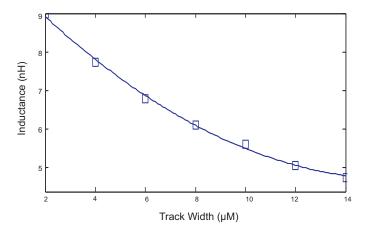

| 3.5  | Simulated effect of spiral width on the inductance of a 5-turn octagonal inductor implemented in M6 of TSMC-0.18 $\mu$ m CMOS technology                                                                                                                                                                                                                                                                                                                                     | 38 |

| 3.6  | Simulated dependence of the capacitive losses of a 5-turn octagonal inductor implemented in M6 of TSMC-0.18 $\mu$ m CMOS technology. The average dimension of the inductor, i.e. $(d_{in}+d_{out})/2$ , where $d_{in}$ and $d_{out}$ are the inner and outer diameters of the inductor, respectively, is 200 $\mu$ m. (a) Overlapping capacitance between spirals. (b) Spiral-to-substrate capacitance                                                                       | 39 |

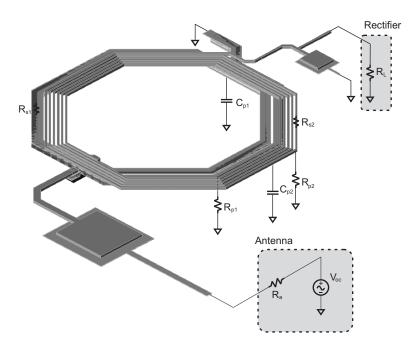

| 3.7  | Configuration of step-up transformer power-matching and gain-boosting network                                                                                                                                                                                                                                                                                                                                                                                                | 40 |

| 3.8  | Equivalent circuit of step-up transformer power-matching and gain-boosting.                                                                                                                                                                                                                                                                                                                                                                                                  | 41 |

| 3.9  | Thevenin equivalent circuit of step-up transformer power-matching and gain-boosting                                                                                                                                                                                                                                                                                                                                                                                          | 42 |

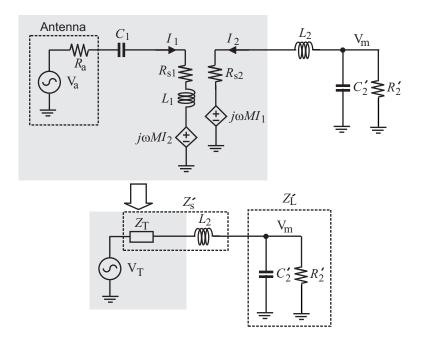

| 3.10 | Simulated passive gain for different values of radiation resistance. (a) LC matching network (spiral width $=5\mu m$ ). (b) LC matching network reduced spiral width (spiral width $=1.5\mu m$ ). (c) Step-up transformer matching network (spiral width in primary winding : $5\mu m$ , spiral width in secondary winding : $1.5\mu m$ . The load resistance is fixed at $R_L = 40k\Omega$                                                                                  | 43 |

| 3.11 | Frequency tuning in (a) LC impedance transformation network and (b) step-up transformer impedance transformation network                                                                                                                                                                                                                                                                                                                                                     | 45 |

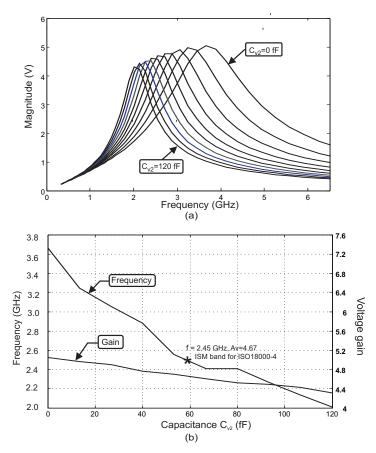

| 3.12 | (a) Simulated dependence of the voltage gain of transformer impedance                                                             |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

|      | transformation network on $C_{v2}$ and $C_{v1}$ . (b) Simulated dependence of                                                     |    |

|      | resonant frequency and voltage gain of transformer impedance transfor-                                                            |    |

|      | mation network on $C_{v2}$ . note that $C_{v1}$ is also varied with $C_{v2}$ to maintain                                          |    |

|      | that the resonant condition is on the primary side                                                                                | 47 |

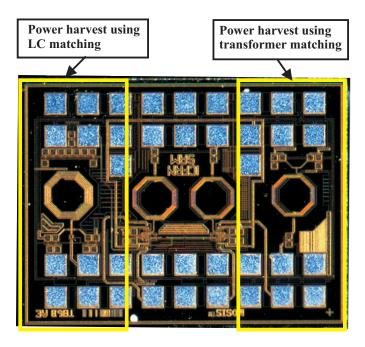

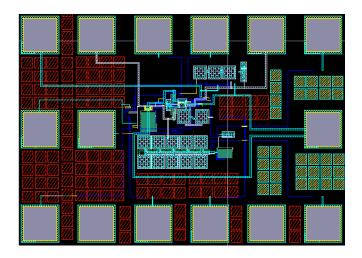

| 3.13 | Microphoto of fabricated chip. Bonding pads are arranged in accordance                                                            |    |

|      | with the configuration of available probes available                                                                              | 48 |

| 3.14 | Measurement setup                                                                                                                 | 49 |

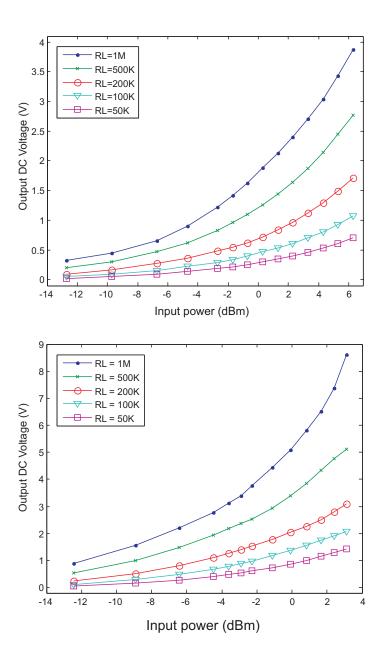

| 3.15 | Measured sensitivity of the fabricated power harvesters for different values                                                      |    |

|      | of output load. (a) Power harvester with LC matching network. (b) Power                                                           |    |

|      | harvester with step-up transformer matching network                                                                               | 53 |

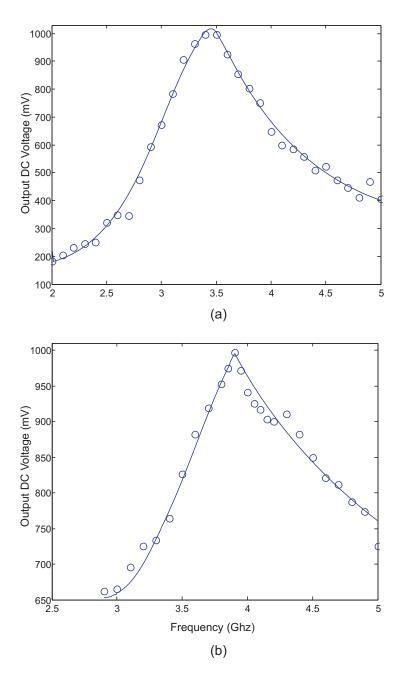

| 3.16 | Measured DC output voltage of the fabricated power harvesters for dif-                                                            |    |

|      | ferent input frequencies. (a) Power harvester with LC matching network.                                                           |    |

|      | Input power -4 dBm. (b) Power harvester with step-up transformer match-                                                           |    |

|      | ing network. Input power -11.9 dBm                                                                                                | 54 |

| 4.1  | Configuration of relaxation oscillators                                                                                           | 56 |

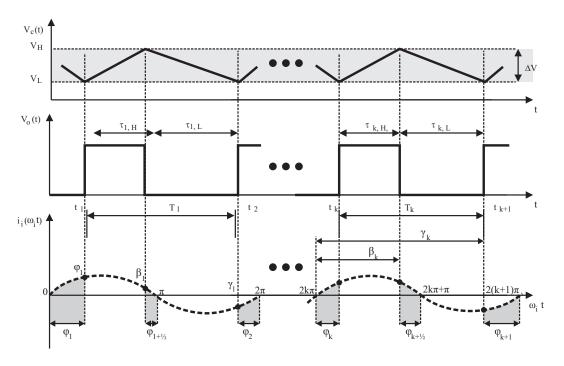

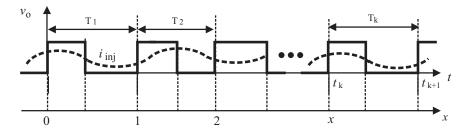

| 4.2  | Waveforms of relaxation oscillators under injection with definitions of                                                           |    |

|      | phase angles and time intervals (Duty-cycle variations have been exag-                                                            |    |

|      | gerated.)                                                                                                                         | 57 |

| 4.3  | Waveforms of $v_o$ and $i_i(t)$ . For each cycle of $v_o(t)$ , $x$ is incremented by one.                                         | 61 |

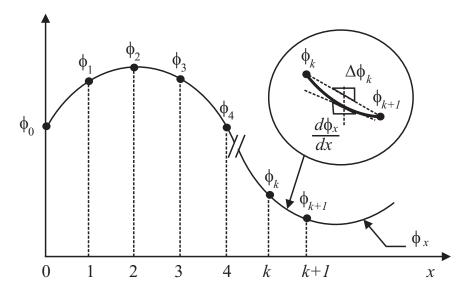

| 4.4  | Phase angle sequence                                                                                                              | 61 |

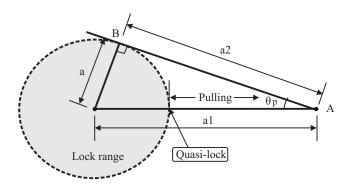

| 4.5  | Graphical representation of the pulling of oscillators under injection                                                            | 64 |

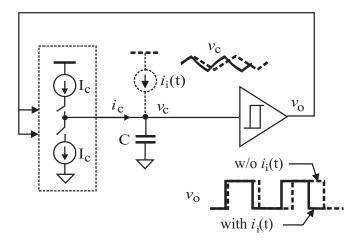

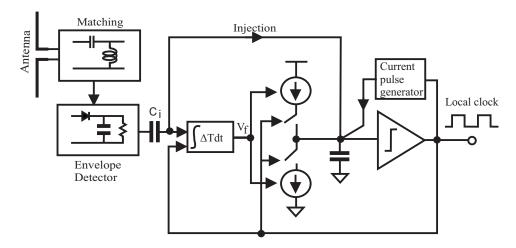

| 4.6  | Remote frequency calibration of local oscillators of passive wireless transpon-                                                   |    |

|      | ders using injection-locked phase-locked loops. The charge pump current is                                                        |    |

|      | controlled by the feedback while the direction of the charge pump current                                                         |    |

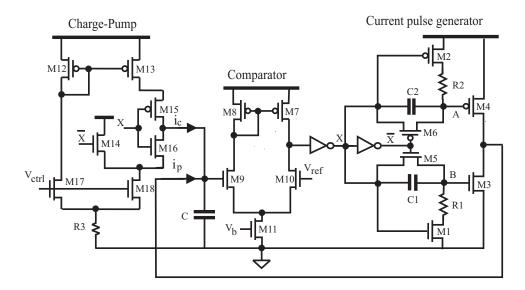

|      | is controlled by the output of the comparator                                                                                     | 72 |

| 4.7  | Proposed relaxation oscillator. $C$ is the timing capacitor. Time con-                                                            |    |

|      | stants $R_1C_1$ and $R_2C_2$ set the width of current pulses. Circuit parame-                                                     |    |

|      | ters: $W_{1,2,5,6,14-16} = 0.5 \ \mu\text{m}, \ W_{3,4,9-11} = 1.5 \ \mu\text{m}, \ W_{12,13} = 2 \ \mu\text{m}, \ W_{17,18} = 1$ |    |

|      | $\mu$ m, $L_{7,8}=1.5~\mu$ m, $L_{9-11}=1~\mu$ m, $L_{12,13}=3~\mu$ m, $L_{17,18}=8~\mu$ m, $R_{1,2}=60~{\rm K},$                 |    |

|      | $R_3$ =500 K, $C_{1,2}$ =50 fF, $C$ =50 fF, $V_{ref} = V_{DD}/2 = 0.5$ V                                                          | 75 |

|      |                                                                                                                                   |    |

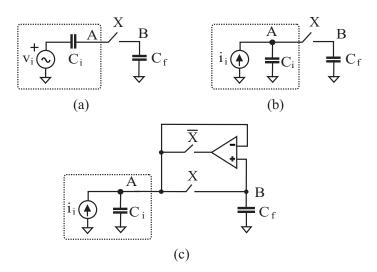

| 4.8  | (a) Envelope detector is represented by $V_i$ and $C_i$ , where $C_i$ is a dc-blocking capacitor. $C_f$ is the feedback integration capacitor. The sampling switch controlled by $X$ and $\overline{X}$ is implemented using transmission gates. (b) Norton equivalent circuit of that in sub-circuit (a). (c) Simplified circuit of mixing/integrating circuit | 76 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

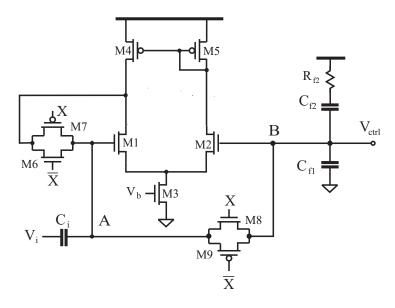

| 4.9  | Integrating feedback circuit. $W_{1-3}=1~\mu\mathrm{m},~W_{4,5}=2~\mu\mathrm{m},~W_6=3~\mu\mathrm{m},~W_7=4~\mu\mathrm{m},~W_{8,9}=5~\mu\mathrm{m},~L_{1,2,4,5}=0.36~\mu\mathrm{m},~L_3=0.72~\mu\mathrm{m},~C_{f1},~C_{f2}$ and $R_{f2}$ are for providing a proper initial control voltage                                                                     | 77 |

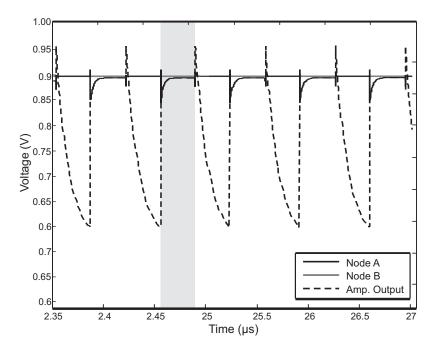

| 4.10 | Simulated voltages at the output of the amplifier, node A, and node B                                                                                                                                                                                                                                                                                           | 78 |

| 4.11 | Layout of IL-PLL. Pads are arranged as per the probes available to us                                                                                                                                                                                                                                                                                           | 79 |

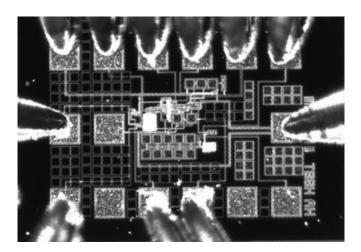

| 4.12 | Micro-photo of fabricated IL-PLL chip with probes shown                                                                                                                                                                                                                                                                                                         | 80 |

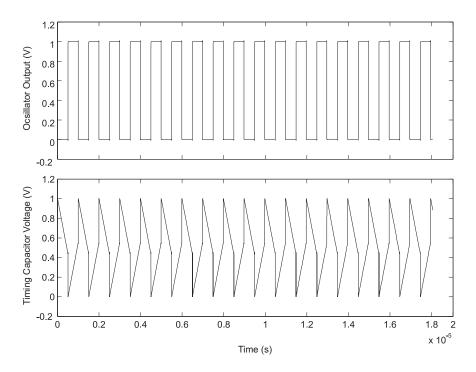

| 4.13 | Simulated (post-layout) waveform of the output voltage of comparator (top) and that of timing capacitor of proposed injection-locked relaxation oscillator with integrating feedback (bottom)                                                                                                                                                                   | 81 |

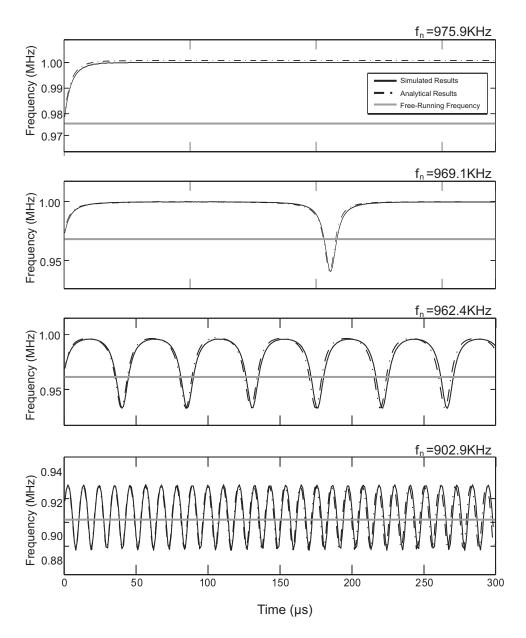

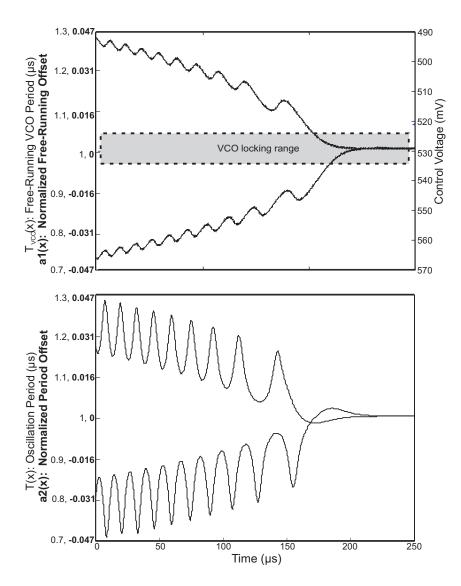

| 4.14 | Simulated effect of the injection of a sinusoidal current on the frequency of the relaxation oscillator without integrating feedback at various frequency offsets from the injection frequency. Legends: Solid line - simulation results. Dotted line - Analytical results                                                                                      | 84 |

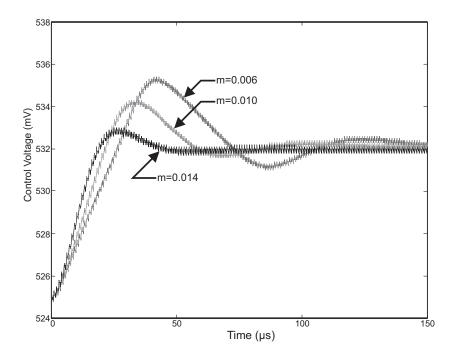

| 4.15 | Simulated effect of integral feedback on oscillator period outside the lock range. It can be seen that the feedback shifts the period towards the lock range.                                                                                                                                                                                                   | 85 |

| 4.16 | Simulated effect of the injection of sinusoidal current on the frequency of the relaxation oscillator at different offsets from injection frequency                                                                                                                                                                                                             | 86 |

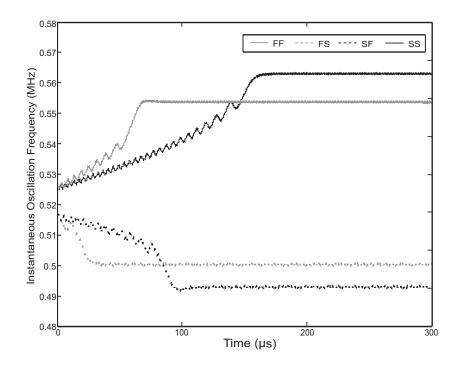

| 4.17 | Simulated control voltage of proposed injection-locked relaxation oscillator with integrating feedback at process corners. SS - slow nMOS/slow pMOS, FF - fast nMOS/fast pMOS, FS - fast nMOS/slow pMOS, and SS - slow nMOS/slow pMOS (post-layout)                                                                                                             | 87 |

| 4.18 | Simulated frequency locking of proposed injection-locked relaxation oscillator with integrating feedback at process corners (post-layout)                                                                                                                                                                                                                       | 88 |

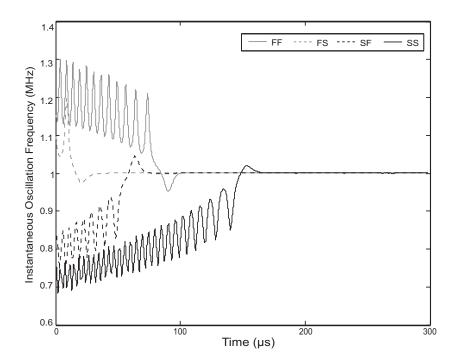

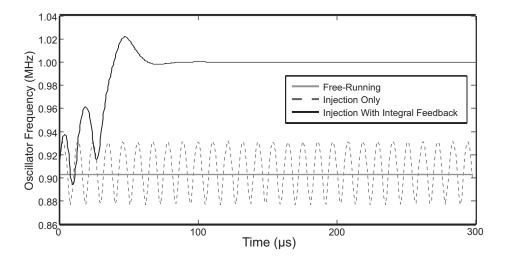

| 4.19 | Comparison of locking process of relaxation oscillator with and with-         |    |

|------|-------------------------------------------------------------------------------|----|

|      | out integrating feedback in the nominal process conditions. Legends :         |    |

|      | Light-colored solid line - Without both injection and integrating feedback.   |    |

|      | Dashed line - With injection only. Dark-colored solid line - With both        |    |

|      | injection and integrating feedback. The small variation of the frequency      |    |

|      | of the oscillator with integrating feedback after locked is due to the large  |    |

|      | relative tolerance used in simulation (reltol = $10^{-3}$ ). The variation is |    |

|      | removed when a smaller reltol is used                                         | 89 |

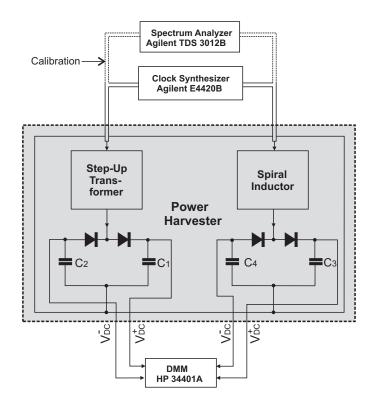

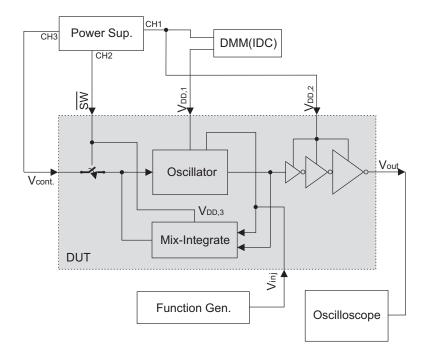

| 4.20 | Measurement setup                                                             | 89 |

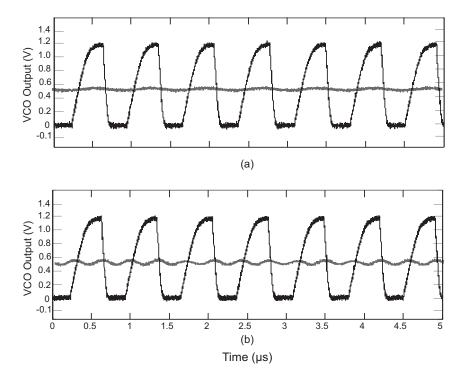

| 4.21 | Measured waveform of the output voltage (square wave) of the oscillator       |    |

|      | of the IL-PLL locked at 1.4 MHz with fundamental (top) and the second         |    |

|      | harmonic (bottom) of the locking frequency. The sinusoid is the injected      |    |

|      | signal                                                                        | 90 |

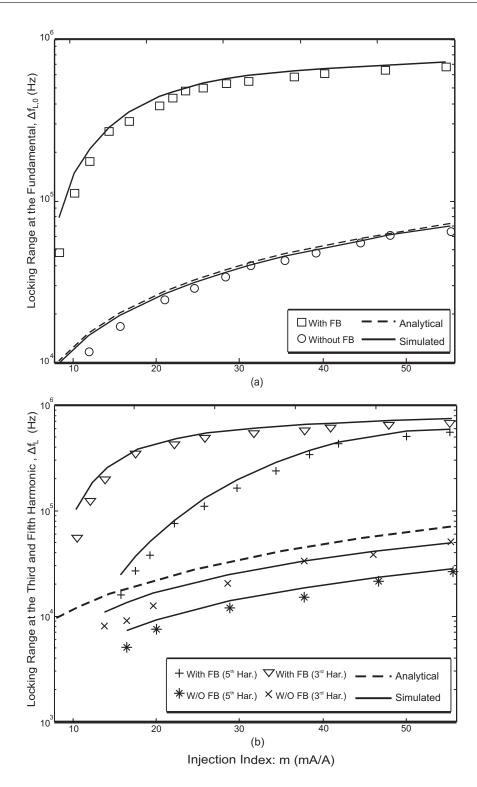

| 4.22 | Measured locking range of the oscillator and IL-PLL injected with (a) the     |    |

|      | fundamental, and (b) 3rd and 5th harmonics of the locking frequency. The      |    |

|      | results from both analytical model and simulation are also plotted for the    |    |

|      | purpose of comparison                                                         | 91 |

|      |                                                                               |    |

# List of Symbols

ADC Analog-to-Digital Converter

ADS Advanced Design Systems

AM Amplitude Modulation

ASK Amplitude-Shift Keying

BER Bit Error Rate

CAD Computer-Aided Design

CMOS Complementary Metal-Oxide Semiconductor

dBm Decibel power with respect to 1 Milliwatt

EEPROM Electronically Erasable Programmable Read-Only Memory

EM Electromagnetic

EPC Gen2 Electronic Product Code Generation 2

FF (nMOS)Fast-(pMOS)Fast

FM Frequency Modulation

FS (nMOS)Fast-(pMOS)Slow

FSK Frequency-Shift Keying

HP Hewlett-Packard

IL-PLL Injection-Locked Phase-Locked Loop

ILO Injection-Locked Oscillator

ISM Industrial Scientific Medical (radio bands)

ISO International Organization for Standardization

LC Inductor-Capacitor

LO Local Oscillator

MH Manual Handeling

MIM(-cap) Metal-Insulator-Metal (Capacitor)

nMOS n-channel Metal-Oxide Semiconductor

PLL Phase-Locked Loop

PM Phase Modulation

pMOS p-channel Metal-Oxide Semiconductor

POR Power-ON Reset

PSK Phase-Shift Keying

PVT Process (supply-)Voltage Temperature

reltol relative tolerance

RF Radio Frequency

RFID Radio Frequency Identification system

RLC Resistor-Inductor-Capacitor

SF (nMOS)Slow-(pMOS)Fast

SS (nMOS)Slow-(pMOS)Slow

TSMC Taiwan Semiconductor Manufacturing Company

${\bf TT} \hspace{0.5cm} ({\bf nMOS}) \\ {\bf Typical-(pMOS)} \\ {\bf Typical}$

UHF Ultra High Frequency

VCO Voltage-Controlled Oscillator

## Chapter 1

## Introduction

RF powered microsystems, also known as passive transponders, are critically needed in many applications such as automated payment systems, irretrievable pressure sensors in cement structures, and remote tracking devices. They have also found emerging applications in implantable electronics [61, 62, 63, 64], retinal prosthetic device [65], neuromuscular stimulation [66], wireless environme ntal monitoring [67], RFID [68], wireless medical endoscopy [9, 10], to name a few. The great advantage of a passive transponder is not having a power supply on-board. This enables it to operate indefinitely without requiring a battery exchange or recharge. Moreover, not having a power source attached to them, the transponders can be manufactured in very small sizes, making them attractive for producing implantable discrete wireless sensors.

## 1.1 Background

An RF powered transponder is a small wireless system that communicates with a nearby station called the *reader*. The reader provides the transponder with power and initial information through a wireless channel. The reader-transponder communication protocol always starts with a relatively long power-up period during which the storage capacitor of the transponder is charged to an operational level [18]. At this point, the reader may send a data request which will be acknowledged by the transponder should the requested data be available. The transponder data are usually sensor readings or identification codes. These data are processed by the reader to gain the knowledge of the transponder's

environment or identify subjects carrying the device.

#### 1.1.1 Architecture

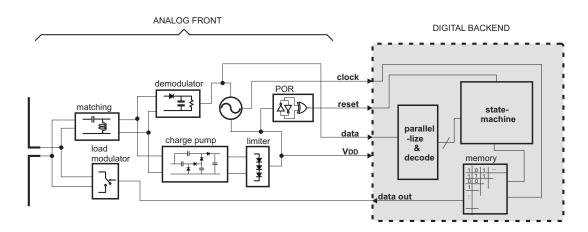

The architecture of an RF powered transponder has two majors layers: (1) an RF front and (2) baseband data units. The baseband circuits provide processing, generation and/or storage of baseband data— or any combination of the three. These units may include EEPROM's for the storage of long ID codes, ADC's for quantizing sensor readings or even microprocessors that provide basic data/signal processing at the transponder. Fig.1.1 is the block diagram of a generic transponder architecture. All these blocks will have very stringent power constraints in an RF powered microsystem. Design for lower power consumption remains the top challenge. The study of baseband circuits, however, is beyond the scope of this thesis and will not be discussed here.

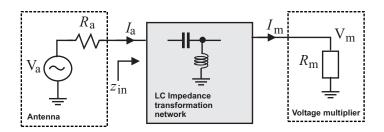

Figure 1.1: Architecture of a typical passive transponder device.

The RF front is responsible for supply of power to the chip, and the wireless data interface with the reader. Major RF front components are antenna, antenna matching network, RF-to-DC converter, modulator and demodulator. The matching network and RF-DC conversion block are some times together referred to as RF power harvester. Each block will be briefly described here, and more detailed presentation will be given in the next two chapters.

#### 1.1.2 Antenna

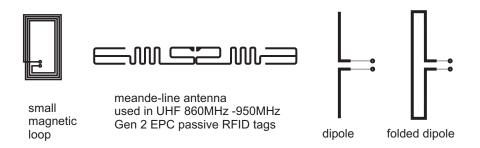

The antenna supplies the chip with power by gathering the electromagnetic wave coming from the reader. It also receives the envelope of data modulated by the reader on the same carrier that provides the power. The shape and dimensions of the antenna are determined by the carrier wavelength, channel bandwidth and polarization of the EM field. For example, lower frequency (near-field) transponders often use magnetic coils whereas dipole, folded-dipole and meander-line antennas are the popular configurations in UHF and microwave transponders. Small loop antenna is also popular geometry especially when the size of the antenna is required to be significantly smaller than the wavelength. Another advantage of the small loop antenna is its large inductive reactance which could be used to create passive voltage gain in the received signal for power harvesting purposes. Fig.1.2 shows different antennas used in RFID's (radio-frequency-identification) and passive transponders.

Figure 1.2: Popular antenna geometries for RFID's and passive transponders.

## 1.1.3 Matching Network

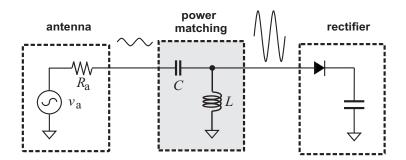

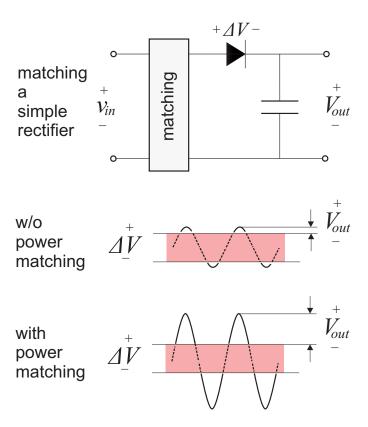

Regardless of the configuration, the impedance of the antenna has to be matched to that of the chip to ensure maximum transfer of power. This is accomplished by using a power matching block, which is a network of inductors and capacitors. Since these elements have purely imaginary impedances, ideally the power matching network does not dissipate power. However due to the conductive loss of the inductor traces, the efficiency of the matching network becomes a pressing issue especially in on-chip matching where, in addition to the conductive loss, a significant portion of the available power is consumed in the substrate. Loss of energy in the substrate is mainly due to the

radial and circular currents caused by coupling of electric and magnetic fields into the substrate. Another power-matching issue is the varying of the chip impedance under different loading conditions and proximities of the reader. These issues, however, are not as problematic. One solution to design the matching network for the worst case condition where the load consumption is the largest. Power matching will be further discussed in 3. Fig.[1.3] shows the diagram of a typical matching network placed between the antenna and the rectification block.

Figure 1.3: A typical matching network used to matching the input impedance of the rectifier to the radiation impedance of the antenna.

#### 1.1.4 Rectification

RF-to-DC conversion is implemented using rectifiers or voltage multipliers. In the higher frequencies however, due to smaller antenna aperture, the signal at the transponder is more attenuated. Most transponders operating at these frequencies use special rectifying charge-pump circuits that also boost the voltage of the signal. Such architectures are called voltage multipliers. The DC output of a voltage multiplier is normally higher than the peak AC voltage applied to it. The main challenge in the design of voltage multipliers is their conversion efficiency which is typically limited to less than 30% in most reported designs. In fact, efficiencies higher than 15% can only be achieved by use of non-standard features such as shottky diodes or silicon on insulator technologies [15, 12, 16].

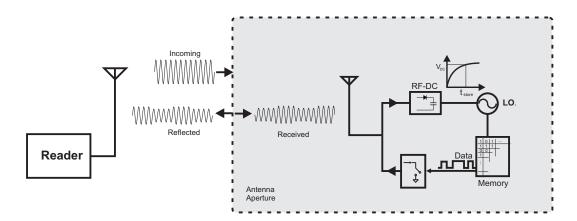

#### 1.1.5 Modulation Backscatter/Load Modulation

In passive designs, the absence of power source makes the transmission of signals from the transponder very challenging. Most designs do not allocate any DC power for RF transmission. Instead, they take advantage of a phenomenon called backscattering or backscatter modulation. Backscatter in antennas is similar to the reflection phenomenon in radars. Here, a portion of the received signal is reflected from the antenna back to the reader. The amount of power reflected and the delay of the reflected wave are determined by the input impedance seen between the two terminals of the receiver antenna. Therefore, by modulating the termination impedance (or load) of the antenna, the reflected wave is modulated. Load modulation eases the power constraints of the design to a great extent. In fact, by using this method along with other low-power design techniques, some of the recent UHF and microwave transponders have been able to lower the overall power consumption to a few microwatt, whereby increasing the operational range to up to over 12 meters, while keeping the reader's transmission powers within the ISM bands regulations[12, 16]. Fig.1.4 shows the principle of backscattering in passive transponders.

Figure 1.4: Different matching network topologies for RF power harvesting. Transformer power matching circuit is proposed in this thesis.

#### 1.1.6 Demodulation

As shown in Fig.1.1, the demodulator is located in parallel with the RF-DC conversion block, and draws a small fraction of the total RF current flowing into the chip. Due to power limitations, demodulation is usually done incoherently using an envelope detector followed by gain and signal quantizing circuits. Since the received signal must be large enough to power the device, envelope detection is well feasible in most cases.

#### 1.1.7 Wireless Link

Based on the wireless link characteristics with readers, transponders are typically categorized into inductively-coupled, electromagnetically-coupled and close-coupled. In inductive coupling, the transponder is physically located in the near field of the reader. By approximation, the near field corresponds to a distance of  $\frac{\lambda}{2\pi}$  or  $0.16\lambda$  from the reader's transmission antenna [18], where  $\lambda$  is the wavelength of the carrier signal. This type of coupling is only viable for frequency bands up to tens of Mega Hertz where the wavelengths are in the meter range. An example is the ISM bands 6.7 MHz and 13.6 MHz. Electromagnetic coupling is a full-fledged wireless link between a reader and a transponder and is used in higher frequency bands, such as UHF and microwave.

System modeling and classification of RF powered microsystems have been extensively studied in the past [18]. The objective of this thesis is to design power-efficient circuits in standard CMOS technologies for use in the RF front of passive transponders and microsensors. The particular frequencies of the circuits proposed in this thesis are the ISM UHF band (900 MHz) and Microwave band (2.45 GHz) which correspond to ISO 18000-6 and ISO 18000-4 RFID standards respectively.

#### 1.2 Motivations

The major motivation of this thesis has been to work toward overcoming the following major challenges in the design of passive wireless transponders:

#### 1.2.1 Challenges in Wireless Transfer of Power

In wireless communication systems, a mobile system must be able to receive data from its base station as well as to transmit packets of data back to the base station over a wireless channel. In active mobile systems, such as cellular phones, large energy storage devices, i.e. batteries, allow for the filtering and amplification of incoming signals as small as a few microvolts of amplitude, and peak transmission output power as large as a few watts. In passive mobile stations, such as RFID tags, however, the only source of energy available to the systems is the power of the radio-frequency waves coming from the base station. Due to the unavailability of large storage capacitors in these passive systems and the fast response requirement of these systems, it is often impractical to store energy for later usage [19]. Therefore, power constraints on design of practical passive mobile wireless systems are:

- 1. A total change of energy over each transaction is zero or negative (no source).

- 2. all the power entering the system should exit *shortly* after (no storage).

The immediate consequence of these constraints is that the power of the output signal from the transponder is directly sourced from the power of the input signal. In other words, the total power available to the transponder at every instance is the power that enters the system through the antenna within a very short time span prior that instance. The instantaneous power flow is due to the lack of large storage devices in these microsystems (the second constraint). The total amount of available power is determined by the following:

- 1. Operating frequency: determines the effective aperture of the antenna. Antenna aperture and available power are larger at low operating frequencies.

- 2. Gain of the antenna: determined by antenna efficiency and directivity.

- 3. Efficiency of RF power harvesting circuit: determined by matching and rectification efficiencies.

- 4. Operating distance: less power is available at a farther distance from the reader.

Here, we will go through each of these factors by discussing their effect of wireless power transfer as well as their limitations in improving the power transfer efficiency:

In most designs, a large operating distance desirable. Usually, all other factors are optimized so as to maximize the operation distance. In cases where a far-reaching operation range is not very critical, optimizing the first three factors leads to more available power. This in turn facilitates the design of a faster, more accurate and/or more complex back-end circuitry. Even though the use of lower operating frequencies leads to higher power availability at a given distance, antennas are much larger in size at lower frequencies. This makes them impractical for many applications such as object tracking and implantable devices.

Increasing the gain of transponder antenna requires larger and more cumbersome geometries. Increasing the directive gain also requires the transponder antenna to be in a particular physical alignment with the reader during operation; a condition that would make the device less attractive for many applications.

The efficiency of RF power harvesters is usually limited to less than 10% using standard CMOS technologies [15] and to around 30% when using off-chip matching circuit and/or more expensive non-standard features such as shottky diodes or silicon-on-insulator technology, such as the ones reported in [17, 12, 13, 16]. In addition to power efficiency, the sensitivity of the power harvester is also limited by the threshold voltage of the rectifying diodes of diode-connected devices. In other words, even when power loss of the RF-DC conversion circuit is small, the rectifier cannot operate when the voltage swing at its input is less than the voltage drop of the diodes.

The operating distance in many applications is desired to be as large so that the transponder can be operational even at farther distances from the reader. Larger operating distance, however, imposes stringent limitation on the amount of available power to the transponder as well as the efficiency of RF power harvesting. As the transponder moves farther away from the reader, the electric and magnetic field components attenuate by a factor of square of distance which means the signal received by the antenna will be much smaller resulting in smaller available power and RF-DC conversion efficiency.

#### 1.2.2 Challenges in Data Communication

In a passive transponder system, the available power is equal to the instantaneous incoming RF power. The power of the signal transmitted by the transponder is indeed less than the available power. Upon arriving at the reader, the signal from the transponder will be extremely attenuated, making the task of receiver design particularly difficult in the reader. If the exact center frequency and bandwidth of the transponder signal is not known to the receiver, the filter has to be designed to have wider passband than the actual bandwidth of the signal so as to cover all possible center frequencies and bandwidths of the transponder signal. Wider passband will result in more noise being filtered through, significantly increasing the BER of the downlink[20]. This point is illustrated graphically in Fig.1.5(b).

Fig.1.5(c) shows a special case were transponder data are modulated by a carrier prior to being backscattered. This method is called backscattering with subcarriers and provides separation between the carrier and the backscattered signal so that the reader can pick up the backscattered signal more easily. The bandwidth and the center frequency of the backscattered signal are set by the local oscillator of the transponder.

The center frequency and bandwidth of transponder signal are set by the frequency of the local oscillator of the transponder. Generating a precise frequency requires quality reference components such as high-precision resistors and capacitors. Due to the low frequency of baseband oscillators, use of the on-chip inductors is usually not practical. High precision components are either not available in standard CMOS processes or they come at an additional cost. An alternative to using high-precision components is to calibrate the frequency of the local oscillator prior to each downlink transaction by having the reader send a calibrating signal of a known duration (pulse width) or frequency. This method is a widely accepted solution to the problem of uncertain LO frequency in low-cost transponder design [20].

In designing frequency calibration for passive transponders and RFIDs, there is an inevitable trade-off between calibration speed and the power consumption of the calibration circuit. This is due to the fact that to transmit the symbol zero, the RF wave must be severely attenuated. This attenuation of the carrier signal lead to less power being available to the transponder. The duration of the attenuation is dictated by the data rate of the wireless link [12]. The amount of attenuation is dictated by the input SNR

Figure 1.5: Power spectrum of signals (a) at the transponder, (b) at the reader without subcarrier, and (c) at the reader with subcarrier.

requirement of the transponder detection circuit which is typically very high due to the small amount of power available. In the ISO-18000-C (EPC Gen2) standard—the most recent standard for UHF RFIDs—to communicate a zero, the RF signal must be attenuated by at lest 90% for at lest 50% of the symbol duration. Performing fast calibration requires sending a high-frequency reference signal to the transponder. This will lead to a sudden drop in the supply voltage.

## 1.3 Objectives

The objectives of this thesis are the following:

1. to design a highly-efficient power harvesting circuit developed entirely on-chip and using only standard CMOS technology components. Such system is critically needed for increasing the power available to the transponder, thereby increasing the operating range and/or functionalities of the system.

2. to design an ultra-low power frequency calibration system with fast operation. Such system is critically needed for establishing a reliable wireless data link without compromising the transponder response time.

#### 1.3.1 Efficient Power Harvesting

In this thesis, the objective is to increase power harvest efficiency and sensitivity by targeting the performance of the matching network. In transpodners, matching network is the passive circuit placed between the antenna and the rectifier/voltage-multiplier to match the impedance of the two blocks. Doing that, the matching network will provide passive voltage gain to the signal coming from the antenna. The increased voltage swing of the RF signal will increase both the efficieny and the sensitivity of the power harvesting circuit.

#### 1.3.2 Low-Power Fast Frequency Calibration

The main focus in design of frequency calibration system in this thesis is to improve the calibration time while maintaining the same low power consumption reported for digital calibration techniques used in [20, 62]. As discussed in Section 1.2.2, the major limitation of digital calibration techniques is the theoretical limit on the speed of the total operation. In this thesis, our effort has been to design an analog calibration techniques using the phenomenon injection locking that can speed up the process of frequency calibration while having a total power consumption in the same range as the ones reported for the digital calibration techniques.

#### 1.4 Contributions

This thesis contains the following original contributions:

• A technique to increase the available power to a passive transponder as outlined in Section 1.3 objective (1). The proposed method provides impedance matching using on-chip an transformer that provides a larger voltage gain than the conventional LC matching network, thereby providing a significantly higher conversion efficiency.

- A low-power frequency calibration technique using injection locking as outlined in Section 1.3 objective (2). This technique injects a small calibrating signal into the local oscillator of the transponder to adjust its oscillation frequency. To make the frequency adjustments permanent, an integrating feedback is simultaneously applied to correct the control voltage of the VCO. This way, the VCO frequency remains at the calibrated value when the injection signal is removed. The external feedback also increases the locking range of the VCO, reducing the minimum required amplitude of the calibrating signal.

- A comprehensive theory of injection locking and pulling in non-harmonic oscillator. The proposed time-domain analysis delivers results analogous to the frequency-domain model provided in [21, 22] for harmonic oscillators. The frequency-domain model, however, is not applicable to digital and other non-harmonic oscillators where the open-loop transfer function is non-linear. This thesis uses discrete time-domain analysis to capture the behavior of non-harmonic oscillators under injection.

- An ultra-low power low- $V_{DD}$ -sensitivity relaxation oscillator to operate under low-supply condition has been proposed. The design reduces the sensitivity of the oscillation frequency to supply voltage by increasing the hysteresis width of the open-loop circuit while using only one timing capacitor. The significance of the single-capacitor design is that the oscillator has a single injection point whereas in the dual-capacitor design ([23, 24]) the injection signal has to be steered between the two capacitors over every charge and discharge interval.

The results of the research presented in this thesis has been published at different stages of their development in the following book chapter, journals and conference proceedings:

- 1. N. Soltani and F. Yuan, "Remote frequency calibration of passive wireless microsystems" in *Integrated Bio-Microsystems: Where Electronics Meets Biology*, Ed. Kris Iniewski. Accepted, 2010.

- 2. N. Soltani and F. Yuan, "A High-Gain Power-Matching Technique for Efficient Radio-Frequency Power Harvest of Passive Wireless Microsystems," *IEEE Trans. Cir. & Sys. I: Regular Papers*, May 2010, In Press.

- 3. N. Soltani, F. Yuan "Nonharmonic Injection-Locked Phase-Locked Loops With Applications in Remote Frequency Calibration of Passive Wireless Transponders," *IEEE Trans. Cir. & Sys. I: Regular Papers*, May 2010, In Press.

- N. Soltani and F. Yuan, "A step-up transformer impedance transformation technique for efficient power harvesting of passive transponders," *Microelectronics Journal*, Vol.41, pp.75-84, 2010.

- 5. N. Soltani, F. Yuan "Low-voltage low  $V_{DD}$  sensitivity relaxation oscillator for passive wireless microsystems," *Electronics Letters*, Vol. 45, No. 21, pp. 1057 1058, Oct. 2009.

- N. Soltani and F. Yuan, "Remote frequency calibration of passive wireless microsensors and transponders using injection-locked phase-locked loop," Proc. IEEE Int'l Symp. Circuits Syst., pp.541-544, Taipei, May 2009.

- 7. N. Soltani and F. Yuan, "A high-gain impedance matching technique for efficient power harvesting of passive wireless microsystems," *Proc. IEEE Int'l Symp. Circuits Syst.*, accepted in Jan. 2010.

- N. Soltani and F. Yuan "Remote frequency calibration of passive wireless transponders using injection-locked PLL," Microsystems and Nanoelectronics Research Conference, 2009, pp. 1 4, Oct. 2009.

- N. Soltani and F. Yuan, "An autotransformer impedance transformation techniquefor efficient powe harvesting of passive transponders and wireless microsensors," Proc. IEEE Mid-West Symp. Cir. Syst., pp. 898-901, Knoxville, TN., Aug. 2008.

- F. Yuan and N. Soltani, "Design techniques for power harvesting of passive wireless microsensors," *Proc. IEEE Mid-West Symp. Circuits Syst.*, pp.289-293, Knoxville, TN. Aug. 2008.

#### 1.5 Thesis Organization

This thesis is organized as follows:

Chapter 1 provides a conceptual overview of passive wireless microsystems. Configuration of the Analog Front of passive transponders is introduced and the functionality of each block is discussed in brief. This chapter also provides some of

the main challenges currently faced in the design of passive communication systems. The objectives of the thesis is defined based on these challenges. Finally, the contributions that the research has made toward achieving those objectives is stipulated.

Chapter 2 provides the state-of-the-art reviews of the two major building blocks of interest in this thesis, namely power harvester and clock frequency calibration systems. This chapter reviews the current trends in the two areas based on the conducted literature reviews, and compares the designs based on their cost and performance.

Chapter 3 describes the proposed technique for radio frequency power harvesting using monolithic transformers. The technique is compared with RF power harvesters using LC resonators. The proposed power harvester improved RF sensitivity and power efficiency. The design is also compared with recently published designs.

Chapter 4 describes the proposed method for remote frequency calibration in passive transponders. A new theory on injection locking and pulling of non-harmonic oscillator is introduced in this chapter. The behavior of relaxation oscillators under injection is studied. The effect of adding an external integrating feedback is also studied.

Chapter 5 summarizes the thesis. The directions of future work are also outlined.

#### 1.6 Chapter Summary

In this chapter we presented an overview of passive wireless communication systems. We presented a brief introduction to passive transponder architecture and the wireless protocols for communication with the reader. Fundamental building blocks of the analog front of the passive transponders were enumerated and briefly discussed in terms of their functionality, implementation and design challenges. It was argued that one the most important areas of improvements in passive transponder systems is the RF power harvesting circuit. The power efficiency of this block is currently imposing significant limitations on the overall efficiency of the transponder systems especially in the ones developed in low-cost CMOS technologies. It was

also pointed out that a critical element is data communication between the reader and the transponder is the local oscillator which is required to provide stable oscillation frequency. Creation of such oscillation requires a frequency calibration system to be implemented on the transponder. The design of frequency calibration system is also a subject of study in this thesis.

#### Chapter 2

### A State-of-the-Art Review in Design of Power Harvesting and Clock Calibration Circuits for Passive Transponders

#### 2.1 Power Harvester Design

Radio-frequency power harvesting efficiency is determined by the efficiency of the antenna of the transponder, the quality of power matching between the antenna and the voltage multiplier for the maximum power transmission, and the power efficiency of the voltage multiplier that converts the received RF signal into a dc voltage from which microsystems are powered. The power efficiency of voltage multipliers has been frequently studied [25, 17, 15] and an in-depth review of the design techniques for voltage multipliers was provided in [28]. Although increasing the gain of the voltage multiplier improves the amount of the power of passive wireless microsystems, voltage multipliers implemented in standard CMOS technologies suffer from a low efficiency, typically less than 14%.

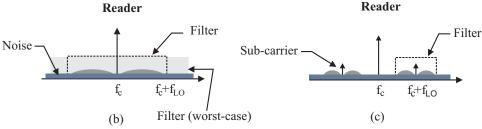

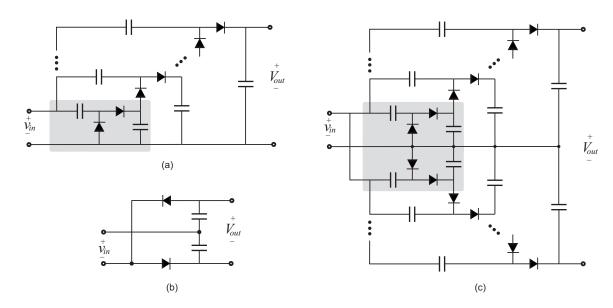

Fig.2.2 shows two of the charge-pump topologies that are widely used in passive transpodners. A major limiting factor on the efficiency of multipliers is the small

Figure 2.1: Impedance transformation network ensures maximum transfer of power by creating passive voltage gain.

voltage across the antenna. It was shown in [31] that to boost the power efficiency of the voltage multiplier, the amplitude of the voltage from antenna must be maximized. The dimension and type of the antenna of passive wireless microsystems determine the radiation resistance and the induced voltage of the antenna. The finite antenna dimension of passive wireless microsystems limits the voltage provided by the antenna. To improve the efficiency of power harvester a matching or impedance transformation network is inserted between the antenna and the rectifier/voltage multiplier, as shown in Fig.[2.1].

An impedance transformation network converts the input impedance of the voltage multiplier to the matching impedance of the antenna to ensure maximum power transfer to the voltage multiplier. In [68], a shunt inductor power-matching network between the antenna and voltage multiplier was employed, as shown in Fig.[2.3](a),

Figure 2.2: Dickson charge-pump [16] and Nakamoto's dual half-wave rectifier [17] widely used for RF signal rectification and voltage boost in transponders

to resonate out the capacitive part of the input impedance of the voltage multiplier. No attempt, however, was made to match the real part of the input impedance of the multiplier to the radiation resistance of the antenna, leaving the task of power-matching entirely to the voltage multiplier. De Vita and Iannaccone proposed a LC power-matching network, shown in Fig.[2.3](b), that consists of one floating inductor, a shunt capacitor, and a grounded inductor [19]. The grounded inductor is used to resonate out the input capacitance of the downstream voltage multiplier while the LC network provides the matching impedance and voltage gain. The LC power-matching network used by Shameli et al. consists of a grounded inductor and a floating capacitor [13]. When used with a 2-stage voltage multiplier made of low-threshold native devices, a 1 V dc output voltage was achieved at design frequency 920 MHz with -14.1 dBm input power and 500 K $\Omega$  output load. Fig.2.3 shows some of the popular topology matching networks. Fig.[2.3](a), (b) and (c) are widely used in transponders while Fig.[2.3](d) is proposed in this paper for on-chip RF power matching in transponders.

This thesis proposes an RF power harvesting circuit which uses on-chip transformers for power matching. The transformer is shown to provide significantly more voltage

Figure 2.3: (a), (b) and (c): Matching network topologies for RF power harvesting used in [12, 13] and [14] respectively. (d) Transformer power matching circuit proposed in this thesis.

gain and RF sensitivity than an LC matching circuit similar to the used in [13]. The proposed power harvester is shown, in 3, to have similar performance to the design developed using non-standard features such as Silicon-on-insulator or low- $V_T$  devices. Fig.[2.4](a) is the 3D illustration of the matching network used in [13], and Fig.[2.4](b) is the matching network proposed in this thesis.

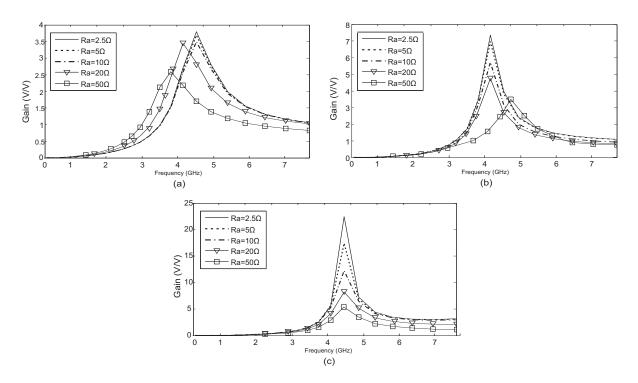

Figure 2.4: (a) RF power harvester proposed by [12, 13]. (b) Transformer power matching circuit proposed in this thesis.

#### 2.2 Current Trends in Frequency Calibration

The local oscillator of a passive wireless transponder provides the clock signal for its baseband units and determines the data rate of the backscattered signals sent by the transponder to its base station [16, 12]. In addition, it creates sub-carriers for backscatter modulation, lowering the interference of the carrier at the base station [18]. Arising from process variation, supply voltage fluctuation, and temperature drift (PVT), the local oscillator of the transponder exhibits a high level of uncertainty in its oscillation frequency [20]. Although the effect of supply voltage fluctuation and temperature variation can be compensated using compensation circuitry [36, 37], their effectiveness is largely hindered by the limited power resources

of passive wireless transponders. An alternative solution is to use an external calibrating signal sent by the base station to the transponder to adjust the oscillation frequency of the local oscillator of the transponder. Frequency calibration must be carried out frequently such that the drift of the frequency of the local oscillator is within the required tolerance. One approach to remotely calibrate the oscillation frequency of the local oscillator of transponders is to estimate the oscillator frequency of the local oscillator using a timing signal provided by the base station and adjust the frequency of the local oscillator using a digital timing feedback loop as shown in Fig.[2.5]. This approach was used by Tran and Lee in [70] where a 9-bit counter was used to estimate the period of the local oscillator. The estimate is then used to adjust the content of an 8-bit successive approximation register whose binary value scales the oscillation frequency. It was demonstrated that this technique can reduce the center frequency error to 0.4% after 8 calibration cycles. This approach, however, requires a long calibration time and complex logic circuitry.

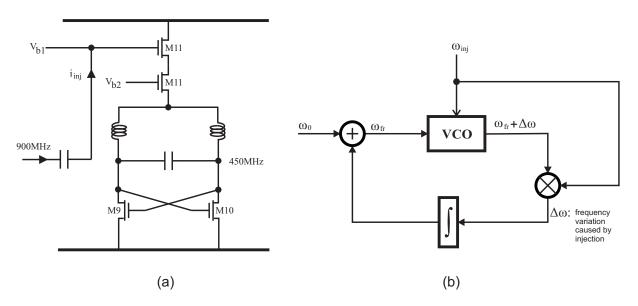

Another method of calibration the frequency of the local oscillator is injectionlocking the oscillator using a signal received from the reader. This method was employed in the transponder developed in [57] where the 900MHz carrier of the reader was used to injection lock the on-chip LC oscillator of the transponder operating at 450MHz. An in-depth study of injection-locking as a way of remotely calibrating the frequency of the oscillator of passive wireless transponders is presented in this thesis. Injection locking of harmonic oscillators has been studied extensively using both linear models [21, 22] and nonlinear models [42, 43, 44, 45, 46]. Chang et al. further showed that the injection of a low-frequency feedback signal obtained from the output of a harmonic VCO under injection to the control signal of the VCO increases the lock range and lowers the phase noise of the VCO [47, 48, 49, 50]. The analysis of the injection locking of harmonic oscillators is greatly simplified considering the bandpass characteristics of the LC tank of these oscillators. The injection locking of non-harmonic oscillators (ring oscillators and relaxation oscillators) is more complex due to the existence of multiple frequencies and has received less attention. Betancourt-Zamora et al. investigated injection-locked ring oscillator prescalers [51] by assuming that the low-pass filtering formed by the output resistance of each stage and the input capacitance of the following stage sufficiently

Figure 2.5: The "Digital Timing Feedback Loop" frequency calibration system used in [70]

suppress the frequency components higher than the frequency of the oscillator. Kinget et al. proposed precision quadrature generation using an injection-locked ring oscillator [52]. In [53], a differential-mode tail injection scheme with shunt inductance resonance was proposed for ring oscillators to achieve a wide frequency range. A phasor-domain treatment of the injection locking of ring oscillators was given in [54]. The time-domain analysis of the injection locking of ring oscillators was also conducted by Gangisani and Kinget [55, 56].

To extend the capabilities of injection-locking in calibrating the frequency of local oscillator, this thesis proposes the use of an external integrating feedback. This block, as shown in Fig.[2.6](b) accumulates the frequency variations caused by the

Figure 2.6: The "Digital Timing Feedback Loop" frequency calibration system used in [70]

injection of the reference signal. This value is then used to adjust the intrinsic frequency of the local oscillator. The steady state output frequency of the system shown in Fig.[2.6](a) is equal to the frequency of the injected signal. Also, the intrinsic (free-running) frequency of the oscillator is also equal to the injected frequency which means that the frequency of the calibrated oscillator stays at the desired value even if the injection source in removed.

#### 2.3 Chapter Summary

A state-of-the-art review of RF power harvester and remote clock frequency calibration in passive transponders was presented. In power harvesting, while most of the current designs use the Dickson charge-pump for rectification and voltage boosting, depending on the characteristics of the antenna, they use different matching networks configuration to resonate out the capacitive component of the multiplier impedance, create voltage gain, or both. In frequency calibration systems, the dig-

ital timing feedback loop was noted as the most widely used method of frequency calibration. Injection locking is another method of frequency calibration which will be studied in thesis.

#### Chapter 3

# Radio Frequency Power Harvesting in Passive Wireless Microsensors<sup>1</sup>

#### 3.1 Introduction

Passive wireless microsystems harvest their power from radio-frequency waves emitted from base stations located in the proximity. The efficiency of power harvest determines the maximum distance over which reliable links between base stations and microsystems can be established and the complexity subsequently the functionalities of the microsystems. Power harvesting efficiency is determined by the efficiency of the matching network as well as that of the voltage multiplier. The efficiency of the voltage multiplier, to a great extent, depend on the peak amplitude of the RF signal at the input such that the conversion efficiency becomes very small if the input swing is close to the voltage drop of the diodes. Therefore, a very effective method of increasing RF-DC conversion efficiency is increasing the amplitude of the RF Signal by increasing the voltage gain of the matching network.

<sup>&</sup>lt;sup>1</sup>The preliminary results of the research regarding radio frequency power harvesting has been published in IEEE conference proceedings [26, 27, 28] and the Elsvier Microelectronics journal [29]. More comprehensive research results on this subject was published in the IEEE Transactions on Circuits and Systems I - Fundamental Theory and Applications [30].

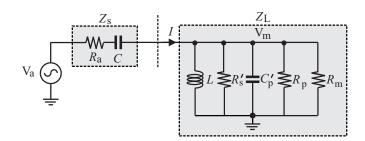

The voltage gain of LC-based power-matching approaches is limited by the low quality of spiral inductors in standard CMOS technologies. In this chapter, we propose a step-up transformer power-matching and gain-boosting technique to provide a matching impedance to the antenna and at the same time a large voltage gain such that both the power transfer from the antenna to the voltage multiplier and the power efficiency of the downstream voltage multiplier are maximized. Utilizing the unique characteristics of the low voltage and large current of the primary winding and the high voltage and low current of the secondary winding of step-up transformers, both the series and shunt losses of the transformer power-matching network are minimized simultaneously by using multiple metal layers connected using vias for the primary winding and by reducing the width of the spiral of the secondary winding. The reduction of the spiral width of the secondary winding accommodates more turns of the secondary winding in the area specified by the primary winding such that the turn ratio of the transformer subsequently the voltage of the secondary winding can be maximized. The paper is organized as the follows: Section 3.2 investigates power-matching and gain-boosting using LC networks. Design principles and constraints are developed. Section 3.3 presents the proposed step-up transformer power-matching and gain-boosting technique. A detailed analysis of the proposed approach is provided. Frequency tuning mechanisms are investigated in Section 3.4. Section 4.6 presents the measurement results of the proposed power-matching network, together with the measurement results of a LC power-matching network for comparison. Both were implemented in TSMC- $0.18\mu \text{m}$  1.8V 6-metal CMOS technology with thick metal options. The chapter is summarized in Section 3.6.

#### 3.2 LC Matching Network

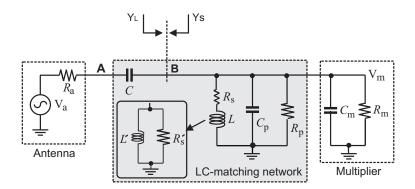

Power-matching and gain-boosting can be achieved simultaneously by inserting a passive impedance transformation network consisting of a spiral inductor and a metal-insulator-metal (MIM) capacitor between the antenna and the multiplier, as shown in Fig.3.1 [13]. The functionality of the impedance transformation network is two-fold: to provide a matching impedance to the antenna in order to max-

imize the power transmission from the antenna to the voltage multiplier at the carrier frequency, and to resonate at the carrier frequency such that the voltage at the output of the impedance transformation network is maximized. Because spiral inductors suffer from both resistive and capacitive losses, power matching, power efficiency, and voltage gain of the impedance transformation network must be considered equally.

Figure 3.1: Impedance transformation network for power matching and gain boosting.

#### 3.2.1 Power Matching

To maximize the power transfer from the antenna to the multiplier, the impedance transformation network in Fig.3.1 must be designed in such a way that  $z_{in} = R_a$ . Fig.3.2 shows a simplified schematic of a power-matching gain-boosting network using a shunt spiral inductor and a series MIM capacitor. To simplify analysis, the MIM capacitor is assumed to be ideal and is represented by an ideal capacitor C. The spiral inductor is modeled using the RLC network with  $R_s$  and  $R_p$  the series and shunt parasitic resistances and  $C_p$  the parasitic shunt capacitance. The multiplier is modeled used resistor  $R_m$  in parallel with capacitor  $C_m$ .

To facilitate analysis, the series  $R_s \sim L$  network of the inductor is replaced with the equivalent parallel  $R_s' \sim L'$  network shown in Fig.3.2 with

Figure 3.2: Power-matching and gain-boosting network using a shunt spiral inductor and a series MIM capacitor.

$$L' = L \left[ 1 + \left( \frac{R_s}{\omega L} \right)^2 \right],$$

$$R'_s = R_s \left[ 1 + \left( \frac{\omega L}{R_s} \right)^2 \right]$$

(3.1)

For practical spiral inductors,  $\omega L \gg R_s$  holds. As a result,  $L' \approx L$ . It can be shown that the matching condition for the maximum power transfer at node A can be shifted to node B. Moving the impedance matching from node A to node B greatly simplifies analysis. Because

$$Y_{L} = \frac{1}{R_{L}} + \frac{1}{R_{p}} + \frac{1}{R'_{s}} + j \left[ \omega \left( C_{P} + C_{L} \right) - \frac{1}{\omega L} \right],$$

$$Y_{s} = \frac{1}{R_{a} + \frac{1}{j\omega C}} = \frac{\omega^{2} C^{2} R_{a} + j\omega C \left[ 1 + \omega^{2} R_{a}^{2} C \right]}{1 + \omega^{2} R_{a}^{2} C^{2}},$$

(3.2)

from matching condition  $Y_L = Y_s^*$ , we have

$$Q = \sqrt{\frac{R_e}{R_a} - 1},\tag{3.3}$$

and

$$\omega_o \approx \frac{\omega_n}{\sqrt{1 + \frac{C_p'}{C}}},\tag{3.4}$$

where

$$R_e = R_s'||R_p||R_m \tag{3.5}$$

is the effective load,  $C'_p = C_m + C_p$  is the total shunt capacitance,

$$Q = \frac{1}{\omega R_a C} \tag{3.6}$$

is the quality factor of  $R_a \sim C$  network, and

$$\omega_n = \frac{1}{\sqrt{LC}} \tag{3.7}$$

is the resonance frequency of the impedance transformation network when its parasitics are not accounted for. Note that  $Q^2\gg 1$  was utilized in derivation of (3.4). Fig.3.3 shows the simplified schematic of the LC power-matching and gain-boosting network.

#### 3.2.2 Power Efficiency

The impedance transformation network is lossy due to the power dissipation of  $R'_s$  and  $R_p$ . To maximize the amount of power transferred from the antenna to the multiplier, the power loss of the impedance transformation network should be

Figure 3.3: Simplified schematic of LC-based power-matching and gain-boosting network.

minimized. The power efficiency of the impedance transformation network defined as the ratio of the power delivered to the multiplier, denoted by  $P_m$ , to the power available at the input of the impedance transformation network, denoted by  $P_{in}$ , i.e

$$\eta = \frac{P_m}{P_{in}} \bigg|_{z_{in} = R_a}$$

(3.8)

must therefore be maximized [19]. Since  $\omega L \gg R_s$  holds for spiral inductors, we have from (3.1)  $R_s' \approx \frac{(\omega L)^2}{R_s}$ . Further from (3.4) and (3.7), we have  $(\omega L)^2 = \frac{1}{\omega^2 (C + C_p')^2}$ . As a result,

$$R_s' = \frac{1}{R_s \omega^2 (C + C_p')^2}. (3.9)$$

Utilizing (3.3), (3.6), and noting  $Q\gg 1$ , we have

$$\frac{1}{\omega R_a C} \approx \sqrt{\frac{R_e}{R_a}}. (3.10)$$

Making use of (3.10), we can write (3.9) as

$$R_s' = \left[\frac{R_a}{R_s} \left(\frac{C}{C + C_p'}\right) - 1\right] (R_m || R_p). \tag{3.11}$$

It is seen from (3.11) that  $C'_p$  lowers  $R'_s$ . This is echoed with an increase in the ohmic loss of the inductor. The power efficiency of the impedance transformation network is obtained by

$$\eta = \frac{P_m}{P_{in}} = \frac{\frac{V_m^2}{R_m}}{\frac{V_m^2}{R_e}} = \frac{R_e}{R_m}.$$

(3.12)

Since

$$\frac{1}{R_e} = \frac{1}{R_s'} + \frac{1}{R_p} + \frac{1}{R_m},\tag{3.13}$$

making use of (3.11), we can write (3.13) as

$$\frac{1}{R_e} = \left(\frac{1}{R_p} + \frac{1}{R_m}\right) \frac{\frac{R_a}{R_s} \left(\frac{C}{C + C_p'}\right)^2}{\frac{R_a}{R_s} \left(\frac{C}{C + C_p'}\right)^2 - 1}.$$

(3.14)

Substituting (3.14) into (3.12) yields

$$\eta = \frac{1 - \frac{R_s}{R_a} \left( 1 + \frac{C_p'}{C} \right)}{1 + \frac{R_m}{R_p}}.$$

(3.15)

Since  $\frac{R_m}{R_p} \ll 1$  typically holds, making use of  $\frac{1}{1+x} \approx 1-x$  when  $|x| \ll 1$ , we can write (3.15) as

$$\eta \approx 1 - \frac{R_s}{R_a} \left( 1 + \frac{C_p'}{C} \right) - \frac{R_m}{R_p}. \tag{3.16}$$

It is evident from (3.16) that the power efficiency of the impedance transformation network is less than 100% due to the non-zero parasitic series resistance  $R_s$ , the finite parasitic shunt resistance  $R_p$ , and the shunt capacitance  $C'_p$ . To improve  $\eta$ ,  $R_s$  and  $C'_p$  should be minimized while  $R_p$  should be maximized. In other words, the shunt-peaking spiral inductor should be as ideal as possible.

#### 3.2.3 Voltage Gain