### Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2012

# High-Power Multimodular Matrix Converters and Modulation

Jiacheng Wang Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

### **Recommended** Citation

Wang, Jiacheng, "High-Power Multimodular Matrix Converters and Modulation" (2012). Theses and dissertations. Paper 1696.

This Dissertation is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

# HIGH-POWER MULTIMODULAR MATRIX CONVERTERS AND MODULATION

By

### **Jiacheng Wang**

B. Sc., Shanghai Jiao Tong University, Shanghai, China, 2001M. Sc., Shanghai Jiao Tong University, Shanghai, China, 2005

A dissertation presented to Ryerson University in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2012

© Jiacheng Wang, 2012

### **Author's Declaration**

I hereby declare that I am the sole author of this dissertation. This is a true copy of the dissertation, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my dissertation may be made electronically available to the public.

# High-Power Multimodular Matrix Converters and Modulation

Jiacheng Wang

Doctor of Philosophy Electrical and Computer Engineering Ryerson University, Toronto, 2012

### Abstract

High-power multimodular matrix converters (MMMCs) comprising multiple threephase to single-phase matrix converter modules have emerged as a viable topology candidate for medium-voltage adjustable speed drives. As a combination of direct power conversion and cascaded multilevel structure, the MMMCs inherit features such as elimination of dc capacitors, four quadrant operation capability, employment of lowvoltage devices only, and superior output waveform quality under a limited device switching frequency. Due to their particular topological structure, modulation scheme design for the MMMCs is not straightforward and complicated. The presented work is mainly focused on development of suitable modulation schemes for the MMMCs. Several viable schemes as well as their corresponding switching patterns are proposed and verified by both simulation and experimental results.

In order for the MMMCs to produce sinusoidal waveforms at both input and output ac terminals, a direct transfer matrix based modulation scheme is presented. It is revealed that a suitable modulation strategy for the MMMCs should aim at fabricating the total input

current on the primary side of the isolation transformer. For topologies with more than two modules in cascade on each output phase, switching period displacement is necessary among modules to generate multilevel output waveforms.

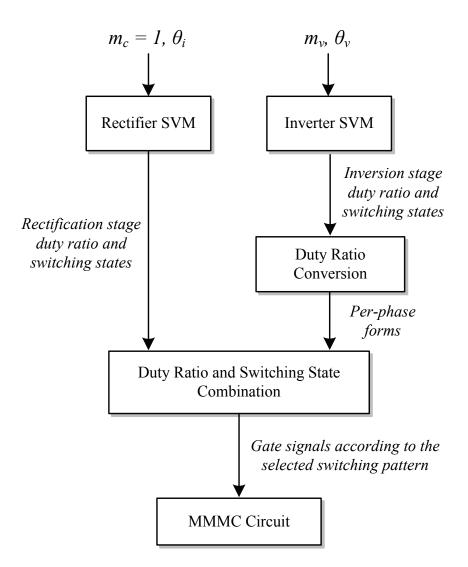

An indirect space vector based modulation scheme for the MMMCs is developed. With a few presumptions satisfied and viewed from a certain perspective, the MMMCs can still be modeled indirectly and be divided into fictitious rectifier and inverter stages. Therefore, space vector modulation methods can be independently applied to both stages for duty ratio calculation, before the results are converted and combined for determining per-phase output pulses. A new output switching pattern providing improved harmonic performance is also proposed.

A novel modulation scheme based on diode rectifier emulation and phase-shifted sinusoidal pulse-width modulation is proposed. The method sacrifices input power factor adjustment, but enables the use of an indirect module construction leading to significantly reduced device count and complexity. Strategy for reducing additional switchings caused by input voltage ripples is also implemented and explained.

In addition to simulation verifications, all the proposed schemes are further tested experimentally on a low-voltage prototype built in the lab. Details about the prototype implementation are introduced.

V

### Acknowledgement

My foremost appreciation goes to my dissertation advisor, Professor Bin Wu, for his continuous and invaluable guidance, support, and patience throughout the course of this work. I was fortunate enough to have worked with him over the last several years.

I am very grateful to Professor David Xu for his tremendous help on the experimental construction of the lab setup, and for the many interesting discussions. Thanks are extended to all the fellow colleagues who have worked at LEDAR during the past years. The time and friendship we shared are truly memorable.

Special thanks to my dear wife and parents for their constant understanding and support, without which this couldn't have been possible.

Financial supports from Professor Bin Wu and Ryerson University are greatly acknowledged.

# **Table of Contents**

| Abstract                                                   | iv  |

|------------------------------------------------------------|-----|

| Acknowledgement                                            | vi  |

| Table of Contents                                          | vii |

| List of Figures                                            | X   |

| List of Tables                                             | XV  |

| Glossary of Acronyms                                       | xvi |

| Chapter 1 Introduction                                     | 1   |

| 1.1 Technical Requirements for MV Drive Converters         | 4   |

| 1.2 Overview of Modern MV Drive Converter Topologies       | 6   |

| 1.2.1 ac-dc-ac Indirect Converters                         | 7   |

| 1.2.2 ac-ac Direct Converters                              | 21  |

| 1.3 Dissertation Objectives                                |     |

| 1.4 Dissertation Outline                                   | 27  |

| Chapter 2 Direct Modulation Scheme for the MMMC Topologies | 29  |

| 2.1 Topological Structure of the MMMCs                     |     |

| 2.1.1 Three-Phase to Single-Phase (3 x 2) MC Module        |     |

| 2.1.2 Three-Module Multimodular Matrix Converter-I         |     |

| 2.1.3 Nine-Module Multimodular Matrix Converter-II         |     |

| 2.2 Direct Modulation Scheme for the MMMCs                 |     |

| 2.2.1 Transfer Function Matrix Derivation                  |     |

| 2.2.2 Switching Pattern                                               | 41   |

|-----------------------------------------------------------------------|------|

| 2.2.3 Switching Period Displacement for MMMC-II                       | 42   |

| 2.3 Simulation Results                                                | 44   |

| 2.3.1 Simulation Results for MMMC-I                                   | 45   |

| 2.3.2 Simulation Results for MMMC-II                                  | 48   |

| 2.4 Experimental Verification                                         | 51   |

| 2.5 Summary                                                           | . 57 |

| Chapter 3 Indirect Space Vector Based Modulation Scheme for the MMMCs | 58   |

| 3.1 Indirect Modeling for the MMMCs                                   | 59   |

| 3.2 CSR SVM for Rectifier Stage Calculations                          | 63   |

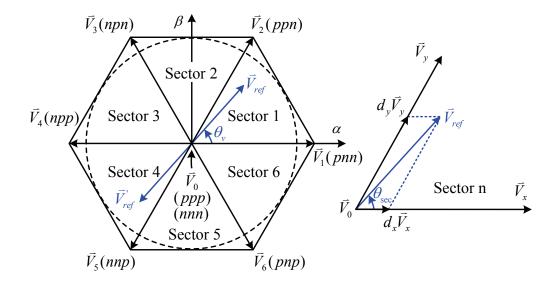

| 3.3 Two-level VSI SVM for Inverter Stage Calculations                 | 65   |

| 3.3.1 Duty Ratio Calculation                                          | 65   |

| 3.3.2 Duty Ratio Conversion                                           | 68   |

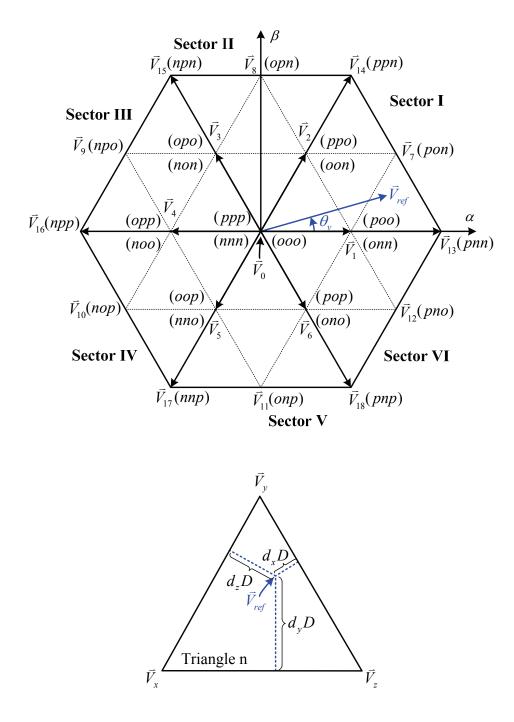

| 3.4 Three-level VSI SVM for Inverter Stage Calculations               | 70   |

| 3.4.1 Duty Ratio Calculation                                          | 70   |

| 3.4.2 Duty Ratio Conversion                                           | 74   |

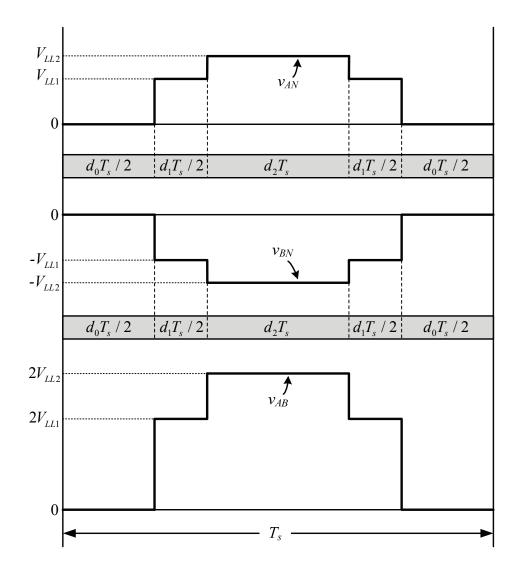

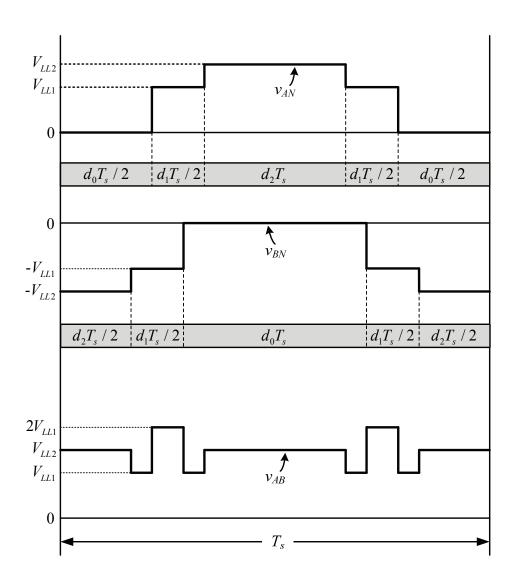

| 3.5 Switching State Combination                                       | 75   |

| 3.6 Switching Pattern Design                                          | 77   |

| 3.7 Simulation Results                                                | 79   |

| 3.7.1 Simulation Results for MMMC-I                                   | 81   |

| 3.7.2 Simulation Results for MMMC-II                                  | 84   |

| 3.8 Experimental Verification                                         | 88   |

| 3.9 Summary                                                           | 94   |

| Chapter 4 Modulation Using DFE Emulation and Phase-Shifted SPWM       | 96   |

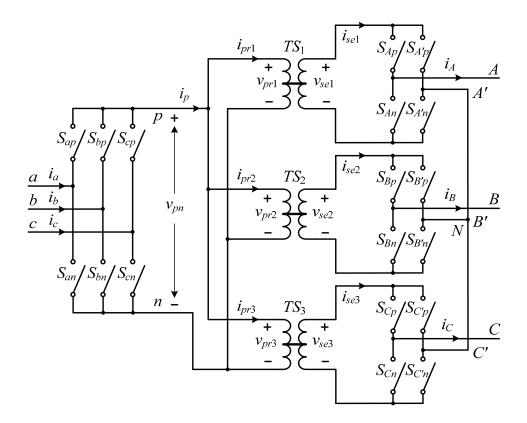

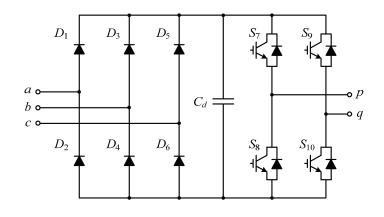

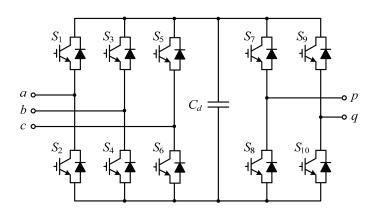

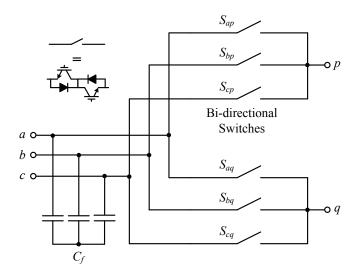

| 4.1 3 x 2 Converter Module Structures                                      | 97  |

|----------------------------------------------------------------------------|-----|

| 4.2 Modulation Scheme                                                      | 102 |

| 4.2.1 Diode Front-End Emulation for the Rectifier Stage                    | 102 |

| 4.2.2 Phase-Shifted SPWM for the Inverter Stage                            | 103 |

| 4.2.3 Mathematical Derivation of Input and Output Quantities               | 104 |

| 4.2.4 Effect of the 18-Pulse Phase-shifting Transformer                    | 110 |

| 4.2.5 Gate Signal Mapping for Direct MC Module                             | 112 |

| 4.2.6 Reduction of Additional Switchings Caused by Input Voltage Ripples . | 113 |

| 4.3 Simulation Results                                                     | 116 |

| 4.4 Experimental Verification                                              | 119 |

| 4.5 Summary                                                                | 123 |

| Chapter 5 Experimental Platform Implementation                             | 125 |

| 5.1 Construction of 3 x 2 MC Power Modules                                 | 128 |

| 5.2 Voltage and Current Measurement                                        | 131 |

| 5.3 Commutation Control of the Bidirectional Switches                      | 132 |

| 5.4 Module Synchronization, Communication and Protection                   | 136 |

| 5.5 Summary                                                                | 137 |

| Chapter 6 Conclusions                                                      | 138 |

| 6.1 Main Contributions and Conclusions                                     | 139 |

| 6.2 Suggested Future Work                                                  | 141 |

| Appendix I Per-Unit System Calculation                                     | 142 |

| References                                                                 | 143 |

# **List of Figures**

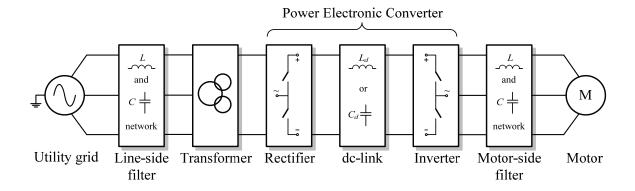

| Fig. 1-1          | General structure of a medium-voltage drive system.                                     | 4  |

|-------------------|-----------------------------------------------------------------------------------------|----|

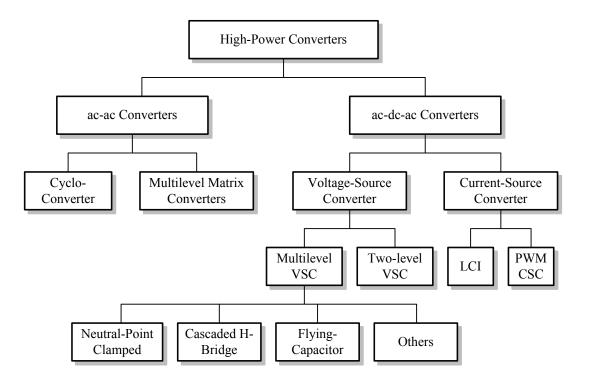

| Fig. 1 <b>-</b> 2 | Classification of high-power converters for MV drive                                    | 7  |

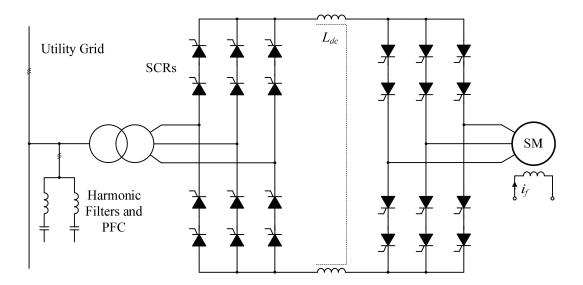

| Fig. 1-3          | LCI based MV drive for synchronous machine load.                                        | 8  |

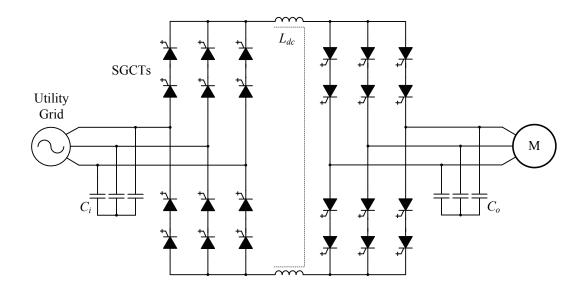

| Fig. 1 <b>-</b> 4 | Configuration of PWM CSC based MV drive system                                          | 9  |

| Fig. 1-5          | NPC converter based MV drive                                                            | 14 |

| Fig. 1-6          | A seven-level CHB converter based MV drive.                                             | 15 |

| Fig. 1-7          | Four-level flying capacitor converter (output phase A)                                  | 17 |

| Fig. 1-8          | NPC/H-bridge converter based MV drive.                                                  | 18 |

| Fig. 1-9          | Five-level active NPC converter (output phase <i>A</i> ).                               | 19 |

| Fig. 1-10         | 0 Modular multilevel converter.                                                         | 20 |

| Fig. 1-1          | 1 Three-phase to three-phase conventional MC.                                           | 23 |

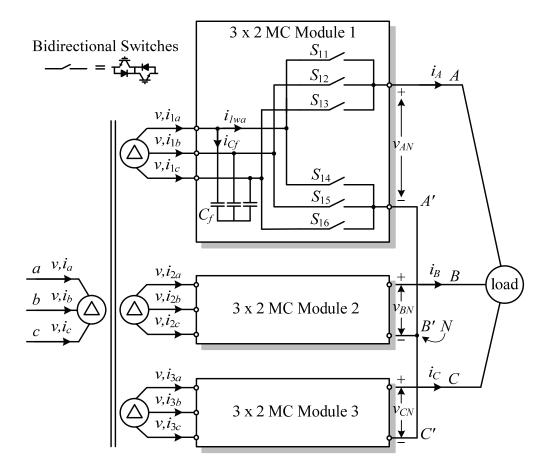

| Fig. 2-1          | Simplified diagram of a 3 x 2 MC module.                                                | 31 |

| Fig. 2-2          | Simplified circuit diagram of three-module MMMC-I                                       | 33 |

| Fig. 2-3          | Simplified circuit diagram of nine-module MMMC-II.                                      | 34 |

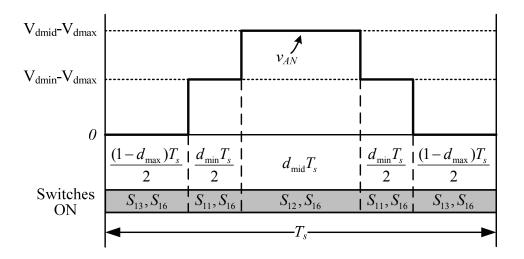

| Fig. 2-4          | Example of switching pattern in a complete switching period                             | 42 |

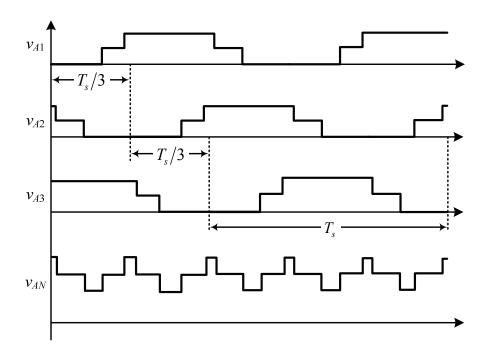

| Fig. 2-5          | Displaced switching periods and resultant phase voltage waveforms                       | 43 |

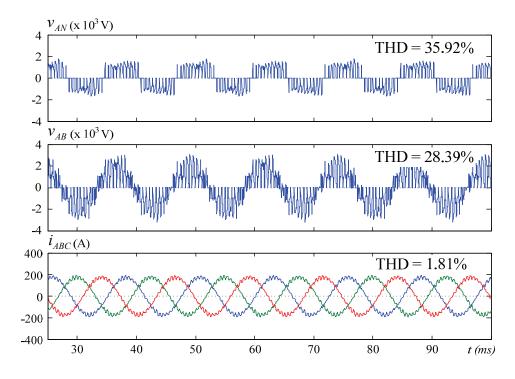

| Fig. 2-6          | Simulated output voltage and current waveforms of MMMC-I ( $f_o = 40$ Hz, $m_a = 0.9$ ) | 46 |

| Fig. 2-7          | Simulated output voltage and current waveforms of MMMC-I ( $f_o = 80$ Hz, $m_a = 0.9$ ) | 46 |

| Fig. 2-8          | Simulated input current waveforms of MMMC-I ( $f_o = 40$ Hz, $m_a = 0.9$ ).             | 47 |

| Fig. 2-9 Simulated output voltage and current waveforms of MMMC-II ( $f_o = 40$ Hz, $m_a = 0.9$ )       |  |

|---------------------------------------------------------------------------------------------------------|--|

| Fig. 2-10 Simulated output voltage and current waveforms of MMMC-II ( $f_o = 80$ Hz, $m_a = 0.9$ )      |  |

| Fig. 2-11 Simulated input current waveforms of MMMC-II ( $f_o = 40$ Hz, $m_a = 0.9$ )                   |  |

| Fig. 2-12 Adjustable input power factor of MMMC-II ( $f_o = 40$ Hz, $m_a = 0.9$ )                       |  |

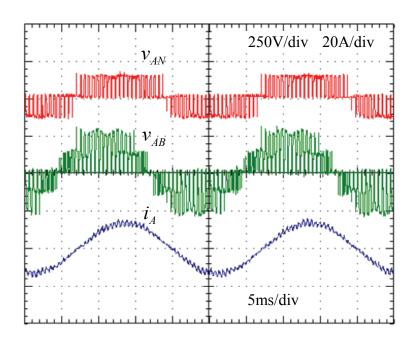

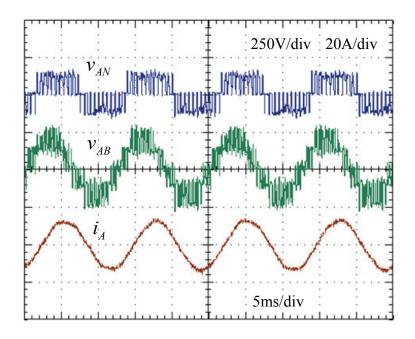

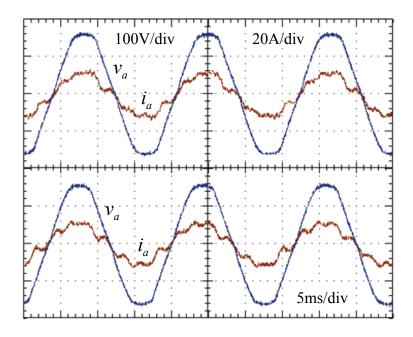

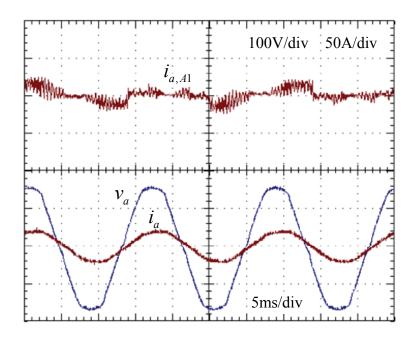

| Fig. 2-13 Experimental output voltage and current waveforms of MMMC-I ( $f_o = 40$ Hz, $m_a = 0.9$ )53  |  |

| Fig. 2-14 Experimental output voltage and current waveforms of MMMC-I ( $f_o = 80$ Hz, $m_a = 0.9$ )54  |  |

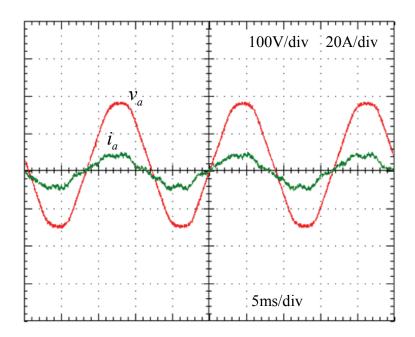

| Fig. 2-15 Experimental grid voltage and current waveforms of MMMC-I ( $f_o = 40$ Hz, $m_a = 0.9$ )      |  |

| Fig. 2-16 Experimental output voltage and current waveforms of MMMC-II ( $f_o = 40$ Hz, $m_a = 0.9$ )55 |  |

| Fig. 2-17 Experimental output voltage and current waveforms of MMMC-II ( $f_o = 80$ Hz, $m_a = 0.9$ )56 |  |

| Fig. 2-18 Experimental grid voltage and current waveforms of MMMC-II ( $f_o = 40$ Hz, $m_a = 0.9$ )     |  |

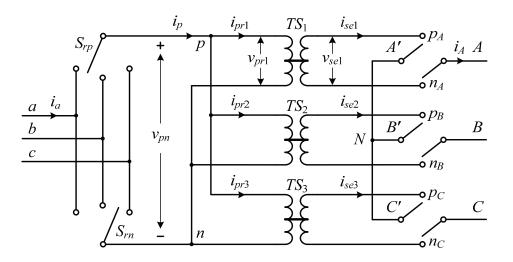

| Fig. 3-1 Simplified diagram of three-module MMMC-I                                                      |  |

| Fig. 3-2 Indirect model for MMMC-I using the fictitious dc concept                                      |  |

| Fig. 3-3 Indirect model for MMMC-I with single-pole single-throw switches                               |  |

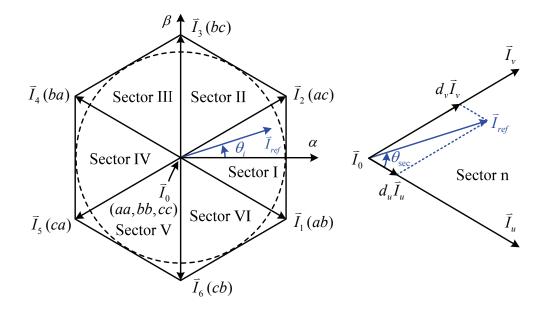

| Fig. 3-4 CSR SVM for rectifier stage current synthesis                                                  |  |

| Fig. 3-5 Two-level VSI SVM for inverter stage voltage synthesis                                         |  |

| Fig. 3-6 Three-level VSI SVM for inverter stage voltage synthesis                                       |  |

| Fig. 3-7 Output switching pattern I                                                                     |  |

| Fig. 3-8 Output switching pattern II                                                                    |  |

| Fig. 3-9 Functional block diagram of the indirect modulation scheme implementation                      |  |

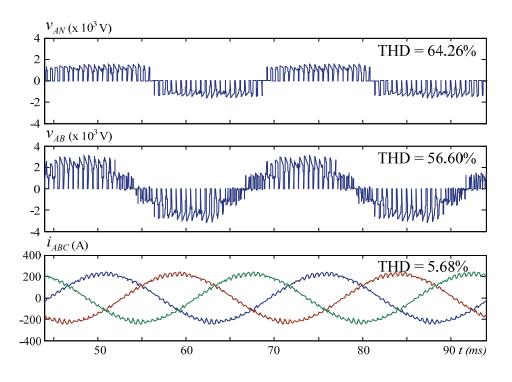

| Fig. 3-10 Simulated output voltage and current waveforms of MMMC-I (Pattern I, $f_o = 40$ Hz, $m_a$     |  |

| = 0.9)                                                                                                  |  |

| Fig. 3-11 Simulated output voltage and current waveforms of MMMC-I (Pattern II, $f_o = 40$ Hz, $m_a$    |  |

| = 0.9)                                                                                                  |  |

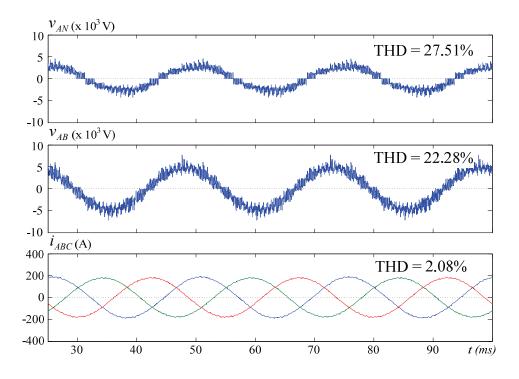

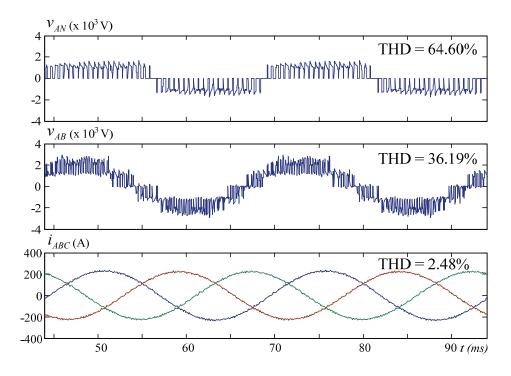

| Fig. 3-12 Simulated output voltage and current waveforms of MMMC-I (Pattern II, $f_o = 80$ Hz, $m_a = 0.9$ ).        | 83  |

|----------------------------------------------------------------------------------------------------------------------|-----|

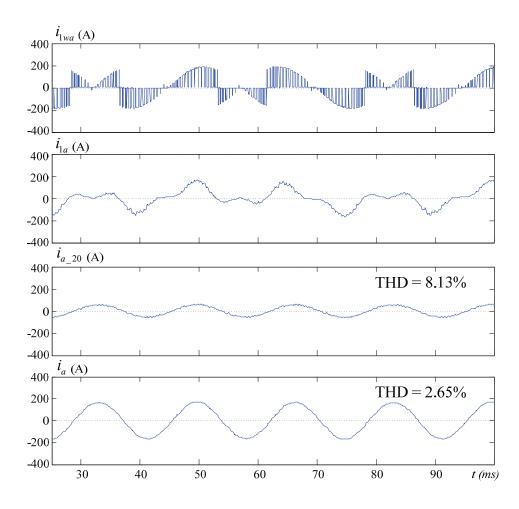

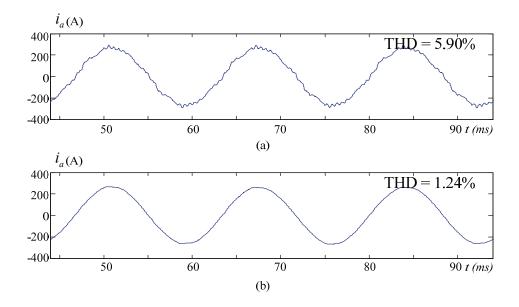

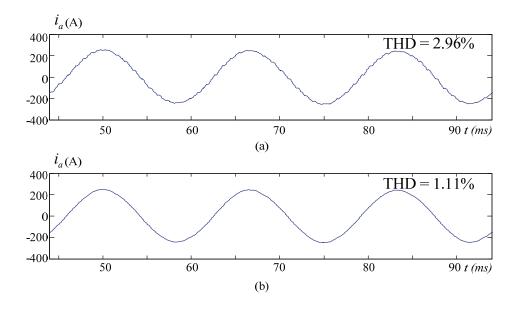

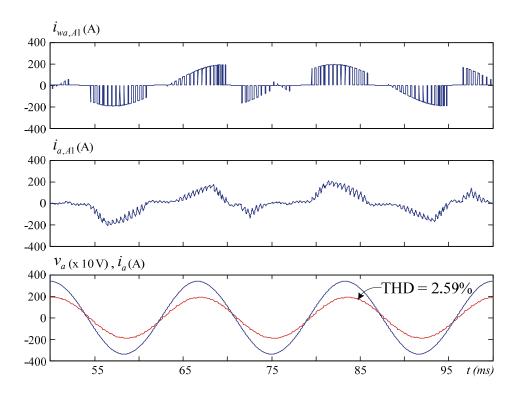

| Fig. 3-13 Simulated input current waveforms of MMMC-I (a) Pattern I. (b) Pattern II. ( $f_o = 40$ Hz, $m_a = 0.9$ ). |     |

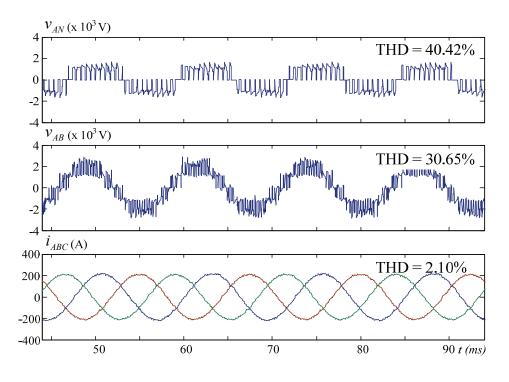

| Fig. 3-14 Simulated output voltage and current waveforms of MMMC-II (Pattern I, $f_o = 40$ Hz, $m_a = 0.9$ ).        | 85  |

| Fig. 3-15 Simulated output voltage and current waveforms of MMMC-II (Pattern II, $f_o = 40$ Hz, $m_a = 0.9$ ).       | 85  |

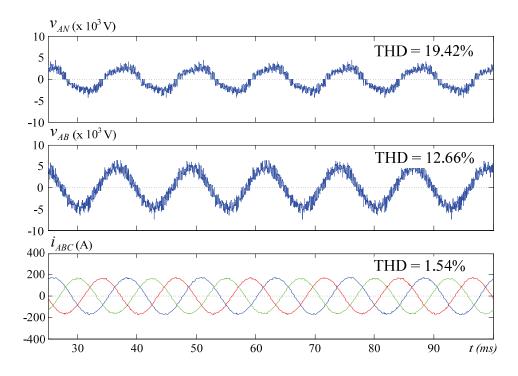

| Fig. 3-16 Simulated output voltage and current waveforms of MMMC-II (Pattern II, $f_o = 80$ Hz, $m_a = 0.9$ ).       |     |

| Fig. 3-17 Simulated input current waveforms of MMMC-II (a) Pattern I. (b) Pattern II. ( $f_o = 40$ Hz,               |     |

| $m_a = 0.9$ )<br>Fig. 3-18 Adjustable input power factor of MMMC-II (Pattern II, $f_o = 40$ Hz, $m_a = 0.9$ )        |     |

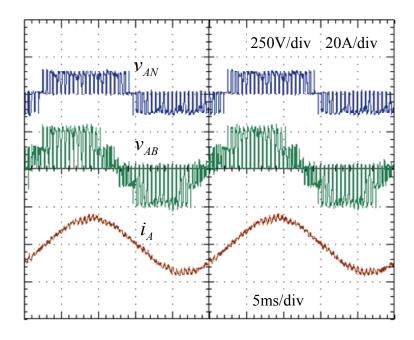

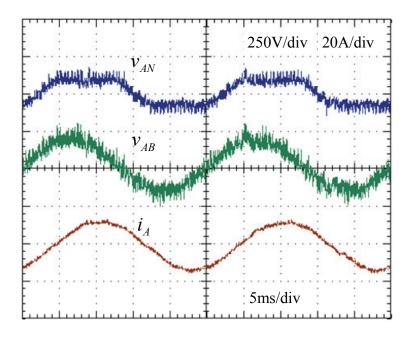

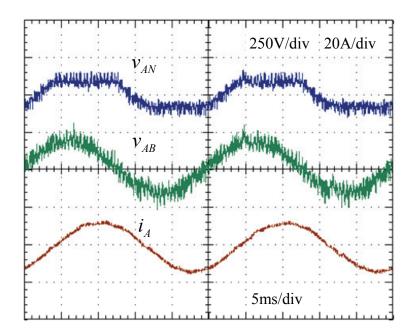

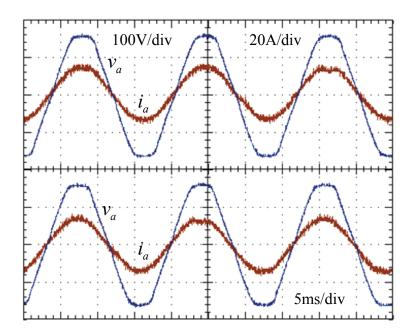

| Fig. 3-19 Experimental output voltage and current waveforms of MMMC-I (Pattern I, $f_o = 40$ Hz,<br>$m_a = 0.9$ ).   | 89  |

| Fig. 3-20 Experimental output voltage and current waveforms of MMMC-I (Pattern II, $f_o = 40$ Hz, $m_a = 0.9$ ).     | 89  |

| Fig. 3-21 Experimental output voltage and current waveforms of MMMC-I (Pattern II, $f_o = 80$ Hz, $m_a = 0.9$ ).     | 90  |

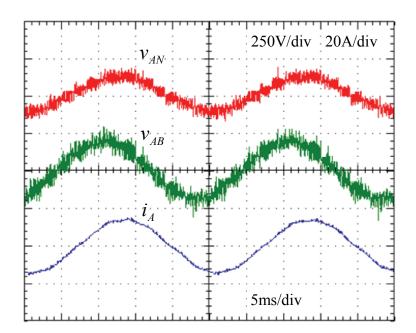

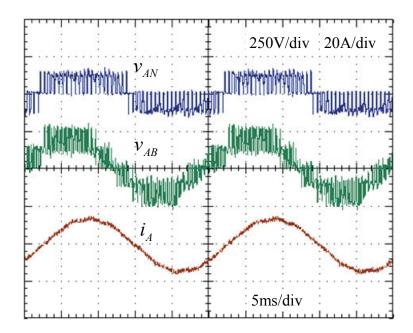

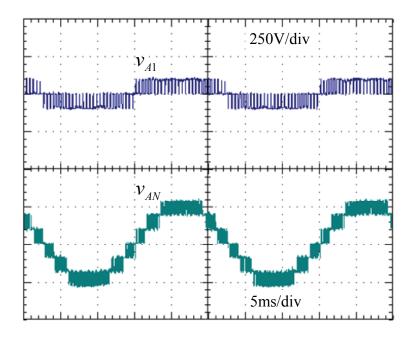

| Fig. 3-22 Experimental output voltage and current waveforms of MMMC-II (Pattern I, $f_o = 40$ Hz, $m_a = 0.9$ )      |     |

| Fig. 3-23 Experimental output voltage and current waveforms of MMMC-II (Pattern II, $f_o = 40$ Hz, $m_a = 0.9$ ).    |     |

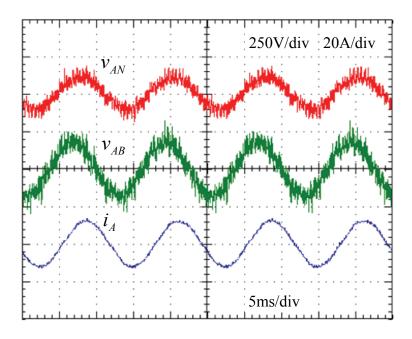

| Fig. 3-24 Experimental output voltage and current waveforms of MMMC-II (Pattern II, $f_o = 80$ Hz,<br>$m_a = 0.9$ ). |     |

| $m_a = 0.7 j.$                                                                                                       | ) 4 |

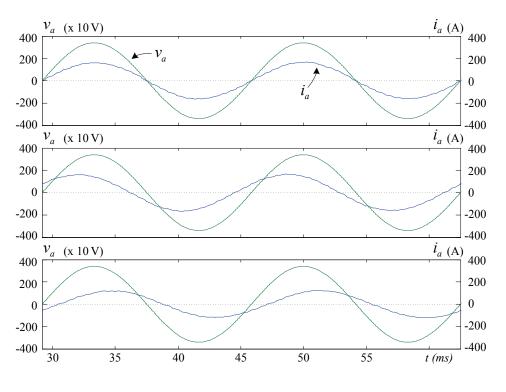

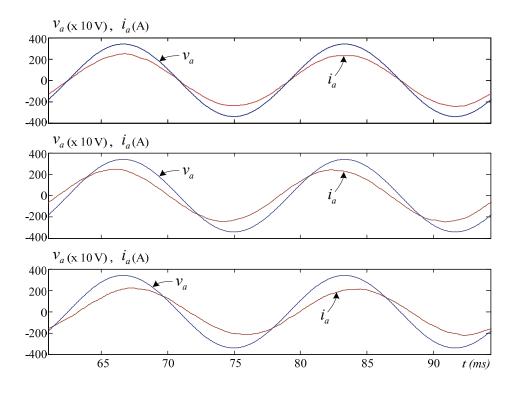

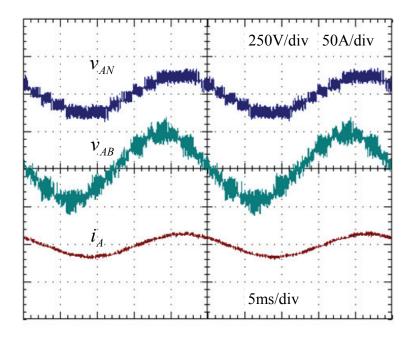

| Fig. 3-25 Experimental input voltage and current waveforms of MMMC-I (Pattern I and II, $f_o = 40$        |

|-----------------------------------------------------------------------------------------------------------|

| Hz, $m_a = 0.9$ )                                                                                         |

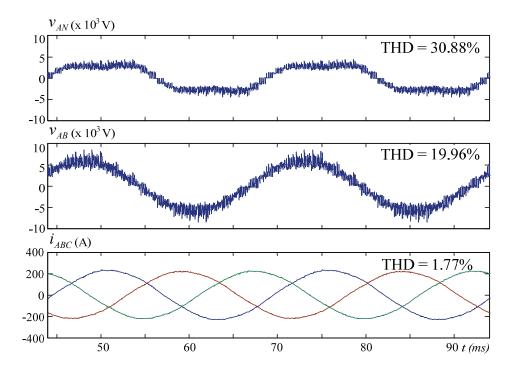

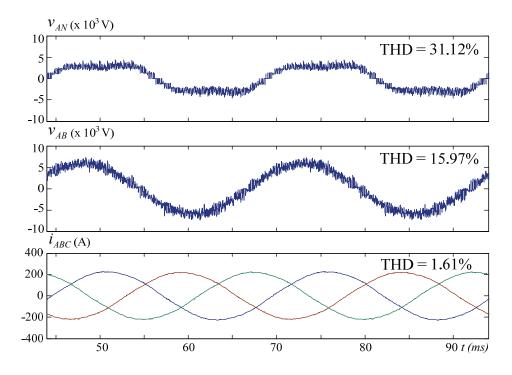

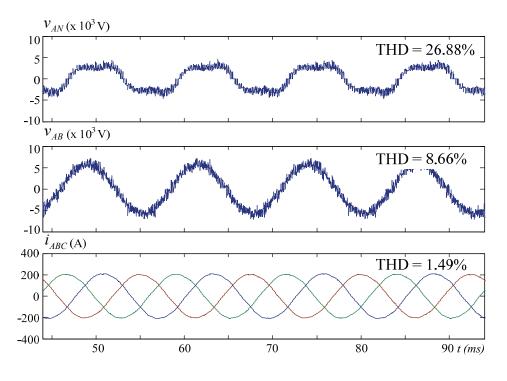

| Fig. 3-26 Experimental input voltage and current waveforms of MMMC-II (Pattern I and II, $f_o = 40$       |

| Hz, $m_a = 0.9$ )                                                                                         |

| Fig. 3-27 Experimental input waveforms of MMMC-II showing adjustable power factor (Pattern II,            |

| $f_o = 40$ Hz, $m_a = 0.9$ )                                                                              |

| Fig. 4-1 Cascaded converter structure with nine power modules                                             |

| Fig. 4-2 Power module construction for (a) Non-regenerative CHB. (b) Regenerative CHB. (c)                |

| MMMC                                                                                                      |

| Fig. 4-3 MMMC leg of output phase A with indirect MC modules                                              |

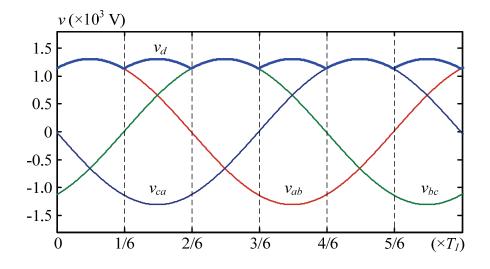

| Fig. 4-4 Ideal rectifier side voltage waveforms in an indirect MC module                                  |

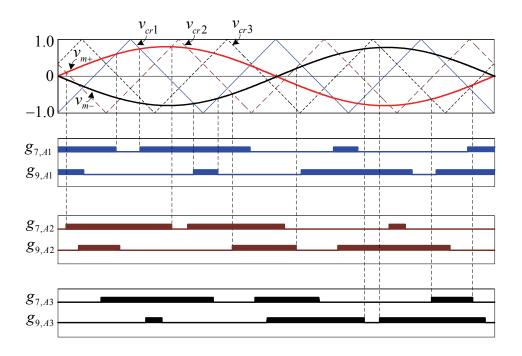

| Fig. 4-5 Inverter stage gate signals generated by phase-shift modulation                                  |

| Fig. 4-6 Ideal phase A output voltages without phase shifts in the transformer secondary windings110      |

| Fig. 4-7 Ideal phase A output voltages with phase shifts in the transformer secondary windings            |

| Fig. 4-8 Additional rectifier stage switchings caused by input voltage ripples. (a) Without filter. (b)   |

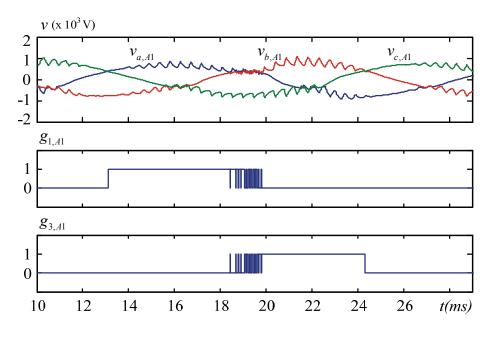

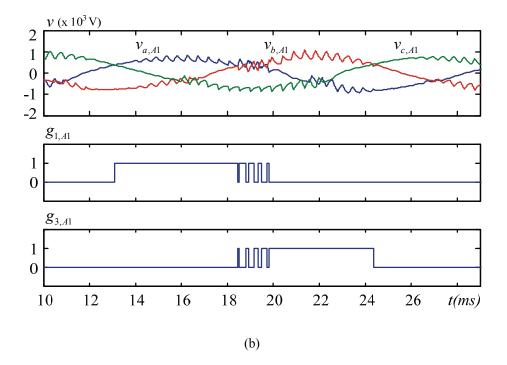

| With filter applied                                                                                       |

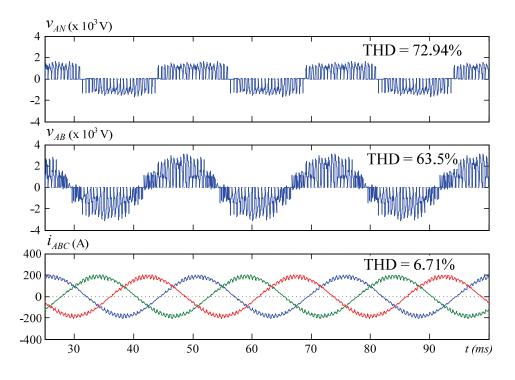

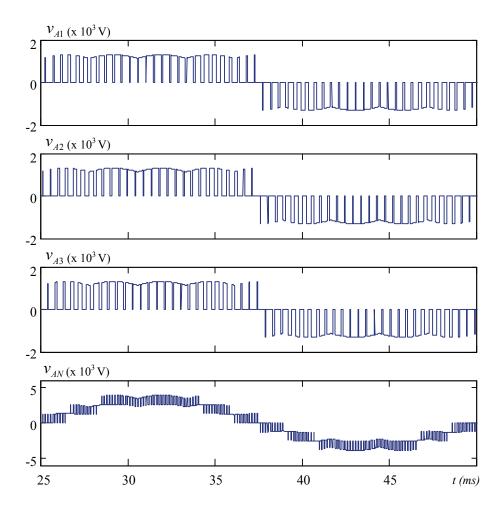

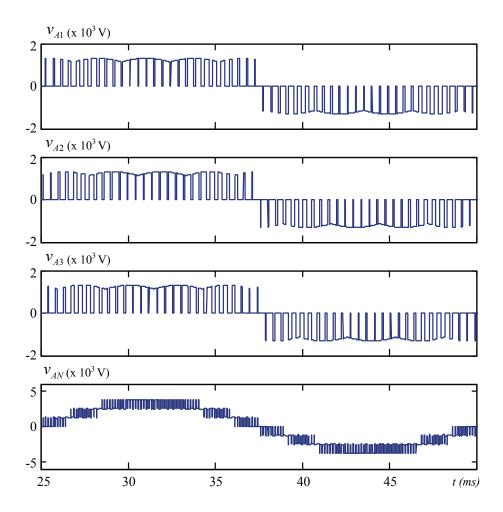

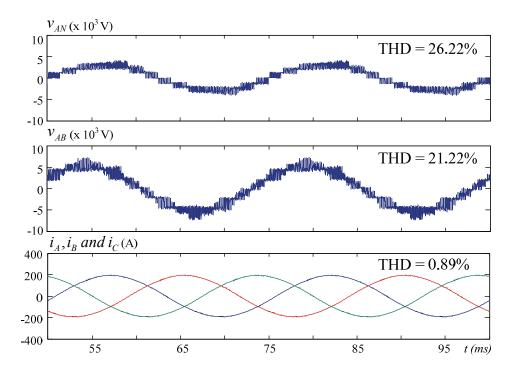

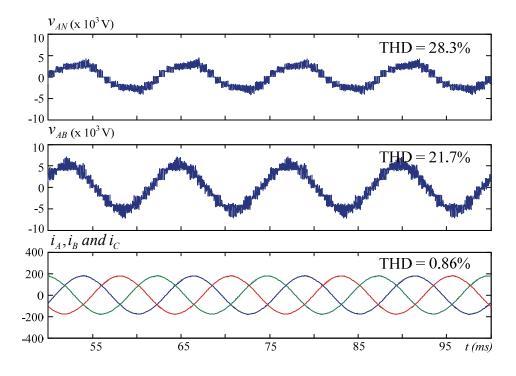

| Fig. 4-9 Simulated output voltage and current waveforms of MMMC-II ( $f_o = 40$ Hz, $m_a = 0.9$ )         |

| Fig. 4-10 Simulated output voltage and current waveforms of MMMC-II ( $f_o = 80$ Hz, $m_a = 0.9$ )        |

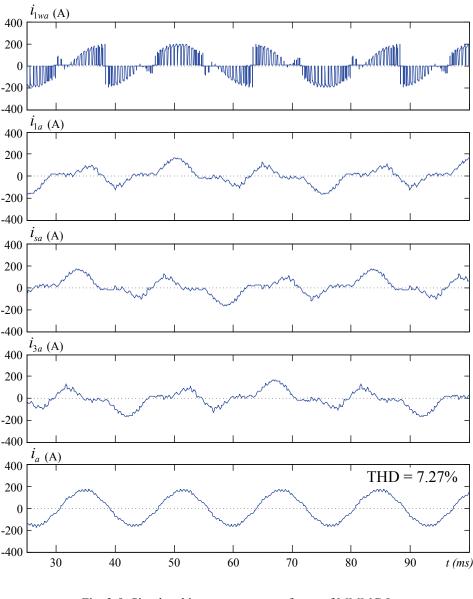

| Fig. 4-11 Simulated input current waveforms of MMMC-II ( $f_o = 40$ Hz, $m_a = 0.9$ )119                  |

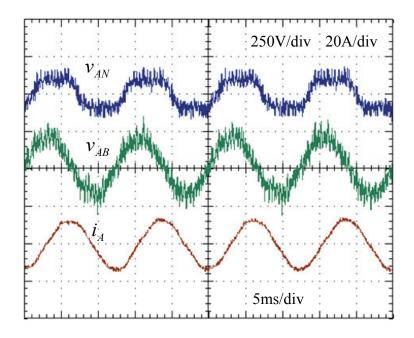

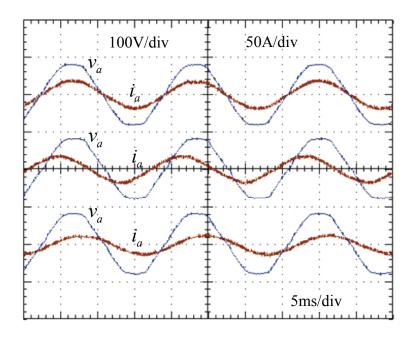

| Fig. 4-12 Experimental output voltage waveforms of MMMC-II under no load condition                        |

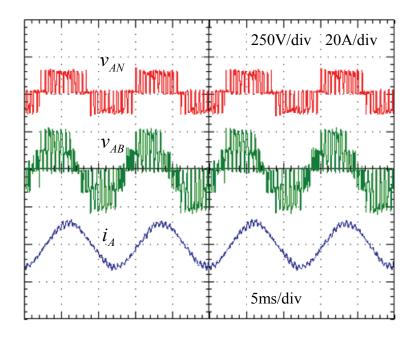

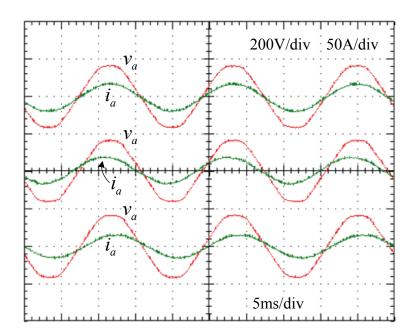

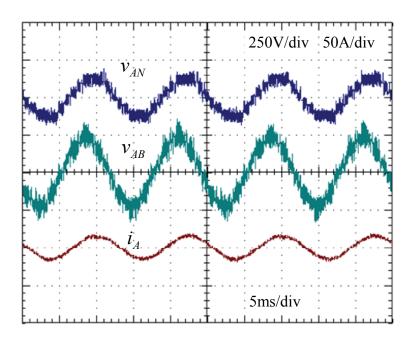

| Fig. 4-13 Experimental output voltage and current waveforms of MMMC-II ( $f_o = 40$ Hz, $m_a = 0.9$ ) 122 |

| Fig. 4-14 Experimental output voltage and current waveforms of MMMC-II ( $f_o = 80$ Hz, $m_a = 0.9$ ) 122 |

| Fig. 4-15 Experimental input side waveforms ( $f_o = 40$ Hz, $m_a = 0.9$ )                                |

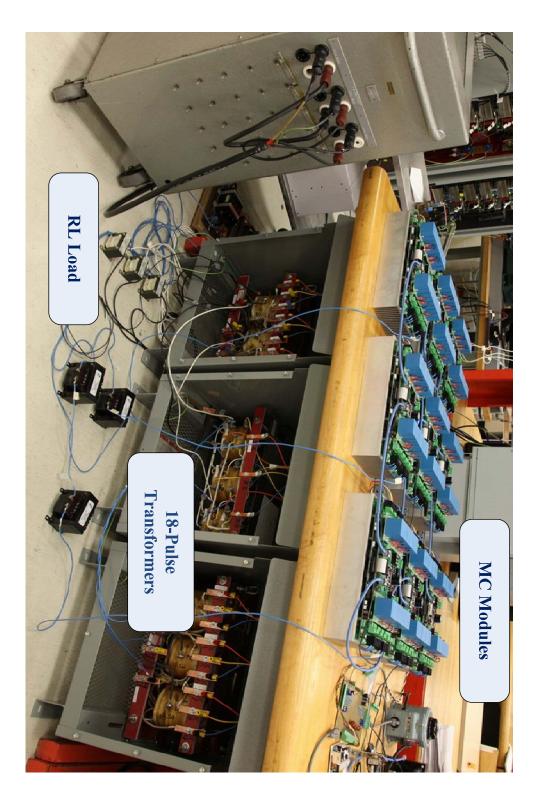

| Fig. 5-1 Structural diagram of the low-voltage experimental setup                                         |

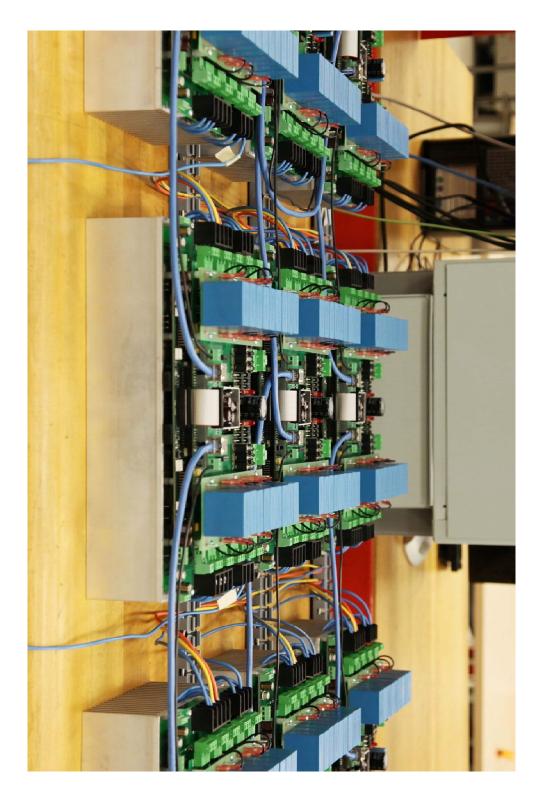

| Fig. | 5-2  | Low-voltage experimental setup of the MMMC.                                               | .127 |

|------|------|-------------------------------------------------------------------------------------------|------|

| Fig. | 5-3  | Construction of the experimental 3 x 2 MC module.                                         | .128 |

| Fig. | 5-4  | Top-front view of the experimental MC modules.                                            | .129 |

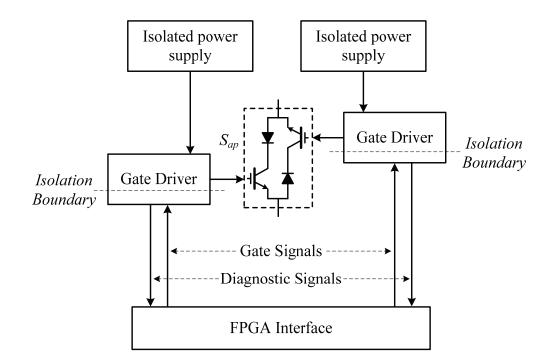

| Fig. | 5-5  | Gate driving of the bidirectional switches.                                               | .130 |

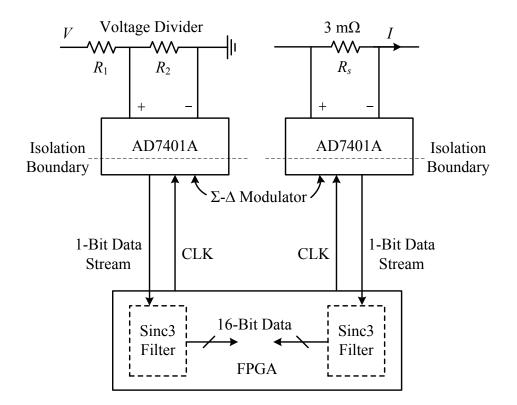

| Fig. | 5-6  | Voltage and current measurement using isolated 1-Bit $\Sigma$ - $\Delta$ Modulator        | .131 |

| Fig. | 5-7  | Initial state of output port <i>p</i> connected to input phase <i>a</i>                   | .132 |

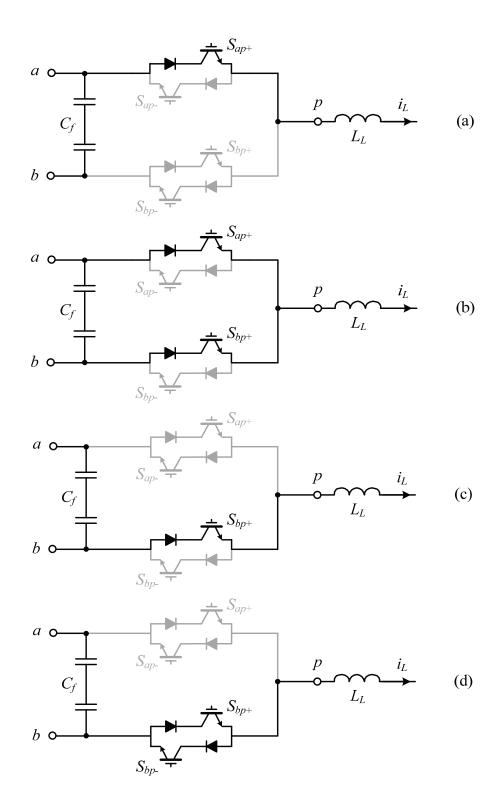

| Fig. | 5-8  | Four-step device commutation based on load current direction. (a) Step 1. (b) Step 2. (c) |      |

| Step | 3. ( | d) Step 4                                                                                 | .133 |

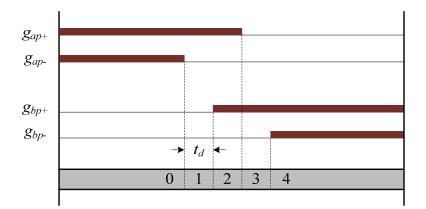

| Fig. | 5-9  | Gate signals during the four-step device commutation.                                     | .134 |

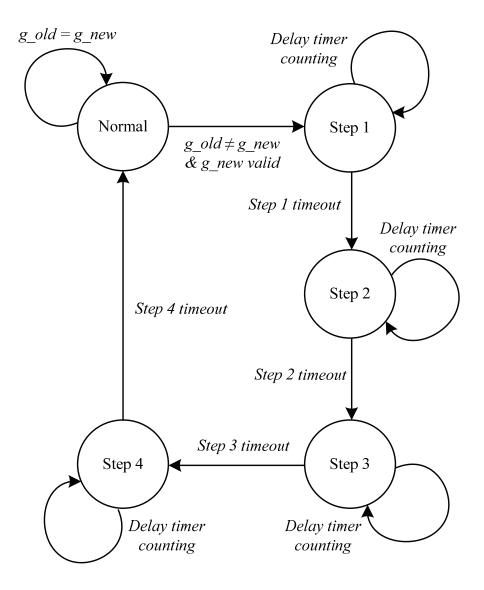

| Fig. | 5-10 | ) FPGA finite state machine implementation of the four-step device commutation            | .135 |

## **List of Tables**

| Table 2-1 System parameters for direct modulation scheme simulation                        | 45  |

|--------------------------------------------------------------------------------------------|-----|

| Table 2-2 Experimental system parameters for direct modulation scheme                      |     |

| Table 3-1 Duty ratio conversion for the inverter stage with the two-level SVM              | 69  |

| Table 3-2 Example of dc-link currents expressed in terms of the load currents              | 72  |

| Table 3-3 Example of duty ratio conversion for the inverter stage with the three-level SVM | 75  |

| Table 3-4 Switching state combination for 3 x 2 MC Module 1                                | 76  |

| Table 4-1 System parameters of MMMC-II for simulation                                      | 116 |

| Table 4-2 Experimental parameters of MMMC-II                                               | 120 |

# **Glossary of Acronyms**

| ANPC    | Active Neutral Point Clamped                    |

|---------|-------------------------------------------------|

| CHB     | Cascaded H-Bridge                               |

| CSC     | Current Source Converter                        |

| CSR     | Current Source Rectifier                        |

| DFE     | Diode Front End                                 |

| EMI     | Electromagnetic Interference                    |

| FPGA    | Field Programmable Gate Array                   |

| FLC     | Flying Capacitor                                |

| GTO     | Gate Turn-Off Thyristor                         |

| HVDC    | High-Voltage Direct Current                     |

| IM      | Induction Machine                               |

| IGBT    | Insulated Gate Bipolar Transistor               |

| IGCT    | Integrated Gate Commutated Thyristor            |

| LS-SPWM | Level-Shifted Sinusoidal Pulse-Width Modulation |

| LCI     | Load Commutated Inverter                        |

| LVDS    | Low-Voltage Differential Signaling              |

| MC      | Matrix Converter                                |

| MV      | Medium Voltage                                  |

| MOV     | Metal Oxide Varistor                            |

| MMC     | Modular Multilevel Converter                    |

| MMMC    | Multimodular Matrix Converter                   |

| NPC     | Neutral Point Clamped                              |

|---------|----------------------------------------------------|

| PS-SPWM | Phase-Shifted Sinusoidal Pulse-Width Modulation    |

| PWM     | Pulse-Width Modulation                             |

| RL      | Resistor and Inductor                              |

| RB-IGBT | Reverse Blocking Insulated Gate Bipolar Transistor |

| SHE     | Selective Harmonic Elimination                     |

| SCR     | Silicon Controlled Rectifier                       |

| SPWM    | Sinusoidal Pulse-Width Modulation                  |

| SVM     | Space Vector Modulation                            |

| SGCT    | Symmetric Gate-Commutated Thyristor                |

| SM      | Synchronous Machine                                |

| THD     | Total Harmonic Distortion                          |

| TPWM    | Trapezoidal Pulse-Width Modulation                 |

| VSC     | Voltage Source Converter                           |

| VSI     | Voltage Source Inverter                            |

### **Chapter 1**

### Introduction

In the area of high-power converters for medium-voltage (MV) motor drives, research and development efforts have been made to either devise new converter configurations, or solve technical problems and optimize performance of existing topologies for specific applications. During the past decade, since there were few revolutionary high-power semiconductors rising, a large percentage of the relevant work was focused on existing topologies and their variants. At present, several major multilevel voltage-source inverters (VSIs) fed by diode or active front-ends are the primary converter choices for most commercial MV drives [1]. Competitive solutions such as the pulse-width modulated (PWM) current-source converter (CSC) are also finding widespread application in industry [2]. In addition to the conventional converters that are relatively mature, alternative topologies including several types of hybrid multilevel converters [3-5], active neutral point clamped (ANPC) converters [6, 7], modular multilevel converters (MMCs) [8, 9], and multilevel matrix converters [10-12] have also attracted increased research interests over the past years. Although the overall effectiveness and potential benefits of these emerging topologies still need further investigation and proof, a few of them have already made their way into practical products and entered the commercial market. Correspondingly, modulation and control strategies adapted to these new converters have been proposed and studied in a large number of recent publications, helping improve operating performance as well as exploring new possibilities.

Among all emerging high-power converter topologies, the multilevel matrix converters form a special category that incorporates the concepts of both multilevel structure and direct power conversion. As alternatives to dc-link based ac-dc-ac converters, direct ac-ac topologies such as the conventional matrix converter (MC) have been extensively studied for several decades [13-15]. However, mainly due to the lack of power semiconductor that can offer sufficiently high voltage and current handling capability, the conventional MCs are not suitable for high-power applications. The fact has led to the invention of multilevel MCs that can reach higher power and voltage levels with existing power semiconductors. This research line is evident in a series of recent publications where the ideas of several major multilevel converter topologies, for instance the neutral-point-clamped (NPC) converter (CHB) [18], are borrowed and combined with the matrix converter concept, resulting in a number of corresponding multilevel MC topologies, namely, the neutral-point-clamped multilevel MCs [10, 19], the capacitor clamped multilevel MC [20], and the multiple cell based MCs [11, 21, 22].

To date, only one particular type of multilevel MC topology has been practically implemented as a commercial MV drive. Designated here as the multimodular matrix converter (MMMC), the topology is composed of a multiple number of three-phase to single-phase MC power modules, cascaded to allow the converter to operate at very high power and voltage levels. It is reported that the commercialized MV drive using this topology has reached 3 MVA / 3.3 kV with three MC modules in series per phase, and 6 MVA / 6.6 kV with six modules in series per phase [12]. Being a member of the MC family, the MMMC possesses features such as elimination of dc energy storage components, extended lifespan, inherent four-quadrant operation, and fast dynamic performance. Additionally, it also possess inherited characteristics from the cascaded multilevel structure,

such as modular design, flexible scalability, and high quality multi-step output voltage waveforms.

Modulation is essential to the proper operation of any type of power converters. For the MMMC, modulation scheme design is not straightforward at first glance due to its particular topological structure. As the converter is composed of three-phase to single-phase MC modules without a stiff dc voltage or current, well established modulation strategies for neither the conventional MCs nor the multilevel converters can be directly adopted. This necessitates the development of specifically tailored modulation schemes for the MMMC to produce sinusoidal input and output waveforms with variable amplitude and frequency.

In this dissertation, several new modulation schemes are proposed and investigated for the MMMC topologies. All the presented schemes are able to generate sinusoidal waveforms at both input and output ports of the converters, with the frequency, amplitude and angle of the output fundamental component arbitrarily adjustable. The input power factor can be adjusted by the first two schemes, while for the last method, it is left uncontrolled but close to unity under suitable component parameters and working conditions.

This chapter is dedicated to the background introduction of the study. First, the general technical requirements on high-power converters for MV drives are briefly summarized. Then, an overview of the state-of-the-art MV drive converter candidates, as well as their features and limitations is provided. After the introduction of the newly emerged multilevel MC topologies, the main objectives and outline of the dissertation are presented at the end of the chapter.

### **1.1 Technical Requirements for MV Drive Converters**

Fig. 1-1 General structure of a medium-voltage drive system.

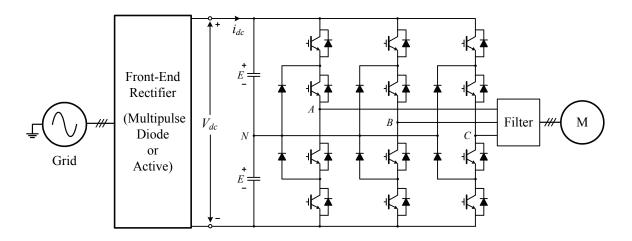

The MV drive is basically an ac-to-ac power converter system which transforms the fixed amplitude and fixed frequency grid voltage into a desired form for varying the speed of the electric motor load. As demanded by motor control objectives such as speed and torque regulation, the output amplitude and frequency of the drive converter need to be freely adjustable. In Fig. 1-1, the general structure of a typical MV drive system is illustrated. The entire system is composed of the following stages: a line-side filter interfacing the grid, an input transformer providing isolation and adequate secondary voltage level, an ac-to-ac power converter which, in most cases, consisting of a rectifier and an inverter coupled through a dc-link, and an output filter located between the inverter and the machine. In a practical MV drive, some of the stages may be omitted depending on the particular converter configuration.

The majority of commercial MV drives are in the power range of 1 to 4 MW, and their voltage ratings are in the range of 3.3 kV to 6.6 kV [23]. As these apparatus present significant loads to the MV distribution grid, they are subject to strict line-side

requirements on the generation of harmonic contents and input power factor regulation. In the context of any electrical grid, harmonic distortions, if not properly contained, may cause many harmful effects such as malfunction and failure of equipments, tripping of important industrial processes, and excessive loss and heating in the transformers. Therefore, power electronics based apparatus like the MV drive should comply with established harmonic standards such as IEC 1000 and IEEE Standard 519-1992 [24]. As harmonic content generation in an MV drive is mainly due to the switching behavior of the rectifier stage, the choice of converter topology and its modulation scheme have a large impact on the lineside harmonic performance. Additionally, the input filter is necessary in most topologies to help with the harmonic reduction.

Besides harmonic distortion, input power factor regulation is another important lineside requirement. In most cases, a high input power factor within a small region close to unity is demanded by the utility grid.

On the motor side of the drive, the waveform quality is also of great importance. Harmonic contents generated by the inverter or LC resonance could result in additional power loss, heating, and torsional vibration in the electric machine, and therefore should be minimized. Minimization of the harmonic contents requires the inverter stage of the drive to produce high quality sinusoidal waveforms by means of well designed modulation strategies. Additional output filters are necessary in many situations to further smooth the waveforms and improve the machine current quality.

Other motor-side technical concerns include high dv/dt in the generated voltage waveforms, electromagnetic interference (EMI), and common-mode voltage stress on the machine load. Since most modern inverters are operated by PWM, the dv/dt and EMI associated with device switching transients can be very high considering the significant voltage ratings of the MV converter. If not properly mitigated, these detrimental effects

may cause premature failure of shaft bearing and motor winding insulation, as well as malfunction or failure of nearby electronic equipments [23]. Possible solutions to attenuate the harmful dv/dt and EMI include employment of dv/dt filters and use of multilevel converters to reduce PWM voltage waveform steps. In addition to dv/dt and EMI, the common-mode voltage stress – also a by-product of the switching behavior of the converter – is another serious concern in the MV drive system. If completely placed on the motor, the high stress caused by common-mode voltages could result in premature failure of the motor winding insulation as well [23]. To avoid this situation, most available MV drives employ an input isolation transformer to undertake the dominant part of the stress. In a few designs where the input transformer is eliminated, the major part of the common-mode voltage can be taken by a specially designed common-mode choke [25]. Furthermore, it is worth mentioning that, the choice of multilevel converter topologies and/or suitable modulation schemes may reduce or even eliminate the switching-generated common-mode voltages [26], thereby relieve the stress on isolation transformer and/or common-mode chokes.

### **1.2 Overview of Modern MV Drive Converter Topologies**

This section gives an overview of the most relevant high-power converter topologies for MV drives. The focus is mainly placed on existing topologies that have found practical presence in industry, as well as several potential topology candidates which are recently proposed and studied in the literature. Although not considered as high-power converters, the conventional matrix converter and some of its multilevel derivatives are also briefly reviewed due to their high relevance to the subject matter.

As shown in Fig. 1-2, converter topologies for MV Drives can be generally classified into two major categories: the ac-dc-ac indirect converters, which contain dc-links interconnecting the rectifier and inverter stages, and the ac-ac direct converters, which perform power conversion directly between their input and output ac terminals.

Fig. 1-2 Classification of high-power converters for MV drive.

### 1.2.1 ac-dc-ac Indirect Converters

The ac-dc-ac indirect converters invariably require dc energy storage components and can be further divided into current-source converters (CSCs) and voltage-source converters (VSCs). The CSCs have a current-stiff dc-link realized by dc inductors, whereas the VSCs feature voltage-stiff dc-links comprised of dc capacitors. Both CSC and VSC topologies have found wide commercial application in the MV drive industry; but they are associated with different characteristics and features.

#### **1.2.1.1** Current-Source Converters

In the subcategory of CSCs, the load-commutated inverter (LCI) and the PWM CSC are the only two types currently being used in practical products. The LCI is built with siliconcontrolled rectifier (SCR) devices, and is mainly suitable for very high power synchronous machine (SM) drives. In contrast, the more modern PWM CSC is made up of symmetric gate-commutated thyristors (SGCTs) with reverse voltage blocking capability. The PWM CSC can be used to drive both megawatt induction machines (IMs) and SMs.

### LCI based CSC

Fig. 1-3 LCI based MV drive for synchronous machine load.

The LCI based MV drive as shown in Fig. 1-3 is essentially a back-to-back thyristor converter constructed with SCR devices [27]. In the dc-link of the converter, a large inductor is employed to smooth the current. Aimed at very high power SM applications, the

power rating of an LCI drive is typically in the range of a few to tens of megawatts, and may even reach a hundred megawatts or beyond in some particular cases. Due to its simple structure and use of inexpensive and rugged SCR devices which are commutated at the fundamental frequency, the LCI drive features low converter cost, low power loss, high efficiency, high reliability, simple control, and allows regenerative operation. As the commutation of SCR devices require a load voltage of leading power factor (hence the name "load-commutated"), the LCI drive is most suited for large SMs that can work in the over-excited condition by adjusting the rotor field current. Along with all the benefits obtained, the LCI has limitations and drawbacks from using the phase-controlled SCRs as well, those include: limited control freedom and dynamic performance, high harmonic contents in both the line- and motor-side currents, and variable input power factor under different load conditions [2, 28]. In a practical LCI drive, input filter and power factor compensator are normally required.

### **PWM CSC**

Fig. 1-4 Configuration of PWM CSC based MV drive system.

The state-of-the-art PWM CSC drive possesses a similar topology to that of the LCI, featuring two three-phase full-bridge converters connected in the classic back-to-back configuration through a dc-link inductor [29]. However, unlike the LCIs which are composed of SCRs and operated by phase control, the PWM CSC consists of fully controllable SGCT devices that can be arbitrarily turned off by the gate signals. These modern high-power devices allow the PWM CSC to be operated by various PWM schemes at a switching frequency of several hundred hertz, generating chopped current pulses at both ac terminals of the converter. Due to PWM operation, ac filter capacitors are required to assist device commutation and to attenuate the generated harmonic current contents. The PWM CSC drive is able to produce variable amplitude variable frequency sinusoidal waveforms with adjustable angle at both the line and motor side. Generally speaking, features of the PWM CSC include simple topology, motor friendly waveforms, and reliable fuse-less short-circuit protection. Moreover, the topological structure of the PWM CSC enables an integrated dc-link choke design using a common magnetic core to realize a practical transformerless MV drive. The integrated choke consists of a differential part as the normal dc-link inductor, and a common-mode choke to undertake the dominant part of the common-mode voltage stress. The otherwise required input isolation transformer can therefore be eliminated.

The PWM CSC can be switched by various modulation schemes, such as trapezoidal PWM (TPWM), selective harmonic elimination (SHE), and space vector modulation (SVM) [23]. The TPWM is a carrier-based modulation strategy where a trapezoidal modulating wave is compared with a specially tailored carrier wave to generate gate signals. Although the scheme satisfies the CSC switching constraints, the generated PWM waveforms contain relatively high low-order harmonic contents. The SHE is an offline calculated method that offers both low switching frequency and superior harmonic profile due to its purposeful

elimination of several low-order harmonics. However, when compared with the online switching schemes, the SHE's dynamic performance is inferior, owing mainly to its lack of modulation index adjustment capability. The SVM is a digital modulation method which performs real-time duty-cycle calculation and reference vector synthesis, and provides excellent dynamic performance for the converter control by offering the complete degrees of control freedoms (modulation index and delay angle). However, the harmonic performance of the conventional CSC SVM is not as good as that of the SHE. Also the SVM is associated with more switchings and power losses by introducing the short-through pulses. These two drawbacks, together with the fact that in a practical PWM CSC drive, the motor-side magnitude adjustment is normally done through controlling the dc-link current level by the rectifier, rather than to utilize the inverter-side modulation index, make SHE the main modulation scheme choice in a PWM CSC drive in the medium to nominal speed range. TPWM and SVM may also be chosen when the load machine works in the low speed region, where the SHE may not find a viable solution for the calculation of angles.

The main drawback of the PWM CSC drive lies in its slow dynamic performance, which is primarily because of the large choke employed in the dc-link, and the drive's control strategy of using the rectifier to regulate dc current level for load-side magnitude adjustment.

### 1.2.1.2 Voltage-Source Converters

Compared with CSCs, VSC topologies are much more popular in many applications including the MV drive. In the fast developing MV drive industry, both conventional two-level VSC and a number of multilevel VSC topologies are currently present in the market. The two-level VSC based MV drive needs to put devices in series to withstand the high voltage stress, and produces large voltage steps in the output waveform equaling that of the

entire dc-link voltage. The multilevel converters, on the other hand, are relieved from many problems of the two-level VSC and, in general, possess the following advantages:

1) Reduced voltage stress on individual power switches. This enables the use of power semiconductors with lower voltage rating and avoids the problems and challenges associated with series device connection;

2) Reduced dv/dt during device switchings. In contrast to the two-level VSC, each device in a multilevel VSC is normally switched between two adjacent voltage levels instead of the entire dc-link voltage. This also brings the benefit of lower common-mode voltage steps/amplitudes;

3) Better input/output waveform quality in terms of total harmonic distortion (THD) and harmonic profile due to the generated multi-step waveform shape that is closer to sinusoid. As a result, the requirement on input/output filters can be significantly lowered or even eliminated.

At present, several multilevel VSC topologies such as the NPC converter and the CHB converter are the primary converter choices for most commercial MV drives.

### **High-Power Two-level VSC**

As the dominant topology in low-voltage motor drives, the two-level VSC has also been used to implement MV drives by a few manufacturers [23]. In a two-level VSC based MV drive, the power devices (insulated gate bipolar transistor, IGBT) need to block the entire dc-link voltage. Since there is no single device available to offer such a high voltage rating, the IGBTs in the converter legs have to be connected in series to share the voltage stress. The series-connection of devices is accompanied by static and dynamic voltage sharing issues which need to be addressed by active or passive means [30]. In addition, the voltage step, *dv/dt* and common-mode voltage stress generated by the two-level VSC are very high, which require large-size differential and common-mode filters to suppress. Depending on specific application requirement, the dc-link of the two-level VSC drive can be fed by a diode front-end for non-regenerative operation, or an active front-end to realize a back-to-back configuration for regenerative breaking. In terms of modulation, the well-established carrier-based sinusoidal PWM (SPWM) and SVM schemes can both be used in the two-level VSC to implement advanced motor control strategies [31].

### **Neutral-Point-Clamped Converter**

The three-level NPC converter as shown in Fig. 1-5 is presently one of the most widely used topologies in newly developed MV drives. Unlike the two-level VSC which only switches between the negative and positive rails of the dc-link, the NPC converter splits the dc-link equally with two cascaded capacitors, and thereby introduces a dc neutral point [16]. On each of the NPC's phase legs there are four power switches. In addition, two diodes are added to connect the dc neutral point to the junctions between the first and second, third and fourth switches, hence allowing the phase output terminal to be clamped to the dc neutral level. As a result, the phase output voltage of an NPC converter can have three levels (with respect to the dc neutral point):  $+V_{dc}/2$ , 0, and  $-V_{dc}/2$ . Compared with the twolevel VSC, the device voltage stress in the NPC converter is halved for a given dc-link voltage. Besides, the output voltage quality of the NPC is better due to the multilevel waveform shape which reduces the requirement of the filter. Commercial NPC drives are implemented with high-voltage IGBTs or integrated gate commutated thyristors (IGCTs), which have replaced gate turn-off thyristors (GTOs) as the dominant high-power semiconductor devices. Currently, the NPC based MV drive covers a voltage rating up to 4.16 kV without putting devices in series or using step-up transformer, and is expected to

extend to higher voltage ranges with the advent of 10 kV IGCTs [32]. In a typical NPC drive, multi-pulse diode rectifier or active rectifier using the same NPC topology can be employed as the front-end converter, for unidirectional or bidirectional power flow applications, respectively.

Fig. 1-5 NPC converter based MV drive.

The NPC converter can be modulated by various modulation schemes, such as the multi-carrier-based SPWM, three-level SVM, and SHE [33]. Both carrier-based PWM and SVM provide the complete control freedoms of modulation index and angle adjustment. Due to the multiplicative effect brought by the three-level structure, the equivalent converter switching frequency of the NPC is twice that of the device switching frequency, offering the converter a good dynamic performance for advanced motor control requirements.

One of the main technical issues associated to the NPC converter is the need to balance dc capacitor voltages during operation. The problem has been solved by many strategies proposed over the years for either diode-front-end-fed or active-front-end-fed configurations [34, 35]. Another drawback of the NPC lies in the uneven power loss and, thereby, uneven heat dissipation on the outer and inner switches. Using active switches in place of the clamping diodes and forming a three-level active NPC topology may significantly improve the loss distribution, but at the expense of increased semiconductor cost [6].

### **Cascaded H-Bridge Converter**

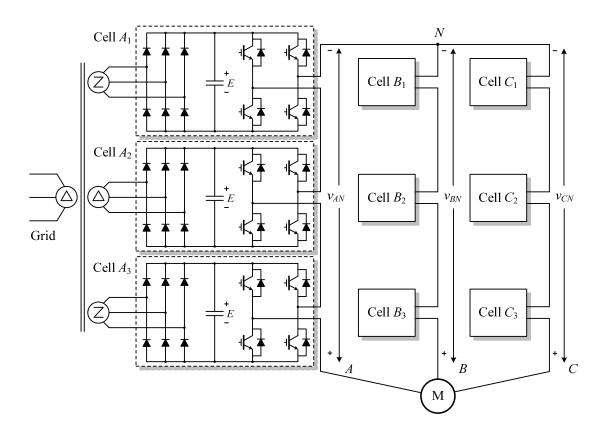

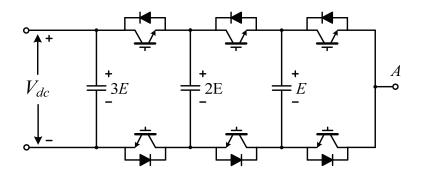

Fig. 1-6 A seven-level CHB converter based MV drive.

Besides NPC, the CHB converter (Fig. 1-6) is another very popular multilevel VSC topology that has been chosen by a large number of MV drive manufacturers. As the name indicates, the CHB is made up of series connected single-phase full-bridge converters (H-

bridges). The H-bridges are supplied by separate dc-link capacitors sourcing energy from three-phase diode-rectifiers, which are normally fed by the secondary windings of a phase-shifting input transformer interfacing the grid. Each H-bridge, together with the dc-link capacitor and the diode rectifier, forms a standard power cell and serves as the fundamental building block for the modular design of the entire converter. Regarding the power cells, although CHB converters with unequal dc-source modules were also revealed to have some advantages by scholarly research [5], the loss of modularity make them unfavorable choices for practical drive products. In a practical CHB drive with equal dc-source cells, as each power cell independently contributes three voltage levels (+*E*, 0, -*E*), the entire converter is able to produce high quality multilevel output voltages, and may reach very high voltage and power ratings using only low-voltage IGBTs. It was reported that the maximum ratings for the CHB converter in use is 13.8 kV / 31000 kVA [1]. On the input side of the converter, the harmonic contents caused by the diode rectifiers are mostly cancelled out in the phase-shifting transformer. Therefore, the total input current has low harmonic distortion and can meet the grid requirements.

The CHB converter can be modulated by several multicarrier-based SPWM schemes, such as the phase-shifted SPWM (PS-SPWM) which employs horizontally shifted triangle carriers for comparison with the sinusoidal modulating wave, and the level-shifted SPWM (LS-SPWM) schemes where the carriers are vertically distributed in the modulation plane. The CHB converter can also be operated by staircase modulation, SVM, and SHE schemes. In practice, the most used scheme is the PS-SPWM which provides decent harmonic performance, even device switchings, and balanced load sharing among the contributing cells. It is worth noting the equivalent switching frequency of the CHB can be several times that of the device switching frequency, making the topology an attractive candidate for high-speed applications.

A main drawback of the CHB converter is its need for a costly and bulky phase-shifting transformer with many secondary windings. Moreover, if regenerative operation is required for a CHB, the diode rectifiers in the power cells have to be replaced by active rectifiers [36], leading to significantly increased cost and complex control.

**Flying Capacitor Converter**

Fig. 1-7 Four-level flying capacitor converter (output phase A).

The flying capacitor (FLC) converter is among the classic multilevel converter topologies and has been well studied in the literature [17]. As shown in Fig. 1-7, The structure of the FLC is similar to that of the high-power two-level VSC, in which IGBT devices are connected in cascade in the phase legs to block the high dc-link voltage. However in an FLC, in addition to the switching devices, capacitors are added to the phase legs and connected between the switch pairs in the upper and lower half bridges, thereby clamping the device joints and introducing more output voltage levels. Although able to produce multilevel output waveforms, the FLC converter requires a large number of extra capacitors that need to be charged during startup and balanced during normal operation, which is main drawback of the topology. FLC converter based drive is offered by only one

manufacturer in the market and is much less popular than the NPC and CHB based products.

#### **NPC/H-bridge Converter**

Fig. 1-8 NPC/H-bridge converter based MV drive.

The NPC/H-bridge converter in Fig. 1-8 employs two NPC legs to support each of its three output phases [37]. The two NPC legs are connected in the H-bridge configuration and able to generate five output voltage levels between their output terminal pair. Because each H-bridge provides one output terminal to be connected with those from the other phases, the three H-bridges in the converter cannot share a common dc-link as in the NPC converter. Instead, they need to be fed by isolated multi-pulse rectifier configurations from the input phase-shifting transformer. Having twice the device count in an NPC converter, the NPC/H-bridge converter provides more voltage levels and covers a higher

power/voltage range than the NPC does. Currently, two manufacturers offer NPC/H-bridge converter based MV drive products with the voltage rating up to 6.9 kV.

#### **Five-level Active NPC Converter**

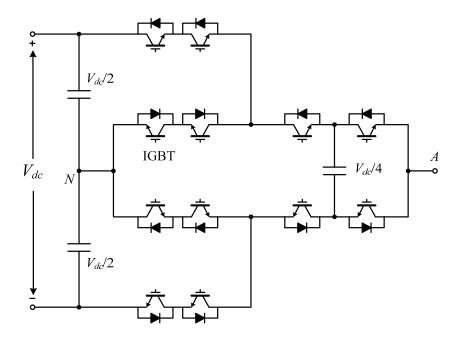

Fig. 1-9 Five-level active NPC converter (output phase A).

The three-level ANPC was further extended into a five-level converter topology in recent years [6, 7, 38]. The outcome is called a five-level ANPC but can be essentially considered as a hybrid combination of a three-level ANPC and a basic flying capacitor power cell. Fig. 1-9 shows the circuit diagram of the five-level ANPC for a single output phase. Through the use of redundant switching states, the voltage across the added flying capacitor is maintained at 1/4 of the dc-link voltage, such that the inverter phase output voltage can be chosen from the following five voltage levels (with respect to the dc neutral

point):  $+V_{dc}/2$ ,  $+V_{dc}/4$ , 0,  $-V_{dc}/4$  and  $-V_{dc}/2$ . Taking into account the voltage stress in the converter, series connection of devices is required in the ANPC part to enable use of unified devices with the same voltage rating. The back-to-back configuration of the five-level ANPC topology has been commercialized as an MV drive by one leading manufacturer, with the power rating up to 1 MVA / 6.9 kV and transformerless option available [7].

#### **Modular Multilevel Converter**

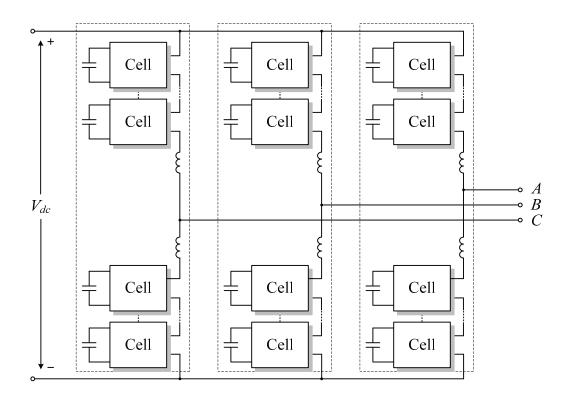

Fig. 1-10 Modular multilevel converter.

The modular multilevel converter (MMC) is a relatively new topology proposed for high-power applications [8, 9, 39]. During the past decade, it has attracted increasing interest and has found industrial presence in a light-weight high-voltage direct current (HVDC) transmission system. The MMC is composed of stacks of series connected halfbridge choppers formed by two IGBTs and a capacitor. Each MMC phase leg consists of a positive stack and a negative stack as well as the necessary output inductors. Due to the cascaded structure, the MMC features very good modularity and scalability, and is therefore able to undertake very high voltages. Not like the CHB converter which is also based on series connection of power cells, the power modules in MMC do not need isolated dc sources. Therefore, the three inverter legs in the MMC can share a common dc-link fed by a common rectifier. The use of MMC for MV drive application was proposed in [40], where it was revealed the fluctuation of the chopper capacitor voltages are related to the motor current frequency. It was also concluded in [8] that the converter can be adapted for loads such as the fans, pumps, blowers and compressors, while not suitable for high-torque low-speed applications.

#### **1.2.2 ac-ac Direct Converters**

Unlike indirect converters that invariably synthesize output voltage or current from a dc-link stage supported by passive elements, the ac-ac converters perform single-stage power conversion directly from the ac inputs and are free of any dc-link components. To date, only a few ac-ac direct converters have found presence in the MV drive industry. These include the classic cycloconverters and one particular type of the newly developed multilevel MC topologies.

#### Cycloconverter

A cycloconverter is a direct frequency changer whereby fixed magnitude fixed frequency input ac power is converted to output ac power in a single stage [2]. With groups of thyristors employed and operated coordinately, both magnitude and frequency of the output can be varied. In order to avoid severe waveform distortion, the output frequency of a cycloconverter cannot exceed a fraction of the input frequency. The output voltage is constituted from selected portions of the input voltage pulses, and its magnitude can be adjusted by means of phase angle control. Motor drives using cycloconverters possess advantages such as simple structure, high reliability, low switching losses and very high efficiency due to the use of naturally commutated thyristor devices. Furthermore, these converters can be operated in all four quadrants and have inherent capability of bidirectional power flow. On the other hand, also owing to the use of phase controlled thyristors, the input power factor of cycloconverters is generally low, with significant harmonic currents being drawn from the grid by the converter. Cycloconverters are mainly used in low-speed high-power motor drives in industries of cement, mining, metals and the like. It should be mentioned that cycloconverter based drives are not as popular as inverter based drives in new designs due to technology advancement and performance improvement of the latter.

#### **Matrix Converters**

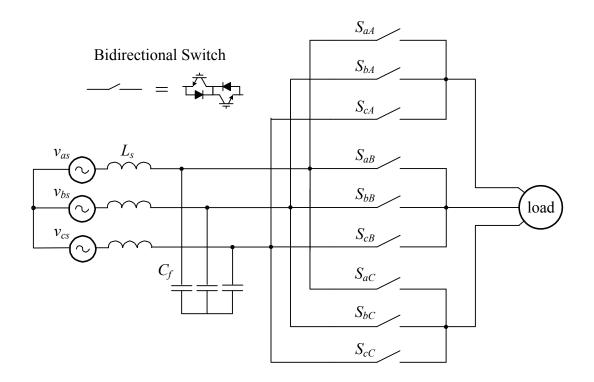

Although matrix converters (MCs) share the same basic functionality with cycloconverters: to perform single stage ac power conversion with variable magnitude and variable frequency, the MCs differ from the cycloconverters in many aspects. Equipped with four-quadrant bidirectional switches made up of force-commutated devices such as IGBT, a typical MC is able to generate output voltages with either higher or lower frequencies than that of the input. A conventional MC features inherent four quadrant

operation capability, sinusoidal input/output waveforms, and a controllable input power factor [14, 41]. If compared with dc-link based indirect converters, the MC possesses several advantages such as reduced size and higher power density, improved lifespan due to elimination of the bulky and often trouble-causing dc-link component, and faster dynamic performance owing to its single stage conversion. Nevertheless, for the same reason of the avoided dc-link component, MCs are also known for their relatively complex modulation and commutation techniques, limited voltage transfer ratio, and lack of ride-through capability.

Fig. 1-11 Three-phase to three-phase conventional MC.

With maturation of suitable power devices and advancement of control, the MC has been considered an alternative topology for dc-link converters where power density and regeneration capability are of great importance. Among all configurations, the three-input three-output MC (3 x 3 MC) as shown in Fig. 1-11 and its topological variants have attracted the most research interest. Although study on the conventional MC can be traced back to several decades ago [13], the topic only started to resurge lately and has regained much attention during the past years. Owing to the solving of several major technical challenges such as bidirectional switch commutation control, the MC has been pushed closer to practical application. It is worth mentioning that the first commercial MC based adjustable speed drive was already released [12]. So far, most of the research work about MC falls into the low-voltage category where the converter can be operated at a relatively high switching frequency, whereas the high power applications had never considered MC as a viable option due to concerns on efficiency and power device rating limitations.

Recently, there has been an increasing interest in introducing MCs into the high-power arena [20, 42-44]. Taking account of the limited voltage ratings of existing power semiconductors, the conventional 3 x 3 MC is still not a viable option for higher voltage applications. In view of this, researchers have directed attention to come up with new MC topologies which incorporate the concepts of multilevel converters. During the past decade, the ideas of several major multilevel VSC topologies have been utilized and combined with the conventional MC concept, resulting in the emergence of the neutral-point-clamped multilevel MCs, the capacitor clamped multilevel MC, and the multi-module based multilevel MCs. In addition to being members of the MC family, these new topologies also possess features similar to the multilevel VSCs. Correspondingly, their modulation and control aspects have been studied in a number of publications [10, 11, 19-21, 44, 45].

The neutral-point-clamped multilevel MCs are developed from the indirect construction of the conventional MCs. The indirect construction separates the whole converter into a rectifier stage and an inverter stage with no dc-link components. Instead of using a twolevel VSC, a three-level NPC converter is employed in the inverter stage to provide more output voltage levels. Recently, several topological variants of the NPC multilevel MC have been discussed in a few publications [10, 19, 43]. Compared with the conventional MC, the neutral-point-clamped MCs improve the output voltage quality at the cost of increased device count. However, the device voltage stress, especially for those in the rectifier stage, is not reduced. The topology is therefore still not suitable for higher voltage applications.

Another novel multilevel MC topology, the capacitor clamped multilevel MC, was proposed in 2005 [20]. This converter employs six flying capacitors to balance voltage distribution among series connected switch modules and to provide middle voltage levels. The voltage stress on the switches is halved comparing to that of a conventional MC. In the meantime, the harmonics in the output voltage and current waveforms are also significantly lowered. The main disadvantage of this topology lies in the large amount of clamping capacitors required, as well as the increased device count and complex converter structure.

At present, the only multilevel MC topology that has found commercial presence is the multimodular matrix converter (MMMC) [11, 12]. Formed by three-phase to single-phase MC (3 x 2 MC) modules, the MMMCs are very similar to the CHB converter in terms of topological structure, but are different from the latter in the construction of constituent power modules. In a CHB converter, each module contains a dc-link capacitor, and the output voltages are synthesized from the dc voltage; whereas in an MMMC, the output voltages of any single module are directly fabricated from the three-phase ac inputs. Due to the series connection of power modules, the MMMC can reach high voltage and power levels while using low-voltage IGBTs only. Meanwhile, they also need the input phase-shifting transformer to provide isolated ac sources, just like the CHB converter.

Proper operation of the MMMC topologies relies on suitable modulation schemes that can generate variable frequency sinusoidal waveforms at both ac terminals. To date, there is no comprehensive study on the modulation scheme design for the MMMCs. It is therefore this work's primary aim to propose and develop appropriate modulation schemes for these particular converters.

# **1.3 Dissertation Objectives**

Modulation scheme design for the MMMC topologies is not a straightforward task. Unlike the conventional MCs that feature a three-phase-in three-phase-out balanced structure, or the dc-link based indirect converters where the dc component decouples the rectifier and inverter stages, the MMMCs are composed of 3 x 2 MC modules in which the power flow is pulsating. Although synthesis of sinusoidal output voltage waveforms can be achieved without much difficulty, the simultaneous generation of sinusoidal line-side current waveforms requires coordination among different MC modules and needs careful design. Aiming at developing various possible modulation schemes for the MMMCs, the main objectives of this dissertation are listed as follows:

- Establish the mathematical transfer function matrix of the MMMCs as a basis for modulation scheme design. Propose a direct transfer function based modulation scheme together with a suitable switching pattern to generate sinusoidal waveforms at both sides of the converters.

- 2) By applying the classic fictitious dc-link concept, create an equivalent indirect circuit model for the MMMCs to lay a foundation for the design of indirect space vector based modulation schemes. Based on the developed model, design indirect modulation schemes and novel switching patterns to improve waveform quality.

- 3) Develop a novel modulation scheme based on diode front-end emulation and phaseshifted SPWM. Different from the other proposed strategies, this new method

allows the use of an indirect module structure with significantly reduced device count and structure complexity, which come at the price of sacrificing the input power factor adjustment capability.

Provide simulation results to verify the proposed concepts, and build a low-voltage prototype of a nine-module system to further test the modulation schemes experimentally.

# **1.4 Dissertation Outline**

This dissertation consists of six chapters which are organized as follows.

Chapter 1 provides the background and introduction of the study.

Chapter 2 describes the MMMC topologies, then proposes a direct transfer-functionbased modulation scheme for generating sinusoidal waveforms at both sides of the converters. Starting with the most fundamental three-module version of the topology, it is revealed that, although the input currents of individual 3 x 2 MC modules contain significant harmonic distortion, the total line-side currents, being the sum of the secondary currents referred to the primary side of the transformer, can still be sinusoidal when a proper modulation method is applied.

Chapter 3 presents an indirect circuit modeling to design indirect space vector based modulation schemes for the MMMCs. Based on the fictitious dc-link concept, the indirect model separates the converter into a rectifier stage and an inverter stage. SVM methods for current-source rectifier and voltage-source inverters can then be independently applied to calculate the duty ratios needed for input current and output voltage synthesis. After the duty ratios are converted and combined, gate signals for the real switches are generated according to two switching patterns. The second proposed switching pattern is proved to offer a superior harmonic profile in the generated waveforms.

Chapter 4 proposes a simple modulation method for the nine-module MMMC fed by an input phase-shifting transformer. Focusing only on fabricating multilevel output voltage waveforms, the method is essentially a combination of diode front-end emulation with phase-shifted SPWM. Although the method does not bother with input current synthesis, because power balance among modules on a same output phase is guaranteed, and owing to the harmonic elimination capability of the phase-shifting transformer, sinusoidal input current with good quality can still be achieved.

Chapter 5 introduces a low-voltage lab prototype constructed for experimental verification of the proposed modulation schemes. Details about the implementation of the power modules, voltage and current measurement, device commutation control as well as module synchronization, communication and protection are provided.

Chapter 6 summarizes the main contributions and conclusions of the presented work. Possible future research directions are also suggested.

# Chapter 2

# **Direct Modulation Scheme for the MMMC Topologies**

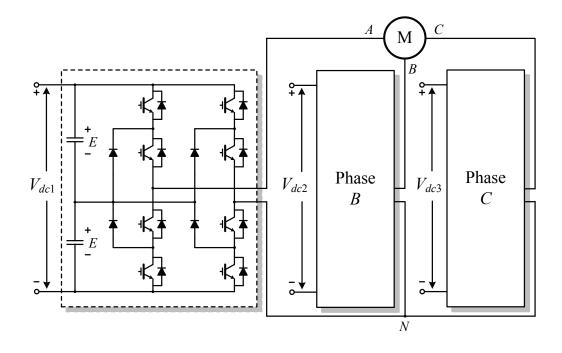

The multimodular matrix converters (MMMCs) are comprised of a multiple number of three-phase to single-phase (3 x 2) matrix converter (MC) modules. The MC modules are normally fed by a multi-winding input transformer, and can be cascaded on the load side to provide high voltage/power output without using power devices of increased voltage ratings. Similar to the cascaded H-bridge (CHB) converter, the MMMCs possess features such as modular design, high quality multi-stepped output voltage waveform, and allow the use of low-voltage power semiconductors under mass production. Moreover, the MMMCs eliminate the dc components necessary in the CHB, and they are inherently regenerative. Due to the unique topological structure, established modulation schemes for neither the CHB converter nor the conventional three-phase to three-phase (3 x 3) MCs can be directly applied to operate the MMMCs. In each 3 x 2 MC module, although generating any desired single-phase output voltage from the three-phase input voltages by means of pulse-width modulation (PWM) is not difficult to achieve, to synthesize three-phase input sinusoidal currents from the single-phase output current is basically an impossible job. The fact can also be appreciated from the power balance perspective, as the single-phase output power is always pulsating, while a balanced three-phase input provides a constant power flow.

The main objective of this chapter is to develop a direct modulation scheme for the MMMCs to synthesize sinusoidal voltage/current waveforms on both ac sides of the converters. Rather than trying to fabricate sinusoidal currents right at the input ports of the MC modules, the proposed strategy targets the total input currents on the primary side of the multi-winding transformer. It will be demonstrated that although the three-phase input currents of each MC module have distortions, the sum of the secondary-winding currents eventually becomes sinusoidal when referred to the primary side of the transformer. As for the output voltage, the generated frequency can be either higher or lower than that of the input, making the converters and the modulation scheme suitable for medium-voltage (MV) drive application where the output voltage and frequency need to be variable to control the machine load.

# 2.1 Topological Structure of the MMMCs

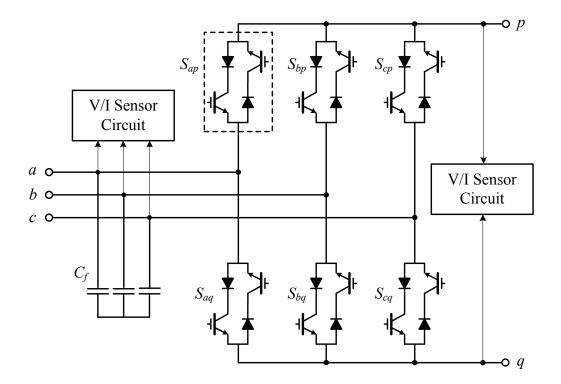

#### 2.1.1 Three-Phase to Single-Phase (3 x 2) MC Module

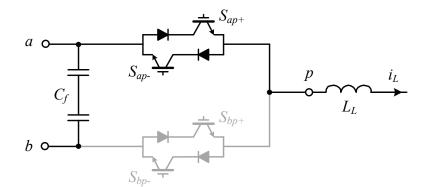

The fundamental building block for the MMMC topologies is a three-phase-in singlephase-out MC module which consists of six bidirectional power switches. As shown in Fig. 1-1, each bidirectional switch can be practically formed by two insulated-gate bipolar transistor (IGBT)-diode pairs connected in anti-series, or by two reverse blocking IGBTs (RB-IGBT) connected in anti-parallel [46]. Since the bidirectional switches are four quadrant operable, they are able to block voltages of both polarities and allow currents in either direction. Under normal operating conditions, when the switches in the module are turned ON and OFF, the output terminals p and q can be arbitrarily connected to any one of the three input terminals a, b, and c to choose a proper voltage level. The input-side terminals of the MC module are fed by a three-phase power supply [ $v_{as}$ ,  $v_{bs}$ ,  $v_{cs}$ ]. A threephase ac filter capacitor is needed at the input port of the module to assist switching commutation and suppress current harmonics. On the output side, the module should be connected to an inductive load, whose continuous current is utilized as a current source for fabrication of desired input currents.

Fig. 2-1 Simplified diagram of a 3 x 2 MC module.

Similar to the conventional 3 x 3 MCs, the 3 x 2 MC module is subject to switching constraints. Any switching state that may cause short circuit of the filter capacitors or interrupt of the inductive load current is prohibited. Hence, at any instant of time, two and only two switches in the module, one from the upper group of  $[S_{ap}, S_{bp}, S_{cp}]$  and the other from the lower group of  $[S_{aq}, S_{bq}, S_{cq}]$  must be in the ON state. The switching constraint for the 3 x 2 MC module can be mathematically expressed as follows

$$\begin{cases} S_{ap}(t) + S_{bp}(t) + S_{cp}(t) = 1 \\ S_{aq}(t) + S_{bq}(t) + S_{cq}(t) = 1, \end{cases}$$

(2.1)

where

$$S_{jk}(t) = \begin{cases} 1, S_{jk} \text{ is } ON \\ 0, S_{jk} \text{ is } OFF, \end{cases}$$

$j \in \{a, b, c\}, k \in \{p, q\}.$

The switching constraint provides a basis for the modulation and switching state design for the MMMCs. In addition, due to the use of bidirectional switches, device commutation between different phases should comply with the constraint as well to avoid short circuit of the capacitors and open circuit of the inductive load during transients. Same as the direct type conventional 3 x 3 MC, the 3 x 2 MC modules can readily adopt the load current or input voltage based multi-step commutation strategies for device commutation control [47]. The principle and implementation details of the commutation are explained in Chapter 5.

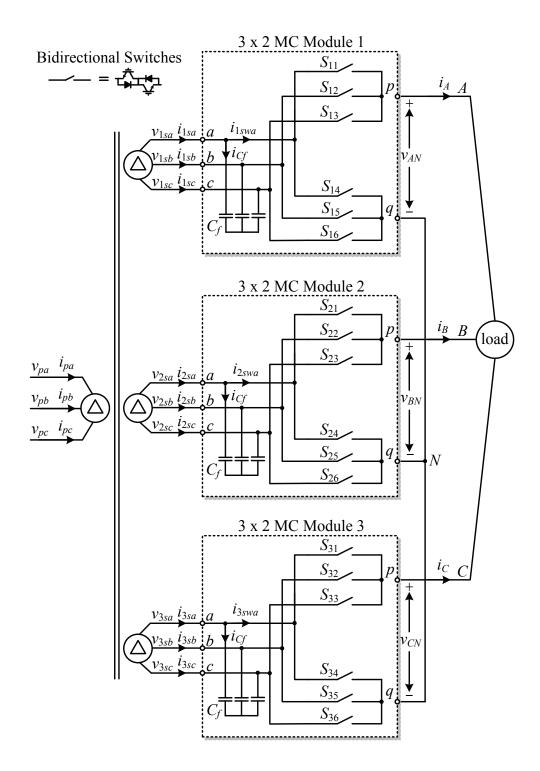

#### 2.1.2 Three-Module Multimodular Matrix Converter-I

Using three 3 x 2 MC modules, the simplest version of the MMMC topology (MMMC-I) can be built to supply an inductive load. Fig. 2-2 shows the simplified circuit diagram of MMMC-I, where a three-phase-four-winding transformer is employed to provide isolation and the required secondary-winding voltage level. The MC modules act as the interface between the input transformer and the load. On the input side, each module is fed by one of the secondary windings of the transformer, and ac filter capacitors are present to assist commutation as well as to filter the switching harmonics. On the output side, the q terminals from all the modules are connected together to form a reference neutral point,

Fig. 2-2 Simplified circuit diagram of three-module MMMC-I.

while the p terminals are directly connected to the load phases. The load of the converter could be either a three-phase RL or an ac machine, the inductive nature of which is necessary for the proper operation of the MC modules.

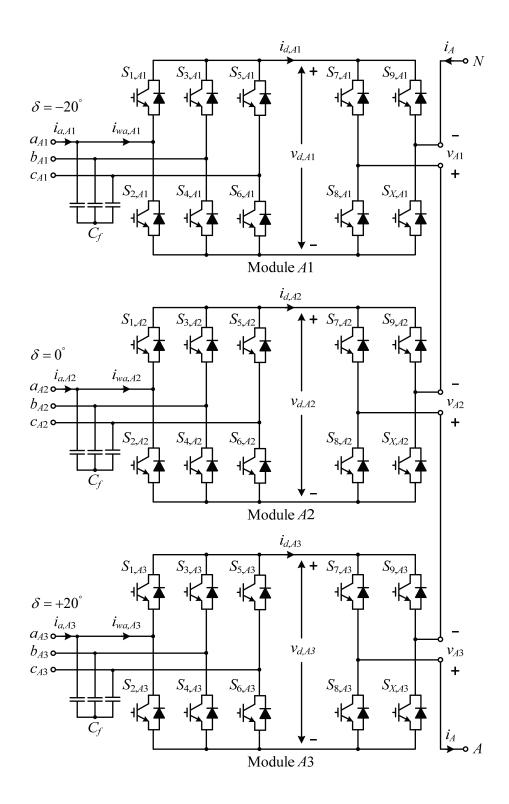

#### 2.1.3 Nine-Module Multimodular Matrix Converter-II

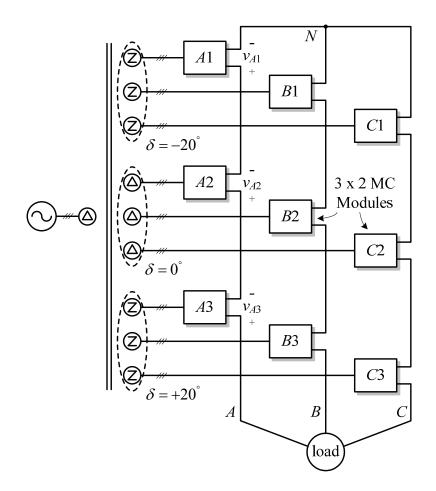

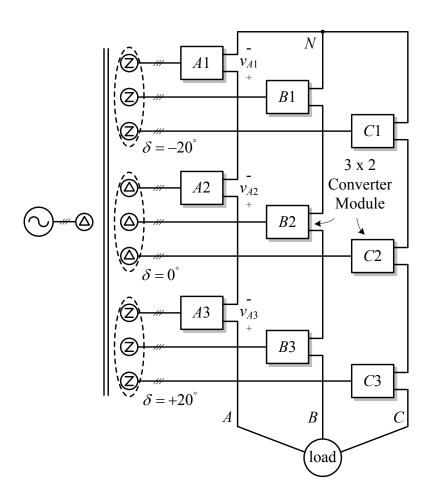

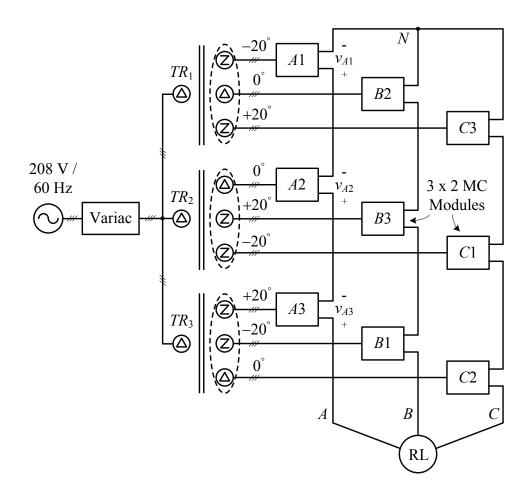

Fig. 2-3 Simplified circuit diagram of nine-module MMMC-II.

If a larger number of MC modules are employed, the fundamental three-module MMMC-I can be extended to multilevel configurations for higher power/voltage output

levels and better waveform quality. Fig. 2-3 illustrates the simplified circuit diagram of a nine-module version of the MMMC. Designated as MMMC-II, the converter is equipped with three MC modules on each of its output phases which are fed by a phase-shifting transformer having nine secondary windings. The secondary windings of the transformer are arranged into three groups with phase displacements of -20°, 0° and +20°, respectively. This configuration allows for cancellation of several unwanted low-order harmonic currents on the primary side [48]. The whole converter of MMMC-II can be essentially viewed as three sets of MMMC-Is connected in series. It is also very similar to the seven-level CHB converter in terms of structure, except that the H-bridge switching cells in the latter are replaced by the MC modules without dc capacitors.

In order to achieve even higher power and voltage output levels, the number of MC modules employed for series connection can be further increased. The commercial MV drive based on the MMMC topology, as an example, puts six MC modules in series per phase to reach a voltage level of 6.6 kV [12]. Nevertheless, this would require the input phase-shifting transformer to have a larger number of secondary windings and more sophisticated phase displacement arrangements, similar to the case of multilevel CHB converters.

## **2.2 Direct Modulation Scheme for the MMMCs**

The challenge for the design of a modulation scheme suitable for the MMMCs lies in how to produce sinusoidal voltage/current waveforms on both sides of the converter. Just like in a conventional 3 x 3 MC, the inputs of the MC modules are regarded as voltage sources whereas the outputs are taken as current sources due to the inductive load. The task of a properly designed modulation scheme is to assemble sinusoidal output voltages from segments of the input voltages, and fabricate sinusoidal input currents with pieces from the load currents, both at the same time. For the conventional 3 x 3 MC, a large number of modulation schemes have been well established in the literature [15, 49-56]. However, these methods cannot be directly applied to the MMMCs. As mentioned earlier, in each individual 3 x 2 MC module, although it is not difficult to generate any desired single-phase output voltage, to directly synthesize three-phase sinusoidal input currents from the single-phase output current would be almost impossible.

The succeeding sections present a direct-transfer-function-based modulation strategy for the MMMCs. The explanation is first carried out based on the three-module MMMC-I. Since the more complicated versions are essentially cascaded connection of multiple sets of MMMC-I, the basic modulation scheme can be easily modified to control them. Instead of trying to obtain sinusoidal currents at the input ports of the MC modules, the proposed scheme targets the total input currents on the primary side of the transformer. As a result of the modulation, although the input currents of each MC module are not sinusoids, the total input current at the primary side of the transformer is sinusoidal and well follows the angle reference. For the output voltage, the frequency and angle can be arbitrarily set, and the magnitude can be controlled through the modulation index adjustment.

#### **2.2.1** Transfer Function Matrix Derivation

Referring to the circuit diagram of MMMC-I in Fig. 2-2, because all the three-phase windings of the input transformer have the same phase shifts, the relationship between the instantaneous output and input voltages of the converter can be established by means of a switching function matrix