# DEVELOPMENT AND IMPLEMENTATION OF INTERACTIVE 3D VIDEO ENVIRONMENT ON RUN-TIME RECONFIGURABLE FPGA PLATFORM

259

By

Sergiy Zhelnakov, B.Sc. Kiev Polytechnic Institute, Ukraine, 1984

A Thesis

Presented to Ryerson University

In partial fulfillment of the requirements

for the degree of Master of Applied Science

in the program of Electrical and Computer Engineering

Toronto, Ontario, Canada, 2006 © Sergiy Zhelnakov, 2006

PROPERTY OF RYERSON UNIVERSITY LIBRARY

UMI Number: EC53554

#### **INFORMATION TO USERS**

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

## UMI®

UMI Microform EC53554

Copyright 2009 by ProQuest LLC

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

#### **Declaration of Authorship**

| Deciaration of Authorship                                                                          |

|----------------------------------------------------------------------------------------------------|

| I hereby declare that I am the sole author of this thesis                                          |

| į.                                                                                                 |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

| I authorize Ryerson University to lend this thesis to other institution or individuals for the     |

| purpose of scholarly research                                                                      |

| 1                                                                                                  |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

| I further authorize Ryerson University to reproduce this thesis by photocopying or by other        |

| means, in total or in part, at the request of other institutions or individuals for the purpose of |

| scholarly research                                                                                 |

| ı                                                                                                  |

|                                                                                                    |

## Borrower's Page

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

| Name        | Signature | Address                                 | Date |

|-------------|-----------|-----------------------------------------|------|

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           | *************************************** |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           | ,                                       |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           | ······                                  |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

|             |           |                                         |      |

| <del></del> |           |                                         |      |

|             |           |                                         |      |

## Development and Implementation of Interactive 3D Video Environment on Run-Time Reconfigurable FPGA Platform

Sergiy Zhelnakov, Master of Applied Science, 2006, Electrical and Computer Engineering, Ryerson University

#### **ABSTRACT**

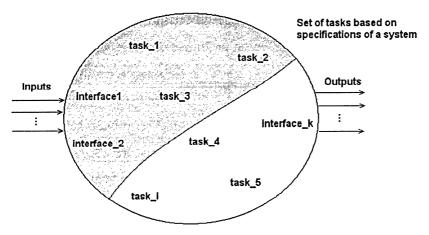

Video data processing tasks are traditionally performed either through software-based systems when various algorithms must be applied to the data and when time issue is not critical, DSPs – when certain time constraints are set but when the set of tasks is limited, or ASICs – when the highest performance is required, the set of tasks is fixed and highly optimized, the data stream doesn't change, and the number of data streams is limited.

For a real-time system which must operate on multiple data streams which also can change in time and on which various data processing algorithms must be applied neither of the mentioned approaches can be used. Timing requirements and power limitation does not allow utilization of a sequential CPU. ASIC becomes too big to accommodate multiple processing circuits for each algorithm and associated modes. Only Run-Time Reconfigurable (RTR) FPGA approach allows implementation of such a system.

The thesis presents a real-time stereo vision system with elements of synthesis of interactive 3-D virtual objects designed and implemented on the FPGA-based reconfigurable platform. FPGA chip integrates a hybrid architecture system with multi-mode and multi-stream processing ability for time critical tasks and with embedded microprocessor(s) for computing complex algorithms for 3-D objects synthesis for which timing requirements are not so strict.

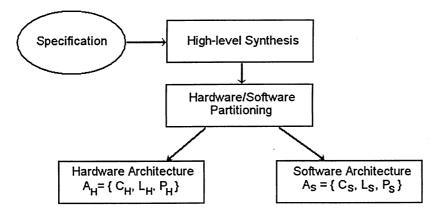

An approach for the formal presentation and processing of the 3-D virtual objects and their transformation is also analyzed and presented in this paper. Architecture synthesis and optimization for a hybrid system are also considered.

The experimental results proved the effectiveness of proposed approach: the FPGA-based system-on-chip provides stereo visualization in different modes (actual image and edge detection image), with synthesized 3-D controls (pressed and released buttons).

Keywords: Stereo Vision, 3-D Synthesis, Reconfigurable Platform, FPGA

#### Acknowledgements

I have been fortunate over the past few years to have worked with my supervising professor, Dr. Lev Kirischian. His guidance, knowledge and support not only contributed much to this work but inspired me to immerse in run-time reconfigurable systems.

My special thanks to professor, Dr. Vadim Geurkov for his valuable suggestions and support during all the time of research and working on the project.

I would also like to thank the Department of Electrical and Computer Engineering for providing facilities and technical resources needed for the research.

Many thanks to the members of the review committee for their participation and consideration. My special gratitude to the OGS for support of this research through scholarships.

I'd like also to express my deep gratitude to Mr. Jim Koch and members of the Embedded Reconfigurable Systems Lab (ERSL), Ph.D. students Mr. Peter (Pil Woo) Chun and Mr. Valeri Kirischian for their technical assistance during the implementation phase of the project.

Last but not least, many thanks to my wife and kids for their understanding, patience and support during all the time of working on this thesis, and to my parents whose wise advises years ago opened the world of electrical engineering for me.

## **Table of Contents:**

| 1. | INT   | RODUCTION                                               | 1     |

|----|-------|---------------------------------------------------------|-------|

|    | 1.1.  | Motivation                                              | 1     |

|    | 1.2.  | Objectives                                              | 5     |

|    | 1.3.  | Original contributions                                  | 5     |

|    | 1.4.  | Thesis organization                                     | 6     |

| 2. | OVI   | ERVIEW OF COMPUTING SYSTEMS FOR REAL-TIME STEREO ANI    | )     |

| P  | ANORA | AMIC VISION WITH ELEMENTS OF 3-D VIRTUAL OBJECTS SYNTH  | ESIS8 |

|    | 2.1.  | Introduction                                            | 8     |

|    | 2.2.  | Real-time video systems                                 | 13    |

|    | 2.3.  | Wide angle or panoramic vision systems                  | 20    |

|    | 2.4.  | Elements of virtual reality technique                   | 25    |

|    | 2.5.  | Conclusion                                              | 27    |

| 3. | THE   | EORY AND METHODOLOGY                                    | 29    |

|    | 3.1.  | Introduction                                            | 29    |

|    | 3.2.  | Synthesis of virtual 3-D objects                        | 30    |

|    | 3.2.1 | 1. Translation transformation                           | 32    |

|    | 3.2.2 | 2. Rotation transformation                              | 33    |

|    | 3.2.3 | 3. Projection transformation                            | 37    |

|    | 3.2.4 | Line segments representation for projected images       | 40    |

|    | 3.2.5 | 5. Rasterizing polygons                                 | 45    |

|    | 3.2.6 | 5. Surface visibility                                   | 47    |

|    | 3.3.  | System architecture synthesis and analysis              | 51    |

|    | 3.3.1 | 1. Design-oriented approach                             | 51    |

|    | 3.3.2 | 2. Synthesis-oriented approach and design space         | 52    |

|    | 3.3.3 | 3. Sequencing graph (or Data Flow Graph)                | 53    |

|    | 3.3.4 | Scheduling                                              | 55    |

|    | 3.3.5 | 5. Binding                                              | 56    |

|    | 3.3.6 | 5. Architecture optimization                            | 57    |

|    | 3.3.7 | Design space and Architecture Configuration Graph (ACG) | 58    |

|    | 3.4.  | Conclusion                                              | 60    |

| 4. | DE   | VELO     | PMENT OF ARCHITECTURE AND IMPLEMENTATION OF THE                     |    |

|----|------|----------|---------------------------------------------------------------------|----|

| SY | STEN | <i>1</i> |                                                                     | 61 |

| 4  | 4.1. | Intro    | duction                                                             | 61 |

| 4  | 4.2. | Arch     | itecture synthesis for the real-time stereo vision system           | 61 |

|    | 4.2. | 1.       | Architecture selection for the Image Capture Subsystem (ICS)        | 62 |

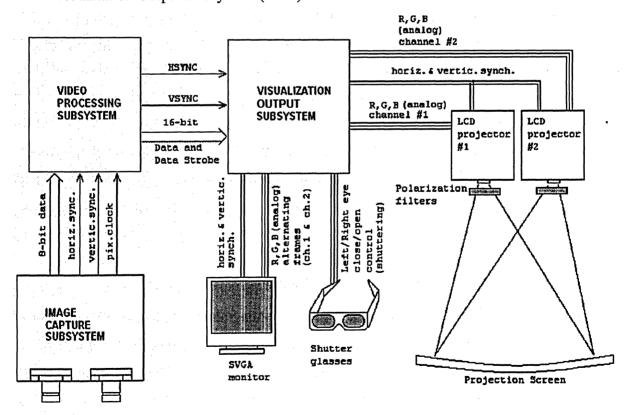

|    | 4.2. | 2.       | Architecture selection for the Visualization Output Subsystem (VOS) | 63 |

|    | 4.2. | 3.       | Architecture selection for the Video Processing Subsystem (VPS)     | 63 |

|    | 4.2. | 4.       | Architecture of the system                                          | 73 |

|    | 4.3. |          | etional description of the system                                   |    |

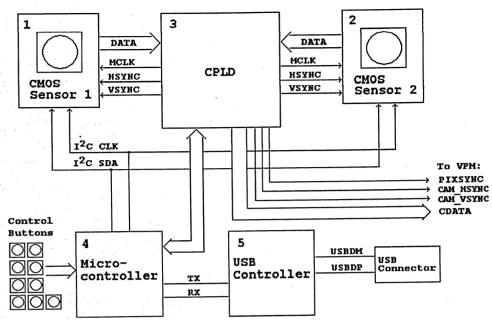

|    | 4.3. |          | Image Capture Module (ICM)                                          |    |

|    | 4.3. |          | Video Processing Module (VPM)                                       |    |

|    | 4.3. |          | Visualization Output Module (VOM)                                   |    |

|    | 4.4. | Con      | clusion                                                             |    |

| 5. | EX   |          | MENTS AND RESULTS                                                   |    |

|    | 5.1. |          | erimental Set-Up                                                    |    |

|    | 5.2. | _        | erimental results                                                   |    |

|    | 5.3. | _        | lysis of results                                                    |    |

| 6. |      |          | JSIONS AND FUTURE WORK                                              |    |

| 7  |      |          | RAPHY                                                               |    |

## List of figures:

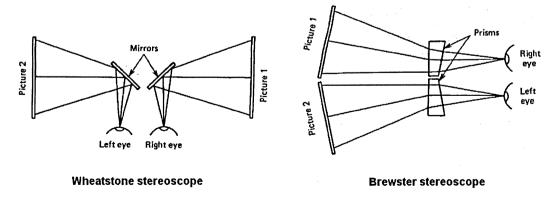

| Figure 2-1. Wheatstone and Brewster stereoscopes                                             | 8  |

|----------------------------------------------------------------------------------------------|----|

| Figure 2-2. Parallax stereogram.                                                             |    |

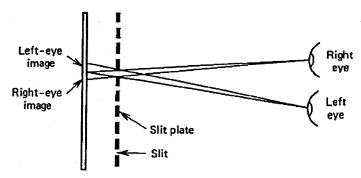

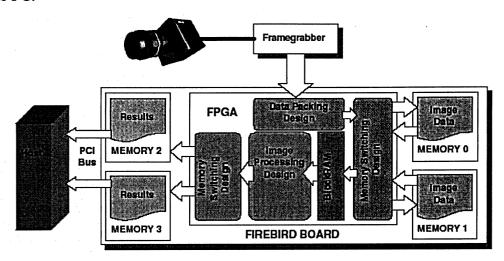

| Figure 2-3. Typical Hardware Setup for designs based on FPGA-GPP combination                 | 13 |

| Figure 2-4. Common Processing Flow                                                           |    |

| Figure 2-5. Hardware setup of the high quality vision system by Leeser, et al                | 15 |

| Figure 2-6. Hardware setup and block diagram of the vision system by Genta, et al            |    |

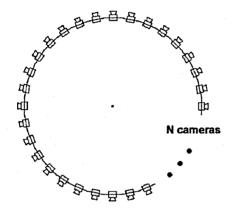

| Figure 2-7. Multicamera system configuration                                                 | 17 |

| Figure 2-8. Digiclops camera system by Point Grey Research Inc                               | 17 |

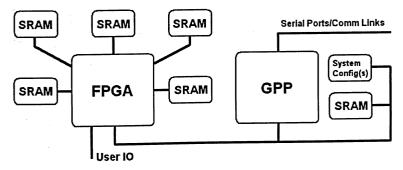

| Figure 2-9. Hardware setup for the system with switching RAM architecture                    | 19 |

| Figure 2-10. Tyzx stereo camera family: 5cm, 22cm, and 33cm baselines and DeepSea            |    |

| processor                                                                                    | 20 |

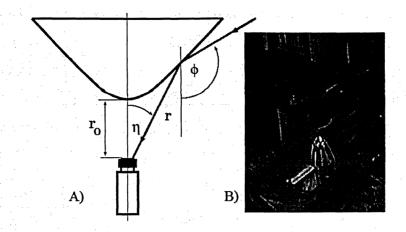

| Figure 2-11. Specially shaped (curved) mirror for panoramic vision                           | 21 |

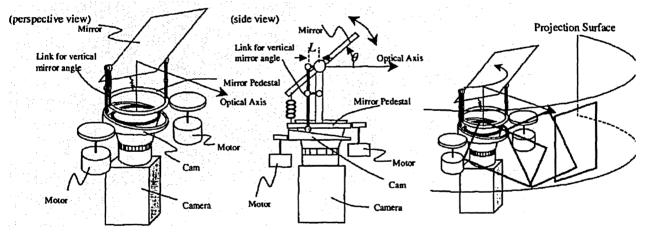

| Figure 2-12. Rotating mirror architecture for panoramic vision                               | 21 |

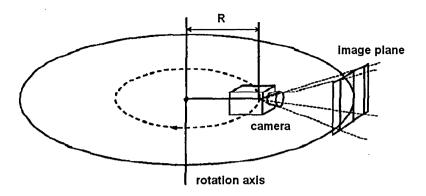

| Figure 2-13. Panoramic view using panning methodology                                        | 22 |

| Figure 2-14. Basic capture units and overlapping of camera views                             | 22 |

| Figure 2-15. Setup for creating stereo panoramic video                                       |    |

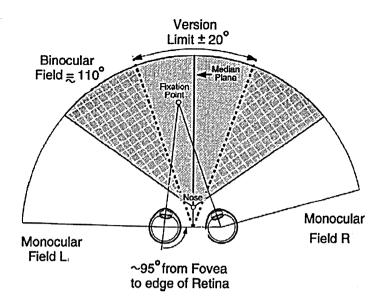

| Figure 2-16. Comfortable viewing range for eye motion (version)                              |    |

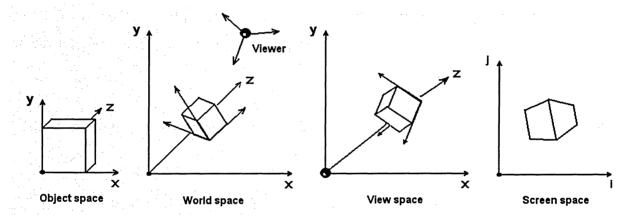

| Figure 3-1. Reference systems classification.                                                | 31 |

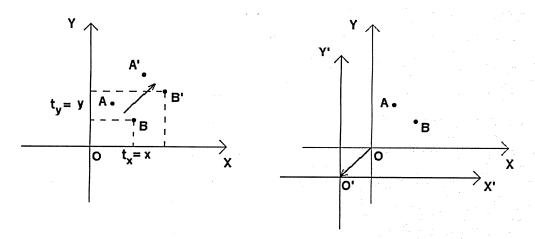

| Figure 3-2. Two approaches to translation transformations: translation of a set of points ar | nd |

| translation of space                                                                         | 32 |

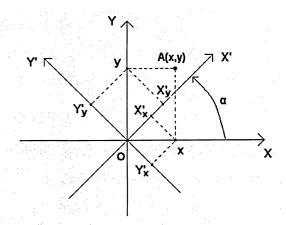

| Figure 3-3. Rotation in 2-D plane.                                                           | 33 |

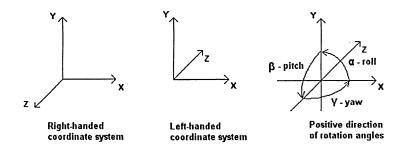

| Figure 3-4. Right- and Left-handed coordinate systems and positive direction of rotation     |    |

| angles                                                                                       | 34 |

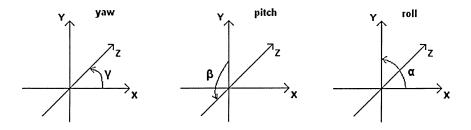

| Figure 3-5. Three consecutive rotations: yaw – pitch – roll                                  | 34 |

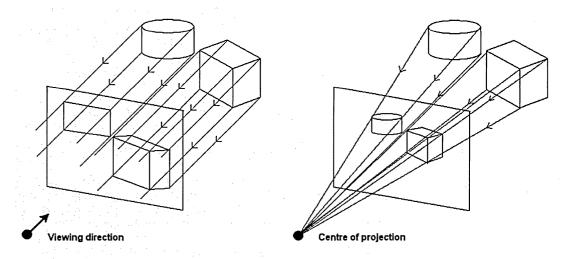

| Figure 3-6. Parallel and perspective projection schemes.                                     | 37 |

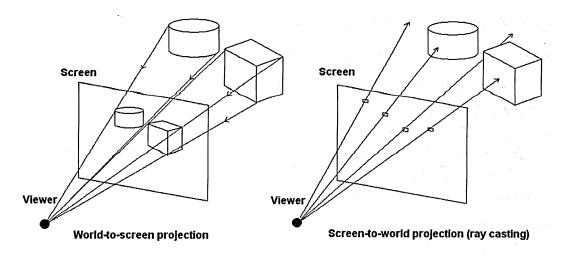

| Figure 3-7. Two types of projection methods: world-to-screen and screen-to-world             | 38 |

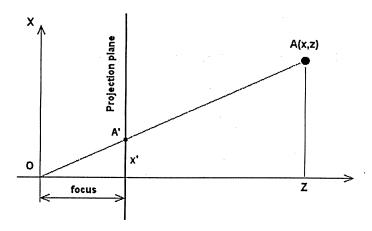

| Figure 3-8. Geometry of perspective projection.                                              | 38 |

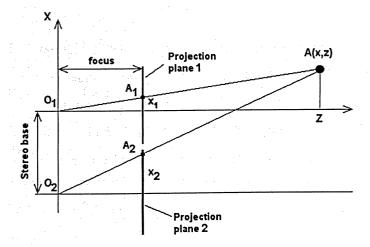

| Figure 3-9. Geometry of perspective projection for stereo vision.                            | 39 |

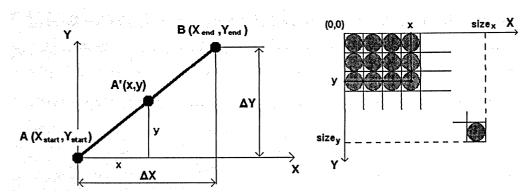

| Figure 3-10. A line segment on the projection plane and image bitmap layout                  | 41 |

| Figure 3-11. Line rasterizing for different values of the slope ratio 'a'                    | 41 |

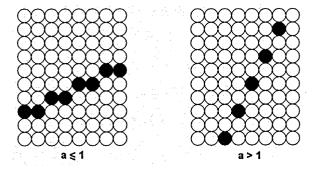

| Figure 3-12. Bresenham's algorithm: the line passing through the pixel grid                  | 42 |

| Figure 3-13. Bresenham's algorithm                                                           | 44 |

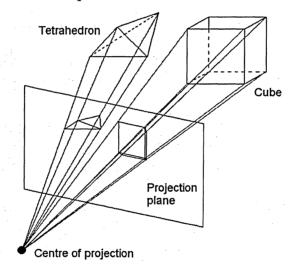

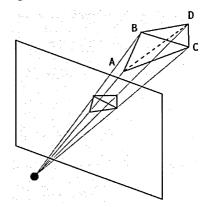

| Figure 3-14. Objects in 3-D space and their perspective projection views                     | 45 |

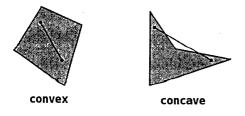

| Figure 3-15. Convex and concave polygons                                                     | 46 |

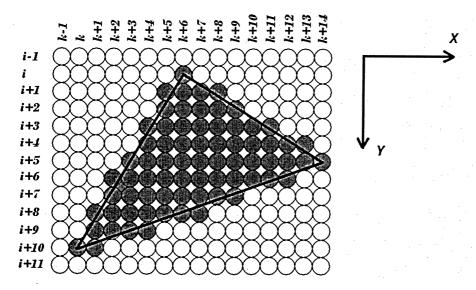

| Figure 3-16. Rasterized triangle representation                                              | 46 |

| Figure 3-17. Hidden surfaces illustration.                                                   | 47 |

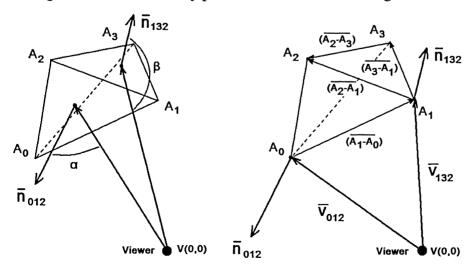

| Figure 3-18. Visible and non-visible surfaces: back-face culling determination technique.    | 48 |

| Figure 3-19. A design-oriented approach to system implementation                             | 52 |

| Figure 3-20. System architecture design process stages.                                      | 52 |

| Figure 3-21. A synthesis-oriented approach to system implementation                          | 53 |

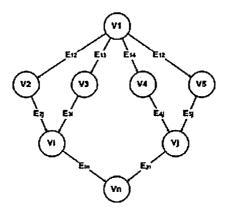

| Figure 3-22. Sequencing Graph (or Data Flow Graph) presentation                              |    |

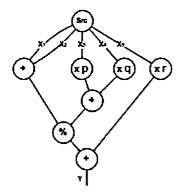

| Figure 3-23. DFG for the example task                                                        |    |

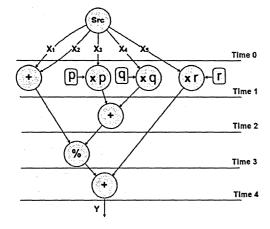

| Figure 3-24. Scheduled DFG.                                                                  |    |

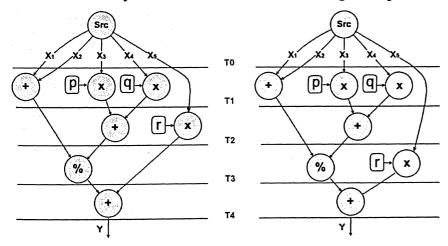

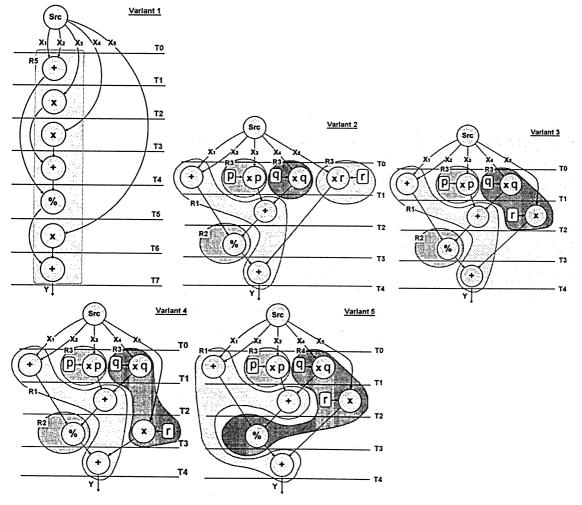

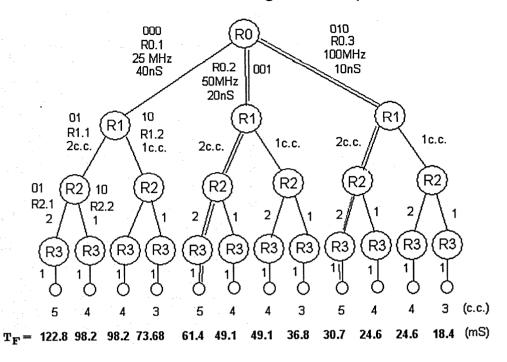

| Figure 3-25. Possible variants of scheduling.                                                |    |

| Figure 3-26. Variants of constrained scheduling and binding.                                 |    |

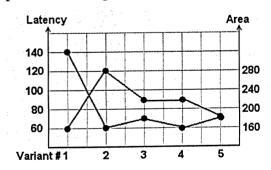

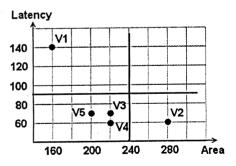

| Figure 3-27. Design space for the system.                                               | .57        |

|-----------------------------------------------------------------------------------------|------------|

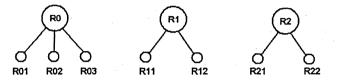

| Figure 3-28. Variants of the resources.                                                 |            |

| Figure 3-29. Design space as an Architecture Configuration Graph (ACG)                  |            |

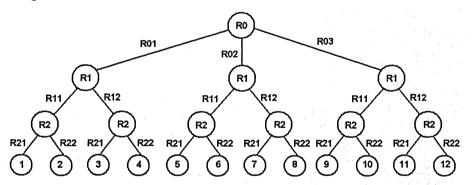

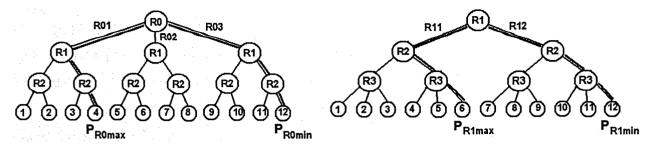

| Figure 3-30. "Minimax" method for hierarchical arrangement of ACG                       |            |

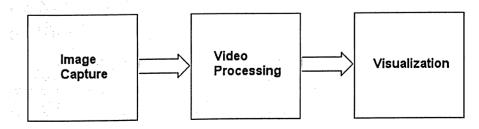

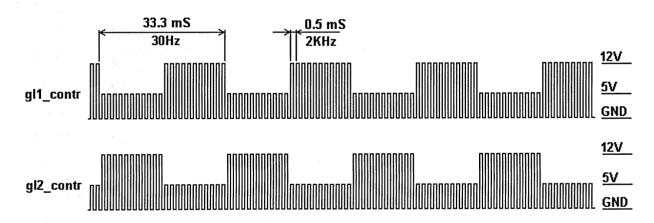

| Figure 4-1. Real-time stereo vision system block diagram                                |            |

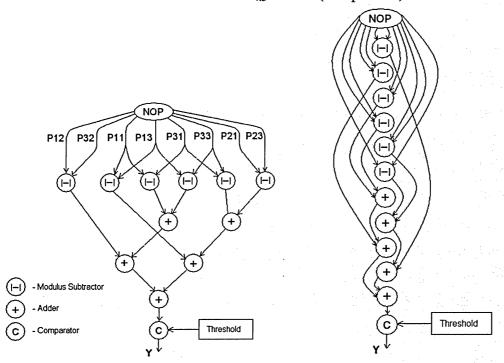

| Figure 4-2. Sobel edge detection algorithm specification                                |            |

| Figure 4-3. Two versions of the DFG for Sobel algorithm implementation (hardware and    |            |

| GPP based).                                                                             | .64        |

| Figure 4-4. Three variants of DFG for Sobel algorithm architecture                      |            |

| Figure 4-5. Architecture Configuration Graph for Sobel algorithm implementation         |            |

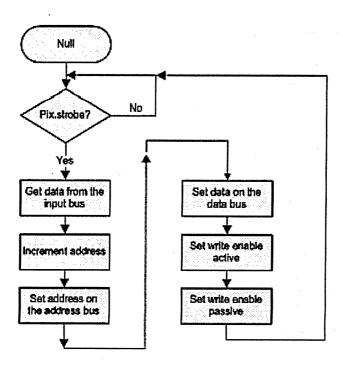

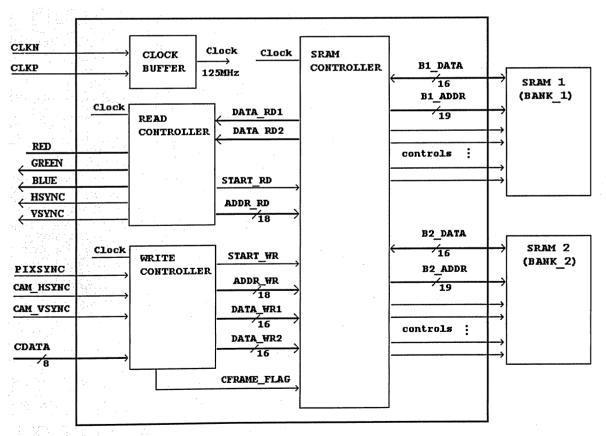

| Figure 4-6. Data flow for the capture system                                            |            |

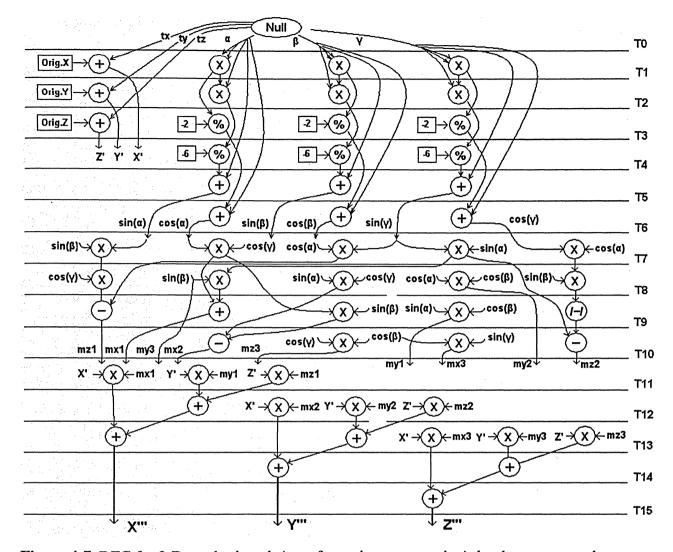

| Figure 4-7. DFG for 3-D synthesis task (transformation computation), hardware approach. |            |

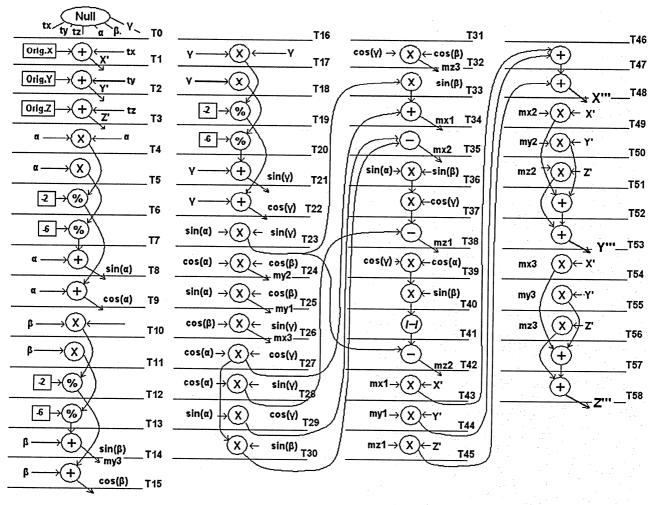

| Figure 4-8. DFG for 3-D synthesis task (transformation computation), GPP approach       |            |

| Figure 4-9. Block diagram of the stereo vision system                                   |            |

| Figure 4-10. Image Capture Module block diagram.                                        |            |

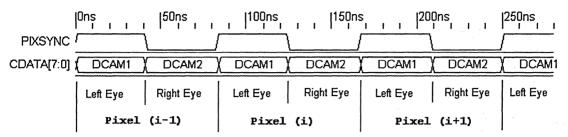

| Figure 4-11. ICM output data format.                                                    |            |

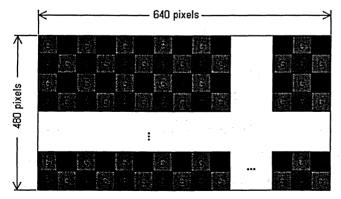

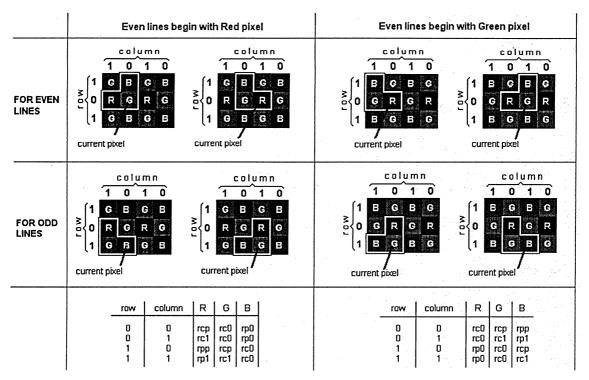

| Figure 4-12. Bayer color pattern for the active CMOS sensor area                        |            |

| Figure 4-13. Video Processing Subsystem block diagram                                   |            |

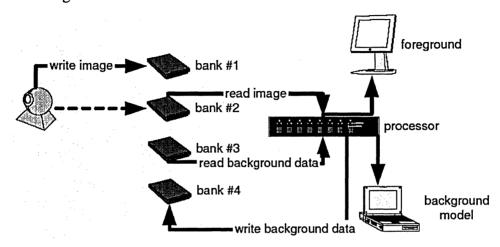

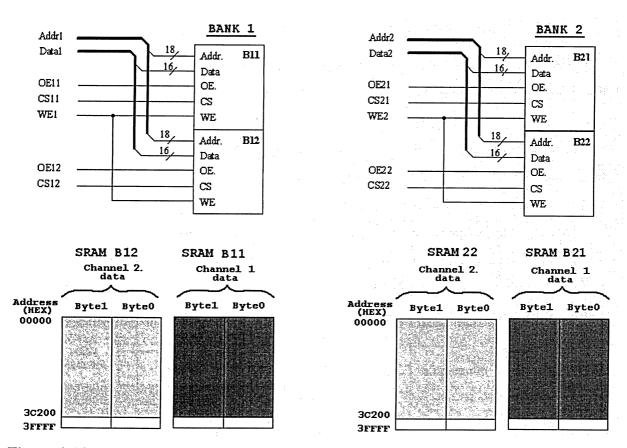

| Figure 4-14. External memory architecture and utilization.                              |            |

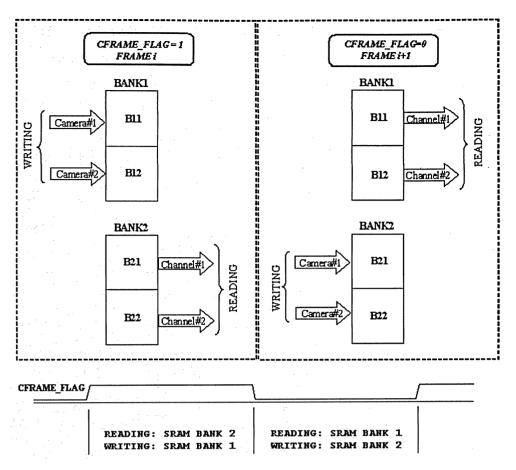

| Figure 4-15. Memory banks operational phases definition                                 |            |

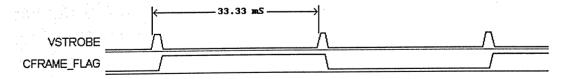

| Figure 4-16. CFRAME_FLAG signal definition.                                             |            |

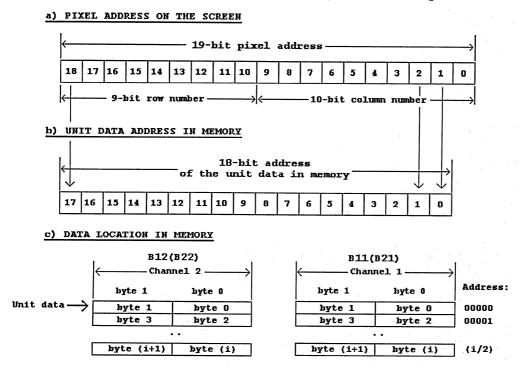

| Figure 4-17. Pixel address on the screen and location in memory                         |            |

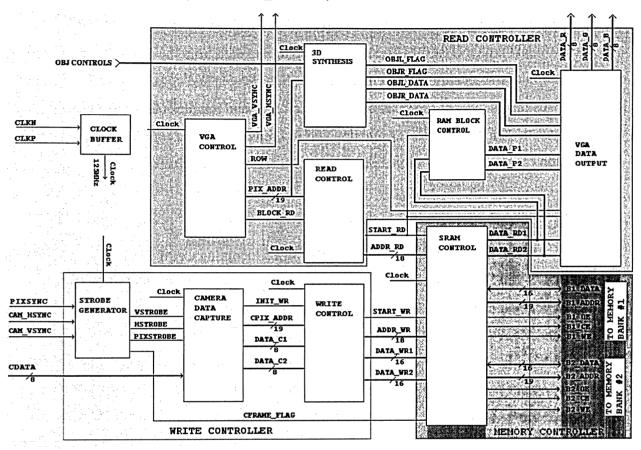

| Figure 4-18. Video Processing Module block diagram                                      |            |

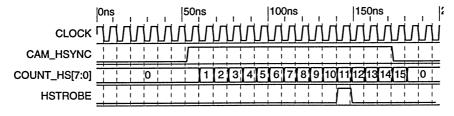

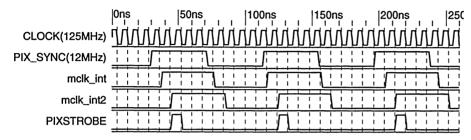

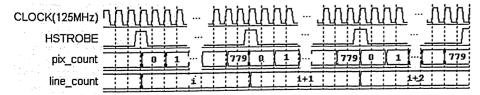

| Figure 4-19. STROBE_GEN IP core: HSTROBE signal generation.                             |            |

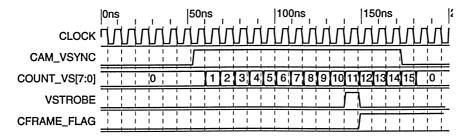

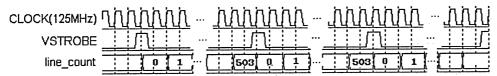

| Figure 4-20. STROBE_GEN IP core: VSTROBE and CFRAME_FLAG signals generation             |            |

|                                                                                         |            |

| Figure 4-21. STROBE_GEN IP core: PIXSTROBE signal generation                            |            |

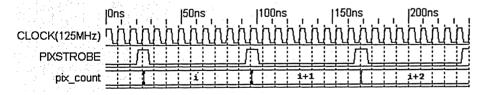

| Figure 4-22. CDATA_CAPTURE IP core: pixels counting                                     |            |

| Figure 4-23. CDATA_CAPTURE IP core: lines counting                                      |            |

| Figure 4-24. CDATA_CAPTURE IP core: lines counter reset.                                |            |

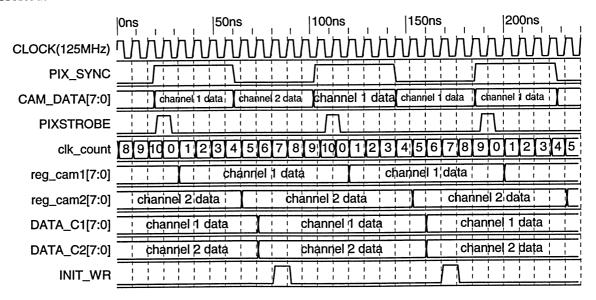

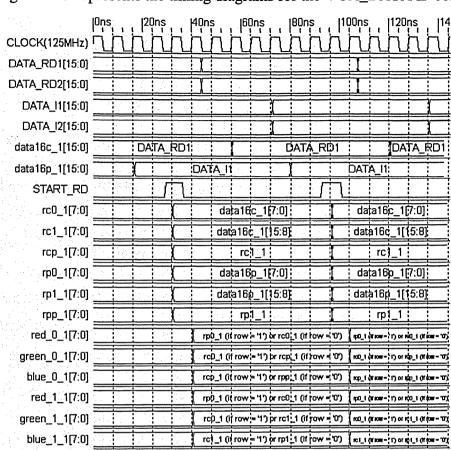

| Figure 4-25. CDATA_CAPTURE IP core: timing diagram                                      |            |

| Figure 4-26. WR_CONTR IP core: timing diagram.                                          |            |

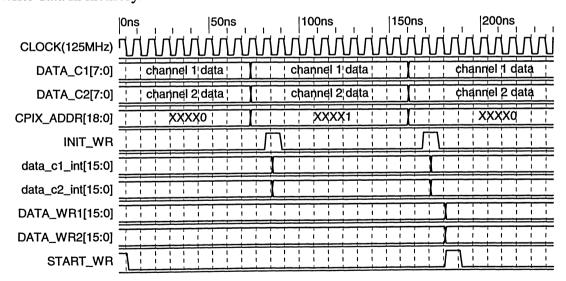

| Figure 4-27. VGA timing requirements.                                                   |            |

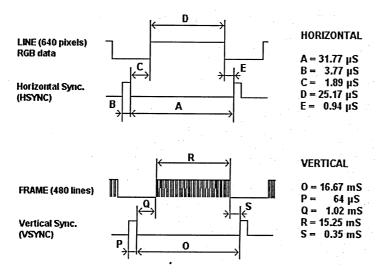

| Figure 4-28. RD_CONTROL IP core: timing diagram                                         |            |

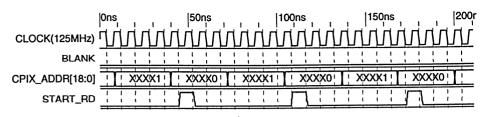

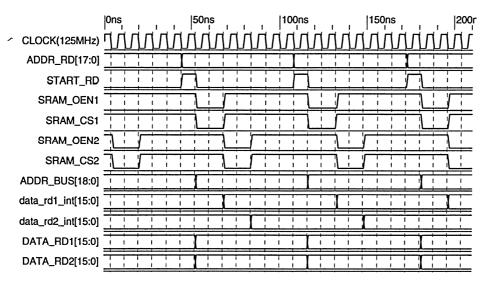

| Figure 4-29. MEMCHIP_CONTR IP core: timing diagram, READ operation                      |            |

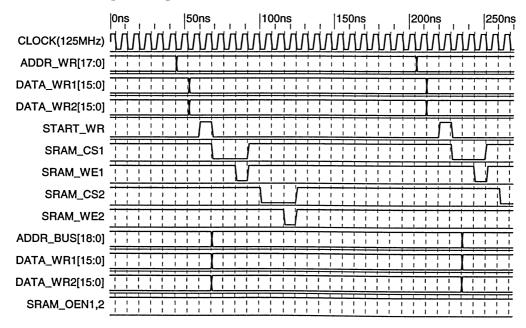

| Figure 4-30. MEMCHIP_CONTR IP core: timing diagram, WRITE operation                     |            |

| Figure 4-30. MEMCHIF_CONTR IF core: timing diagram, wRITE operation                     |            |

|                                                                                         |            |

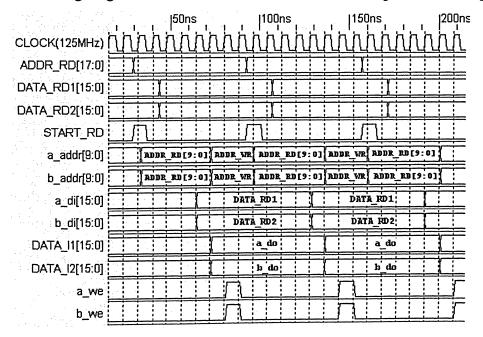

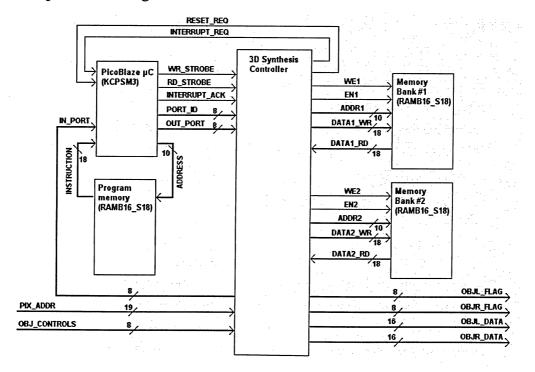

| Figure 4-32. 3D Synthesis IP core schematics.                                           |            |

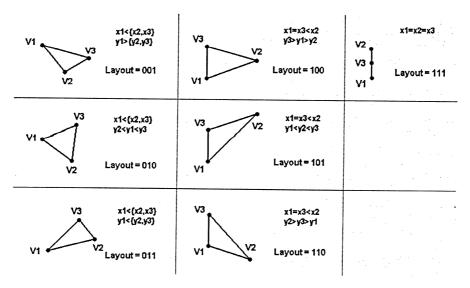

| Figure 4-33. Possible layouts of elementary triangle on the projection plane            |            |

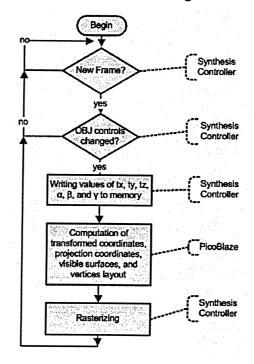

| Figure 4-34. 3D SYNTHESIS module functionality algorithm                                |            |

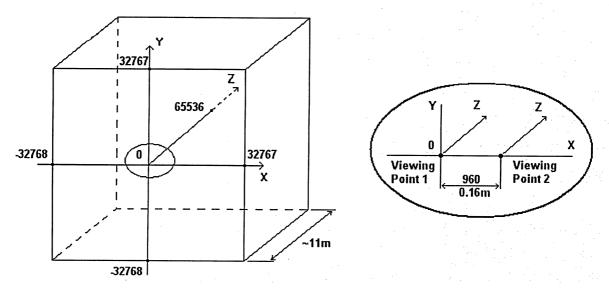

| Figure 4-35. Virtual object space configuration.                                        | . 94       |

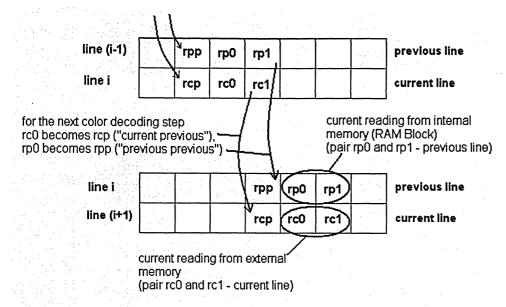

| Figure 4-36. Data reading and internal registers assignment scheme.                     | . YJ       |

| Figure 4-37. Color assignment scheme                                                    | 90.<br>20. |

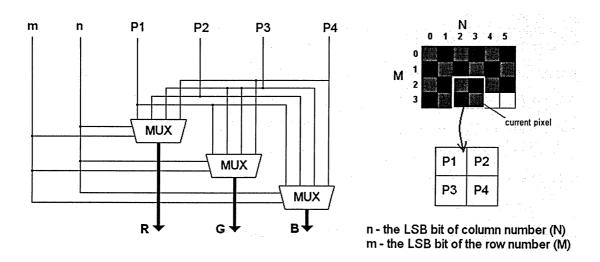

| Figure 4-38. Implementation of the multiplexer-based color assignment algorithm         | . 90       |

| Figure 4-39. VGA_DATA IP core: timing diagram.                                          | .9/        |

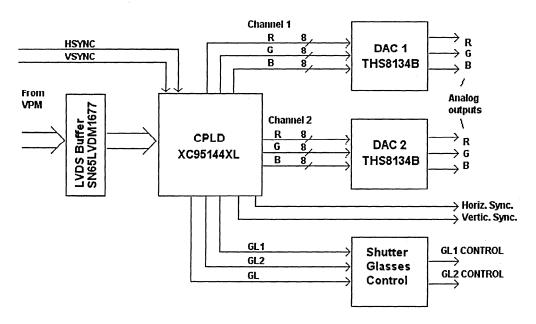

| Figure 4-40. Block diagram of the Visualization Output Module                           | , 98       |

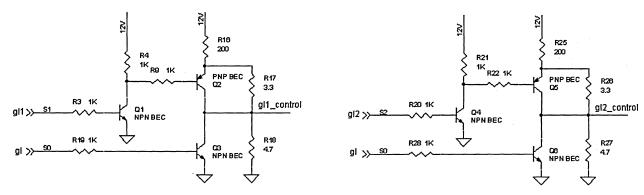

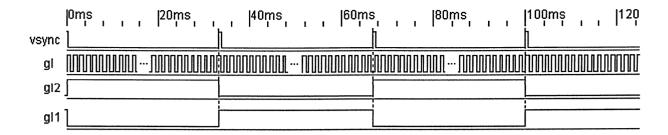

| Figure 4-41. Shutter Glasses Control subsystem schematics                  | 98  |

|----------------------------------------------------------------------------|-----|

| Figure 4-42. Control signals for shutter glasses generated by CPLD.        | 99  |

| Figure 4-43. Shutter Glasses analog control signals: timing diagram        | 99  |

| Figure 5-1. Experimental set-up for real-time stereo visualization         | 101 |

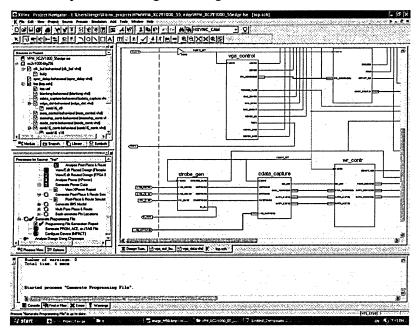

| Figure 5-2. Designing system with Xilinx' ISE ver.7.1.04i                  | 102 |

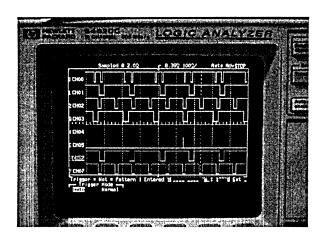

| Figure 5-3. Debugging system with HP54620C logic analyzer                  | 102 |

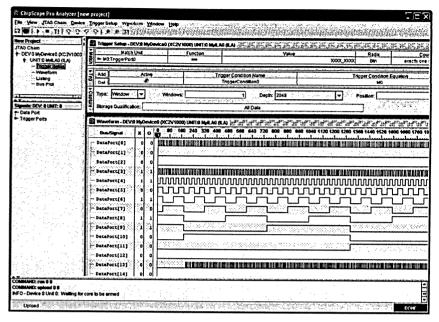

| Figure 5-4. Debugging of the system with the Xilinx' ChipScope Pro tool    | 103 |

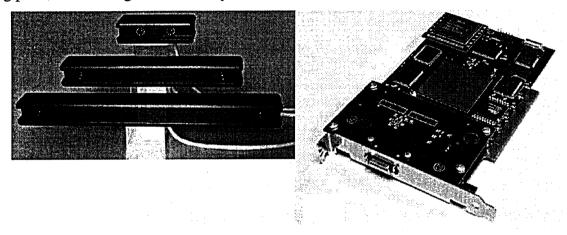

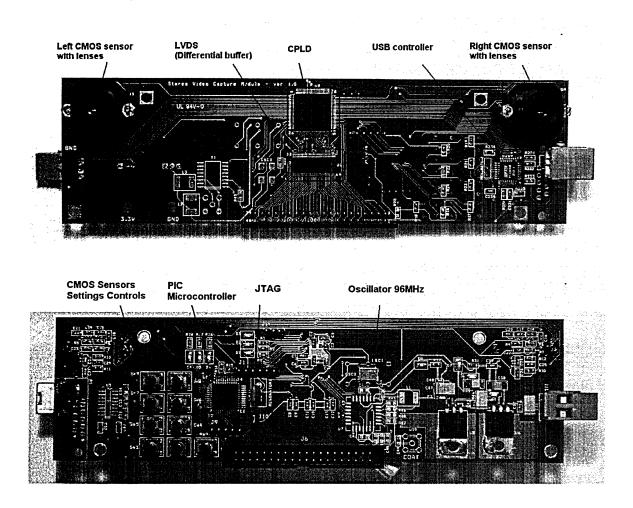

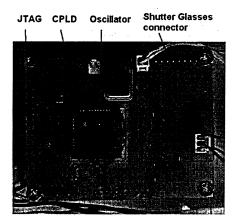

| Figure 5-5. Photographic picture of the ICM (front and back sides)         | 104 |

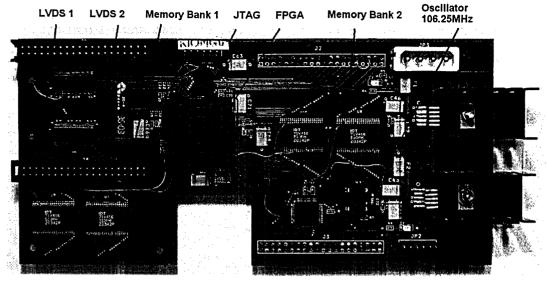

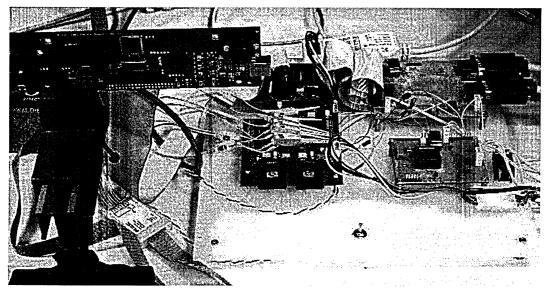

| Figure 5-6. Photographic picture of the Reconfigurable FPGA-based platform | 105 |

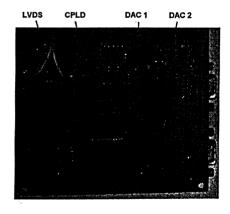

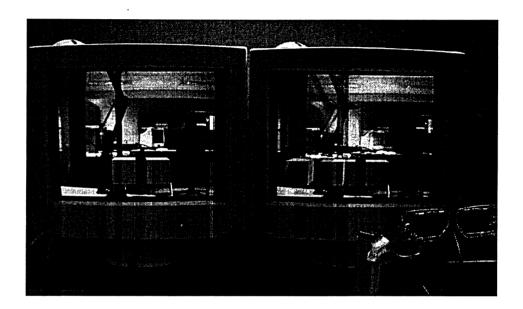

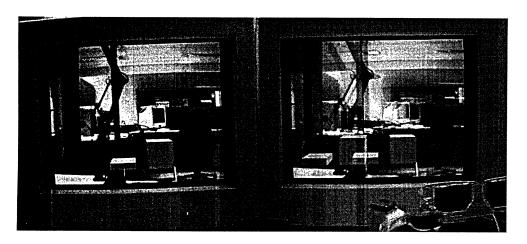

| Figure 5-7. Photographic picture of the Visualization Output Module        | 105 |

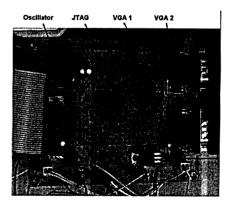

| Figure 5-8. Photographic picture of the Shutter Glasses control sub-module | 106 |

| Figure 5-9. General layout of the stereo vision system: photographic image | 106 |

| Figure 5-10. Real-time images visualization: both virtual buttons released | 107 |

| Figure 5-11. Real-time images visualization: one button pressed            | 108 |

| Figure 5-12. Real-time edge detection image visualization                  | 109 |

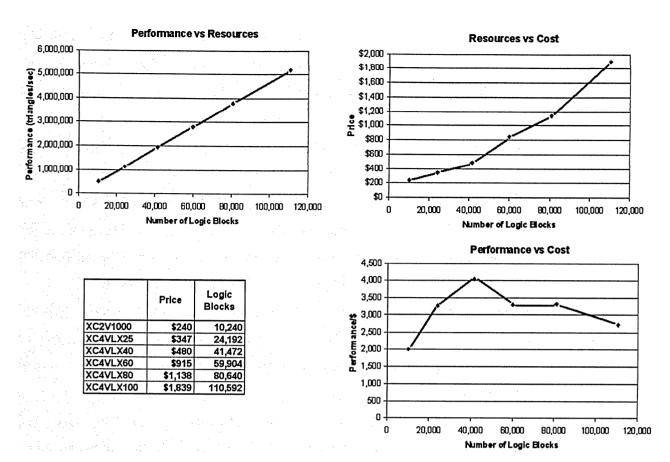

| Figure 5-13. Performance vs. Cost analysis                                 | 113 |

#### List of tables:

| Table 2-1. Summary of existing hardware-based real-time video systems and their basic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26   |

| Table 3-1. Number of arithmetic operations required for translation transformation per                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| vertex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33   |

| Table 3-2. Number of arithmetic operations required for rotation transformation computat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| per vertex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36   |

| Table 3-3. Number of arithmetic operations required for perspective projection computations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| per vertex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40   |

| Table 3-4. Number of arithmetic operations required for the Bresenham's algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44   |

| Table 3-5. Data structure (array) for storing triangle's pixel lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47   |

| Table 3-6. Number of arithmetic operations required for the back-face culling algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| implementation, per each surface of an object                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 50   |

| Table 4-1. Estimation of computational time for a tetrahedron image synthesis using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| PicoBlaze computational resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72   |

| Table 4-2. HW-SW partitioning of the tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74   |

| Table 4-3. Structure of data in memory for a 3-D object                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91   |

| Table 4-4. Data format of the rasterized line segments and surfaces in memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 93   |

| Table 5-1. Design overview for the stereo vision system generated by ISE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .110 |

| Table 5-2. Modern FPGA resources: overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .111 |

| I WOLD O MI I TO COLLEGE OF THE COLL |      |

#### **List of Acronyms**

3-D – Three Dimensional

ACG - Architecture Configuration Graph

ASIC - Application Specific Integrated Circuit

CISC – Complex Instruction Set Computer (or Computing)

CLB - Configurable Logic Block

CPU - Central Processor Unit

CPLD - Complex Programmable Logic Device

DFG – Data Flow Graph

DSP - Digital Signal Processor

FPGA - Field Programmable Gate Array

GPP – General Purpose Processor

HDL - Hardware Description Language

ICM - Image Capture Module

ILP - Instruction Level Parallelism

IOB - Input Output Block

IP Core – Intellectual Property Core

ISE – Integrated Software Environment

LSB - Lowest Significant Bit

LUT – Look-Up Table

MSB – Most Significant Bit

LCD – Liquid Crystal Display

LVDS - Low Voltage Differential Signal

PCB - Printed Circuit Board

PLD – Programmable Logic Device

RISC – Reduced Instruction Set Computer (or Computing)

RTR – Real-Time Reconfigurability

SOC - System-On-Chip

VGA - Video Graphics Array

VHDL – Very High Speed Integrated Circuits (VHSIC) Hardware Description Language

VOM – Visualization Output Module

VPM – Video Processing Module

#### 1. INTRODUCTION

#### 1.1. Motivation

Visual information plays a special role in perception of the surrounding world by humans. Still and motion images are considered the most important informative sources. Through vision we perceive various information and knowledge, directions and instructions for all kinds of our activities.

Special vision systems are widely used in many areas of human activity: in medical service and research, e.g. computer tomography systems (CT), magnetic resonance imaging (MRI), X-ray or ultrasound imaging systems, for telemedicine; in navigation systems for navy and aviation, for spacecrafts, submarines and Unmanned Autonomous Vehicles (UAV) incorporate sophisticated video systems built on the base of advanced image processing algorithms. Video systems play a special role in space exploration as it was demonstrated by the latest NASA's mission to the Mars started in 2004. The images of the Martian surface sent to the Earth by two autonomous rovers Spirit and Opportunity are hard to over-evaluate. Flight simulators provide virtual airplane cabin set-up and environment for training of pilots. Entertainment and art are based both on video and audio perception of a human.

The areas of application of real-time vision systems include also telematic systems used for remote control of manipulators operating in hazardous environment. It is very required for operating robotized manipulators in space, when the actual stereo scene is visualized in real-time and interactive virtual controls images are dynamically generated on the visualization device as well, thus making it possible for an astronaut not to look aside for activating a needed control button.

Video systems also play important role in industry, engineering and science, for example, for research of fast processes in chemistry and mechanics. High speed video recording is used for cars collision research to provide engineers with the information on how to improve a car design to reach better level of driving safety. It is also used in aerodynamics for study and research of airplanes flight characteristics in different environmental conditions and of new materials behavior under critical conditions.

Today's video systems provide possibility to visualize both real-time (or recorded) video and synthesized virtual three-dimensional graphical objects. Various captions, charts, diagrams and artificially created backgrounds are an integral part of modern TV broadcasting.

Different image processing algorithms and techniques are widely employed in today's cinema industry for creating scenes from other planets or prehistoric creatures.

Stereo vision systems provide more realistic view of the surrounding world or virtual reality than just "one-eye" view since scene depth information is there. Stereo vision techniques necessarily integrate two sources of video data, i.e. two video cameras which should be properly oriented in space to produce matched images. Panoramic vision systems are aimed to provide a realistic view of the scene with a very wide angle of view (up to 360°).

The main purpose of real-time multi-channel vision systems is to process in a certain way one or multiple video data streams. Data stream means that the data flow is homogenous and regular. Each unit data bears information just about the current elementary picture component (pixel) brightness. In general case, the system is doing the same operations over each coming pixel or over a group of coming pixels from the current scanning line or from a number of adjacent lines. It means that the computation can be performed in parallel and be deeply pipelined.

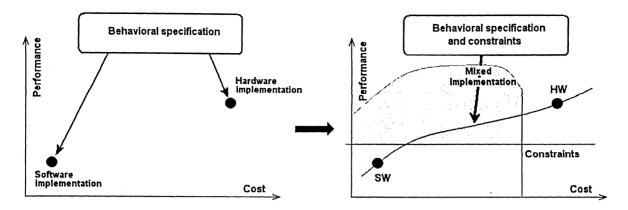

A typical approach for real-time vision systems design is that a kind of hybrid architecture is employed for implementation. On the one end of such a system are image sensors with configuring hardware based on PLD devices (CPLD or FPGA). This hardware also performs initial processing on incoming data to facilitate the interface between the data source (video cameras) and the main processing system. The main processing system is usually built on the base of a personal computer or high performance workstation, General Purpose Processor (GPP), Digital Signal Processor (DSP), or Application Specific Integrated Circuit (ASIC). For the visualization of real-time video and synthesized graphical objects the resources of a standard PC with a powerful graphic card are usually used.

The main advantage of using a GPP, as well as host workstation for image processing is that the task implementation migrates into the software design domain. It allows implementing sophisticated algorithms using traditional, and thus well developed, technique of sequencing programming. The evident drawback of this approach is that real-time processing is impossible in this case. A GPP based system is not fast enough to produce a processed unit data at the rate

of real-time data rate. For example, for the standard VGA resolution of 640 x 480 pixels and frame rate of 60 fps a system must output a processed pixel each 40nS. For a RISC microprocessor operating at the clock frequency of 200MHz a clock cycle takes 5nS. Even if it takes four clock cycles per one command execution, only two commands can be allocated within a time slot of 40nS. It's not enough just for reading data from memory. For real-time video systems GPP approach for data processing is not acceptable.

Using DSPs for image processing tasks can significantly facilitate various algorithms implementation, but deep pipelining and parallelism, as it is needed for stream data processing, can not be reached.

From the performance point of view using ASICs for image processing tasks gives the best results. But ASICs are very application specific devices destined only to mass production sector. For example, ASICs for graphic adapters are built on the base of parallel vector processor architecture. The performance of the modern graphic adapters is very impressive (for example, ATI's Radeon X1900 Series graphic adapter's core speed is 650MHz, it incorporates 48 pixel shader processors, 8 vertex shader processor and 256-bit 8-channel GDDR3 SDRAM [1]). But they are designed to perform only a particular processing task directed mostly to the games industry: generating highly realistic synthesized 3-D image. The operational frequencies for modern graphic processing ASICs are close to physical limits, and thus they need complex cooling systems. ASIC based systems are also not reconfigurable, their architecture is fixed. If a system needs to provide, for example, different resolution for different viewing angles, as it may be needed for panoramic vision systems, or to process two or more data streams as it's needed for stereo vision, a standard ASIC can't be used. For a multi-mode system a number of ASICs must be employed. In this case the chips must communicate to each other via PCB's copper traces and the resulting cross-talks limit the performance of the system. Even if a single chip's core can operate at the speed of 500MHz and above, the PCB limits the data rate by approximately 133MHz. For multiple-chip systems the power consumption increases and reliability falls. Besides, time-to-market for the ASIC design is significantly higher than for other approaches.

It means that for processing of a number of data streams which can change in time and which may require different processing algorithms to be applied on data streams, a system must provide high level of parallelism and reconfigurability, and has to be implemented within one

chip. So, the problem is that we are speaking about video systems that can incorporate several algorithms and several modes of each algorithm. This is the requirement for many applications nowadays (e.g. synthesis of complex virtual environments, MPEG 4, 7, 21 video compression, object recognition, etc.)