# A 10 GBPS 4-PAM CMOS SERIAL LINK TRANSMITTER WITH PRE-EMPHASIS

by

Minghai Li B.Eng, North University of China, China, 1996

A thesis

presented to Ryerson University

in partial fulfillment of the

requirement for the degree of

Master of Applied Science

in the Program of

Electrical and Computer Engineering.

Toronto, Ontario, Canada, 2006

© Minghai Li, 2006

PROPERTY OF RYERSON UNIVERSITY LIBRARY

UMI Number: EC53600

### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

UMI Microform EC53600

Copyright 2009 by ProQuest LLC

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

### **Author's Declaration**

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Signature

V

p

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

Signature

## **Instructions on Borrowers**

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

### A 10 GBPS 4-PAM CMOS SERIAL LINK TRANSMITTER WITH PRE-EMPHASIS

Master of Applied Science

2006

Minghai Li

Electrical and Computer Engineering

Ryerson University

### Abstract

This thesis presents the design of 10 Gbps 4-PAM CMOS serial link transmitters. A new area-power efficient fully differential CMOS current-mode serial link transmitter with a proposed 2/4-PAM signaling configuration and a new pre-emphasis scheme is presented. The pre-emphasis in the analog domain and the use of de-emphasis approach decrease pre-emphasis power and chip area. The high-speed operation of the transmitter is achieved from the small voltage swing of critical nodes of the transmitter, shunt peaking with active inductors, multiplexing-at-input approach, the distributed multiplexing nodes, and the low characteristic impedance of the channels.

The fully differential and bidirectional current-mode signaling minimizes the noise injected to the power and ground rails and the electromagnetic interference exerted from the channels to neighboring devices. A PLL containing a proposed five-stage VCO is implemented to generate multi-phase on-chip clocks. The proposed VCO minimizes the phase noise by keeping a constant rising and falling time.

Simulation results demonstrate that the current received at the far end of a 10 cm FR-4 microstrip has a 4-PAM current eye width of 185 ps and eye height of 1.21 mA. It consumes 57.6 mW power with differential delay block, or 19.2 mW power with inverter buffer chain. The total transistor area of the transmitter is 26.845  $\mu m^2$  excluding the delay block.

## Acknowledgments

I would like to express my gratitude to Dr. Fei Yuan for being an outstanding advisor and excellent professor. His constant encouragement, support, and valuable suggestions made this work possible and successful. He has been everything one could want in an advisor.

I am deeply indebted to my defense committee members Dr. Alagan Anpalagan, Dr. Xavier Fernando, and Dr. Gul Khan for their time and effort in reviewing this work. My thanks also go to Mr. Jason Naughton and Mr. Daniel Giannitelli for their support and help on Cadence and computer systems.

I have enjoyed a warm atmosphere in MCS group and valuable discussion with my colleagues in the research group. Special thanks go to Jean Jiang and Bendong Sun who helped me a lot in the early stage of my research.

I am deeply and forever indebted to my parents for their love, support and encouragement through my entire life. It is certainly hard to find a word to express my gratitude to my wife Elyn, who provides me with a constant support and trust.

# Contents

| 1 Introduction |     |        | ion                                                | 1          |

|----------------|-----|--------|----------------------------------------------------|------------|

|                | 1.1 | Motiv  | ration                                             | 1          |

|                | 1.2 | Contr  | ibutions                                           | 4          |

|                | 1.3 | Organ  | nization                                           | $\epsilon$ |

| 2              | An  | Overv  | riew of Serial Links                               | 7          |

|                | 2.1 | A Typ  | pical Serial Link Architecture                     | 7          |

|                | 2.2 | Signal | ling                                               | 9          |

|                |     | 2.2.1  | Voltage-Mode Signaling                             | 9          |

|                |     | 2.2.2  | Current-Mode Signaling                             | 10         |

|                | 2.3 | Limita | ations                                             | 11         |

|                |     | 2.3.1  | Electronic Limitations                             | 11         |

|                |     | 2.3.2  | Transmission Medium Limitations                    | 14         |

|                |     | 2.3.3  | Multi-Phase Clock Generation                       | 16         |

|                | 2.4 | Design | Techniques                                         | 17         |

|                |     | 2.4.1  | Voltage Mode and Current Mode                      | 17         |

|                |     | 2.4.2  | Multi-Level Pulse Amplitude Modulation             | 19         |

|                |     | 2.4.3  | Transmitter Pre-emphasis and Receiver Equalization | 19         |

|                |     | 2.4.4  | Active Inductors                                   | 22         |

|                | 2.5 | Summ   | ary                                                | 24         |

| 3 | High-speed Serial Link Transmitter Design    |                                           |                                                            | <b>2</b> 5 |  |

|---|----------------------------------------------|-------------------------------------------|------------------------------------------------------------|------------|--|

|   | 3.1                                          | 1 An overview of Serial Link Transmitters |                                                            |            |  |

|   |                                              | 3.1.1                                     | Transmitter with Inverter Driver                           | 27         |  |

|   |                                              | 3.1.2                                     | Transmitter with LVDS Driver                               | 28         |  |

|   |                                              | 3.1.3                                     | Transmitter with Open-Drain Driver                         | 29         |  |

|   |                                              | 3.1.4                                     | Transmitter with Class AB Driver                           | 30         |  |

|   | 3.2                                          | .2 10 Gbps Current-Mode Transmitters      |                                                            |            |  |

|   |                                              | 3.2.1                                     | $V_{DD}$ -Insensitive Transmitter                          | 31         |  |

|   |                                              | 3.2.2                                     | 4-PAM Transmitter with Current-Mirror Driver               | 36         |  |

|   |                                              | 3.2.3                                     | 2/4-PAM Transmitter with Class AB Driver                   | 46         |  |

|   | 3.3                                          | Summ                                      | ary                                                        | 47         |  |

| 4 | Tra                                          | $_{ m nsmitt}$                            | er Pre-emphasis                                            | 50         |  |

|   | 4.1 Pre-emphasis - A State-of-the-Art Review |                                           |                                                            |            |  |

|   |                                              | 4.1.1                                     | Pre-emphasis in Digital Domain                             | 52         |  |

|   |                                              | 4.1.2                                     | Pre-emphasis in Analog Domain                              | 53         |  |

|   |                                              | 4.1.3                                     | Pre-emphasis Using Pseudo-nMOS Multiplexer                 | 54         |  |

|   | 4.2                                          | Power                                     | -Area Efficient Pre-emphasis in Analog Domain              | 55         |  |

|   |                                              | 4.2.1                                     | Power-Area Efficient Current-Mode Pre-Emphasis Transmitter | 56         |  |

|   |                                              | 4.2.2                                     | The Multiplexer                                            | 57         |  |

|   |                                              | 4.2.3                                     | The Pre-amplifier and Driver                               | 59         |  |

|   |                                              | 4.2.4                                     | The Pre-emphasis                                           | 62         |  |

|   |                                              | 4.2.5                                     | 4-PAM Current-Mode Pre-Emphasis Transmitter                | 65         |  |

|   |                                              | 4.2.6                                     | Simulation Results                                         | 66         |  |

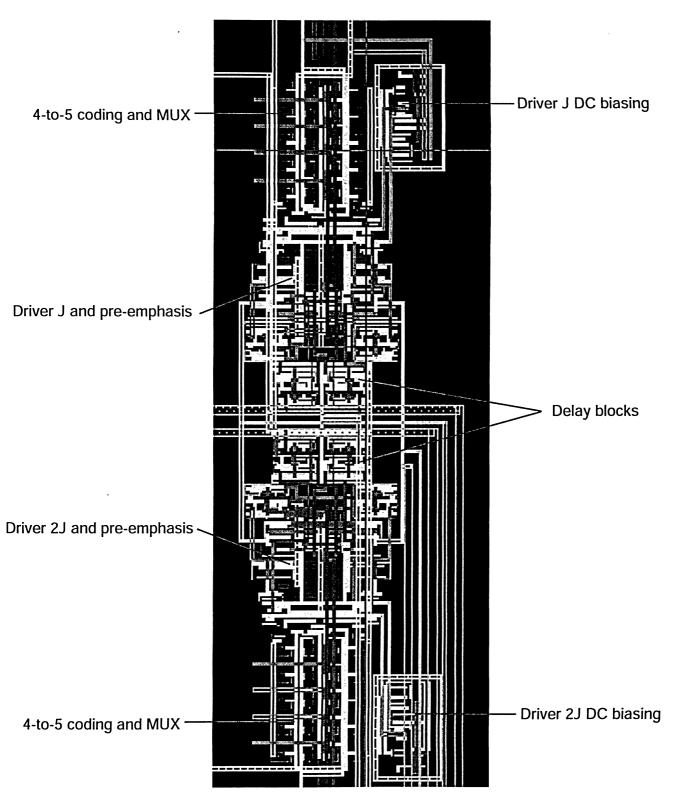

|   |                                              | 4.2.7                                     | Transmitter Layout                                         | 70         |  |

|   | 4.3                                          | Summ                                      | nary                                                       | 71         |  |

| 5 | Mu                                           | lti-pha                                   | se Clock Generation                                        | <b>7</b> 4 |  |

|   | 5.1                                          | Phase                                     | -Locked Loops                                              | 74         |  |

|    |       | 5.1.1   | Loop Dynamics                 | . 75 |

|----|-------|---------|-------------------------------|------|

|    | 5.2   | Buildi  | ng Blocks                     | . 77 |

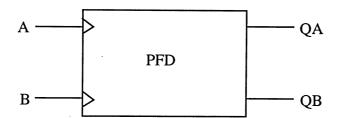

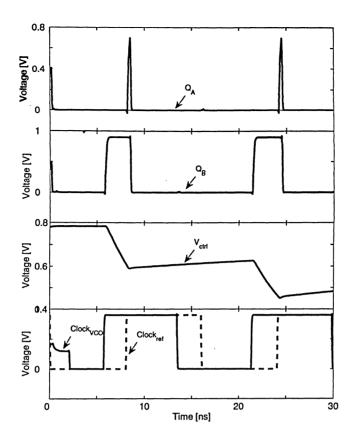

|    |       | 5.2.1   | Phase-Frequency Detector      | . 77 |

|    |       | 5.2.2   | Charge Pump                   | . 78 |

|    |       | 5.2.3   | Voltage-Controlled Oscillator | . 81 |

|    |       | 5.2.4   | Frequency Divider             | . 85 |

|    |       | 5.2.5   | Simulation Result             | . 86 |

|    | 5.3   | Summ    | ary                           | . 86 |

| 6  | Con   | clusion | ns                            | 89   |

|    | 6.1   | Conclu  | usions                        |      |

|    | 6.2   |         | e Work                        |      |

| Bi | bliog | raphy   |                               | 92   |

| Gl | ossar | ·y      |                               | 98   |

# List of Tables

| 2.1 | Skin depth of some interconnects at 100 MHz and 5 GHz                         | 15 |

|-----|-------------------------------------------------------------------------------|----|

| 3.1 | Output impedance of inverter drivers                                          | 28 |

| 3.2 | Comparison of none-saturated, saturated class AB, and open drain transmitter. | 38 |

| 3.3 | Output of 2-bit DACs and transmitter                                          | 39 |

| 3.4 | Output of 4-PAM transmitter                                                   | 46 |

| 4.1 | 4-PAM current-mode transmitter with pre-emphasis                              | 66 |

| 4.2 | Circuit parameters ( $L$ =0.13 $\mu m$ is used for all transistors)           | 67 |

| 4.3 | Performance of transmitter                                                    | 71 |

# List of Figures

| 1.1  | Backplane system cross-section indicating different sections of the signaling  |    |

|------|--------------------------------------------------------------------------------|----|

|      | path                                                                           | 2  |

| 1.2  | The response of a FR4 cable to a 100ps wide pulse                              | 3  |

| 1.3  | The effect of inter-symbol interference                                        | 3  |

| 1.4  | Pulse response from a pre-emphasized transmitter                               | 4  |

| 1.5  | An example of 4-PAM signaling symbols                                          | 5  |

| 2.1  | Structure of serial links                                                      | 8  |

| 2.2  | Voltage-mode signaling scheme.                                                 | 9  |

| 2.3  | Voltage at the far end of a 4-ns line when a logic level "1" is applied at the |    |

|      | near end of the cable                                                          | 10 |

| 2.4  | Current-mode signaling scheme                                                  | 10 |

| 2.5  | (a) Reduction EMI with bi-directional signaling scheme, (b) EMI in a single-   |    |

|      | ended signaling scheme.                                                        | 11 |

| 2.6  | Eye diagram showing limitations of bit time                                    | 12 |

| 2.7  | The noise sources in a typical PLL                                             | 13 |

| 2.8  | Lumped LCRG model of transmission line                                         | 14 |

| 2.9  | Skin effect of transmission lines                                              | 15 |

| 2.10 | Frequency dependance of cable loss                                             | 16 |

| 2.11 | Clock generation using a 3-stage ring oscillator                               | 17 |

| 2.12 | EMI cancellation in LVDS current-mode driver                                   | 18 |

| 2.13 | Transmitter pre-emphasis and receiver equalization.                            | 20 |

| 2.14 | Effect of 3-tap pre-emphasis, $a_1, a_2$ and $a_3$ are the pre-emphasis coefficients                                                                                               | 20 |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

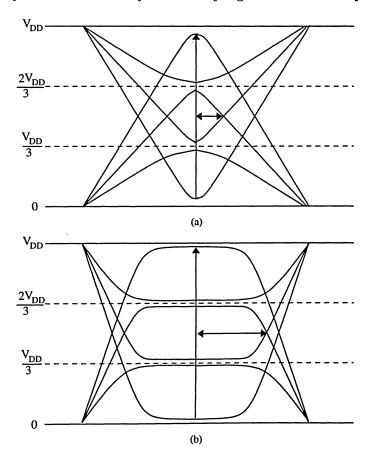

| 2.15 | 4-PAM eye diagrams, a) slow transition, b) sharp transition                                                                                                                        |    |  |

| 2.16 | Active inductor and its small-signal equivalent circuit. $g_m$ , $C_{gs}$ and $C_{gd}$ are                                                                                         |    |  |

|      | transistors' trans-conductance, gate-source and gate-drain capacitances, re-                                                                                                       |    |  |

|      | spectively, $\mathcal{C}_L$ is the total capacitance associated with the driving node                                                                                              | 23 |  |

| 2.17 | (a) Active inductor equivalent circuit, (b) active inductor bode plot                                                                                                              | 24 |  |

| 3.1  | (a) Voltage-mode transmitter. (b) Current-mode transmitter                                                                                                                         | 26 |  |

| 3.2  | Transmitter with inverter driver                                                                                                                                                   | 27 |  |

| 3.3  | Transmitter with LVDS driver                                                                                                                                                       | 28 |  |

| 3.4  | Transmitter with open drain driver                                                                                                                                                 | 29 |  |

| 3.5  | Transmitter with class AB driver                                                                                                                                                   | 30 |  |

| 3.6  | Full rail-to-rail N-to-1 multiplexer with inductive shunt peaking. $W_S =$                                                                                                         |    |  |

|      | $\overline{W}_S = 10 \ \mu\text{m}, \ W_{LP} = \overline{W}_{LP} = 3 \ \mu\text{m}, \ W_{LN} = \overline{W}_{LN} = 1.5 \ \mu\text{m}, \ W_{(N-1)} = W_{(N-2)} = 1.5 \ \mu\text{m}$ |    |  |

|      | $W_{(N-3)}=2~\mu{\rm m},~R_{in}=7~K\Omega,~L=0.13~\mu{\rm m}$ is used for all transistors                                                                                          | 32 |  |

| 3.7  | Class AB driver. Circuit parameters : $W_{a1}=W_{a2}\!=\!5~\mu\mathrm{m},~W_{a3}=W_{a4}\!=\!10$                                                                                    |    |  |

|      | $\mu \text{m},  W_{N} = 5  \mu \text{m},  W_{P} = 10  \mu \text{m},  W_{DN} = 10  \mu \text{m},  W_{DP} = 10  \mu \text{m},  R_{a1} = R_{a1} = 4  K\Omega,$                        |    |  |

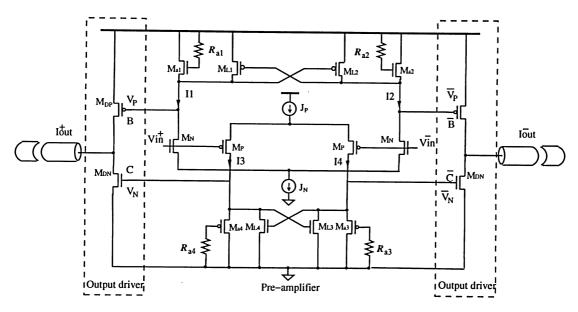

|      | $R_{a3}=R_{a4}{=}1~K\Omega,J_P{=}0.8$ mA, $J_N{=}1$ mA, $L{=}0.13~\mu{\rm m}$ for all transistors                                                                                  | 33 |  |

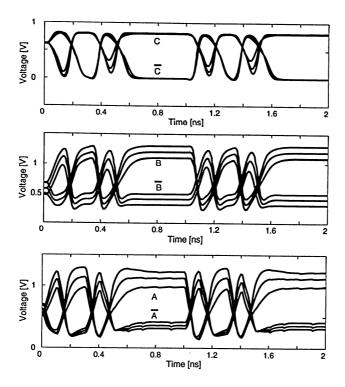

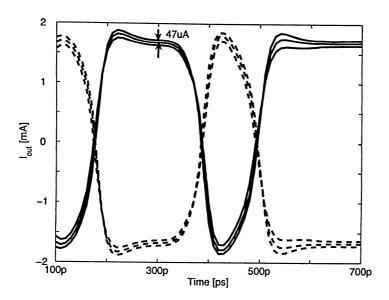

| 3.8  | Voltages of nodes $A, \overline{A}, B, \overline{B}, C, \overline{C}$ of the proposed transmitter. $V_{DD}$ is varied                                                              |    |  |

|      | from 1.1 V to 1.3 V with step 0.1 V                                                                                                                                                | 35 |  |

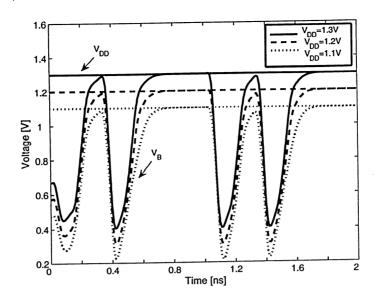

| 3.9  | Voltage at nodes $B$ and $\overline{B}$ of the proposed transmitter. $V_{DD}$ is varied from                                                                                       |    |  |

|      | 1.1 V to 1.3 V with step 0.1 V                                                                                                                                                     | 36 |  |

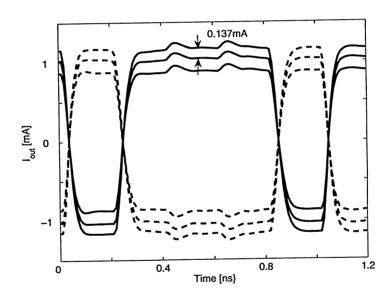

| 3.10 | Output current of the class AB serial link transmitter in [6]. $V_{DD}$ is varied                                                                                                  |    |  |

|      | from 1.1 V to 1.3 V with step 0.1 V                                                                                                                                                | 36 |  |

| 3.11 | Output current of the proposed transmitter. $V_{DD}$ is varied from 1.1 V to 1.3                                                                                                   |    |  |

|      | V with step 0.1 V                                                                                                                                                                  | 37 |  |

| 3.12 | Output current of the open-drain transmitter. $V_{DD}$ is varied from 1.1 V to                                                                                                     |    |  |

|      | 1.3 V with step 0.1 V                                                                                                                                                              | 37 |  |

| 3.13 | Received eyediagram after 5 cm FR4 cable                                                                                                                                           | 38 |  |

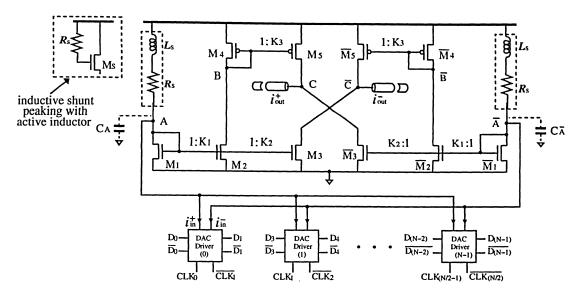

| 3.14 | N-to-1 fully differential 4-PAM current-mode transmitter with inductive shunt                                                                           |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | peaking. $W_1=\overline{W}_1=6~\mu\text{m},W_2=\overline{W}_2=9~\mu\text{m},W_3=\overline{W}_3=18~\mu\text{m},W_4=\overline{W}_4=15$                    |    |

|      | $\mu \text{m}$ , $W_5 = \overline{W}_5 = 30 \ \mu \text{m}$ , $K_1 = 3$ , $K_2 = 1.5$ , $K_3 = 2$ , $R_s = 500 \ \Omega$ , $L = 0.13 \ \mu \text{m}$ is |    |

|      | used for all transistors                                                                                                                                | 39 |

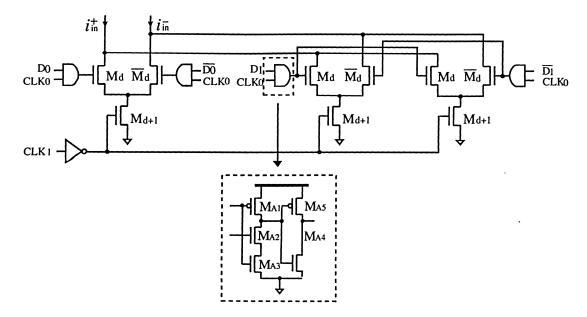

| 3.15 | Fully differential 2-bit digital-to-analog converter<br>(DAC) $W_d=\overline{W}_d$ =0.8 $\mu{\rm m},$                                                   |    |

|      | $W_{d+1} = 3 \ \mu\text{m}, \ W_{A1} = W_{A2} = W_{A3} = W_{A4} = 0.6 \ \mu\text{m}, \ W_{A5} = 1.5 \ \mu\text{m}. \ L = 0.13 \ \mu\text{m}$            |    |

|      | is used for all transistors                                                                                                                             | 40 |

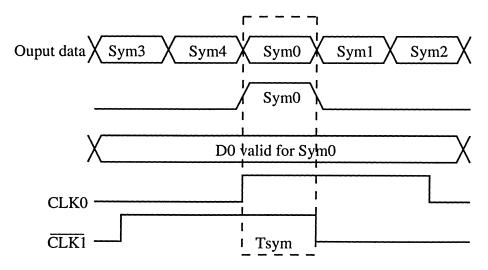

| 3.16 | Selection pulse generation                                                                                                                              | 40 |

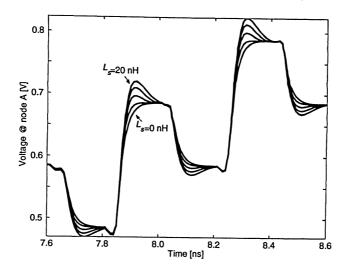

| 3.17 | Voltage at the multiplexing node $A$ with passive peaking inductors. The                                                                                |    |

|      | inductance of the shunt-peaking inductors is varied from 0 nH to 20 nH with                                                                             |    |

|      | step 5 nH                                                                                                                                               | 43 |

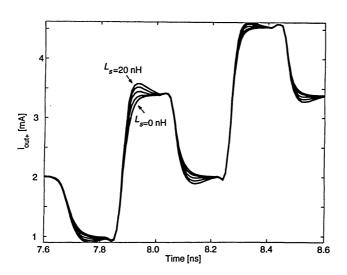

| 3.18 | Output current of the transmitter with passive peaking inductors. The induc-                                                                            |    |

|      | tance of the shunt-peaking inductors is varied from 0 nH to 20 nH with step                                                                             |    |

|      | 5 nH                                                                                                                                                    | 43 |

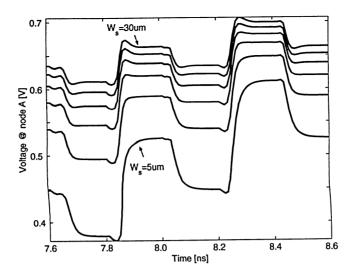

| 3.19 | Voltage at the multiplexing node $A$ with active peaking inductors. The width                                                                           |    |

|      | of transistor forming the active inductor is varied from 5 $\mu$ m to 30 $\mu$ m with                                                                   |    |

|      | step 5 $\mu\mathrm{m}$                                                                                                                                  | 44 |

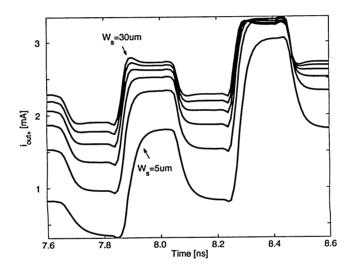

| 3.20 | Output current of transmitter with active peaking inductors. The width of                                                                               |    |

|      | transistor forming the active inductor is varied from 5 $\mu m$ to 30 $\mu m$ with step                                                                 |    |

|      | 5 $\mu \mathrm{m}$                                                                                                                                      | 44 |

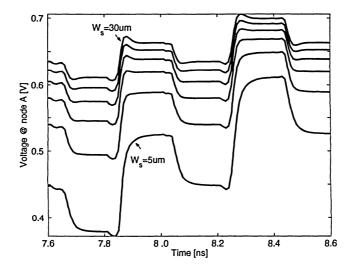

| 3.21 | Voltage at the multiplexing node $A$ when active peaking inductors. The width                                                                           |    |

|      | of transistor $M_5$ and $\overline{M}_5$ is 60 $\mu\mathrm{m}$ . The width of transistor forming the active                                             |    |

|      | inductors is varied from 5 $\mu$ m to 30 $\mu$ m with step 5 $\mu$ m                                                                                    | 45 |

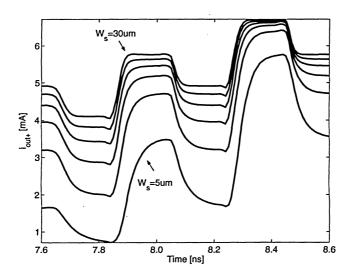

| 3.22 | Output current of the transmitter when active peaking inductors. The width                                                                              |    |

|      | of transistor $M_5$ and $\overline{M}_5$ is 60 $\mu\mathrm{m}$ . The width of transistor forming the active                                             |    |

|      | inductors is varied from 5 $\mu m$ to 30 $\mu m$ with step 5 $\mu m$                                                                                    | 45 |

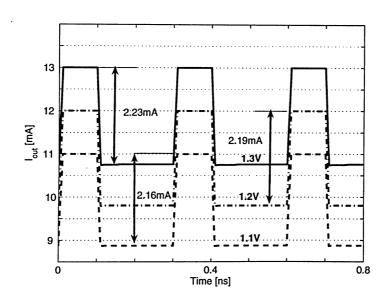

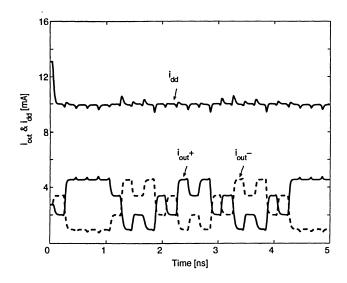

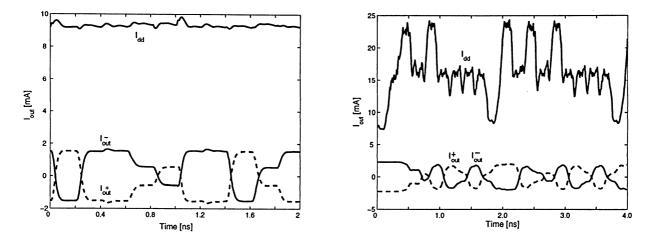

| 3.23 | Total current $i_{dd}$ drawn from $V_{dd}$ and output current of the 4-PAM current-                                                                     |    |

|      | mode transmitter with active peaking inductors                                                                                                          | 46 |

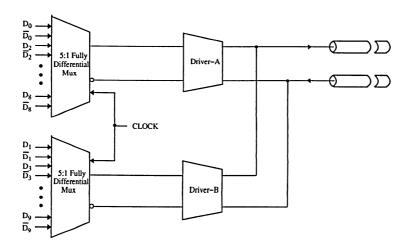

| 3.24 | Configuration of the 4-PAM current-mode transmitter with active peaking                                           |    |

|------|-------------------------------------------------------------------------------------------------------------------|----|

|      | inductors                                                                                                         | 47 |

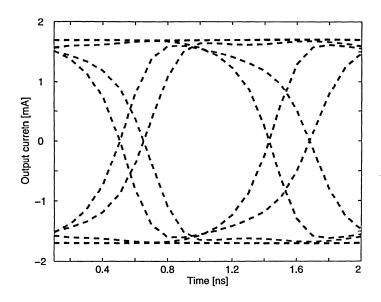

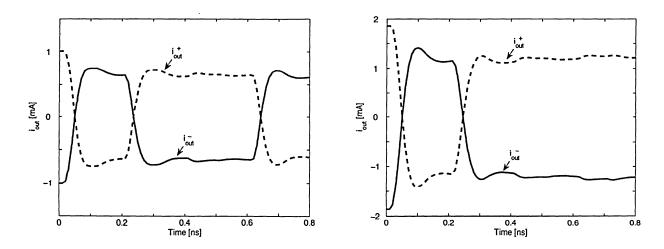

| 3.25 | (Left): Current output of driver J, (Right): Current output of driver 2J                                          | 48 |

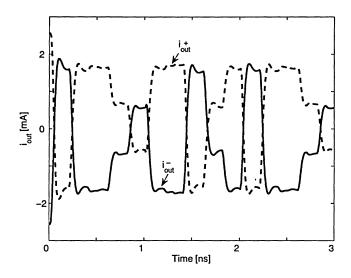

| 3.26 | 4-PAM current output of transmitter                                                                               | 48 |

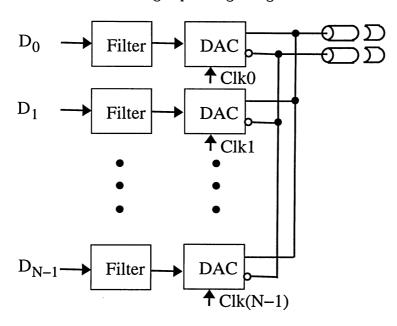

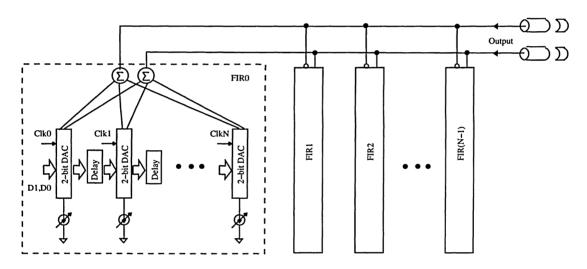

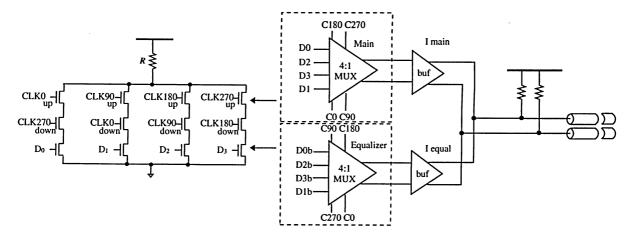

| 4.1  | Serial link transmitter with digital pre-emphasis                                                                 | 53 |

| 4.2  | Serial link transmitter with analog pre-emphasis.                                                                 | 54 |

| 4.3  | Serial link transmitter with pseudo-NMOS multiplexer pre-emphasis                                                 | 55 |

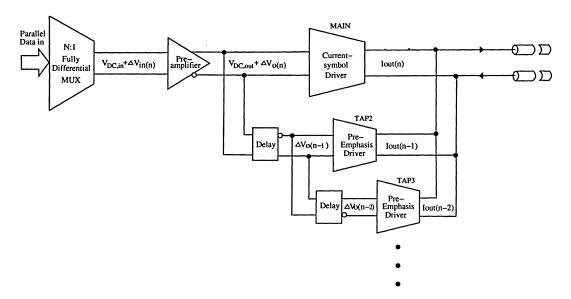

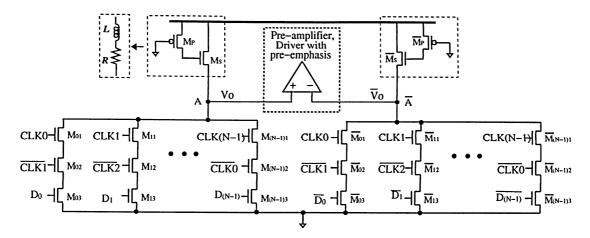

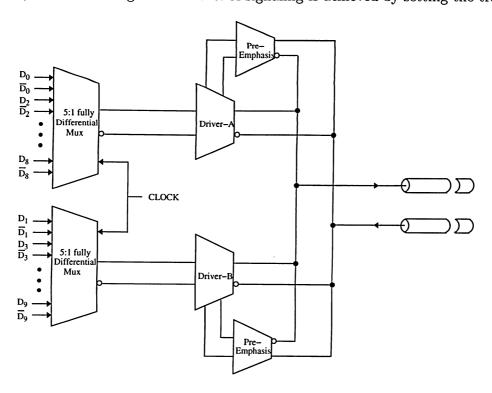

| 4.4  | Architecture of the proposed area-power efficient pre-emphasis serial link trans-                                 |    |

|      | mitter                                                                                                            | 56 |

| 4.5  | Fully differential multiplexer                                                                                    | 57 |

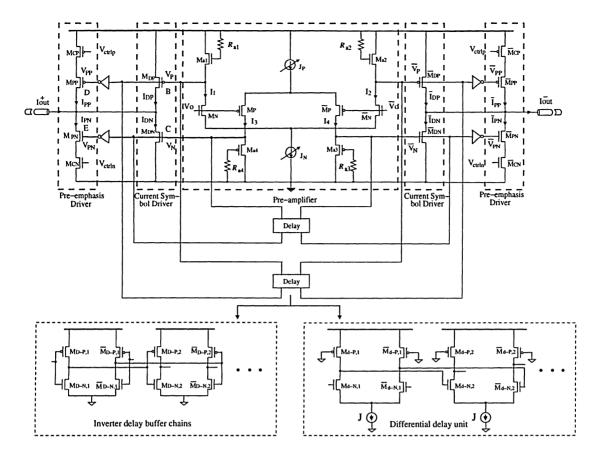

| 4.6  | 2-PAM serial link transmitter driver with pre-emphasis                                                            | 60 |

| 4.7  | 2-PAM signaling pre-emphasis analysis                                                                             | 63 |

| 4.8  | 4-PAM signaling pre-emphasis analysis                                                                             | 63 |

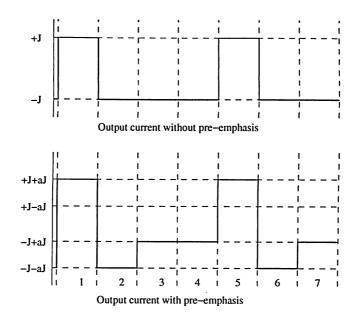

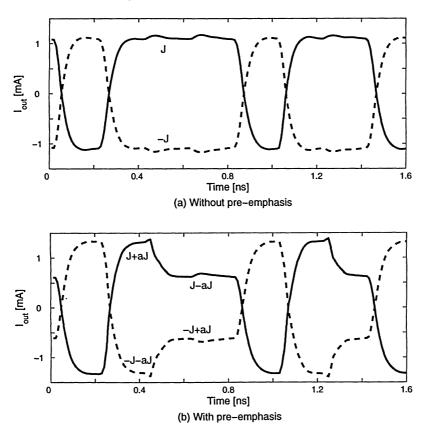

| 4.9  | Output current of 2-PAM serial link transmitter with pre-emphasis                                                 | 64 |

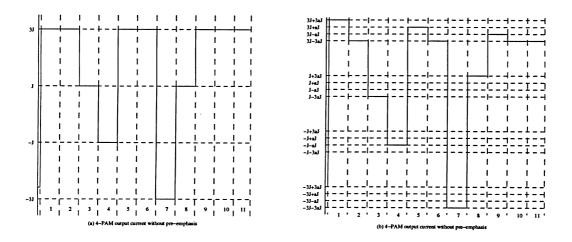

| 4.10 | Architecture of 4-PAM serial link transmitter                                                                     | 65 |

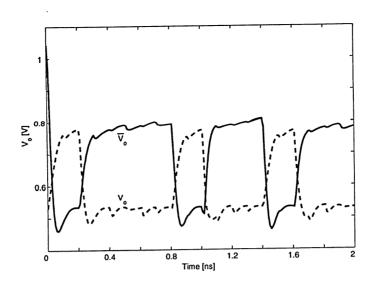

| 4.11 | Voltage of multiplexing node of fully differential multiplexer                                                    | 68 |

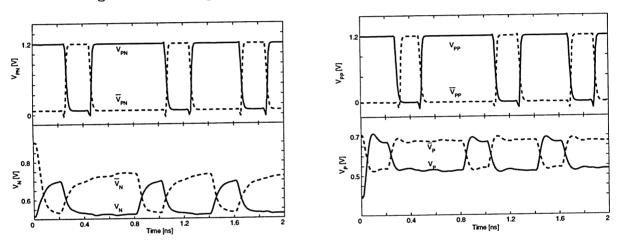

| 4.12 | Voltage of the critical nodes of pre-amplifier and driver, $V_{PN}, \overline{V}_{PN}, V_{PP}, \overline{V}_{PP}$ |    |

|      | lags $V_N, \overline{V}_N, V_P, \overline{V}_P$ by $T_{sym}=200$ ps                                               | 68 |

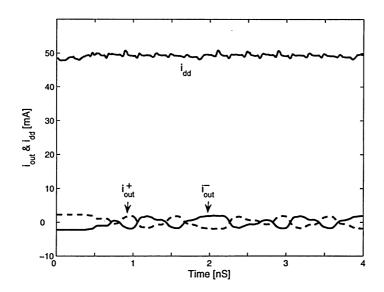

| 4.13 | 4-PAM transmitter output current and current drawn from $V_{DD}$ , Left: without                                  |    |

|      | pre-emphasis, Right: with pre-emphasis and inverter buffer chains                                                 | 69 |

| 4.14 | 4-PAM transmitter output current and current drawn from $V_{DD}$ with pre-                                        |    |

|      | emphasis and differential pair delay block                                                                        | 69 |

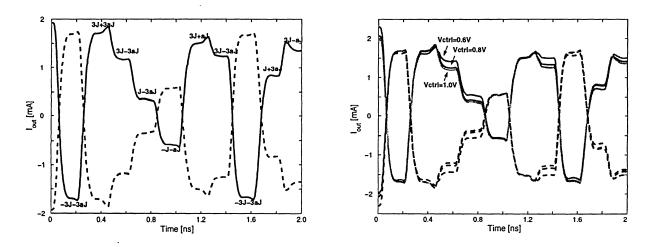

| 4.15 | Output current of 4-PAM transmitter. Left - with pre-emphasis $V_{ctrl,n}{=}1.0~V$                                |    |

|      | and $V_{ctrl,p}$ =0.2 V). Right: $V_{ctrl,n}$ is varied from 0.6 V to 1.0 V, and $V_{ctrl,p}$                     |    |

|      | varied from 0.6 V to 0.2 V with step 0.2 V                                                                        | 70 |

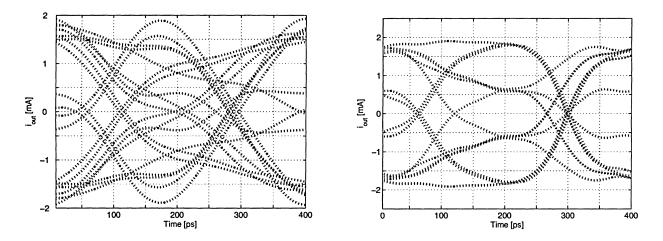

| 4.16 | Eye diagram of the received current after 10 cm FR-4 cable. Left - without                                        |    |

|      | pre-emphasis; Right - with pre-emphasis ( $V_{ctrl,n}$ =0.8 $V$ , $V_{ctrl,p}$ =0.4 $V$ )                         | 70 |

| 4.17 | Layout of the proposed 4-PAM transmitter with pre-emphasis                                                        | 73 |

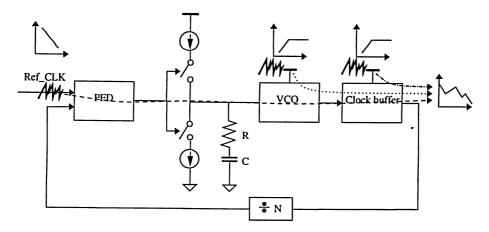

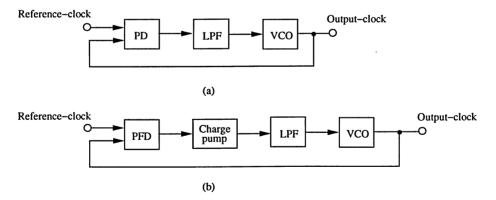

| 5.1  | (a) XPR/LPF type PLL, (b) Charge-pump type PLL                                                                                                                             | 74 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2  | PLL configuration                                                                                                                                                          | 75 |

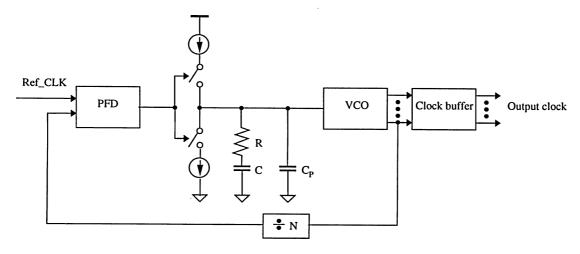

| 5.3  | Linear model of charge-pump type PLL                                                                                                                                       | 76 |

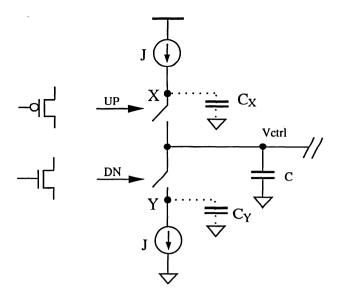

| 5.4  | Phase-frequency detector diagram                                                                                                                                           | 77 |

| 5.5  | D-FlipFlop PFD clock diagram and characteristic                                                                                                                            | 78 |

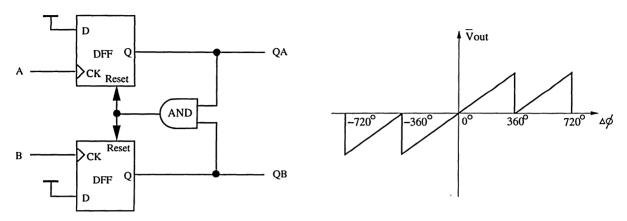

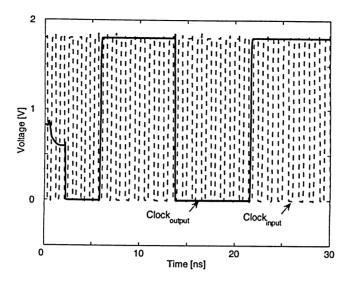

| 5.6  | Simulation result of DFF phase-frequency detector                                                                                                                          | 79 |

| 5.7  | Block diagram of charge pump.                                                                                                                                              | 80 |

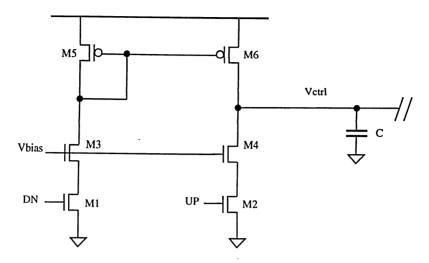

| 5.8  | Charge pump implementation. $\overline{M}_{1,2}=8~\mu\text{m},~\overline{M}_{3,4}=15~\mu\text{m},~\overline{M}_{5,6}=40~\mu\text{m},$                                      |    |

|      | $L{=}0.18~\mu\mathrm{m}$ is used for all transistors                                                                                                                       | 81 |

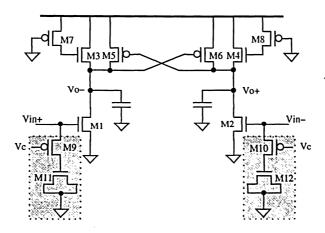

| 5.9  | Proposed ring VCO delay cell. $\overline{M}_{1,2}{=}10~\mu\text{m},~\overline{M}_{3,4}{=}15~\mu\text{m},~\overline{M}_{5,6}{=}5~\mu\text{m},$                              |    |

|      | $\overline{M}_{7,8}{=}25~\mu\mathrm{m},\overline{M}_{9,10}{=}15~\mu\mathrm{m},\overline{M}_{11,12}{=}30~\mu\mathrm{m}~L{=}0.18~\mu\mathrm{m}$ is used for all transistors. | 83 |

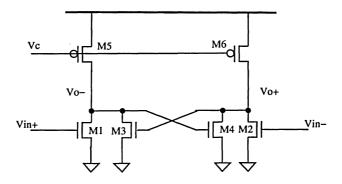

| 5.10 | Cross-coupled ring VCO with active inductor loads in [40, 41]. $\overline{M}_{1,2}$ =10 $\mu$ m,                                                                           |    |

|      | $\overline{M}_{3,4}{=}5~\mu\mathrm{m},~\overline{M}_{5,6}{=}15~\mu\mathrm{m},~L{=}0.18~\mu\mathrm{m}$ is used for all transistors                                          | 83 |

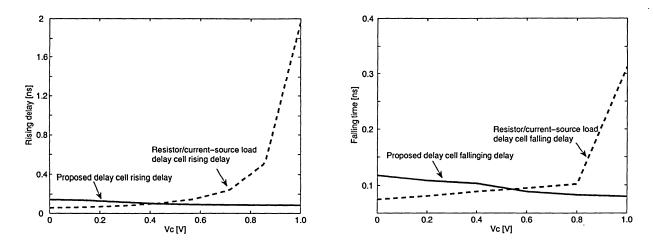

| 5.11 | Comparison of the rise and fall times of the proposed ring VCO and the                                                                                                     |    |

|      | cross-coupled ring VCO with active load [40, 41]                                                                                                                           | 84 |

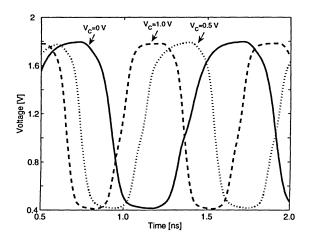

| 5.12 | Output voltage waveform of proposed VCO with a single delay loop                                                                                                           | 84 |

| 5.13 | Frequency tuning range of 5-stage proposed ring VCO, $W{=}10~\mu\mathrm{m}$ for the                                                                                        |    |

|      | control pMOS transistor                                                                                                                                                    | 85 |

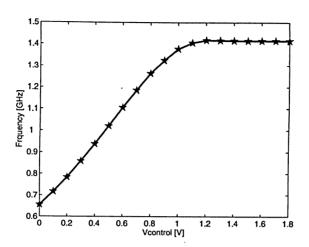

| 5.14 | Divide-by-four frequency divider (a) Block diagram, (b) Timing diagram. The                                                                                                |    |

|      | width of NMOS and PMOS transistors in inverters are 2.5 $\mu m$ and 5 $\mu m$                                                                                              |    |

|      | respectively, all transistor width for transmission gate is 4 $\mu m$ , 0.18 $\mu m$ is                                                                                    |    |

|      | used for all transistor length                                                                                                                                             | 86 |

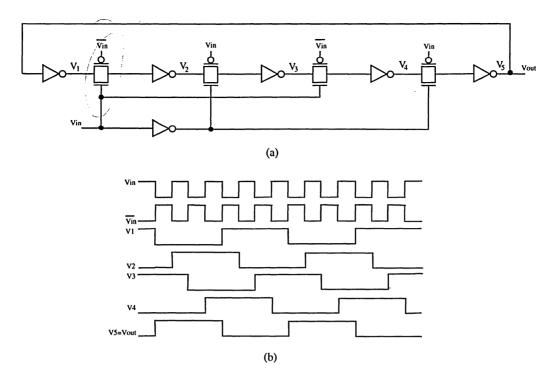

| 5.15 | Simulation result of PFD                                                                                                                                                   | 87 |

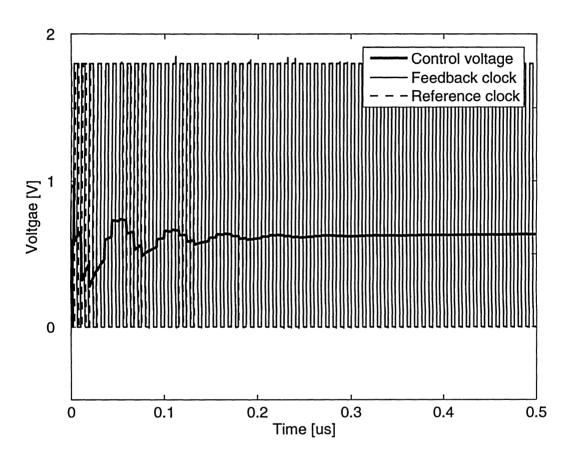

| 5 16 | PLL control voltage reference clock and VCO output clock                                                                                                                   | 88 |

# Chapter 1

# Introduction

### 1.1 Motivation

We have witnessed the integration of computer systems into a more global context of information technology system in the past decade. Moore's law allows every new generation of CMOS device's performance to increase at an exponential rate, allowing more computations to occur within chips. However, the continued scaling of integrated circuit technology not only increases the data processing capabilities, but also raises the challenges in the field of data communication, that does not improve with Moore's law. Thus, chip-to-chip interconnection has become one of the leading bottlenecks of computer system performance improvement. The challenges and demands associated with eliminating these bottlenecks and providing efficient data communication with a high speed, low power consumption, and a smaller chip area have brought a boom in development of techniques.

Traditionally, high-speed serial links in the giga-bit-per-second range was implemented in GaAs or bipolar technologies. An advantage of these technologies over CMOS technology is the high intrinsic device speed. However, the main reason why CMOS becomes targeted technology for serial links is the high degree of integration. Recent advance in CMOS technology has significantly reduced the feature size of MOS devices to nanometer regions. As a result, the intrinsic cutoff frequency of MOS devices has been increased to several tens giga hertzs while the switching power consumption is kept very low, which is on the order of 0.1 mW/GHz/gate. Data transmission over copper channels at giga-bit-per-second

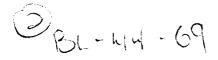

is of the fundamental to the systems such as the backplane of complex microelectronic systems, multi-processor systems, gigabit Ethernet for LANs and WANs, data communications between computers and peripheral devices, and global interconnects linking subsystems integrated on the same silicon substrate. A sample signaling path is illustrated in the Fig. 1.1.

Figure 1.1: Backplane system cross-section indicating different sections of the signaling path.

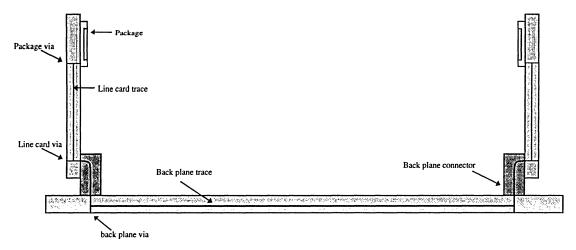

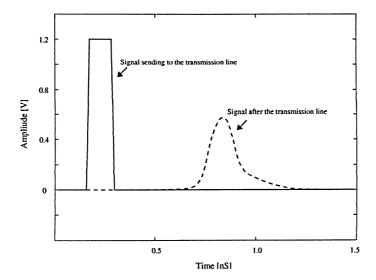

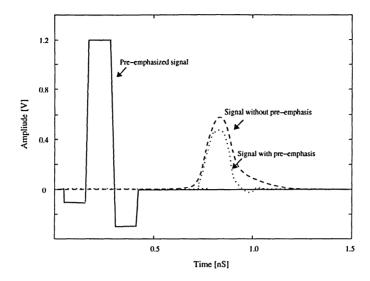

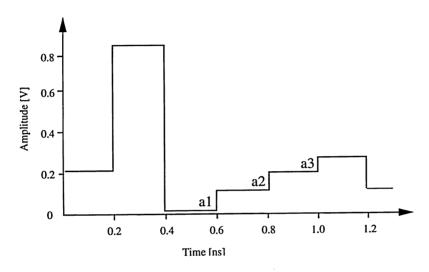

Channels of serial links are band-limited. A narrow pulse at the near end of the channels will be significantly attenuated and becomes much wider at the far end of the channels, as shown in Fig. 1.2 [1]. If two neighboring narrow pulses are sent to the channel, as shown in Fig. 1.3, an inter-symbol interference (ISI) effect will be seen at the far end of the channel [1, 2].

There are two solutions at the near end of channels to overcome the limitation mentioned above:

#### 1. Transmitter pre-emphasis:

Transmitter pre-emphasis is a finite impulse response(FIR) filter integrated into the line driver specified by the following equation:

$$V_o(n) = V_i(n) - \sum_{k=1}^{M} a_k V_i(n-k),$$

(1.1)

Figure 1.2: The response of a FR4 cable to a 100ps wide pulse.

Figure 1.3: The effect of inter-symbol interference.

where  $V_i(n)$  and  $V_i(n-k)$  are the present and past  $k^{th}$ -input of the pre-emphasis respectively,  $V_o(n)$  is the output of the pre-emphasis,  $a_k$  is the weighting factor of the past  $k^{th}$ -input of the pre-emphasis, and M is the number of taps. The pre-emphasis filter effectively suppresses the power of low-frequency components by reducing the amplitude of continuous strings of same-value data on the line. Simultaneously, it keeps the power of high-frequency components the same. Fig. 1.4 shows the pre-

emphasized pulse and the resulting pulse at the end of the cable compared with the original pulse [1].

Figure 1.4: Pulse response from a pre-emphasized transmitter.

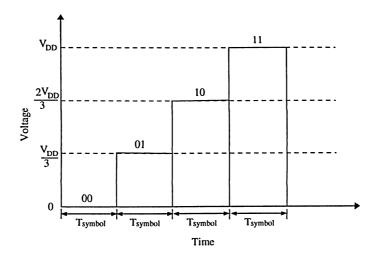

### 2. Multi-level pulse amplitude modulation (M-PAM):

M-PAM signaling is another way to overcome the finite bandwidth limitation of transmission channels. It transmits multi-bit in each symbol time. As a result, the required bandwidth of a channel for a given bit rate decreases. An example of 4-PAM signaling symbols is shown in Fig. 1.5.

Pre-emphasis proposed in [3] pre-distorts the signal based on the algorithm specified by Eq. (1.1), has been proven effective to overcome the inter-symbol interference (ISI). M-PAM signaling reduces the bandwidth of the signal, while keeping the data rate constant by using a simple coding. However, these approaches have a common drawback - an increased hardware cost and power consumption.

### 1.2 Contributions

This thesis contains the following original contributions:

Figure 1.5: An example of 4-PAM signaling symbols.

- 1. A new current-mode class AB transmitter with a low supply voltage sensitivity. The rail-to-rail swing mode ensures that the output current is insensitive to supply voltage fluctuation. The full push-pull operation of the driver minimizes the static power consumption of the transmitter.

- 2. A new fully differential current-mode 4-PAM transmitter with a current mirror driver is proposed. This transmitter utilizes the advantages of the multiplexing-at-input approach and active inductors to maximize the bandwidth and minimize the area and power consumption.

- 3. A new fully differential current-mode 4-PAM transmitter with class AB driver is proposed. The transmitter provides both 5 Gbps (2-PAM) and 10 Gbps (4-PAM) signaling abilities. The proposed inheres all the advantages of current-mode transmitter, while providing an attractive feature a tunable signal amplitude.

- 4. A novel pre-emphasis approach is proposed. This approach avoids the re-construction of the past symbols needed for transmitter pre-emphasis in the digital domain, as of most reported pre-emphasis transmitters that require a large chip area and a high level of power consumption, the pre-emphasis of the proposed transmitter is realized in the analog domain by employing a delay block for each pre-emphasis tap, such that

- the degree of each pre-emphasis tap can be tuned individually and independent of the current symbol.

- 5. A new VCO delay cell is proposed to overcome the effects of unequal rising and falling time. The equal rising and falling times lead to lower timing jitter of clock. The proposed VCO also provides good linearity with a very large frequency tuning range.

- 6. A phased-locked loop (PLL) with the proposed VCO delay cell is implemented in UMC's 0.13  $\mu$ m CMOS technology. The PLL generates a multi-phase clock with a large frequency tuning range, a symmetric waveform at 1GHz.

## 1.3 Organization

This thesis is organized into the following six chapters:

- Chapter 1 introduces the background and motivation of this work.

- Chapter 2 describes a typical high-speed serial link architecture, and investigates limitations, channel properties, trade-offs between different modulation and equalization schemes.

- Chapter 3 introduces two different signaling schemes and investigates different serial link transmitter designs to overcome the limitations of device speed, noise and transmission medium. Three serial link transmitters are proposed.

- Chapter 4 reviews existing pre-emphasis approaches. A current-mode transmitter with a novel power-area efficient pre-emphasis scheme is proposed.

- Chapter 5 presents a comparative study of the architecture of low-voltage CMOS ring-VCOs. A phase-locked loop (PLL) that employs the proposed delay cell is designed in this chapter.

- Chapter 6 concludes the thesis and discusses the directions of future work.

# Chapter 2

# An Overview of Serial Links

In this chapter, a basic serial link architecture is examined to provide a framework for understanding the trad-offs and limitations of serial link transmitters. Factors that affect the bandwidth of serial links are discussed in detail. Two signaling schemes and techniques to overcome the limitations are introduced.

## 2.1 A Typical Serial Link Architecture

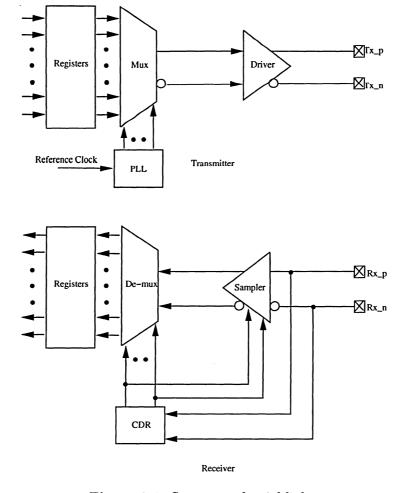

The basic configuration of a serial link is shown in Fig. 2.1. It consists of the following blocks:

- Registers: Registers located at both the transmitter and the receiver ends synchronize the input/output data.

- Multiplexer (MUX): Parallel input data streams after synchronization are serialized by the multiplexer. The on-chip clock period of digital circuitry that supplies parallel data is  $\frac{1}{N}$  that of the serial link, where N is the degree of serialization of the multiplexer [4, 5].

- Phase-locked Loop (PLL) and Clock and Data Recovery (CDR): A PLL acts

as a timing generator in a serial link. It generates a high-frequency clock by multiplying

a low-frequency reference clock. The CDR block at the receiver end incorporates a

Figure 2.1: Structure of serial links.

PLL and additional circuits needed to synchronize the receiver with the incoming data stream.

- Driver: A driver provides voltages or currents that sufficiently large to channels such that the data received at the receiver end can be recovered with a low bit-error-rate (BER).

- Sampler and De-multiplexer (De-MUX): A sampler and a de-multiplexer sample a bit stream using evenly spaced clock phases to de-multiplex the data directly. The data and clock recovery unit adjusts the phase of the sampling clock such that data

are sampled at the center point of data eyes.

## 2.2 Signaling

Two signaling techniques for high-speed digital system signaling are introduced in this section. The first one is voltage-mode signaling, it has been used in most computers in the past several years. The second technique is current-mode signaling.

### 2.2.1 Voltage-Mode Signaling

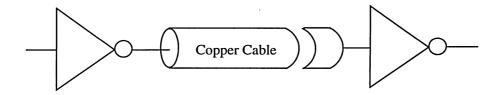

CMOS inverters are typically used at both transmitter and receiver ends. As shown in Fig. 2.2, the transmission medium, typically a cable or a PCB trace, has a characteristic impedance of about 50 to  $100\Omega$ , and is unterminated at the receiver end.

Figure 2.2: Voltage-mode signaling scheme.

The reasons why voltage-mode signaling is not suitable for high-speed data transmission are as the followings:

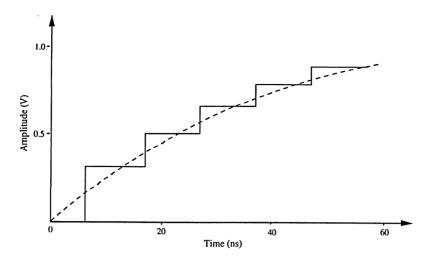

- 1. Unterminated receiver: receivers with a high input impedance limit signaling speed. The high impedance driver is unable to switch the line voltage completely [3]. The driver must charge up the line as the signal propagates over several round trip instead. The figure in Fig. 2.3 shows the voltage at the far end of the line as a function of time.

- 2. **High power consumption:** voltage-mode signaling is power hungry. This is because they use rail-to-rail signal swings for transmission. As a result, a high level of power consumption is required.

Figure 2.3: Voltage at the far end of a 4-ns line when a logic level "1" is applied at the near end of the cable.

3. Low speed: rail-to-rail large swing of voltage-mode signaling increase the time to charge or discharge the capacitance of critical nodes, this increased time constrains the speed of a voltage-mode signaling.

### 2.2.2 Current-Mode Signaling

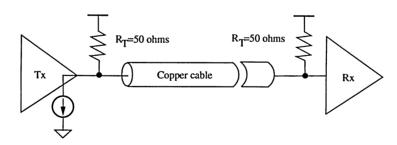

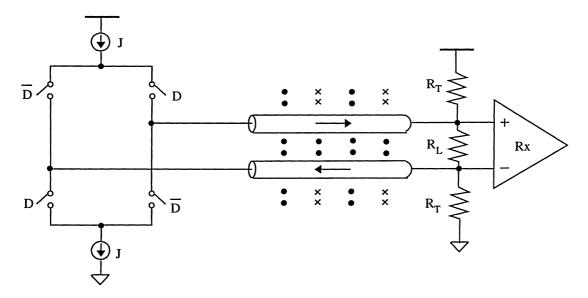

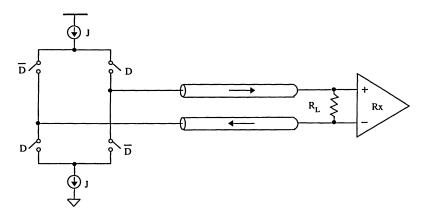

A signaling scheme overcomes the limitations of the voltage-mode signaling scheme is shown in Fig. 2.4. The transmitter (Tx) behaviors as a current source and draws a current from the channel. The voltage swing is in the range of 100 mV to 1 V. The serial link is terminated at

Figure 2.4: Current-mode signaling scheme.

both ends with its characteristic impedance. Taking advantages of the improved receiver

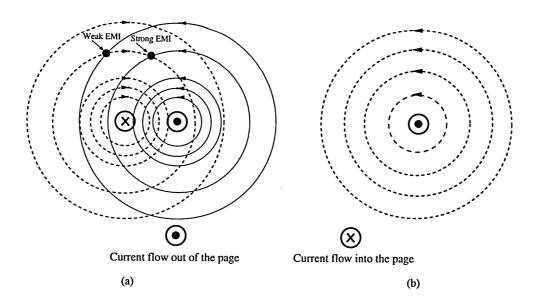

detection with a low offset voltage and high sensitivity, this signaling scheme can operate reliably using very small voltage swings. Another advantage resulting from the small voltage swing is a considerable power consumption reduction. Incorporating with a differential configuration, the bi-directional current-mode signaling scheme, as shown in Fig. 2.5, can minimize the EMI to neighboring devices.

Figure 2.5: (a) Reduction EMI with bi-directional signaling scheme, (b) EMI in a single-ended signaling scheme.

### 2.3 Limitations

Many factors limit the performance of a high-speed serial link, including device speed, transmission medium, high-speed on-chip clock generation, and noise. The following two sections examine these limitations in detail.

### 2.3.1 Electronic Limitations

### 1. Speed

The maximum data rate of a serial link is limited by the electronics used to generate

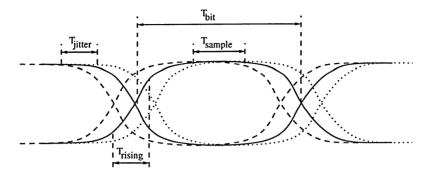

and receive the signal. As shown in Fig. 2.6, limits of signaling speed arise from rising time, sampling time, timing jitter [3]. The symbol time  $T_{symbol}$  must exceed  $T_{rising}$  (the time required for a signal to change from one logic to another), summed with  $T_{sampling}$  (the time for receiver to sample a signal while stable), and  $2T_{jitter}$  (timing uncertainty).

Figure 2.6: Eye diagram showing limitations of bit time.

A metric for bit rate that is independent of technology and operation conditions, such as process technology, temperature and supply voltage, is needed to compare the performance between different systems. FO4 is a figure of merit qualifying the average propagation delay of a complementary static inverter of the minimum size with the load of four identical inverters. For a typical 0.18  $\mu$ m and 0.35  $\mu$ m CMOS technology, the approximately value is 80 ps and 175 ps respectively.

#### 2. Noise

As CMOS technology and supply voltage are continuously scaled down, the signal represented by the voltage in most systems is getting lower. However, the noise existing in electronic systems remains at the same level.

The noise of the transmitted signal or the received sampling clock is qualified by the timing jitter. Some other noises include limited sampling resolution, thermal device noise and supply noise.

(a) Timing noise: timing noise origination is from the source of timing generation on a chip, which is usually a PLL or a DLL. A typical PLL is shown in Fig.

2.7, the dominant noise source is the VCO (voltage-controlled oscillator), which generates the clock and distributes to the output through the clock buffer. The phase-frequency detector generates the phase error signal, which is then filtered by the low-pass filter to create control voltage for the VCO and steer its phase to align with the reference clock.

Figure 2.7: The noise sources in a typical PLL.

- (b) Other noise sources: Some other noise sources existing in a serial link include thermal device noise, supply noise and limited sampling resolution.

- i. Thermal device noise: the source of thermal noise in serial links are the  $50\Omega$  termination resistor at the receiver end [2]. In addition to the termination resistor, the device noise of the receiver circuits also adds several dB of noise figure to the termination noise level.

- ii. Supply and substrate noise: the supply and substrate noise does not introduce noise to the link directly, instead, the noise impact the performance by inducing jitter in transmit timing generation loops [6], and by modulating the input-reffered receiver offset [7].

- iii. Sampling resolution: sampling resolution is the minimum voltage level that can be distinguished by the receiver comparator when other noise sources are not considered. It is determined by several factors such as: receiver static

offset voltage due to transistor mismatches, input-referred supply noise, and the input voltage required for the comparator to obtain a decision within a certain period of time.

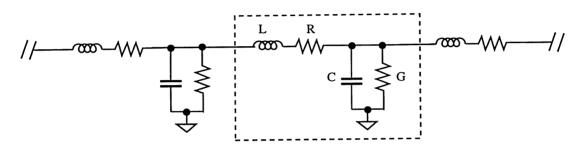

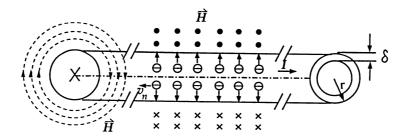

# 2.3.2 Transmission Medium Limitations

Transmission lines in high-speed serial links include PCB traces, coaxial and twisted-pair cables. They can be modelled by a series of lumped LCRG elements, as shown in Fig. 2.8. The signal loss in the transmission line is mainly caused by the series resistance, the parallel conductance, and radiations.

Figure 2.8: Lumped LCRG model of transmission line.

Frequency-dependent loss in transmission lines is mainly due to the skin-effect resistance. As shown in Fig. 2.9, a magnetic field is created when an AC current flows though a conductor. The resultant magnetic field will impact a force called **Lorezen force** on moving electrons and push them to the surface of the conductor, resulting a higher resistance at the center and a lower resistance near the surface. As shown in Fig. 2.9, the effective conducting area is measured by skin depth  $\delta$  given by

$$\delta = \frac{1}{\sqrt{\pi\mu\sigma f}},\tag{2.1}$$

where  $\mu$  is the permittivity of the conductor,  $\sigma$  is the conductivity of the inductor, and f is the frequency of the current. The induced resistance is given by R(f),  $R_{DC}$  is the resistance when a DC signal is applied, r is the radius of the conductor, and L is the length of the transmission line.

$$R(f) = R_{DC}(\frac{r}{2\delta}). \tag{2.2}$$

As seen from above equation, the skin-induced resistance is proportional to the square-root of frequency. The skin depth for some interconnect materials at 100KHz and 5GHz are give in Table 2.1.

Figure 2.9: Skin effect of transmission lines.

| Interconnect | Resistivity $(10^{-9}\Omega m)$ | Skin depth at 100 MHz(µm) | Skin depth at 5 $GHz(\mu m)$ |

|--------------|---------------------------------|---------------------------|------------------------------|

| Silver       | 16.3                            | 6.4                       | 0.905                        |

| Copper       | 17.3                            | 6.6                       | 0.933                        |

| Gold         | 22.7                            | 7.6                       | 1.07                         |

| Aluminum     | 27.3                            | 8.3                       | 1.17                         |

| Silicon      | 100-300                         | 15.9-27.6                 | 2.25-3.9                     |

Table 2.1: Skin depth of some interconnects at 100 MHz and 5 GHz.

For some insulating materials, dielectric absorbtion also causes a frequency-dependant loss. It can be modelled as a conductance G between the signal wire and the ground. This effect can be mitigated by using a low-loss dielectric material. However, the material choice is also limited because of certain restriction on PCB materials. The PCB traces demonstrate a higher dielectric loss compared to cables. The loss is defined as Loss Tangent in [3]:

$$\tan(\sigma_D) = \frac{G}{\omega C},\tag{2.3}$$

where C is the capacitance-per-unit-length, and it is approximately constant, therefore, the dielectric loss typically increases lineally with the frequency. With these analysis, the total frequency loss is given by the following equation [3],

$$H(f,l)|_{dB} = -(h_s\sqrt{f} + h_d f)l,$$

(2.4)

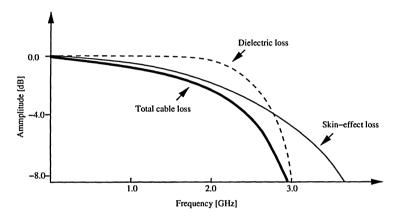

where l is the length of the transmission line, and  $h_s$ ,  $h_d$  are the skin-effect and dielectric loss coefficients respectively. Fig. 2.10 shows the frequency response of a copper wire, with skin-effect and dielectric loss component shown separately. At low frequencies, the skin effect is the dominant loss, while the dielectric loss dominates at higher frequencies.

Figure 2.10: Frequency dependance of cable loss.

### 2.3.3 Multi-Phase Clock Generation

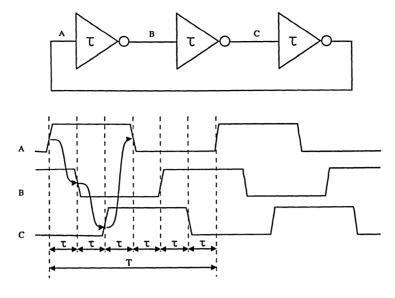

Multi-phase clock generation is another challenge in serial link design. It is usually implemented by multiplying a reference clock through a PLL or a DLL. The smallest period determined by a ring VCO in a given technology is limited to be no more than 2(N+1)FO4, where N is the number of stages. Consider the example of a 3-stage ring VCO shown in Fig. 2.11. The narrowest pulse width generated by this circuit is approximately 3FO4 if the delay  $\tau$  is 1FO4. The highest frequency can be calculated from

$$f_{max} = \frac{1}{6\tau}. (2.5)$$

Figure 2.11: Clock generation using a 3-stage ring oscillator.

Another way to generate the on-chip clock is to use a LC tank oscillator to provide frequencies above 10 GHz. However, the bulky, noisy, and large chip area inductors have to be fabricated on-chip, which is not attractive for system-on-chip (SOC) design.

Another design difficulty for clock generation is the clock jitter in addition to the clock speed. The clock jitter usually comes from the unstable off-chip reference clock, thermal noise, noisy power rails and substrate. The details on this topic is discussed in Chapter 5.

## 2.4 Design Techniques

### 2.4.1 Voltage Mode and Current Mode

Voltage-mode and current-mode signaling schemes have been used in high-speed serial links. Current-mode signaling offers following advantages over voltage-mode counterpart:

1. **Higher speed:** the speed of a serial link transmitter is determined from the charging and discharging times of the critical nodes in the transmitter. The capacitance of one node is fixed for a given technology, and the capacitance charging and discharging time is determined from

$$\Delta t = \frac{C\Delta V}{I},\tag{2.6}$$

where  $\Delta V$  is the voltage swing of the node, I is the average current to charge or discharge the node, and C is the capacitance of the node. A typical characteristic of a current-mode circuit is its small voltage swing. It can be seen from the above equation that a smaller voltage swing at the node results in a smaller  $\Delta t$ .

- 2. A constant current drawn from power rails: with a well defined differential configuration, a constant current is drawn from the power source such that noise injection to the substrate and neighboring devices is minimum.

- 3. Lower electromagnetic interference (EMI): a typical example is the LVDS current-mode driver shown in Fig. 2.12. It is seen that the EMI caused by the differential currents in the channel cancel each other.

Figure 2.12: EMI cancellation in LVDS current-mode driver.

### 2.4.2 Multi-Level Pulse Amplitude Modulation

As discussed in section 2.3, a signal is usually distorted after the transmission line due to its limited bandwidth. As a result, the signal can not travel far and usually causes Inter-Symbol Interference (ISI), and limits the performance of serial links. This problem becomes more server for high-frequency signals, which use narrow pulses to represent the signal information. Multi-level transmission schemes using each pulse conveys  $\log_2(M)$  bits of information have been proven effective [4, 8]. For a given data rate, M-PAM modulation reduces the effective symbol rate by a factor of  $\log_2(M)$  compared to a conventional 2-PAM signaling scheme. This symbol-rate reduction not only reduces ISI in the channel, but also relaxes on-chip clock frequency.

The cost of a M-PAM serial link scheme is its complex configuration. A 4-PAM signaling scheme usually doubles the hardware as compared with its 2-PAM counterpart. Another reason for avoiding a large M is due to the limited signal resolution of the receiver and transmitter swing budget.

This work uses a fully differential 4-PAM signaling scheme to decrease the symbol rate by a factor of 2. The differential configuration improves the performance by eliminating the effect of common-mode noise and increasing the total signal swing by a factor of 2 as compared to single-ended signaling.

### 2.4.3 Transmitter Pre-emphasis and Receiver Equalization

### 1. Transmitter pre-emphasis:

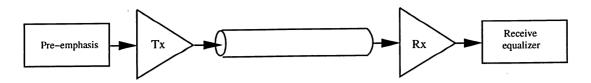

Transmitter pre-emphasis is a technique to alleviate ISI and compensate for the high-frequency loss of channels. As shown in Fig. 2.13,

it uses a symbol-spaced finite impulse response (FIR) filter integrated into the line driver, that performs the following computation:

$$V_o(n) = V_i(n) - a_1 V_i(n-1) - a_2 V_i(n-2) - \dots,$$

(2.7)

Figure 2.13: Transmitter pre-emphasis and receiver equalization.

where  $V_i(n-k)$  are the present and past input symbols respectively,  $V_o$  is the output, and  $a_1, a_2...$  are the weight coefficients of the filter. The output will no longer have the distinct signal levels of the unfiltered signal stream, as shown in Fig. 2.14.

Figure 2.14: Effect of 3-tap pre-emphasis,  $a_1, a_2$  and  $a_3$  are the pre-emphasis coefficients.

Another observation from Fig. 2.14 is that the FIR filter suppresses the power of low-frequency components and keeps the power of the high-frequency components by decreasing and keeping the amplitude of the signals respectively. One drawback of this approach is the reduction of the low-frequency components decreases the signal-to-noise ratio.

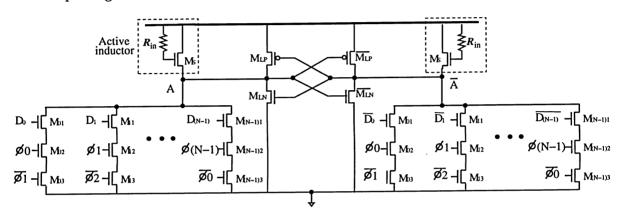

In this work, we not only decrease the amplitude of the low frequency components, but also increase the amplitude of the high frequency components. As a result, the current difference between the low frequency and high frequency components is doubled as compared to conventional approach such that a more efficient pre-emphasis scheme is achieved. A detailed discussion on this topic will be seen in Chapter 4.

#### 2. Receiver equalization:

High frequency components can be further accentuated by increasing high frequency gain at the receiver end. An equalizer at the receiver end can not be substituted by pre-emphasis at the transmitter end.

A sharp transition at the transmitter end is desirable for eye-opening, as shown in Fig. 2.15. Clearly, the eye diagram with a sharp slope results in larger timing margins, which makes the system more tolerant to sample phase errors. The effect of sharp transitions become even more important for 4-PAM signaling schemes, where the top and bottom eye-width is seriously affected by signal transition slope.

Figure 2.15: 4-PAM eye diagrams, a) slow transition, b) sharp transition.

Although a fast transition is critical at the transmitter end, it is undesirable from the transmission media point of view. This is because a sharp transition will cause ringing and crosstalks between adjacent channels. Another reason is that the preemphasized high-frequency components at the transmitter move signal power into more lossy regions of channels. Therefore, the transition slope of the signal should adjusted to the minimum required value.

Ideally, a better approach to overcome the loss caused by lossy channels is to perform equalization at the receiver end. Since no signal power loss is wasted for pulse preshaping at the transmitter end, filters can also be used to sharpen the transition edges of the signal at the far end of channels.

#### 2.4.4 Active Inductors

Inductors have been widely used in transceiver design to increase bandwidth [14, 15]. This technique moves the -3 dB pole to a higher frequency and improves bandwidth as much as 70 percent.

Conventional on-chip inductors are usually realized using planner spirals. They suffer from several design difficulties: 1) a large chip area, 2) a large parasitic capacitance to the substrate, 3) a small and none-tunable inductance, and 4) a low self-resonant frequency and low quality factor. As compared to passive inductors, active inductors, which are synthesized using active devices, offer intrinsic advantages including: 1) a small area, 2) a large and variable inductance, and 3) a high and tunable quality factor. However, active inductors also suffer from the following drawbacks: 1) high noise due to thermal noise of resistors and MOSFETs, 2) a smaller dynamic range because MOSFETs must be in the saturation region, and 3) a limited frequency range over which an inductor characteristic exists.

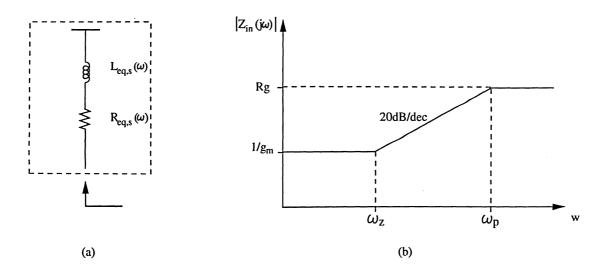

There are many ways to implement active inductors. A simple active inductor shown in Fig. 2.16 can be realized using a NMOS transistor and a resistor. The resistor can be implemented using a PMOS transistor.

By applying a voltage source at the source terminal of the NMOS transistor, the input

Figure 2.16: Active inductor and its small-signal equivalent circuit.  $g_m$ ,  $C_{gs}$  and  $C_{gd}$  are transistors' trans-conductance, gate-source and gate-drain capacitances, respectively,  $C_L$  is the total capacitance associated with the driving node.

impedance is obtained from Eq. (2.8).

$$Z_{in}(s) = \frac{1 + sC_{gs}R_g}{g_m + sC_{gs}}. (2.8)$$

The equivalent inductance  $L_{eq,s}(\omega)$  and  $R_{eq,s}(\omega)$  of the active inductor can be obtained by substituting s with  $j\omega$ :

$$Z_{in}(\omega) = \frac{1 + j\omega C_{gs}R_g}{q_m + j\omega C_{gs}} = \frac{g_m + \omega^2 C_{gs}^2 R_g}{q_m^2 + \omega^2 C_{gs}^2} + j\omega \frac{C_{gs}(g_m R_g - 1)}{g_m^2 + \omega^2 C_{gs}^2}.$$

(2.9)

The equivalent impedance of the active inductor is as shown in Fig. 2.17(a), where the equivalent series resistance, inductance and Q-factor are given in the following equations:

$$R_{eq,s}(\omega) = \frac{g_m + \omega^2 C_{gs}^2 R_g}{g_m^2 + \omega^2 C_{gs}^2},$$

(2.10)

$$L_{eq,s}(\omega) = \frac{C_{gs}(g_m R_g - 1)}{q_m^2 + \omega^2 C_{gs}^2},$$

(2.11)

$$Q(\omega) = \frac{\omega L_{eq,s}(\omega)}{R_{eg,s}} = \omega \frac{C_{gs}(g_m R_g - 1)}{g_m + \omega^2 C_{gs}^2 R_g}.$$

(2.12)

The dependance of  $|Z_{in}|$  on  $R_g$  and  $g_m$  is shown in Fig. 2.17(b), where the pole frequency  $\omega_p = \frac{g_m}{C_{gs}}$  and zero frequency  $\omega_z = \frac{1}{R_g C_{gs}}$  are determined from Eq.(2.8). It is seen that:

Figure 2.17: (a) Active inductor equivalent circuit, (b) active inductor bode plot.

- 1. An increase in  $R_g$  lowers the lower bound of the frequency range over which the circuit exhibits an inductive characteristic and reduces the self-resonant frequency of the active inductor.

- 2. An increase in the width of the NMOS transistor lowers the impedance of the active inductor and reduces the self-resonant frequency.

## 2.5 Summary

The shortcomings of conventional CMOS serial links and the limitations have been investigated. The bandwidth of channels is limited by the low-pass characteristics of the channels caused by skin-effect resistance and dielectric loss. The finite bandwidth of the channels gives rise to an inter-symbol interference.

A number of techniques have been investigated in this chapter. M-PAM modulation enables systems to transmit  $\log_2 M$  bits per symbol time. It decreases the symbol rate and relaxes on-chip clock by a factor of  $\log_2(M)$ . FIR filters are used at both the transmitter and receiver ends to increase eye opening. Active inductors at critical nodes sharpen transaction edges.

# Chapter 3

# High-speed Serial Link Transmitter Design

In this chapter, a state-of-the-art review for several serial link transmitters with inverter, LVDS, open-drain and class AB drivers is presented. Three transmitters including a 2-PAM transmitter with improved  $V_{DD}$  insensitivity and two 4-PAM current-mode transmitters for 10 Gbps serial links are proposed.

This chapter is organized as follows: section 3.1 provides an in-depth review of the design of serial link transmitters. The advantages and limitations of the four widely used serial link transmitter drivers are investigated. Section 3.2 proposes a 2-PAM and two 4-PAM current-mode 10 Gbps serial link transmitters. Simulation results are presented at the end of this section. Finally. The chapter is summarized in section 3.3.

# 3.1 An overview of Serial Link Transmitters

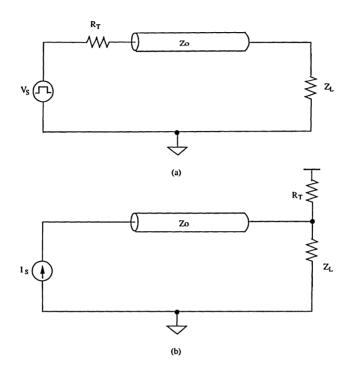

A serial link transmitter converts parallel digital streams into a serial analog signal with a pre-defined waveform and amplitude to compensate for high-frequency loss of channels. The parallel-to-serial function is realized by a multiplexer. In order to achieve a high speed, a small time constant is always preferred at the multiplexing node. Depending on signals, transmitters are classified into the following categories, as shown in Fig. 3.1.

Voltage-mode transmitter: Transmitters with a high output impedance making their appearance as a voltage source and are referred as voltage-mode transmitters.

Current-mode transmitter: Transmitters with a low output impedance making their appearance as a current source and are referred as current-mode transmitters.

Figure 3.1: (a) Voltage-mode transmitter. (b) Current-mode transmitter.

Traditional voltage-mode transmitters become a bottleneck in serial link transmitter designs when the signaling speed reaches the range of giga-bit-per-second. The average rising and falling times of a node is determined from

$$\Delta t = \frac{C_{node} \Delta V_{node}}{I},\tag{3.1}$$

where I is the average current charging or discharging the node,  $C_{node}$  and  $V_{node}$  are the capacitance and the voltage variation of the nodes respectively. This equation reveals that a high speed can be achieved by: 1) minimizing the voltage swing at the node, nd 2) maximizing the current available for charging and discharging the capacitance of the node.

# 3.1.1 Transmitter with Inverter Driver

Transmitter with an inverter driver, as shown in Fig. 3.2, have been traditionally used for low-speed signaling.

Figure 3.2: Transmitter with inverter driver.

They are voltage-mode transmitters due to the high output output impedance and full swing voltage signaling. The impedance matching is normally realized with a serial termination resistor at the near end. Due to the full swing nature of inverters, the rising and falling times can not be improved by reducing the  $\Delta V$ , as shown in Eq. (3.1). Another observation is to reduce the resistance by increasing the transistor size of PMOS and NMOS, such that a increase of I can be achieved. An increase in capacitance at the node is also seen with the increase of the transistor size. As a result, no net speed improvement is achieved. Another drawback of inverter drivers is the variation of the output impedance due to the changing of the transistor operation mode. With the drain-source voltage variation, the output impedance is determined from the Table 3.1, where  $R_{NMOS-triode}$  and  $R_{PMOS-triode}$  are the output impedance of the NMOS and PMOS in triode region respectively, and  $R_{NMOS-saturation}$ ,  $R_{PMOS-saturation}$  are the NMOS and PMOS output impedance in saturation. Due to the large impedance of inverter, a strong reflection is seen at the output node during the transaction. Another observation is another strong reflection caused by the

large input impedance at the receiver end, which is also implemented with a inverter, resulting into multiple reflections of the signal at both near and far end of the channel, thereby limiting the transceiver data rate. Some other drawbacks are also seen including: 1) a large dynamic power consumption, 2) the injection of impulse currents to the power rails, and 3) sensitivity of the output voltage to supply and ground fluctuations.

Table 3.1: Output impedance of inverter drivers.

| Output Impedance | Impedance                                  | Operation mode                  |

|------------------|--------------------------------------------|---------------------------------|

| $Z_{out}$        | $R_{NMOS-triode}$                          | When $V_{out}$ is low           |

| $Z_{out}$        | $R_{PMOS-triode}$                          | When $V_{out}$ is high          |

| $Z_{out}$        | $R_{NMOS-saturation}//R_{PMOS-saturation}$ | When $V_{out}$ is in transition |

#### 3.1.2 Transmitter with LVDS Driver

The Low-voltage differential-signaling (LVDS) driver, as shown in Fig. 3.3, sources and sinks two well-defined currents to the channels [9]. LVDS drivers are current-mode transmitter drivers.

Figure 3.3: Transmitter with LVDS driver.

Because the total current drawn from the supply voltage and that injected to the ground rail are constant, the switching noise induced by LVDS drivers is minimum. Also, because the current conveyed to the channels is well-defined and is independent of the fluctuation of the supply voltage and ground bouncing, the effect of switching noise on the output current is minimum. Moreover, the differential output currents that have the same amplitude and flow in the opposite directions minimize the electro-magnetic interference exerted from the channels to neighboring devices.

The advantages of the LVDS driver are obvious, however, there are several drawbacks limiting the application of LVDS drivers: 1) the need for four transistors stacked between the supply voltage and ground rails limits the LVDS applications where only a low supply voltage is available, 2) a large input capacitance exists because both PMOS and NMOS switches must be driven at the same time, and 3) the need for four noisy buffer chains to drive the four switching transistors that must be sufficiently large to drive channels.

## 3.1.3 Transmitter with Open-Drain Driver

The open drain driver is shown in Fig. 3.4. The two NMOS transistors behave as a pair of complementary switches, the open-drain driver sinks a constant current from the channels by steering well-defined tail currents [4, 10].

Figure 3.4: Transmitter with open drain driver.

An open-drain driver is a typical current-mode driver and offers the following intrinsic advantages: 1) the constant current drawn from the channel minimizes both the noise coupled from the supply voltage and ground rails and the switching noise injected by the driver, 2) consumes less power at multi-Gbps data rates despite its DC power consumption, and 3) the swing of the signal represented by current can be large with a low supply voltage, this is

especially critical when the supply voltage is reduced. A number of drawbacks, however, exist with this configuration: 1) the multiplexing-at-output approach requires that the number of drivers is the same as the parallel-to-series ratio, as shown in Fig. 3.4. Because these drivers must be large enough to provide sufficiently large output currents to the channels, a large chip area, a high level of power consumption, and a high level of switching noise exist, 2) the common-mode component of the output current is high, causing difficulties in the design of the receivers, and 3) the unipolar signaling characteristics of the open-drain drivers also gives rise to a high level of electro-magnetic interference exerted from the channels to neighboring devices.

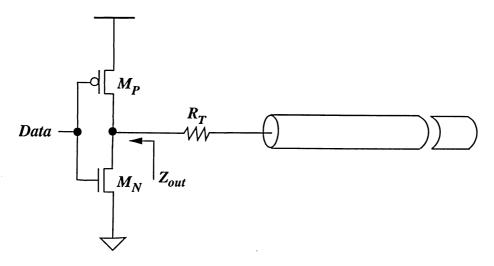

#### 3.1.4 Transmitter with Class AB Driver

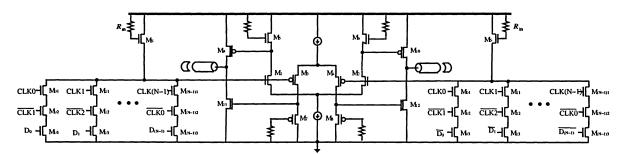

Class AB driver shown in Fig. 3.5 employs a pair of N and P-differential pairs in its preamplifier stage to achieve signal amplification. They are driven by the differential voltage signals from the output of the multiplexer and generate two pairs of differential voltage signals at output nodes of the two pairs, these signals are then used to drive the output stage, which operates in a push-pull mode. One key point in this transmitter is that all the transistors are biased in the saturation mode to avoid the delay of fully on and off.

Figure 3.5: Transmitter with class AB driver.

A high data rate, low power consumption, and a small chip area are achieved by multiplexing at low impedance nodes, the use of multiplexing-at-input approach, the use of active inductors at critical nodes, and the push-pull configuration of the driver. This configuration, however, has the following drawbacks: 1) although the voltage drop of one threshold voltage

$V_T$  caused by the active inductors in both the multiplexer and the pre-amplifier ensures that all transistors, especially those in the push-pull output stage, remain in saturation all the time to avoid the speed penalty of the complete turn-on/off of the transistors, the small output impedance of deep sub-micron CMOS technologies, gives rise to a direct path from the supply voltage to the ground. As a result, the output current is sensitive to the fluctuation of the supply voltage and ground bouncing, and 2) the output transistors, which are large in size, are in saturation all the time, resulting in a high level of static power consumption.

# 3.2 10 Gbps Current-Mode Transmitters

Three 10 Gbps current mode transmitters, including a 2-PAM  $V_{DD}$ -insensitive transmitter, a 4-PAM transmitter with a current-mirror driver, and a 2/4-PAM transmitter with class AB driver are proposed in this section.

## 3.2.1 $V_{DD}$ -Insensitive Transmitter

In this section, we propose a new fully differential current-mode transmitter with a low supply voltage sensitivity for 10 Gbps serial links. The transmitter consists of a modified full-swing pseudo-NMOS multiplexer that provides a rail-to-rail output voltage swing to a class AB pre-amplification stage, and a push-pull driver stage that operates in a full push-pull mode. The current-mode architecture of the transmitter ensures that the nodes of the transmitter are of a low-impedance characteristic. The rail-to-rail output voltage of the multiplexer ensure that the downstream class AB pre-amplification and push-pull driver stage are operated in a true class AB mode such that not only the static power consumption of the driver stage is minimized, the effect of the supply voltage fluctuation and that of ground bouncing on the output current are also minimized.

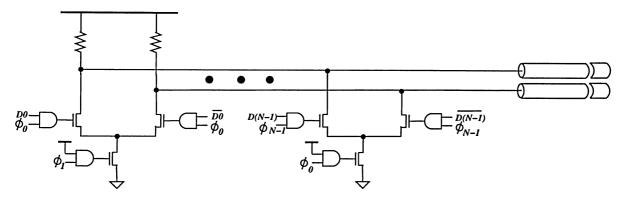

#### 1. Full-Swing Pseudo-NMOS Multiplexer

The schematic of the full-pseudo-NMOS multiplexer is shown in Fig. 3.6. The active shunt peaking inductors are formed by  $M_s$  and resistor  $R_{in}$ . The voltage swing of the output

$$V_A = V_{DD} - V_{TN}$$

(Logic-1),

$\overline{V_A} = \frac{3R_o}{3R_o + R_s} V_{DD}$  (Logic-0), (3.2)

Where  $R_s$  is the resistance seen from the source of  $M_s$  and  $\overline{M}_s$  and is given by  $\frac{1}{g_{ms}}$  at low frequencies,  $R_o$  is the output impedance of the  $M_{(N-1),(1,2,3)}$ . Due to the finite resistance of deep sub-Micron MOSFETs, both  $R_o$  and  $R_s$  are small. As a result, a small voltage swing at multiplexing nodes A and  $\overline{A}$  exists.

Figure 3.6: Full rail-to-rail N-to-1 multiplexer with inductive shunt peaking.  $W_S = \overline{W}_S = 10 \ \mu\text{m}$ ,  $W_{LP} = \overline{W}_{LP} = 3 \ \mu\text{m}$ ,  $W_{LN} = \overline{W}_{LN} = 1.5 \ \mu\text{m}$ ,  $W_{(N-1)} = W_{(N-2)} = W_{(N-3)} = 2 \ \mu\text{m}$ ,  $R_{in} = 7 \ K\Omega$ ,  $L = 0.13 \ \mu\text{m}$  is used for all transistors.

To increase the swing of the output voltage of the multiplexer, a nMOS-latch and a pMOS-latch are added, as shown in Fig. 3.6.  $M_{LP,LN}, \overline{M}_{LP,LN}$  form the latches to provide a rail-to-rail output voltage. Observed from Fig. 3.6, when A = Logic-1 and  $\overline{A} = \text{Logic-0}$ , transistors  $M_{LP}$  and  $\overline{M}_{LN}$  turn on,  $M_{LN}$  and  $\overline{M}_{LP}$  turn off. As a result, the multiplexing node A will be continually charged from  $V_{DD} - V_T$  to  $V_{DD}$  via  $M_{LP}$ , while the node  $\overline{A}$  will be continually discharged from  $\frac{3R_o}{3R_o + R_s}V_{DD}$  to 0 via  $\overline{M}_{LP}$  such that a full rail-to-rail output voltage swing is obtained.

## 2. Fully Push-Pull Class AB Driver

As shown in Fig. 3.7, the fully push-pull class AB driver employs a nMOS and a pMOS differential pairs with active inductors as its pre-amplification stage. The active inductors sharpen the voltage at the input nodes of the output drivers that have a large capacitance.

The rail-to-rail voltage from the preceding multiplexer ensures that nMOS and pMOS pairs are fully switched such that the rail and head current of the differential pairs is steered between their two arms. To ensure that the transistors in the output stage operate in a full push-pull mode, two latches are employed to overcome the voltage loss caused by the active inductors. The size of the latch transistors should be kept small to minimize their impact on the delay.