# Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2010

# On-chip interconnects modeling and timing driven buffer insertion

Alaa R. Abdullah *Ryerson University*

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations

Part of the Electrical and Computer Engineering Commons

#### **Recommended** Citation

Abdullah, Alaa R., "On-chip interconnects modeling and timing driven buffer insertion" (2010). Theses and dissertations. Paper 817.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

# **ON-CHIP INTERCONNECTS MODELING AND TIMING DRIVEN BUFFER INSERTION**

By

# Alaa R. Abdullah

Bachelor of Science, University of Technology, Baghdad, Iraq, 1989

A thesis Presented to Ryerson University in partial fulfillment of the requirement for the degree of **Master of Applied Science (MASc)**

In the program of

Electrical and Computer Engineering Toronto, Ontario, Canada, April, 2010

© 2010 Alaa R. Abdullah

# **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

Alaa R. Abdullah .....

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part at the request of other institutions or individuals for the purpose of scholarly research.

Alaa R. Abdullah .....

# **INSTRUCTIONS ON BORROWERS**

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below and give address and date.

| Name | Signature | Address | Date |

|------|-----------|---------|------|

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

|      |           |         |      |

## ABSTRACT

© Alaa R. Abdullah, 2010 Master of Applied Science (MASc) Electrical and Computer Engineering Ryerson University, Toronto, 2010

With the increasing effect of on-chip interconnects on nowadays VLSI design performance, modeling of interconnects becomes a necessity. GAM, TPN, and AWE are well known methods that are used to map an interconnect to an equivalent electrical circuit. In this thesis, a general approach that considers z-parameters is developed which allows the generation of equivalent RC, RLC, and RLCG circuits for both T and  $\Pi$  configurations. The performance of these generated circuits is compared to H-spice simulations by measuring the effect of interconnects on the transition times and delays under different conditions such as input transition times, interconnect lengths and capacitive loads. As a result, the a-configuration of AWE method reveals consistently an acceptable performance which makes it a good candidate to be utilized for buffer insertion.

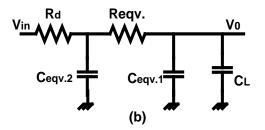

Buffer insertion is a popular technique used to reduce the delay of a long interconnect by segmenting it and inserting buffers among these segments. Therefore, the performance of this technique depends strongly on the accuracy of the considered interconnect model. However, using a model such as the RLCG of II-configuration which is derived from using the AWE method is not practical due to the complexity accompanied by such model which makes the derivation of closed-form expressions very complicated. To overcome this dilemma, the selected configuration has been mapped to a simple equivalent RC circuit. As a consequence, a new RC representation of on-chip interconnects is developed. Moreover, depending on the developed RC model, the proposed buffer insertion technique shows superiority over previously published works.

# AKNOWLEDGEMENT

This thesis would not have been possible without help my wife Nissreen Hasan. She has always been the main source of support and confidence in my life and I have relied on her constant encouragement and love throughout my graduate studies. Her love and sacrifice for me will always be a great source of my inspiration.

In my passion, to whom (my brother Adnan) who finish his life sacrificing, supporting and encouraging me to reach this successful time, I present this work.

I would like to express my deep gratitude to my supervisor Dr. Adnan Kabbani for his support and encouragement during my research. I am very grateful for his guidance and valuable advice.

# TABLE OF CONTENTS

| ABSTRACT                       | iv   |

|--------------------------------|------|

| Table of Contents              | ix   |

| List of Tables                 | xiii |

| List of Figures                | ix   |

| List of Appendices             | xiv  |

| List of Symboles and Notations | xv   |

# **CHAPTER 1**

| Introduction1 |  |

|---------------|--|

|               |  |

## CHAPTER 2

| Background                                        | 5  |

|---------------------------------------------------|----|

| 2.1 Introduction                                  | 5  |

| 2.2 Interconnect Models                           | 5  |

| 2.2.1 Interconnect Lumped Models                  | 5  |

| 2.2.2 Distributed Transmission Line Models        | 8  |

| 2.3 Transmission Line theory                      | 11 |

| 2.3.1 Transmission Lines                          | 11 |

| 2.4 Interconnects in VLSI Circuits                | 15 |

| 2.4.1 RC- Delay Models                            | 15 |

| 2.4.2 Elmore Delay Models                         | 16 |

| 2.4.3 High Order Delay Models                     | 18 |

| 2.5 Methodologies Used for Interconnect Modeling  | 19 |

| 2.5.1 Global Approximation Method (GAM)           | 19 |

| 2.5.2 Two-Port Network (TPN)                      | 22 |

| 2.5.3 Asymptotic Waveform Evaluation (AWE) Method | 27 |

| 2.6 Summary                                       | 28 |

## CHAPTER 3

| Generalizing the GAM, TPN and AWE Methods Using Z-Parameters | 29 |

|--------------------------------------------------------------|----|

| 3. 1 Introduction                                            | 29 |

| 3.2 | Z-F  | Parameter Representation for the Telegraph Equations                  | . 30 |

|-----|------|-----------------------------------------------------------------------|------|

| 3.3 | Z-F  | Parameter Modeling For Interconnect Based on GAM, TPN and AWE Methods | . 32 |

| 3   | .3.1 | GAM Based Z-Parameter Modeling                                        | . 32 |

| 3   | .3.2 | TPN Based Z-Parameter Modeling                                        | . 39 |

| 3   | .3.3 | AWE Based Z-Parameter Modeling                                        | . 45 |

| 3.4 | Su   | nmary                                                                 | . 51 |

# **CHAPTER 4**

| Performa | nce Comparison and Characterization of the GAM, TPN and AWE Methods | 52   |

|----------|---------------------------------------------------------------------|------|

| 4.1 In   | troduction                                                          | . 52 |

| 4.2 V    | erification of the Simulation Ranges                                | . 52 |

| 4.2.1    | Range of the Interconnect Length                                    | . 52 |

| 4.2.2    | 2 Range of the Capacitive Load                                      | . 53 |

| 4.2.3    | Range of the Input Transition Time                                  | 53   |

| 4.3 M    | lodels Evaluation                                                   | 53   |

| 4.3.1    | Delay Based Comparison for the RLCG Models                          | . 53 |

| 4.3.2    | 2 Output Transition Time Based Comparison for the RLCG Models       | . 56 |

| 4.4 S    | ummary                                                              | 57   |

# **CHAPTER 5**

| Wire Segmentation, Buffer Insertion and Buffer Sizing Techniques for Minimizing an Intercon Delay |    |

|---------------------------------------------------------------------------------------------------|----|

| 5.1 Introduction                                                                                  |    |

| 5.2 Buffer Insertion (Repeaters)                                                                  | 59 |

| 5.3 Wire Segmentation                                                                             | 51 |

| 5.4 Buffer Sizing                                                                                 | 52 |

| 5.5 Mapping an RLCG Model into an RLC Model                                                       | 54 |

| 5.6 Mapping an RLC Model into an RC Model                                                         | 55 |

| 5.7 Closed-Form Expression for Optimum Interconnect Delay                                         | 73 |

| 5.8 Interconnect Critical Length and Optimum Buffer Sizing for Minimizing the Delay7              | 74 |

| 5.9 Summary                                                                                       | 77 |

# **CHAPTER 6**

| Conclusions and Future V | Works | 78 |

|--------------------------|-------|----|

|--------------------------|-------|----|

| REFERENCES | <br> |

|------------|------|

|            |      |

|            |      |

|            |      |

## APPENDIX A

## **APPENDIX B**

Driving Z-Parameter Modeling of the Π-Configuration Based on the AWE Method ......95

## **APPENDIX C**

# LIST OF TABLES

| Table 2.1.         | Six sets of network parameters for two-port network method                                 | .23  |

|--------------------|--------------------------------------------------------------------------------------------|------|

| <b>Table 5.1</b> . | Error calculations for the vdd/2 delay between the RLC model and the improved R            | C    |

|                    | model for different R1, C1 and                                                             | 69   |

| Table 5.2.         | The error calculations of the $vdd/2$ delay for the circuits shown in Figure 5.12 (a, b    | ))   |

|                    | for different driver and load buffer sizes and interconnect lengths                        | 72   |

| Table 5.3.         | Error calculations for the $vdd/2$ delay of the RLC model and the equivalent RC model      | odel |

|                    | for different R1, C1 and C3                                                                | .73  |

| Table 5.4.         | The performance of buffer insertion for using proposed model vs. previous published models | .77  |

# LIST OF FIGURES

| Figure 2.1: Interconnect Lumped Capacitive Model                                             |

|----------------------------------------------------------------------------------------------|

| <b>Figure 2.2</b> : Interconnect Lumped RC Model (A) Π-Configuration (B) T- Configuration    |

| <b>Figure 2.3</b> : Interconnect Lumped RLC Model (A) Π-Configuration (B) T-Configuration7   |

| Figure 2.4: Interconnect Lumped RLCG Model (A) Π- Configuration (B) T- Configuration 8       |

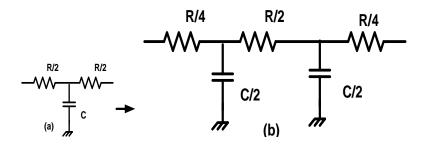

| Figure 2.5: Lumped Circuit Approximations For Distributed RC Lines (A) RC T-Configuration    |

| (B) RC 2T- Configuration                                                                     |

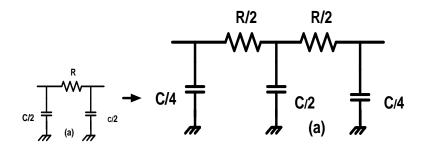

| Figure 2.6: Lumped Circuit Approximations For Distributed RC Lines (A) RC П- Configuration   |

| (B) RC 2Π- Configuration                                                                     |

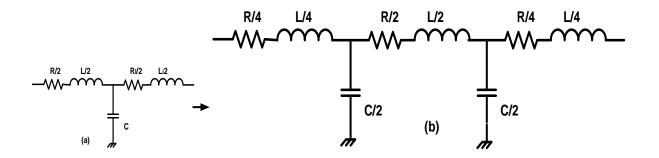

| Figure 2.7: Lumped Circuit Approximations For Distributed RLC Lines (A) RLC T-               |

| Configuration (B) RLC 2T- Configuration                                                      |

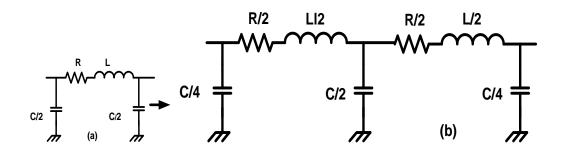

| Figure 2.8: Lumped Circuit Approximations For Distributed RLC Lines (A) RLC П- Configuration |

| (B) RLC 2Π- Configuration                                                                    |

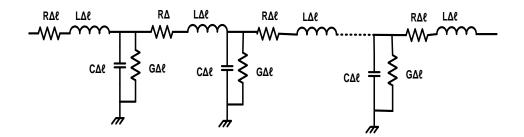

| Figure 2.9: Lumped Circuit Approximations For Distributed RLCG Lines (A) RLCG T-             |

| Configuration (B) RLCG 2T- Configuration                                                     |

| Figure 2.10: Lumped Circuit Approximations For Distributed RLCG Lines (A) RLCG Π-            |

| Configuration (B) RLCG 2П- Configuration 10                                                  |

| <b>Figure 2.11</b> : A Section Of An RLCG Π- Configuration Of Transmission Line              |

| Figure 2.12: Equivalent Circuit Model Of A Lossless Transmission Line                        |

| Figure 2.13: Equivalent RLCG Circuit Model Of A Lossy Transmission Line                      |

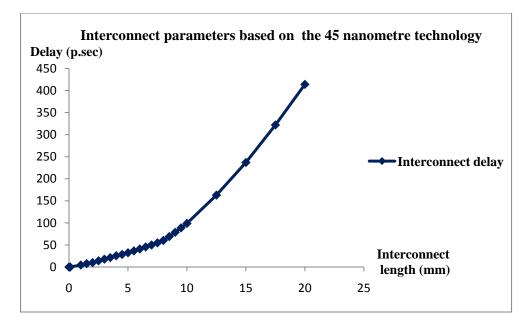

| Figure 2.14: The Relationship Between The Interconnect Delay And Interconnect Length 16      |

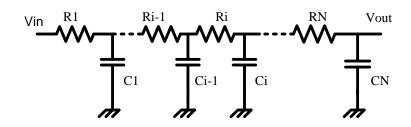

| Figure 2.15: Distributed RC-Model Of Interconnect                                            |

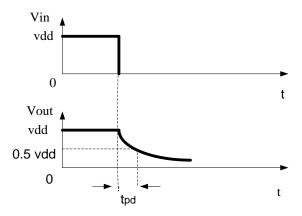

| Figure 216: Delay Calculation At Vdd/217                                                     |

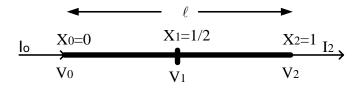

| Figure 2.17: Interconnect With The Assumption Of The Three Grid Points [79]                  |

| Figure 2.18: Shows The Variables For A Two-Port Network                                      |

| Figure 2.19: Current Requirements Of The Ports                                               |

| Figure 2.20: Cascade Connections For Two-Port Networks                                       |

| Figure 2.21: T-Configuration.    26                                                          |

| Figure 2.22: The Equivalent Z-Parameter Of T-Model                                           |

| Figure 3.1: Distributed Z-Parameter Model Of A Transmission Line                                 |

|--------------------------------------------------------------------------------------------------|

| Figure 3.2: The Circuit After Manipulations Of The Voltage Equations                             |

| Figure 3.3: The Z-Parameter Of T-Configuration After The Voltage And Current Equations Are       |

| Manipulated                                                                                      |

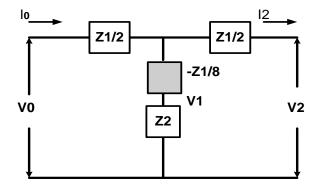

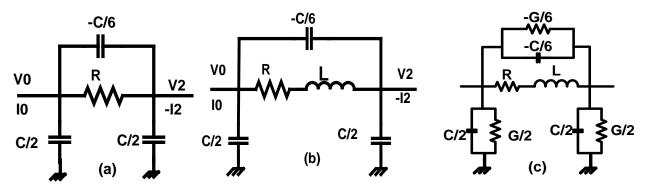

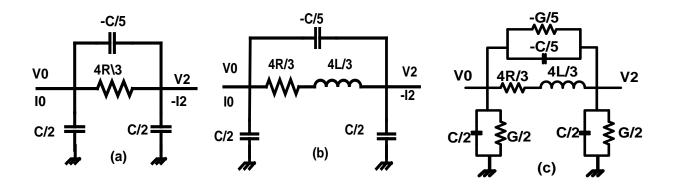

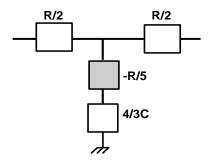

| Figure 3.4: Interconnect T-Configuration Based On The GAM For (A) RC, (B) RLC And 36             |

| (C) RLCG Interconnects                                                                           |

| Figure 3.5: The Circuit After Manipulations Of The Current Equations                             |

| Figure 3.6: The Z-Parameter Of II-Model After The Voltage And Current Equations Are              |

| Manipulated                                                                                      |

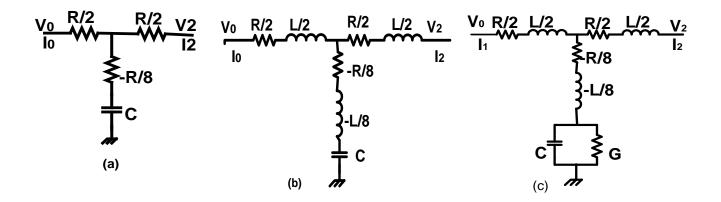

| Figure 3.7: Interconnect Π- Configuration Based On The GAM For (A) RC, (B) RLC And (C)           |

| RLCG Interconnects                                                                               |

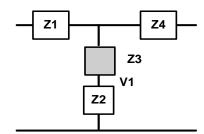

| Figure 3.8: Z-Parameter Model Of The T- Configuration Based On The TPN Method                    |

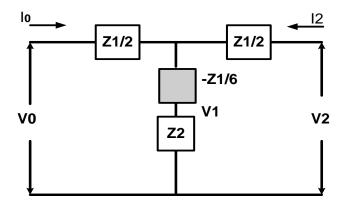

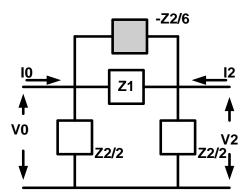

| Figure 3.9: Interconnect T-Model Based On The TPN Theory For An (A) RC (B) RLC And 43            |

| (C) RLCG Interconnects                                                                           |

| Figure 3.10: Interconnect Z-Parameters Model Of The Π- Configuration Based On The TPN 44         |

| Figure 3.11: Interconnect IT - Model Based On The TPN Theory For An (A) RC (B) RLC And 45        |

| (C) RLCG Interconnects                                                                           |

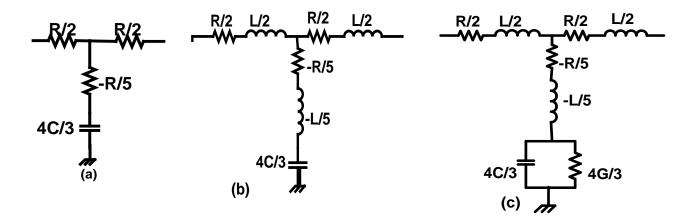

| Figure 3.12: The Improved T-Model In The Z-Parameter                                             |

| Figure 3.13: The T- Configuration Based On The AWE For An (A) RC, (B) RLC And (C) RLCC           |

| Interconnects                                                                                    |

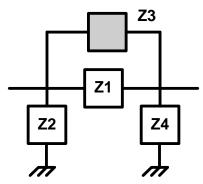

| Figure 3.14: The Assumption Of The П- Configuration                                              |

| Figure 3.15: II-Configuration Based On The AWE For An (A) RC, (B) RLC And (D) RLCG               |

| Models                                                                                           |

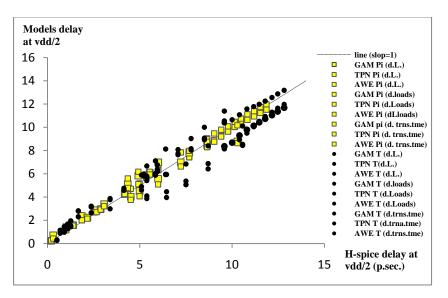

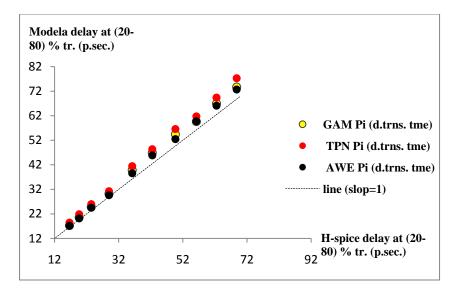

| Figure 4.1: The Comparison Of The Vdd/2 Delay Between The RLCG Models And H-Spice                |

| Simulation For Different Interconnect Lengths, Capacitive Loads And Output Transition Times.52   |

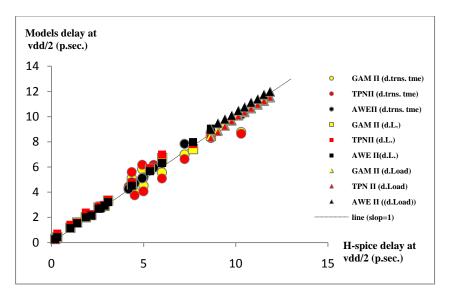

| Figure 4.2: The Comparison Of The Vdd/2 Delay Between The Π Configuration And H-Spice            |

| Simulation For Different Interconnect Lengths, Capacitive Loads And Output Transition Times.50   |

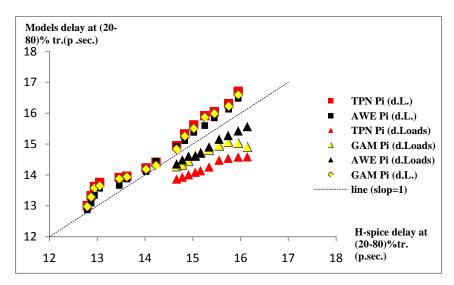

| <b>Figure 4.3</b> : The Comparison Of The Output Transition Time Between The Π Configuration And |

| H-Spice Simulation For Different Interconnect Lengths And Capacitive Loads                       |

| Figure 4.4: The Comparison Of The Output Transition Time Between The Π Configuration And         |

| H-Spice Simulation For Different Output Transition Times                                         |

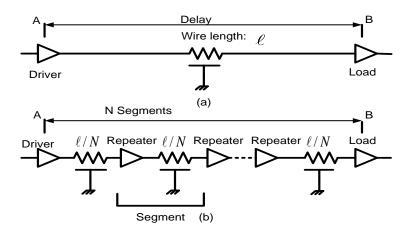

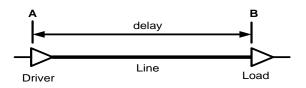

| Figure 5.1: Wire (A) Without Repeaters, (B) With Repeaters                            | 60         |  |  |  |

|---------------------------------------------------------------------------------------|------------|--|--|--|

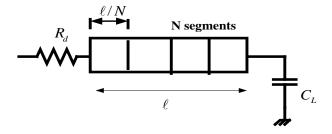

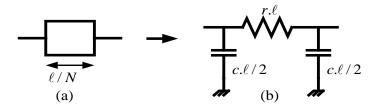

| Figure 5.2: Interconnect With N Segments                                              | 61         |  |  |  |

| Figure 5.3: Interconnect (A) One Segment, (B) RC П-Model                              |            |  |  |  |

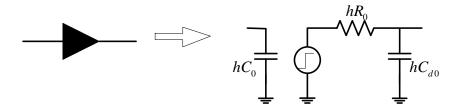

| Figure 5.4: The Model Of A Buffer Has Size $h$ As A Switch-Level RC Circuit           |            |  |  |  |

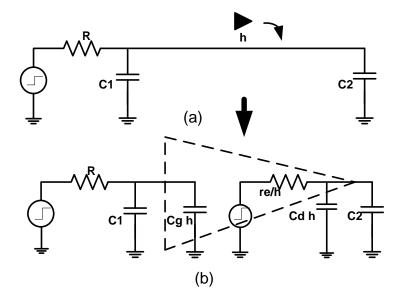

| Figure 5.5: Delay Reduction By Buffer Insertion (A) Wire Without A Buffer (B) Wire W  | With A     |  |  |  |

| Buffer                                                                                |            |  |  |  |

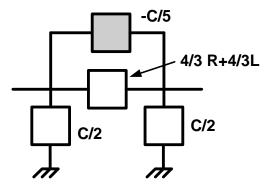

| Figure 5.6: The RLCG Model Of The Π-Configuration Which Was Derived From Using        | g The AWE  |  |  |  |

| Method.                                                                               |            |  |  |  |

| Figure 5.7: The RLC Model Of The Π Configuration Which Was Derived From Using         | The AWE    |  |  |  |

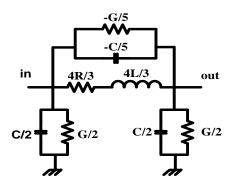

| Method                                                                                |            |  |  |  |

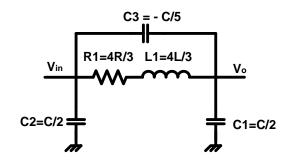

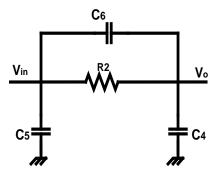

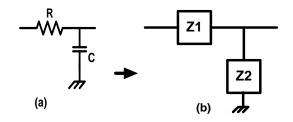

| Figure 5.8: The RC Equivalent Circuit For The Model Shown In Figure 5.7               |            |  |  |  |

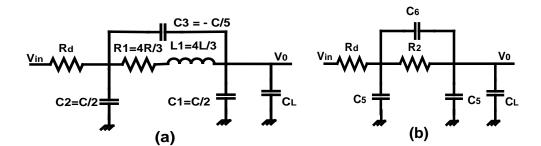

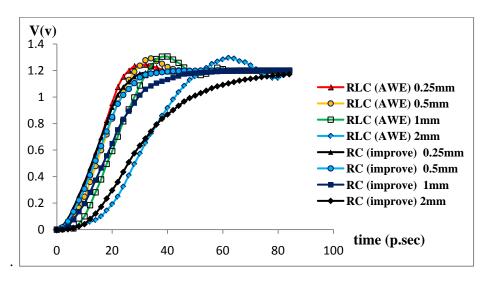

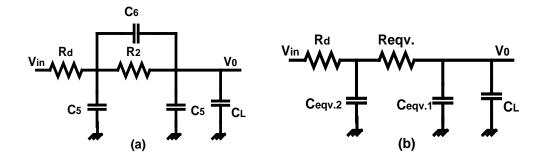

| Figure 5.9: The Comparison Between The (A) RLC (B) Improved RC Models                 | 67         |  |  |  |

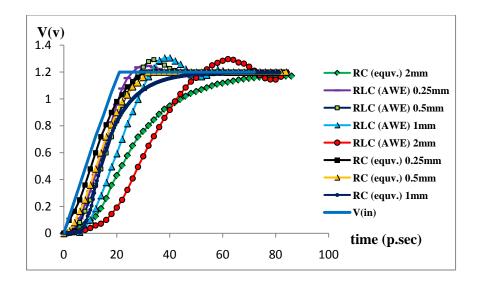

| Figure 5.10: The Output Responses For The RLC Model Which Was Derived From Usi        | ng The     |  |  |  |

| AWE Method And The RC Improved For Different Interconnect Lengths                     |            |  |  |  |

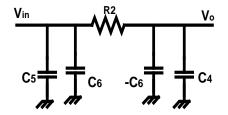

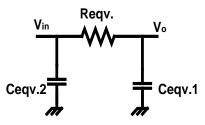

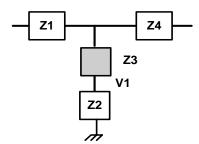

| Figure 5.11: The Equivalent RC Circuit For The Circuit Shown In Figure 5.8.           | 69         |  |  |  |

| Figure 5.12: The Equivalent RC Circuit For The Circuit Shown In Figure 5.8.           |            |  |  |  |

| Figure 5.13: Circuit Test (A) The Improved RC Circuit (B) The Equivalent RC Circuit.  |            |  |  |  |

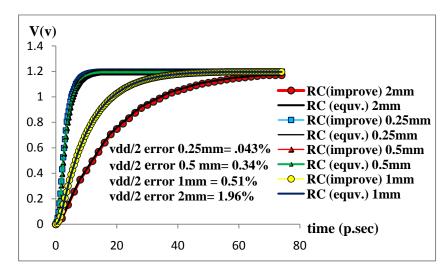

| Figure 5.14: The Output Responses For The Improved RC And Equivalent RC Models        | For        |  |  |  |

| Different Interconnect Lengths.                                                       | 71         |  |  |  |

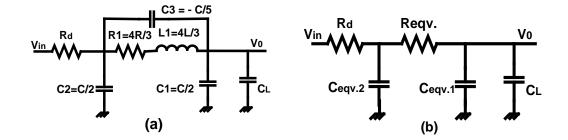

| Figure 5.15: Circuit Test (A) The Improved RC Circuit (B) The Equivalent RC Circuit.  | 72         |  |  |  |

| Figure 5.16: The Output Responses For The RLC Model (AWE) And The Equivalent R        | C Models   |  |  |  |

| For Different Interconnect Lengths.                                                   |            |  |  |  |

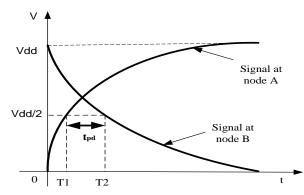

| Figure 5.17: The Vdd/2 Delay Calculation From Point A To Point B As Illustrated In Fi | gure 5.1a. |  |  |  |

|                                                                                       |            |  |  |  |

| Figure A-1: Interconnect Lumped Model (A) RLC-Model, (B) Z-Model.                     |            |  |  |  |

| Figure A-2: Represents The Improved T-Model In Z-Parameter.                           |            |  |  |  |

| Figure A-3: Represents The RC T-Model Based On AWE                                    |            |  |  |  |

| Figure B-1: Interconnect Z-Parameter Of Lumped Model.                                 |            |  |  |  |

| Figure B-2: Represents The Improved П-Model In Z-Parameter                            |            |  |  |  |

| Figure B-3: Represents The Interconnect RLC $\Pi$ -Model Based On The AWE Method.     | 100        |  |  |  |

| Figure C-1: Interconnect With Driver And Load Buffers.                                | 101        |  |  |  |

| Figure C- | 2: Circuit Representation | Of Figure C-1 |  | 01 |

|-----------|---------------------------|---------------|--|----|

|-----------|---------------------------|---------------|--|----|

# LIST OF APPENDICES

| Appendix A : Driving Z-Parameter Modeling of the T-Configuration Based on the AWE Method                                    |

|-----------------------------------------------------------------------------------------------------------------------------|

| Appendix B : Driving Z-Parameter Modeling of the П-Configuration Based on the AWE Method                                    |

| Appendix C : Closed-Form Expressions for Interconnect Critical Length, Minimum Buffer Sizing and Optimum Interconnect Delay |

# LIST OF SYMBOLE AND NOTATIONS

| r        | Interconnect resistance per unit length      |

|----------|----------------------------------------------|

| l        | Interconnect inductance per unit length      |

| С        | Interconnect inductance per unit length      |

| 8        | Interconnect conductance per unit length     |

| R        | Interconnect resistance                      |

| L        | Interconnect inductance                      |

| С        | Interconnect capacitance                     |

| G        | Interconnect conductance                     |

| $\ell$   | Interconnect length                          |

| v        | Signal propagation speed                     |

| $t_{pd}$ | Propagation delay                            |

| $Z_o$    | Line characteristic impedance                |

| γ        | Propagation constant                         |

| α        | Signal attenuation                           |

| β        | Phase constant                               |

| ω        | System frequency                             |

| $V_{in}$ | Input voltage                                |

| $V_o$    | Output voltage                               |

| Ν        | Number of line segments                      |

| $X_n$    | The selected grid points on the interconnect |

| (')      | Derivative                                   |

| $Z_n$    | Circuit impedance                            |

| $Y_n$    | Circuit admittance                           |

| IC       | Integrated circuit                           |

- $\ell_{crt.}$  The interconnect length where the interconnect delay is in linear proportion with its length

- $R_0$  Output resistance of a unit inverter

- $C_0$  Capacitance of a unit inverter

- $c_{g}$  Gate capacitance of a unit inverter

- $C_{d0}$  Drain capacitance of a unit inverter

- $R_d$  The output resistance of the driver buffer

- $C_L$  The gate capacitance of the load buffer

- $C_N$  Unit capacitance of NMOS transistor

- *h* Buffer width

- VLSI Very Large Scale Integration

- SoC System on-Chip

- MOS Metal Oxide Semiconductor

- *KVL* Kirtchhoff's Voltage Law

- KCL Kirtschhoff's Current Law

- TSMC Taiwan Semiconductor Manufacturing Company

- DSM Deep sub-micron

- $a_n, b_n$  Frames coefficients

- $T, \Pi$  Network configurations

- GAM Global Approximation Method

- TPN Two-Port Network Method

- AWE Asymptotic Waveform Evaluation Method

- *U.A.* Unit area

- *No.S* Number of segments

- DWB Delay with buffers

- DNB Delay without buffers

- *d.trns.tme*. Different transition times

- *d.Loads* Different loads

# *d.L.* Different interconnect lengths

(20-80)% *Delay* Transition time

## **CHAPTER 1**

## Introduction

With the continued down scaling of CMOS technology to reach nanometre scale and the requirement for high speed, (SoC) interconnect emerges as one of the main performance limiting factors. As a matter of fact, it has been shown in [1] that interconnect delay is more than the logic delay and reaches 70-80% of all signal delays in a chip at 0.18µm technology. Thus, modeling and accounting for interconnect effects as early as possible in the design process becomes a major concern of VLSI designers. Modeling an interconnect expresses the characterization of the interconnect and its effects on the circuit's performance. On-chip interconnects modeling historically began in 1959 when Fairchild Semiconductor took the first step towards manufacturing an integrated circuit IC. In those days, interconnect effects were ignored because interconnects were short and circuits were simple. Therefore, an interconnect was modeled as a short circuit. With the scaling of the minimum feature size, interconnect effects started to be considerable. The first interconnect effect had to be considered when interconnect capacitances had become comparable to the gate capacitance. Thus, an interconnect was modeled as a single lumped capacitance [2-4]. With the increase in the device densities per unit area, the interconnect density has also correspondingly increased. Thus, the cross-sectional area of interconnects had been reduced to provide more interconnect per unit area [5]. Also, the global wires across the chip increased in length. So, because of the decrease in the cross-sectional area and increase in the interconnect length, the interconnect resistance could no longer be neglected and had to be considered in interconnect modeling. Therefore, the interconnect was modeled as an RC circuit [6-8]. With the demand of increasing the speed of on-chip circuits and using wider wire for distributing the clock, especially in the global wires, the inductance effect of on-chip interconnects became more important. Therefore, accounting the interconnect inductance in the interconnect modeling is crucial [9-13]. Using multilayer techniques to increase the functionality of on-chip circuits with long wires, the effects of the dielectric loss is considered to accurately model the interconnect effects [1], [14,15].

Interconnect delay is a major concern of System on-Chip design. Basically, the interconnect delay in SoC is due to the line resistance, capacitance, inductance and dielectric conductance. These

elements are in direct proportion to the interconnect length ( $R = r.\ell$ ,  $L = l.\ell$ ,  $C = c.\ell$ ,  $G = g.\ell$ ). Elmore delay modeling for an RC interconnect [16] shows that the interconnect delay is in quadratic proportion to the interconnect length ( $t_{pd} \Rightarrow r.c.l^2$ ). This quadratic of interconnect delay with interconnect length significantly degrades the performance of VLSI circuits with long wires. In order to reduce this quadratic increase in delay with interconnect length, repeaters (or a series of CMOS inverters separated by interconnects) are inserted along these long interconnect lines to partition the lines into shorter sections, thereby reducing the total delay of the interconnect path [17-22].

Buffer insertion technique is shown to be an effective technique for interconnect delay optimization. Buffer insertion problem can be partitioned into sizing as well as segment length and width determination. Some authors considered these two problems independently [23,24]. While others tackled both problems [25-31].

In this thesis we derive general z-parameter models for both T and  $\Pi$  configurations targeting the Global Approximation Method (GAM), Two-Port Network (TPN) and Asymptotic Waveform Evaluation (AWE). The general z-parameter models allow easy and directly switching between the RC, RLC and RLCG models for both T and  $\Pi$  configurations for GAM, TPN and AWE modeling techniques. The interconnect RC, RLC and RLCG models were tested for different interconnect lengths, capacitive loads and input transition times and are presented in this thesis. The test results show that the RLCG model of the  $\Pi$  configuration which was derived from using the AWE method exhibits more acceptable, satisfactory and consistent results than other models. Thus, this model was selected as the candidate model for buffer insertion analysis. We will use this model to reduce the on-chip interconnect delay by considering the buffer insertion technique and Elmore delay modeling. By using this model, it is difficult to derive the closed-form expression for the on-chip interconnect delay based on the Elmore delay model Because of the model complexity. Therefore, modifying the model is crucial. Some modifications have been applied on the model to reduce this complexity. The first modification was eliminating the effect of the dielectric loss from the model and converting the model from RLCG model to RLC model. The second modification was mapping the interconnect RLC model into the RC model. The effect of the interconnect inductance is

compensated in the RC model. This generates an improved RC model. This model has a negative capacitance connected in the upstream of the model. We modified it to the down stream of the model and generated an equivalent RC model. This model is simple and easy to use for calculating the on-chip interconnect delay using buffer insertion technique. Moreover, this model has the simplicity of general RC model and the accuracy of the RLC model.

The thesis is organized as follows: The history of the interconnect modeling in VLSI circuits is briefly reviewed in Chapter 2. Model characterizations are also reviewed in chapter 2 which is started from the simple model represented as a short circuit and changes with time to C, RC, RLC and RLCG [2-8],[9-13],[32-35],[36-64]. Also, in Chapter 2, basic transmission line theory is briefly reviewed. The theory of transmission lines is discussed for types of transmission lines: lossless LC transmission lines, lossy RLCG transmission lines. Furthermore, brief discussions on the GAM, TPN and AWE methods are addressed.

Z-parameters of Telegraph equations are derived in Chapter 3. A general form of z-parameters of both T and  $\Pi$  configurations from using the GAM, the TPN and the AWE are presented respectively. Using these general z-parameter models, eighteen different RC, RLC and RLCG models are generated.

In chapter 4, the comparison for the vdd/2 and transition time between the H-spice and the RLCG models of T and  $\Pi$  configurations which were derived from using the GAM, TPN and AWE methods for different interconnect lengths, input transition times and capacitive loads was introduced. The comparison revealed that the RLCG model of the  $\Pi$  configuration which is derived from using the AWE method exhibits more acceptable and satisfactory results than other models.

The buffer insertion technique is used in Chapter 5 to reduce the on-chip interconnect delay. The equivalent RC model was considered and the Elmore delay model was used to derive closedform expressions for the interconnect critical length, minimum buffer sizing and optimum interconnect delay. In this chapter, these closed-form expressions were compared with other studies. Conclusions and future works are provided in Chapter 6. In Appendix A, a general z-parameter model of the T configuration is presented based on the AWE method. A general z-parameter model is derived based on the AWE method for the  $\Pi$  configuration in Appendix B. In Appendix C, closed-form expressions for interconnect critical length, minimum buffer sizing and optimal interconnect delay are derived.

## **CHAPTER 2**

# Background

#### 2.1 Introduction

In VLSI, interconnect can be defined as the path, usually a metal line, that joins two or more points in the circuit. When a signal propagates through it, it exhibits some responses which affect the signal behaviour and integrity. Interconnect responses against the propagation signal such as delay, noise, reflection, etc. depends on many factors which may be grouped as interconnect and signal dependent factors. The first group includes factors such as interconnect dimensions, material, etc. The second group consists of factors such as the signal's amplitude, transition time, etc.

With the down scaling of technology, interconnects start to play a major role in determining the design performance. Thus, this chapter is dedicated for reviewing the state of the art of on-chip interconnect modeling.

#### 2.2 Interconnect Models

On-chip interconnect modeling tries to describe the behaviour of on-chip interconnects in terms of their dimensions, materials, and propagation signal properties. Accurate models are the models which are able to characterize the interconnect behaviour accurately to reach the real behaviour. Interconnect modeling can be classified based on the signal wavelength into: lumped and distributed models.

#### **2.2.1 Interconnect Lumped Models**

Interconnects have a distributed nature and they should be modeled accordingly. However, when the signal wavelength is larger than the interconnect length, modeling interconnects as lumped elements provides good accuracy and reduce the modeling complexity. Therefore, for high-speed digital circuits, local interconnects, which is the majority of on-chip interconnects, can be safely treated as lumped models because their lengths are negligible compared to the wavelength of the traveling signals [1].

#### 2.2.1.1 C- Lumped Models

In the 1990s, when the gate's capacitance dominated the interconnect's parasitic capacitance, interconnects were modeled as short circuits. However, with the scaling of the minimum feature, the interconnect parasitic capacitance became comparable to the gate capacitance. Thus, an interconnect was modeled as a lumped capacitance [2-4]. As shown in Figure 2

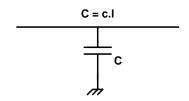

Figure 2.1: Interconnect lumped capacitive model.

In Figure 2.1,  $C = c.\ell$  where C is the line capacitance, c is the line capacitance per unit length and  $\ell$  is the interconnect length.

#### 2.2.1.2 RC- Lumped Models

The resistance effect of on-chip interconnect is significant for global interconnects and it becomes even more prominent with the technology downscaling [5-6]. For such interconnects, modeling the resistance effect is necessary to achieve good accuracy. Figure 2.2 shows an RC-lumped interconnect modeling.

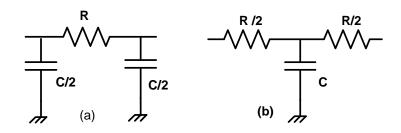

Figure 2.2: Interconnect lumped RC model (a) Π-configuration (b) T- configuration.

In Figure 2.2,  $R = r.\ell$  where R is the line resistance,  $C = c.\ell$  where C is the line resistance and c, r are interconnect unit capacitance and resistance respectively.

As illustrated in Figures 2.1, the C-lumped model has only one node. So, there is no voltage difference along the line whereas the RC-lumped model as shown in Figure 2.2 has two nodes in

the Π-configuration and three nodes in the T- configuration. Thus, the analysis of the RC-lumped model is more complicated than the C-lumped model due to the changes in the node voltages [7, 8], [32-35].

#### 2.2.1.3 RLC- Lumped Models

The increased demand for faster VLSI chips pushes ASIC designers to use the wide wire upper metal layers [9-13], [36-55]. For global interconnects such as clock distribution, moreover, this also pushes the industry to develop low resistivity materials such as copper [42, 46] and low k materials to reduce the interconnect capacitance [42, 46]. These advance technologies allowed longer and denser interconnects which increased the inductance effect. Thus, modeling such interconnects considers their inductance effects [54]. Therefore, interconnects are modeled as lumped RLC circuits as shown in Figure 2.3.

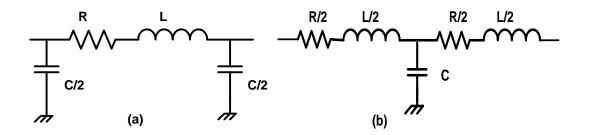

Figure 2.3: Interconnect lumped RLC model (a) Π-configuration (b) T-configuration.

In Figure 2.3,  $L = l.\ell$  where L is the line inductance and l is the line inductance per unit length.

The amount of inductance effects presented in an RLC line depends on the ratio between the RC and the LC time constant of the line [55]. Hence, as inductance effects increase, the LC time constant dominates the RC time constant.

By combining all these effects with the dielectric loss G, RLCG configuration becomes necessary to characterize the behaviour of the interconnect accurately.

#### 2.2.1.4 RLCG- Lumped Models

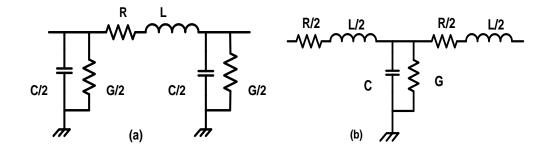

In VLSI circuit fabrication, G represents the conductivity of the dielectric layers such as silicon dioxide (SiO<sub>2</sub>) and silicon nitride (Si<sub>3</sub>N<sub>4</sub>) located between an interconnect and the substrate layer. Generally, there are many benefits from using dielectric layers in the chip fabrication. First of all, they are used to isolate active circuits from each other and to provide mechanical and chemical protection to the device itself. Second, dielectric layers are widely used in the fabrication of components essential to circuit functionality such as capacitors and MOS transistors. Lastly, dielectric layers are also used as masking materials during wafer fabrication. However, naturally there are no ideal dielectric materials. Thus, they reveal some conductivity. Although this conductivity is very low, it behaves as a path for the current to pass through it and cause power loss. This loss will affect the signal integrity and delay [56, 57]. This loss has to be considered in the interconnect modeling to represent the real behaviour of the interconnect. In this case, the interconnect takes another shape of configuration, which is the RLCG model as shown in Figure 2.4, where  $G = g.\ell$ , G is the line conductance and g is the line conductance per unit length.

Figure 2.4: Interconnect lumped RLCG model (a) Π- configuration (b) T- configuration.

#### 2.2.2 Distributed Transmission Line Models

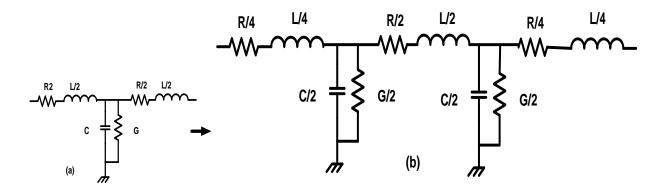

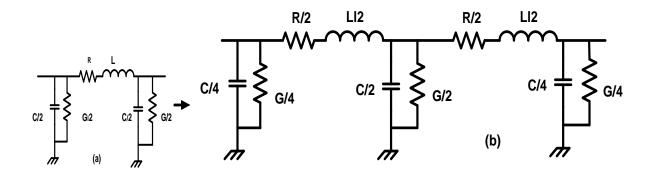

When the signal transition time becomes less than or comparable to the signal traveling time on interconnects, lumped models do not characterize the behaviour of interconnects with adequate accuracy. Therefore, the distributed transmission line models are needed to fully consider this behaviour. Figures (2.5-2.10) represent the equivalent circuits of the distributed 2T and 2 $\Pi$  models for one lump of interconnect T and  $\Pi$  configurations [64].

Figure 2.5: Lumped circuit approximations for distributed RC Lines (a) RC T- configuration (b) RC 2T- configuration.

Figure 2.6: Lumped circuit approximations for distributed RC Lines (a) RC П- configuration (b) RC 2П- configuration.

Figure 2.7: Lumped circuit approximations for distributed RLC Lines (a) RLC T- configuration (b) RLC 2T- configuration.

Figure 2.8: Lumped circuit approximations for distributed RLC Lines (a) RLC  $\Pi$ - configuration (b) RLC  $2\Pi$ - configuration.

Figure 2.9: Lumped circuit approximations for distributed RLCG Lines (a) RLCG T- configuration (b) RLCG 2T- configuration.

Figure 2.10: Lumped circuit approximations for distributed RLCG Lines (a) RLCG Пconfiguration (b) RLCG 2П- configuration.

#### 2.3 Transmission Line Theory

Transmission line theory discusses the behaviour of a transmission line during signal propagation. When an electrical signal propagates through a transmission line, the voltage and current along the transmission line can vary in magnitude and phase as a function of position. Therefore, standard circuit theory cannot be employed on an electrical network; an alternative analysis must be applied to the system. As we know, transmission line theory represents a traditional topic in electrical engineering, especially in the area of power transmission. This topic received renewed attention because transmission line theory has found new and important applications in the area of highspeed VLSI circuits. Interconnect in a high-speed VLSI circuit reveals nonlinear delay effects. So, the interconnect can be modeled as a transmission line loaded with nonlinear element such as a capacitance. This nonlinearity may lead to many new effects such as instability and generation of higher order harmonics. The mathematical models of transmission lines with nonlinear loads consist of the linear partial differential equations describing the current and voltage dynamics along the lines together with the nonlinear boundary conditions imposed by the nonlinear loads connected to the lines. These nonlinear boundary conditions make the mathematical treatment very difficult. Moreover, in a high-speed VLSI circuit, the transmission line is stripped compared with the wavelength, and the transmission line can be characterized by the propagation constant and characteristic impedance.

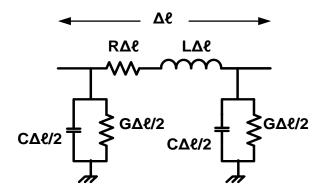

#### 2.3.1 Transmission Lines

The transmission line, as the name implies, is the line used to transmit an electrical signal from one point to another. When the electrical signal propagates through the transmission line, the line exhibits resistive, capacitive, inductive and conductive effects against the signal. Therefore, the line in a VLSI circuits can be modeled as a transmission line which is composed of interconnect series resistance, series inductance, shunt capacitance and shunt conductance, R, L, C and G respectively, as illustrated in Figure 2.11. The resistance R comes from the self resistance of the interconnect itself (the resistance of the materials used for interconnect); the inductance L represents the interconnect self inductance; the capacitance C is mainly due to the capacitance formed between the interconnect and the substrate layers; and the conductance G represents the conductivity of the dielectric layers located between the interconnect and the substrate layer. Interconnect parasitic impedances push the line to deviate from the ideal characteristic impedance.

In VLSI chips, interconnects can be modeled as micro-strips or as parallel-plate transmission lines [58- 60]. The best signal transmission from one point to another on the transmission line can be reached if the losses across the transmission are low, if the attenuation and velocity of the waves across the transmission line are frequency independent and if the characteristic impedance of the transmission line and the source and load impedances are matched to prevent reflections [61- 63].

Figure 2.11: A section of an RLCG Π- configuration of transmission line.

Based on the interconnect loss, interconnects in VLSI circuits can be classified as: Lossless and Lossy transmission lines.

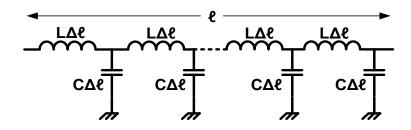

#### 2.3.1.1 Lossless Transmission Lines

When the loss, which acts on the propagated signal on an interconnect in VLSI circuits due to the line elements (interconnect resistance and conductance) is ignored, the interconnect can be modeled as an LC model called a lossless transmission line model. To get a more accurate representation model, the interconnect is sampled into small pieces. Each piece represents small LC lumped circuit elements. These elements are distributed uniformly down the length of the line as shown in Figure 2.12.

Figure 2.12: Equivalent circuit model of a lossless transmission line.

A lossless transmission line behaves as a short circuit at low frequencies because line inductance L can be represented as a short circuit whereas the line capacitance C can be represented as an open circuit. Therefore, a short circuit lossless transmission line at low frequencies represents an ideal medium for signal propagation. However, at high frequencies, the behaviour of a lossless transmission line is totally different than the short circuit representation. Delay of the propagation signal along the wire as well as the reflection is the most important two things that should be considered compared with the short circuit representation. In [64], lossless transmission line velocity, characteristic impedance and delay are calculated as illustrated in equations (2.1-2.3),

$$v = \frac{1}{\sqrt{lc}}$$

(2.1)

$$Z_0 = \sqrt{\frac{l}{c}}$$

(2.2)

$$t_{pd} = \frac{\ell}{\nu} \tag{2.3}$$

where v is the velocity of the signal on the line,  $Z_0$  is the line characteristic impedance and  $t_{pd}$  is the signal propagation delay.

#### 2.3.1.2 Lossy Transmission Lines

When the loss is significant, the effects of the series resistance R and the dielectric conductance G should be included in the transmission line models. Figure 2.13 shows the equivalent circuit model of a lossy transmission line with distributed lumps of RLCG elements,

Figure 2.13: Equivalent RLCG circuit model of a lossy transmission line.

To describe Eq. (2.4), the characteristics of the wave propagation along the line ( $\gamma$ ) is a complex number. The real part represents the signal attenuation ( $\alpha$ ) due to the line resistance and dielectric conductance. The imaginary part ( $\beta$ ) represents the phase constant, which determines the speed of the propagation signal across the line. Thus  $\gamma$  can be expressed as

$$\gamma = \alpha + j\beta \tag{2.4}$$

For an RLCG lossy transmission line, the attenuation ( $\alpha$ ) can be described as in [64],

$$\alpha = \frac{r}{2Z_o} + \frac{gZ_o}{2} \tag{2.5}$$

Clearly, we can see from Eq. (2.5) that the attenuation of the lossy RLCG transmission line is directly proportional to line resistance and conductance. Also, if we neglect the effects of the line resistance and conductance, the attenuation will be zero and the line will be a lossless transmission line. The speed of the wave propagation along the transmission line for RLC and RLCG transmission lines as represented in [64] is

$$v = \frac{\omega}{\beta} \tag{2.6}$$

where  $\omega$  and  $\beta$  are the system frequency and the phase constant respectively.

From Eq. (2.6), we see that the speed of the signal across the transmission line will be frequency dependent.

#### **2.4 Interconnects in VLSI Circuits**

On-chip interconnect can be represented as series resistance R due to the line resistance and inductance L due to the interconnect inductance and shunt capacitance C due to the capacitance formed between the interconnect layer and the substrate and conductance G due to the conductivity of the dielectric layer. When a signal propagates through an interconnect, it takes a non-negligible amount of time, which is called interconnect delay or propagation delay, to travel from one end to the other. A large portion of this time is due to the time it takes to charge and discharge the capacitance of the wire and gate capacitance of the transistors through the interconnect resistance.

#### 2.4.1 RC- Delay Models

For an RC circuit, delay can be characterized by the time constant RC. For on-chip interconnects, the delay of the signal mainly occurs due to the interconnect resistance R and the interconnect capacitance C. Interconnect resistance and capacitance are in direct proportion to the interconnect length. Based on the Elmore delay method [65], the delay of the *RC* line is in quadratic proportion to the interconnect length ( $t_{pd} = RC \Rightarrow r.c.l^2$ ) as shown in Figure 2.14.

Figure 2.14: The relationship between the interconnect delay and interconnect length.

Figure 2.14 represents the changing of the interconnect delay with its length and a specific width. Clearly, we see that the interconnect delay increases nonlinearly with increasing the interconnect length. In addition, increasing interconnect length causes the delay to increase rapidly at a specific interconnect length (called critical length).

#### 2.4.2 Elmore Delay Models

Elmore delay model [65] is widely used delay model in interconnect optimization. It is also the delay model used in this thesis. Despite its simplicity, Elmore delay model provides fairly good accuracy when compared with CAD tools such as H-spice. With an acceptable accuracy, on-chip interconnects and buffers can be replaced by an RC components. Therefore, interconnects and buffers become an RC circuit. At any point on the interconnect, the upstream resistance is equalled to the sum of the resistances from a driver (or a buffer before the point) to that point. The downstream capacitance is equalled to all capacitances from that point to a sink (or a buffer after the point). The Elmore delay model is basically a resistance-capacitance product. The Elmore delay along a signal path in the RC circuit is the sum of the delays associated with resistors in the path, where the delay is associated with a resistor is equalled to its resistance times its downstream capacitances as shown in Figure 2.15.

Figure 2.15: Distributed RC-model of interconnect.

Figure 216: Delay calculation at vdd/2.

$$t_{pd} = C_N \frac{(R_1 + R_2 + \dots + R_N)}{N} + \dots + C_2 \frac{(R_1 + R_2)}{N - 1} + C_1 R_1$$

(2.7)

For the uniform interconnect, line resistance and capacitance change with the length of the interconnect (interconnect thickness and width are constant). Then,

$$R_i = R\Delta\ell$$

and  $C_i = C\Delta\ell$  (2.8)

Eq. (2.7) can be expressed as

$$t_{p.d} = R(\Delta \ell) \frac{[C(\Delta \ell) + C(\Delta \ell) + \dots + C(\Delta \ell)]}{N}$$

(2.9)

$$t_{p.d} = R(\Delta \ell) \frac{[C(\Delta \ell) + C(\Delta \ell) + \dots + C(\Delta \ell)]}{N+1} + \dots + R(\Delta \ell)C(\Delta \ell)$$

(2.10)

$$t_{p.d} = RC(\Delta \ell)^2 (1 + 2 + ... + N)$$

(2.11)

$$t_{p.d} = RC(\Delta \ell)^2 \frac{N(N+1)}{2}$$

(2.12)

where  $\Delta \ell = \frac{\ell}{N}$ , ( $\ell$  represents the interconnect length, N represents the network sections), we have

$$t_{pd} = \frac{1}{2} RC\ell^2 \tag{2.13}$$

Eq. 2.13 shows that the delay of the distributed RC modeled interconnect is in the quadratic proportion to the length of the interconnect.

There are many advantages and disadvantages for using the Elmore delay method. The advantages are simple closed-form expression, usefulness for interconnect optimization and good solutions compared with the H-spice delay model. However, the disadvantages are poor for slope computation and inability to handle inductance effects because it represents the first moment of the impulse response.

#### 2.4.3 High Order Delay Models

For long interconnects where the effect of the parasitic inductance is crucial to achieve accurate modeling, many models that account for the inductance effect have been proposed [66- 69]. Zhou et al. [66] presented an analytical approach of a two-pole circuit approximation to provide a closed form solution. Kahng and Muddu [67] obtained an analytical delay model, based on first and second moments of RLC interconnection lines, that considers the effect of line inductance.

Subsequently, Tutuian et al. [68] found a stable time domain expression of the transfer function by matching the residues of the first two dominant poles with the first two moments of the transfer function. For more accurate methods, Pillage [69] proposed the asymptotic wave evaluation (AWE) method which matches the first moments of the transfer function. Later, more stable methods namely, pade via Lanczos (PVL) [70], matrix pade via Lanczos (MPVL) [71], Arnoldi algorithm

[72], block Arnoldi algorithm [73], and passive reduced order interconnect macromodeling algorithm (PRIMA) [74]. Moreover, G. Chen and Eby G. Friedman [75] have used Fourier analysis of an RLC interconnect modeling to find the transfer function, then they found the closed-form expression for the delay. These models are very accurate but need complex numerical computations.

## 2.5 Methodologies Used for Interconnect Modeling

In this section, we will discuss three well-known methods of characterizing on-chip interconnects: The GAM [76], TPN [77] and AWE [69] methods. The works in [78-80] have considered these three methods to find improvement models. In [78], Xu and Mazumder presented an RC macro-modeling of  $\Pi$  configuration using GAM and AWE methods. The work in [79] continued by presenting the RC T configuration using GAM method and also presented an RLC model for both T and  $\Pi$  configurations. Subsequently, Sun, et al., [80] obtained an RLC macro-modeling using TPN and AWE methods. The GAM, TPN and AWE methods will be explained briefly in the following sections.

## 2.5.1 Global Approximation Method (GAM)

The GAM is a method used to provide a mathematical approximation of a physical model. Depending on the range of its applicability, the mathematical approximation of a physical model can be classified as Local Approximation Method (LAM) (valid in the vicinity of a design point) or Global Approximation Method (GAM) (valid in the whole design space). LAM are usually based on Taylor series expansion at the current point using a function value and its first derivative, whereas GAM are normally based on the information taken in a series of points in the feasible design space.

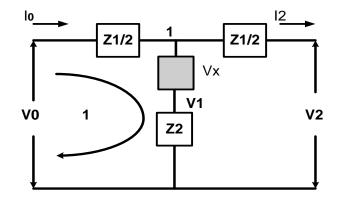

The construction of a GAM relies on the sampling of the design space at  $X_n$  locations to obtain response values for the objective function. To apply this method to interconnect modeling, let us consider an interconnect of length  $\ell$  [79] as shown in Figure 2.17, where  $X_n$  represents the selected grid points on the interconnect and  $V_i$  represents the voltages at selected grid points.

Figure 2.17: Interconnect with the assumption of the three grid points [79].

Along the line, three grid points have been selected:

$$x_{0} = 0$$

,  $x_{1} = \frac{1}{2}$  and  $x_{2} = 1$  (2.14)

Voltages and currents at these points can be expressed in Laplace domain as follows:

$$V_0 = V(x_0, s)$$

,  $V_1 = V(x_1, s)$ ,  $V_2 = V(x_2, s)$  (2.15)

$$I_0 = I(x_0, s)$$

,  $I_1 = I(x_1, s)$ ,  $I_2 = I(x_2, s)$  (2.16)

To find the approximation frame for this interconnect, based on the GAM, the current differences for each two points equals the sum of the derivative currents for all branches between these two points [76].

$$I(x_2, s) - I(x_0, s) = a_1 I'(x_0, s) + a_2 I'(x_1, s) + a_3 I'(x_2, s)$$

(2.17)

The voltage difference between two points equals the sum of the derivative voltages of the outer points.

$$V(x_1, s) - V(x_0, s) = b_1 V'(x_0, s) + b_2 V'(x_2, s)$$

(2.18)

$$V(x_2, s) - V(x_1, s) = b_3 V'(x_0, s) + b_4 V'(x_2, s)$$

(2.19)

The approximation frame has coefficients  $a_1, a_2, a_3, b_1, b_2, b_3$  and  $b_4$  and (') denotes the derivative with respect to x ( $x \in [0,1]$ ) where x is the normalized interconnect length. The value of these coefficients can be found by using the generalized Galerkin's method [76]. The generalized Galerkin's method assumes that interconnect currents and voltages change with interconnect length. So, to find the current response at each point, the fitting function method is used to express the current based on the location (x). The power of (x) increases with the number of derivative of the current assumed in the frame as shown below:

$$I(x,s) = x$$

as a fitting function (2.20)

Using this assumption to find the coefficients  $a_1, a_2$  and  $a_3$  used in Eq. (2.17), we get

$$At I(x,s) = x (2.21)$$

$$x_{2} - x_{0} = a_{1}x'|_{x=x_{0}} + a_{2}x'|_{x=x_{1}} + a_{3}x'|_{x=x_{2}}$$

(2.22)

$$1 - 0 = a_1 + a_2 + a_3 \Longrightarrow a_1 = 1 - a_2 - a_3 \tag{2.23}$$

$$I(x,s) = x^2 \tag{2.24}$$

$$x_{2}^{2} - x_{0}^{2} = a_{1} (x^{2})' \Big|_{x=x_{0}} + a_{2} (x^{2})' \Big|_{x=x_{1}} + a_{3} (x^{2})' \Big| x = x_{2}$$

(2.25)

$$1 = a_2 + 2a_3 \Longrightarrow a_2 = 1 - 2a_3 \tag{2.26}$$

$$I(x,s) = x^3 \tag{2.27}$$

$$x_{2}^{3} - x_{0}^{3} = a_{1}(x^{3})'\Big|_{x=x_{0}} + a_{2}(x^{3})'\Big|_{x=x_{1}} + a_{3}(x^{3})'\Big|x = x_{2}$$

(2.28)

$$1 = \frac{3a_2}{4} + 3a_3 \Longrightarrow a_3 = \frac{4 - 3a_2}{12}$$

(2.29)

From Eqs. (2.23, 2.26 and 2.29), we get

$$a_1 = \frac{1}{6}, a_2 = \frac{2}{3} \text{ and } a_3 = \frac{1}{6}$$

(2.30)

In the same way, to find the voltage response at each point, the fitting function method is used to express the voltage based on the location (X). Again, the power of (X) increases with the number of derivative of the voltages assumed in the frame as shown below:

Substituting V'(x,s) = x and  $x^2$  as the fitting functions used in Eq. (2.18), yield

$$b_1 = \frac{3}{8}$$

and  $b_2 = \frac{1}{8}$  (2.31)

Also,  $b_3 = \frac{1}{8}$  and  $b_4 = \frac{3}{8}$  can be obtained in the same way from Eq. (2.19).

The approximation frame for interconnect current and voltage differences after applying the GAM and using the generalized Galerkin's method is

$$I(x_2, s) - I(x_0, s) = \frac{1}{6}I'(x_0, s) + \frac{2}{3}I'(x_1, s) + \frac{1}{6}I'(x_2, s)$$

(2.32)

$$V(x_1, s) - V(x_0, s) = \frac{3}{8}V'(x_0, s) + \frac{1}{8}V'(x_2, s)$$

(2.33)

$$V(x_2, s) - V(x_1, s) = \frac{1}{8}V'(x_0, s) + \frac{3}{8}V'(x_2, s)$$

(2.34)

## 2.5.2 Two-Port Network (TPN)

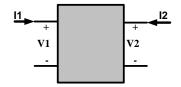

TPN has two ports, each port is characterized by voltage and current variables as shown in Figure 2.18.

Figure 2.18: Shows the variables for a two-port network.

The subscript 1 is used to refer to the variables at the input port (at the left) and the subscript 2 to refer to the variables at the output port (at the right). At both of these ports the variables are defined so that their relative reference directions obey the usual convention (input and output current for each port should be equal). Since we now have four variables, it requires two equations to relate these variables. The general form of these equations is expressed as

$$U_1(s) = K_{11}(s)W_1(s) + K_{12}(s)W_2(s)$$

(2.35)

$$U_2(s) = K_{21}(s)W_1(s) + K_{22}(s)W_2(s)$$

(2.36)

where the quantities  $U_1(s), U_2(s), W_1(s)$  and  $W_2(s)$  maybe any of the voltage and current variables  $V_1(s), V_2(s) I_1(s)$  or  $I_2(s)$ . Coefficients  $K_{ij}(s)$  are the network functions that relate these variables. Sometimes  $K_{ij}(s)$  are called *network parameters*. There are six different possible combinations that can be used to represent  $U_1(s)$  and  $U_2(s)$  in Eqs. (2.35-2.36). A tabulation of these six possible combinations is given in Table 2.1.

| case | $U_1(s)$ | $U_2(s)$ | $W_1(s)$ | $W_2(s)$    |

|------|----------|----------|----------|-------------|

| 1    | $V_1(s)$ | $V_2(s)$ | $I_1(s)$ | $I_2(s)$    |

| 2    | $I_1(s)$ | $I_2(s)$ | $V_1(s)$ | $V_2(s)$    |

| 3    | $I_1(s)$ | $V_2(s)$ | $V_1(s)$ | $I_2(s)$    |

| 4    | $V_1(s)$ | $I_2(s)$ | $I_1(s)$ | $V_2(s)$    |

| 5    | $V_1(s)$ | $I_1(s)$ | $V_2(s)$ | $-I_{2}(s)$ |

| 6    | $V_2(s)$ | $I_2(s)$ | $V_1(s)$ | $-I_1(s)$   |

Table 2.1: Six sets of network parameters for two-port network method.

Here we may note that any one of these six sets of parameters (if it exists) has the property completely characterizes the network. Also, any set can be utilized to find other sets of parameters [77].

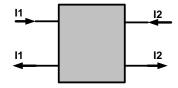

The general TPN configuration shown in Figure 2.19 has four individual terminals. It is theoretically possible to define four current variables rather than the two shown in the Figure 2.18. The requirement of a network port is that the current into one of the port terminals, at every instant of time, equals the current out of the other terminal of the port. This is called the port current requirement and it is illustrated in Figure 2.19. Most of the situations to which TPNs are applied automatically satisfy this requirement. If a port is open-circuited (i.e. if nothing is connected to it), the currents at the two terminals defining the port are zero. Thus the requirement is satisfied. When the case where any two-terminal elements (including a short circuit) are connected to the port, the currents into and out of the two-terminal element must be equal, the port current requirement is always satisfied in this case. The requirement is also satisfied for the case where a group of twoport networks is connected in cascade as shown in Figure 2.20. Consider the first network (on the left) in the cascade. The restriction on the currents is satisfied at the input port of this network by the open circuit. KCL now requires that the sum of the other two-terminal currents must be zero; thus the port current requirement is satisfied. Since the requirement at the output port of the first network is met, it must also be satisfied at the input port of the second network since the ports are directly connected.

Figure 2.19: Current requirements of the ports.

Figure 2.20: Cascade connections for two-port networks.

### 2.5.2.1 Z-Parameters in TPN Method

Table 2.1 shows that there are six ways in which the voltage and current variables of a TPN method may be selected so as to define a set of network functions. The first case in Table 2.1 will be considered to represent the z-parameter. We Choose  $V_1(s)$  and  $V_2(s)$  as the quantities  $U_1(s)$  and  $U_2(s)$  as shown in Eqs. (2.35) and (2.36) and  $I_1(s)$  and  $I_2(s)$  as the quantities and  $W_2(s)$ . Since the left members of the resulting set of equations have the dimensions of voltage, all the terms in the right members of these equations must also have the dimensions of voltage. Therefore, since the quantities  $W_1(s)$  and  $W_2(s)$  have the dimensions of current, this requires that coefficients  $K_{ij}(s)$ have the same dimensions of impedance. Equations (2.35) and (2.36) can be written in the form of

$$V_1(s) = Z_{11}(s)I_1(s) + Z_{12}(s)I_2(s)$$

(2.37)

$$V_2(s) = Z_{21}(s)I_1(s) + Z_{22}(s)I_2(s)$$

(2.38)

Quantities  $Z_{ij}(s)$  are called Z parameters. We can write equations (2.37) and (2.38) in the matrix form.

$$V(s) = \begin{bmatrix} V_1(s) \\ V_2(s) \end{bmatrix} = \begin{bmatrix} Z_{11}(s) & Z_{12}(s) \\ Z_{21}(s) & Z_{22}(s) \end{bmatrix} \begin{bmatrix} I_1(s) \\ I_2(s) \end{bmatrix} = Z(s)I(s)$$

(2.39)

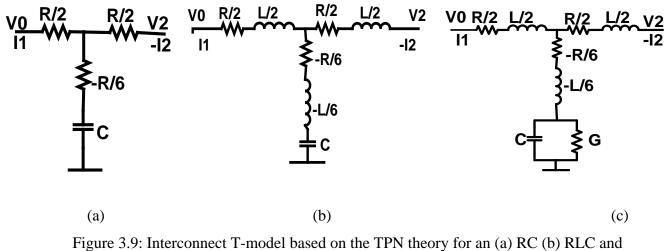

Eq. (2.39) represents the z-parameter matrix where for a given set of z-parameters (shown in Eq. (2.39)), there are some commonly used network forms which may be used as circuit configurations. One of the well known methods of these forms is the "T" network configuration as show in Figure 2.21. When  $Z_{12}(s)$  is equal to  $Z_{21}(s)$ , the network is reciprocal. Let us consider the T configuration of two-terminal impedances shown in Figure 2.21. The z-parameter matrix for this network is readily shown to be

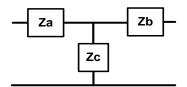

Figure 2.21: T-Configuration.

$$\begin{pmatrix} Z_{11}(s) & Z_{12}(s) \\ Z_{21}(s) & Z_{22}(s) \end{pmatrix} = \begin{pmatrix} Z_a(s) + Z_c(s) & Z_c(s) \\ Z_b(s) & Z_b(s) + Z_c(s) \end{pmatrix}$$

(2.40)

From the matrix above, the relations of the network elements  $Z_a, Z_b$  and  $Z_c$  as functions of the network parameters can be found from [77].

$$Z_a = Z_{11}(s) - Z_{12}(s) \tag{2.41}$$

$$Z_b = Z_{22}(s) - Z_{12}(s) \tag{2.42}$$

$$Z_c = Z_{12}(s) \tag{2.43}$$

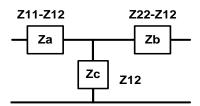

Thus, the T-network may be redrawn with the expressions specifying the two-terminal impedances given directly in terms of z-parameters as shown in Figure 2.22.

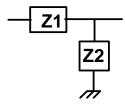

Figure 2.22: The equivalent z-parameter of T-model.

### 2.5.3 Asymptotic Waveform Evaluation (AWE) Method

The AWE was introduced in [69] as an efficient technique for the solution of linear circuits. It is a general method that applies to circuits consisting of all types of lumped, linear elements connected in any valid topology. The AWE method employs an efficient algorithm to compute the time moments of circuit responses. These moments are then matched via Pade approximation [70], a simple recursive formula method [106], or Maclaurin series projection [83] to reduced-order rational function models. The reduced-order models can be used to characterize the circuit's time and frequency.

In AWE, a Taylor series expression could be used to express the circuit response in a polynomial form. Then a simple recursive formula in [106] and the approaches in [83] are used to find the polynomial coefficients as illustrated below.

$$Y_{in}(s) = \frac{a_0 + a_1 s + \dots + a_{2n-1} s^{2n-1}}{1 + b_1 s + \dots + b_{2n-1} s^{2n}}$$

(2.44)

Eq. (2.44) can be expressed using a polynomial of order 2n-1, as in the Taylor series

$$Y_{in}(s) = Y_0 + Y_1 s + \dots + Y_{2n-1} s^{2n-1}$$

(2.45)

The coefficients  $Y_k$  of Eq. (2.45) can be found by a simple recursive formula [106],

$$Y_{k} = a_{k} - \sum_{i=1}^{k} b_{i} Y_{k-i}$$

(2.46)

where  $Y_{in}(s)$  is the input admittance of a circuit in s-domain,  $Y_k$  are the coefficients of the input admittance,  $a_k$  are the coefficients of the numerator of the input admittance equation, n is the number of the circuit sections, and  $b_i$  are the coefficients of the denominator of the input admittance.

## 2.6 Summary

In this chapter, the history of the interconnect modeling were briefly reviewed. The amendments of the interconnect modeling based on the interconnect effects in the circuits toward the accuracy are briefly addressed. Lumped and distributed interconnect models, namely C, RC, RLC, and RLCG, were addressed. A transmission line of lossy and lossless models was mentioned for RC and LC configurations respectively. Delay models based on interconnect RC configuration, Elmore method and high order delay methods were discussed. The GAM, TPN, and AWE methods were briefly reviewed. In each method, the derivation of an interconnect model is considered. These methods are fully considered in the next chapter.

# **CHAPTER 3**

# Generalizing the GAM, TPN and AWE Methods Using Z-Parameters

#### **3.1 Introduction**

With the use of nano-meter technology, integrated circuits (ICs) have become more dense and more complex. Subsequently, interconnect delay has become the dominant factor in nano-meter design. The effects of interconnects on chip performance such as delay, crosstalk, and reflection are becoming critical factors in VLSI design [81].

In recent years also, various improvement methods have been proposed on the interconnect models [78-80]; an improved RC T-configuration based on the GAM and RC  $\Pi$ - configuration based on the AWE have been proposed in [78]. These models are not robust because they don't consider the effect of the interconnect inductance. In [79], improved RC and RLC models for both T and  $\Pi$  configurations based on the GAM have been proposed. Furthermore, improved RLC models for both T and  $\Pi$  configurations based on the TPN and AWE methods have been presented in [80]. Although these models exhibit good accuracy compared with H-spice, unfortunately, the complexity of using these methods prevents including the effect of the dielectric loss in their models. Therefore, generalizing these methods to find all the RC, RLC and RLCG models are crucial.

In this chapter, we generalized these methods into z-parameter models. We started to derive the Telegraph equations for the currents and voltages of a transmission line in z-parameter representation. A z-parameter of interconnect modeling for both T and  $\Pi$  configurations based on the GAM, TPN, and AWE is proposed. Eighteen different RC, RLC and RLCG models are easily generated from using the derived models.

## **3.2** Z-Parameter Representation for the Telegraph Equations

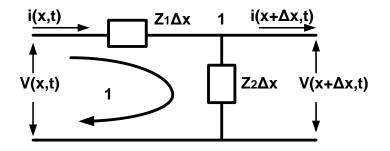

To derive the telegraph equation for the currents and voltages of a transmission line, we consider the general form using the z-parameter model where there are resistance, capacitance, inductance and/or conductance. Moreover, the distributed z-parameter model will be considered as shown in Figure 3.1.

In this section, telegraph equations for voltage and current differences of the interconnect-zparameter model in s-domain have been derived.

Figure 3.1: Distributed z-parameter model of a transmission line.

By applying KVL for loop1 of Figure 3.1, we get

$$v(x,t) = i(x,t)Z_1\Delta x + v(x + \Delta x,t)$$

(3.1)

$$v(x + \Delta x, t) - v(x, t) = -i(x, t)Z_1 \Delta x$$

(3.2)

$$\frac{d (x,t)}{dx} = \frac{\Delta v(x,t)}{\Delta x} \bigg|_{\Delta x \to 0} = -i(x,t)Z_1$$

(3.3)

Expressing Eq. (3.3) in s-domain, gives

$$\frac{dV(x,s)}{dx} = -I(x,s)Z_1 \tag{3.4}$$

$$V'(x,s) = -Z_1 I(x,s)$$

(3.5)

By applying KCL at node1, results in

$$i(x,t) = i(x + \Delta x, t) + v(x + \Delta x, t) / Z_2 \Delta x$$

(3.6)

$$i(x + \Delta x, t) - i(x, t) = -\nu(x + \Delta x, t) / Z_2 \Delta x$$

(3.7)

$$\frac{\Delta i(x,t)}{\Delta x} = -v(x,t)/Z_2 \tag{3.8}$$

$$\frac{d(x,t)}{dx} = \frac{\Delta i(x,t)}{\Delta x} \bigg|_{\Delta x \to 0} = -v(x,t)/Z_2$$

(3.9)

Expressing Eq. (3.9) in s-domain, yields

$$\frac{dI(x,s)}{dx} = -V(x,s)/Z_2 \tag{3.10}$$

$$I'(x,s) = -V(x,s)/Z_2$$

(3.11)

Eqs. (3.5, 3.11) represent the Telegraph equations for voltages and currents difference of the zparameter-transmission line in s-domain. From these equations, it is easy to get the telegraph equations of current and voltage difference for transmission line RC, RLC, or RLCG models as shown below:

For the RC distributed model, if we substitute  $Z_1 = R$  and  $Z_2 = \frac{1}{sC}$  in Eqs. (3.5, 3.11), we have

$$V'(x,s) = -RI(x,s) \tag{3.12}$$

$$I'(x,s) = -sCV(x,s) \tag{3.13}$$

For the RLC distributed model, substituting  $Z_1 = R + sL$  and  $Z_2 = \frac{1}{sC}$  in Eqs. (3.5, 3.11), we

have

$$V'(x,s) = -(R+sL)I(x,s)$$

(3.14)

$$I'(x,s) = -sCV(x,s)$$

(3.15)

For the RLCG distributed model, substituting  $Z_1 = R + sL$  and  $Z_2 = \frac{1}{G + sC}$  in Eqs. (3.5, 3.11), we have

$$V'(x,s) = -(R+sL)I(x,s)$$

(3.16)

$$I'(x,s) = -(G+sC)V(x,s)$$

(3.17)

From all the results above, Eqs. (3.5, 3.11) represent the general z-parameter telegraph equations for transmission line currents and voltages. Therefore, Eqs. (3.5, 3.11) can be directly used to find

RC, RLC and/or RLCG telegraph equations by replacing  $Z_1$  and  $\frac{1}{Z_2}$  with their actual components,

where  $Z_1$  is the impedance between the two points at which the voltages change, and  $\frac{1}{Z_2}$  is the

shunt admittance where the currents change.

# **3.3 Z-Parameter Modeling For Interconnect Based on GAM, TPN and AWE Methods**

A general z-parameter interconnect modeling is a model which can be used to find an RC, RLC and/or RLCG interconnect model directly in both T and  $\Pi$  configurations. Three well known methods have been used for interconnect modeling: GAM, TPN and AWE. In this section, we will discuss all these three methods of analysing interconnects in z-parameter form and for each method, both T and  $\Pi$  configurations will be considered.

## 3.3.1 GAM Based Z-Parameter Modeling

z-parameter modeling using the GAM method is presented by deriving Telegraph equations for interconnect voltages and currents in z-parameters. The GAM method is taken for interconnect voltages and currents. Based on that, approximation frames for voltages and currents in z-parameters are obtained. The fitting function of the Galerkin's method is used to find the approximation frames coefficients. Some mathematical manipulations are applied on the frames. z-

parameter modeling for both T and  $\Pi$  configurations is derived. Z-parameter modeling based on the GAM method can be used easily to switch between the interconnect RC, RLC and RLCG modeling

## 3.3.1.1 Z-Parameters Derivation For T-Configuration

In this section, we will present the z-parameter model for an interconnect T-presentation based on the GAM. By considering Eqs. (3.5, 3.11), Eqs. (2.32-2.34), which are proposed in section 2.5.1, can be rewritten as:

$$I(x_2, s) - I(x_0, s) = -\frac{1}{6} \frac{V(x_0, s)}{Z_2} - \frac{2}{3} \frac{V(x_1, s)}{Z_2} - \frac{1}{6} \frac{V(x_2, s)}{Z_2}$$

(3.18)

$$V(x_1, s) - V(x_0, s) = -\frac{3}{8}I(x_0, s)Z_1 - \frac{1}{8}I(x_2, s)Z_1$$

(3.19)

$$V(x_2, s) - V(x_1, s) = -\frac{1}{8}I(x_0, s)Z_1 - \frac{3}{8}I(x_2, s)Z_1$$

(3.20)

Also, by considering Eqs. (2.15, 2.16) in section 2.5.1, Eqs. (3.18-3.20) above can be rewritten as

$$I_0 - I_2 = \frac{1}{6} \frac{V_0}{Z_2} + \frac{2}{3} \frac{V_1}{Z_2} + \frac{1}{6} \frac{V_2}{Z_2}$$

(3.21)

$$V_0 - V_1 = \frac{3}{8} Z_1 I_0 + \frac{1}{8} Z_1 I_2$$

(3.22)

$$V_1 - V_2 = \frac{1}{8}Z_1I_0 + \frac{3}{8}Z_1I_2$$

(3.23)

Eq. (3.22) can be rewritten as

$$V_1 = V_0 - \frac{3}{8} Z_1 I_0 - \frac{1}{8} Z_1 I_2$$

(3.24)

Substituting Eq. (3.24) in equation (3.23), yields

$$V_2 = V_0 - \frac{3}{8} Z_1 I_0 - \frac{1}{8} Z_1 I_2 - \frac{1}{8} Z_1 I_0 - \frac{3}{8} Z_1 I_2$$

(3.25)

$$V_2 = V_0 - \frac{1}{2} Z_1 I_0 - \frac{1}{2} Z_1 I_2$$

(3.26)

$$V_0 - V_2 = \frac{1}{2}Z_1I_0 + \frac{1}{2}Z_1I_2$$

(3.27)

Depending on Eq.(3.27), the circuit can be constructed as shown in Figure 3.2.

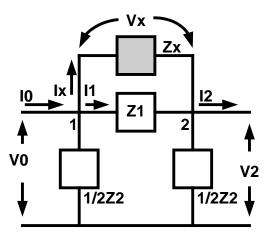

Figure 3.2: The circuit after manipulations of the voltage equations.

By applying KVL for loop 1 of Figure 3.2, we can write

$$V_0 = \frac{1}{2} Z_1 I_0 + V_1 + V_x \tag{3.28}$$

$$V_0 - V_1 = \frac{1}{2} Z_1 I_0 + V_x \tag{3.29}$$

Substituting Eq. (3.29) in Eq. (3.22), yields

$$\frac{1}{2}Z_1I_0 + V_x = \frac{3}{8}Z_1I_0 + \frac{1}{8}Z_1I_2$$

(3.30)

$$V_x = \frac{3}{8}Z_1I_0 - \frac{1}{2}Z_1I_0 + \frac{1}{8}Z_1I_2$$

(3.31)

$$V_x = -\frac{1}{8}Z_1(I_0 - I_2) \tag{3.32}$$

So, from Eqs. (3.27, 3.32), the circuit can be presented as shown in Figure 3.3.

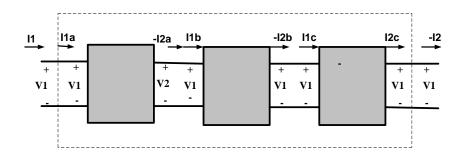

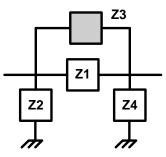

Figure 3.3: The z-parameter of T-configuration after the voltage and current equations are manipulated.

It can be seen that Eqs. (3.29, 3.32) represent the general form of the interconnect z-parameter for T-configuration based on the GAM. Figure 3.4 represents the interconnect T-configuration for RC, RLC and RLCG circuits based on the GAM as obtained from Eqs. (3.27, 3.32).

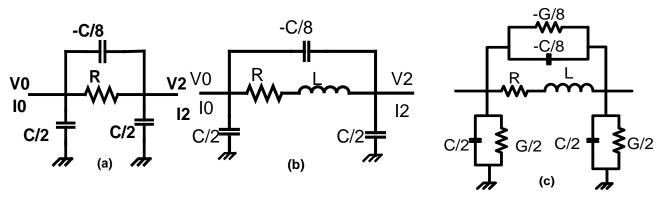

Figure 3.4: Interconnect T-configuration based on the GAM for (a) RC, (b) RLC and (c) RLCG interconnects.

In this section, we derived the z-parameter model of interconnects in T-configuration based on the GAM. In this model, the voltage differences of the line are expressed in Eq. (3.27) and the current differences are expressed in Eq. (3.32). Figures 3.4 (a, b and c) represent the result of the general z-parameter model in T-configuration based on the GAM for RC, RLC and RLCG models. Qinwei and Pinaki in [78] derived only the RC T-configuration based on GAM. They did not mention RLC and the RLCG models. Later on, the work in [79] mentioned both T and II configurations for RC and RLC models based on the GAM but omitted RLCG models. Clearly, the revision of the z-parameter model revealed better results than the works in [78,79] because using the z-parameter model, we can easily find the T-configuration of the RC, RLC or RLCG interconnect models not only the RC or RLC model.

## **3.3.1.2** Z-Parameters Derivation for II-Configuration

In this section, we derive the z-parameter model for on-chip interconnect for  $\Pi$ -configuration based on the GAM. Eqs. (3.5) and Eq. (3.11) represent the relationship of duality [80]. i.e., if we replace V(x, s) with I(x, s) and  $Z_1$  with  $Z_2$ , then Eq. (3.5) and Eq. (3.11) become identical. This duality can also be applied to Eqs. (3.18-3.32) which results in another approximation frame.

$$V_0 - V_2 = \frac{1}{6}Z_1I_0 + \frac{2}{3}Z_1I_1 + \frac{1}{6}Z_1I_2$$

(3.33)

$$I_0 - I_1 = \frac{3}{8} \frac{V_0}{Z_2} + \frac{1}{8} \frac{V_2}{Z_2}$$

(3.34)

$$I_1 - I_2 = \frac{1}{8} \frac{V_0}{Z_2} + \frac{3}{8} \frac{V_2}{Z_2}$$

(3.35)

Eqs. (3.34) can be rewritten as

$$I_1 = I_0 - \frac{3}{8} \frac{V_0}{Z_2} - \frac{1}{8} \frac{V_2}{Z_2}$$

(3.36)

Substituting Eq. (3.36) in Eq. (3.35), we get

$$I_{2} = I_{0} - \frac{3}{8} \frac{V_{0}}{Z_{2}} - \frac{1}{8} \frac{V_{2}}{Z_{2}} - \frac{1}{8} \frac{V_{0}}{Z_{2}} - \frac{3}{8} \frac{V_{2}}{Z_{2}}$$

$$I_{0} - I_{2} = \frac{1}{2} \frac{V_{0}}{Z_{2}} + \frac{1}{2} \frac{V_{2}}{Z_{2}}$$

$$(3.37)$$

$$(3.38)$$

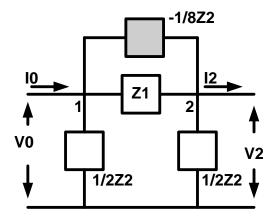

Based on Eq. (3.38), the circuit will be as shown in Figure 3.5.

Figure 3.5: The circuit after manipulations of the current equations.

By considering KCL at node 1, we get

$$I_0 - I_1 = \frac{1}{2} \frac{V_0}{Z_2} + I_x \tag{3.39}$$

Substituting Eq. (3.39) in Eq. (3.34), gives

$$\frac{1}{2}\frac{V_0}{Z_2} + I_x = \frac{3}{8}\frac{V_0}{Z_2} + \frac{1}{8}\frac{V_2}{Z_2}$$

(3.40)

$$I_x = \frac{3}{8} \frac{V_0}{Z_2} - \frac{1}{2} \frac{V_0}{Z_2} + \frac{1}{8} \frac{V_2}{Z_2}$$

(3.41)

$$I_x = -\frac{1}{8Z_2} (V_0 - V_2) \tag{3.42}$$

So, from Eqs. (3.38) and Eq. (3.42), the circuit can be constructed as shown in Figure 3.6.

Figure 3.6: The z-parameter of  $\Pi$ -model after the voltage and current equations are manipulated.