#### Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2003

# A low-voltage CMOS current-mode differential front-end for optical communications

Bendong Sun Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Sun, Bendong, "A low-voltage CMOS current-mode differential front-end for optical communications" (2003). *Theses and dissertations*. Paper 204.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

6- 65

# A Low-Voltage CMOS Current-Mode Differential Front-End for Optical Communications

by

#### Bendong Sun (B.Eng, Shanghai Jiaotong University, 1992)

A thesis

presented to Ryerson University in partial fulfillment of the requirement for the degree of Master of Applied Science in the Program of Electrical and Computer Engineering.

Toronto, Ontario, Canada, 2003

© Bendong Sun, 2003

UMI Number: EC52900

#### INFORMATION TO USERS

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleed-through, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

# UMI®

UMI Microform EC52900 Copyright 2008 by ProQuest LLC. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest LLC 789 E. Eisenhower Parkway PO Box 1346 Ann Arbor, MI 48106-1346

#### Instructions on Borrowers

Ryerson University requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

### "A Low-Voltage CMOS Current-Mode Differential Front-End for Optical Communications" Master of Applied Science, 2003 Bendong Sun Department of Electrical and Computer Engineering

Ryerson University

#### Abstract

This thesis deals with the design of a low-voltage fully-differential CMOS currentmode preamplifier for optical communications. An in-depth comparative analysis of the building blocks of low-voltage CMOS current-mode circuits is carried out. Two new bandwidth enhancement techniques, namely inductor series-peaking and current feedback, are introduced and implemented in the design. The feedback also reduces the value of the series-peaking inductor. The minimum supply voltage of the amplifier is only one threshold voltage plus one pinch-off voltage. The preamplifier has a balanced differential topology such that the effect of bias-dependent mismatches is minimized and the amplifier is insensitive to the switching noise caused by the digital circuitry. Negative differential current feedbacks are implemented to boost the bandwidth and increase the dynamic range. The design is based on 0.18  $\mu$ m CMOS technology. It has the bandwidth of 3.5 GHz and provides 66 dB differential transimpedance gain with standard 50  $\Omega$  loads.

#### Acknowledgments

I am deeply indebted to Professor Fei Yuan for his enthusiastic support, constant guidance and inspiration throughout the course of this research. His intuition, rigorism and patience have made the journey of my graduate study full of enjoyment.

My heartfelt gratitude goes to Professor Khoman Phang from the Department of Electrical and Computer Engineering, University of Toronto, Professor Xavier Fernando and Professor Gul N. Khan from the Department of Electrical and Computer Engineering, Ryerson University, for their participation in my defense.

I am grateful to the School of Graduate Studies and the Department of Electrical and Computer Engineering of Ryerson University for providing me with the graduate scholarships and the research stipends during my study.

Finally, my deepest thanks to my wife, Yi, for her love, patience, and understanding. This work could not have been completed without her support and encouragement.

v

## Contents

| 1 | Intr | roduction                                                 | 1  |

|---|------|-----------------------------------------------------------|----|

|   | 1.1  | Overview                                                  | 1  |

|   | 1.2  | Original Contributions                                    | 3  |

|   | 1.3  | Thesis Organization                                       | 4  |

| 2 | Bac  | kground                                                   | 7  |

|   | 2.1  | Generic Optical Communication Systems                     | 7  |

|   | 2.2  | Photodetectors                                            | 9  |

|   | 2.3  | Optical Preamplifiers                                     | 12 |

|   |      | 2.3.1 Preamplifier Performance Parameters                 | 12 |

|   |      | 2.3.2 Conventional Preamplifier Structures                | 14 |

|   |      | 2.3.3 Current-Mode Approach                               | 18 |

| 3 | Cor  | nparative Study of Low-Voltage CMOS Current-Mode Circuits | 22 |

|   | 3.1  | Input Impedance                                           | 22 |

|   | 3.2  | Bandwidth                                                 | 28 |

|   | 3.3  | Dynamic Range                                             | 31 |

|   | 3.4  | Noise                                                     | 32 |

|   | 3.5  | Summary                                                   | 33 |

| 4 | Nev  | v Bandwidth Enhancement Techniques for CMOS Current-Mode  | :  |

|   | Circ | cuits                                                     | 34 |

|   | 4.1   | Inductive Shunt-Peaking and Resistive Compensation          | 35 |

|---|-------|-------------------------------------------------------------|----|

|   | 4.2   | Inductor Series-Peaking                                     | 38 |

|   |       | 4.2.1 Current-Mirror Amplifiers                             | 38 |

|   |       | 4.2.2 Optical Preamplifiers                                 | 42 |

|   | 4.3   | Negative Current Feedback                                   | 44 |

|   | 4.4   | Inductor Series-Peaking with Current Feedback               | 47 |

|   | 4.5   | Summary                                                     | 50 |

| 5 | Top   | oologies and Strategies of Current-Mode Amplifiers          | 53 |

|   | 5.1   | Gain and Bandwidth                                          | 53 |

|   | 5.2   | Noise                                                       | 56 |

|   | 5.3   | Mismatches                                                  | 57 |

|   | 5.4   | Power Consumption and Output Impedance                      | 60 |

|   | 5.5   | Differential Configuration                                  | 61 |

|   | 5.6   | Differential Current Feedback                               | 63 |

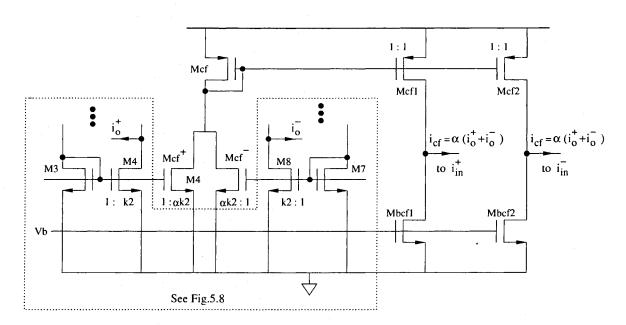

|   | 5.7   | Common-Mode Feedback                                        | 67 |

|   | 5.8   | Summary                                                     | 68 |

| 6 | Nev   | w Low-Voltage Differential CMOS Current-Mode Optical Pream- |    |

|   | plifi | ler                                                         | 69 |

|   | 6.1   | Circuit Schematic and Parameters                            | 69 |

|   | 6.2   | Circuit layout                                              | 75 |

|   |       | 6.2.1 Transistors                                           | 75 |

|   |       | 6.2.2 Inductors                                             | 75 |

|   |       | 6.2.3 Routings                                              | 77 |

|   |       | 6.2.4 Pads and Power supply                                 | 77 |

|   | 6.3   | Simulation Results                                          | 79 |

١

.

| 7 | Con | clusions                | 82 |

|---|-----|-------------------------|----|

|   | 7.1 | Summary and Conclusions | 82 |

|   | 7.2 | Future Work             | 83 |

|   | _   |                         | 85 |

A Brief SONET Specifications

viii

# List of Figures

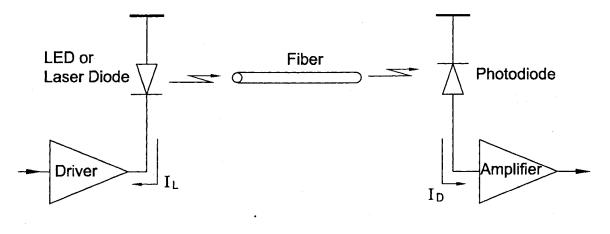

| 2.1 | Simple optical communication system                                      | 8  |

|-----|--------------------------------------------------------------------------|----|

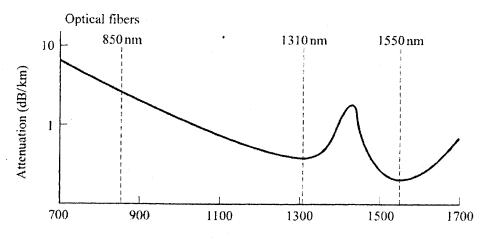

| 2.2 | Attenuation in optical fibers                                            | 9  |

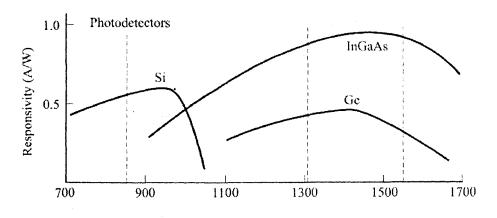

| 2.3 | Responsivity of photodetectors                                           | 10 |

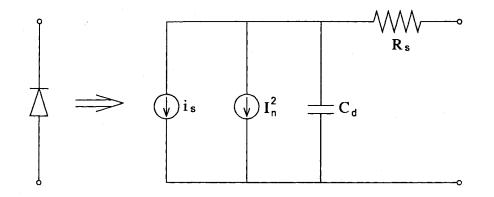

| 2.4 | Small signal equivalent circuit of PIN photodiodes                       | 11 |

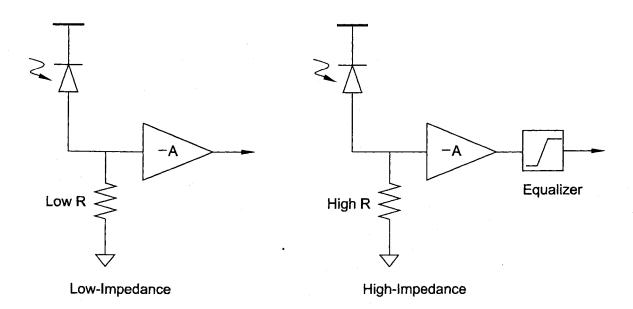

| 2.5 | Low impedance and high impedance amplifiers                              | 15 |

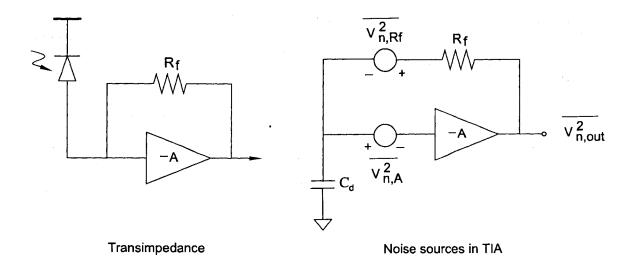

| 2.6 | Transimpedance amplifier and its noise sources                           | 16 |

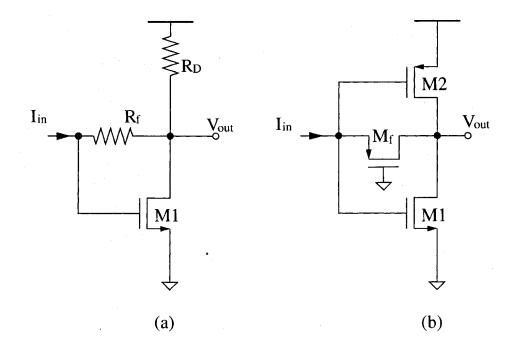

| 2.7 | CMOS transimpedance amplifiers                                           | 18 |

| 2.8 | Current-mode approach of optical fron-end                                | 19 |

| 3.1 | (a) Basic current mirror (BASIC); (b) Low input-impedance current mir-   |    |

|     | ror (LI-IMP)                                                             | 23 |

| 3.2 | Current mirrors with common-gate feedback (CGFB)                         | 23 |

| 3.3 | (a) Mirror with active feedback (ACTIVE). (b) Bootstrapped current       |    |

|     | mirror (BSTRP)                                                           | 24 |

| 3.4 | (a) Auxiliary differential-input single-output Opamp. (b) High bandwidth |    |

|     | current mirror (HBW)                                                     | 24 |

| 3.5 | (a) Current mirror with current feedback (CCFB). (b) Current mirror      |    |

|     | with resistor (RES)                                                      | 26 |

| 3.6 | Input impedance                                                          | 27 |

| 3.7 | Output current                                                           | 30 |

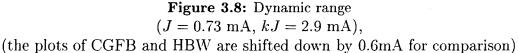

| 3.8 | Dynamic range                                                            | 31 |

| 4.1  | Inductive shunt-peaking technique                                                | 36 |  |  |  |

|------|----------------------------------------------------------------------------------|----|--|--|--|

| 4.2  | Resistive compensation technique                                                 | 37 |  |  |  |

| 4.3  | Current-mirror amplifier with series-peaking inductor                            |    |  |  |  |

| 4.4  | The effect of the peaking inductor on the bandwidth of current-mirror            |    |  |  |  |

|      | amplifier                                                                        | 41 |  |  |  |

| 4.5  | Optical preamplifier with series-peaking inductor                                | 42 |  |  |  |

| 4.6  | Current-mirror amplifier with current feedback                                   | 45 |  |  |  |

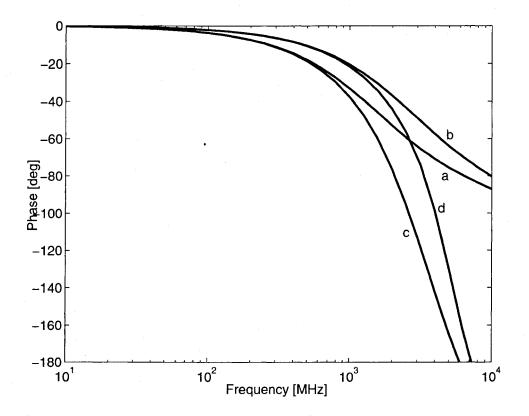

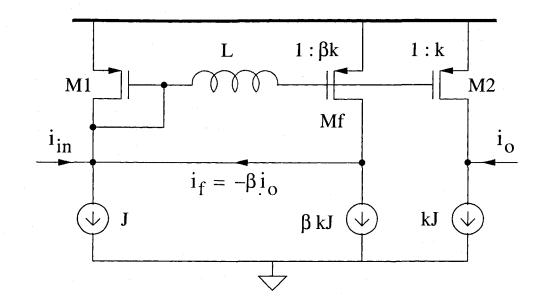

| 4.7  | Phase response of current-mirror amplifier                                       | 46 |  |  |  |

| 4.8  | Current-mirror amplifier with series-peaking and current feedback                | 47 |  |  |  |

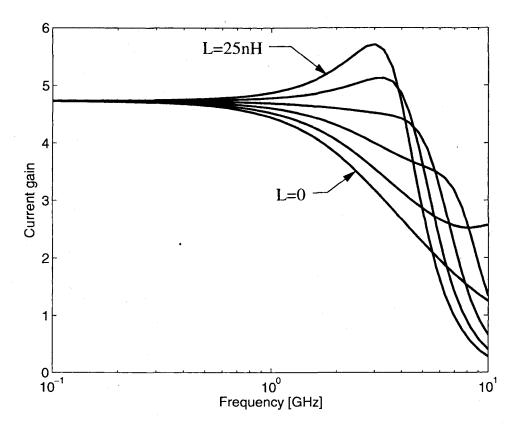

| 4.9  | The effect of peaking inductor on the bandwidth of current-mirror ampli-         |    |  |  |  |

|      | fier with current feedback                                                       | 48 |  |  |  |

| 4.10 | Optical preamplifier with series-peaking and current feedback                    | 50 |  |  |  |

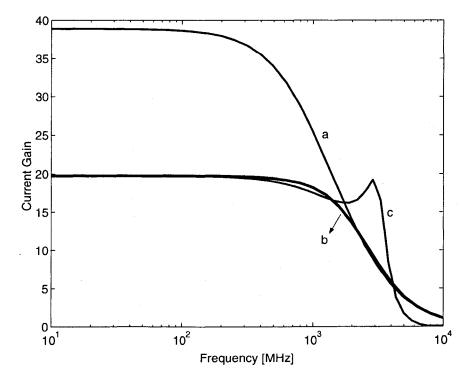

| 4.11 | Frequency response of current-mirror amplifier                                   | 51 |  |  |  |

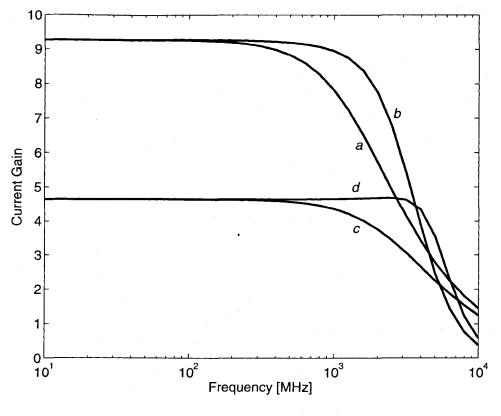

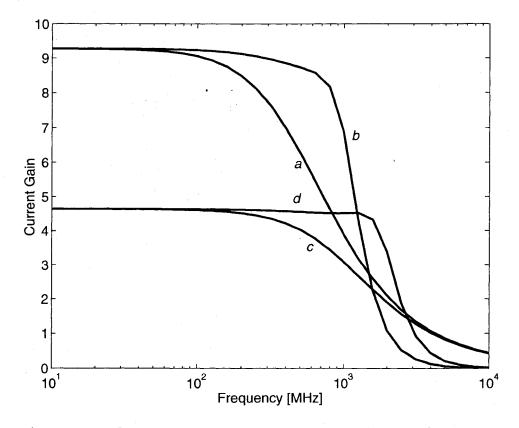

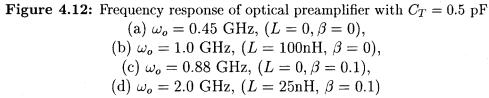

| 4.12 | Frequency response of optical preamplifier with $C_T = 0.5 \text{ pF} \dots$     | 52 |  |  |  |

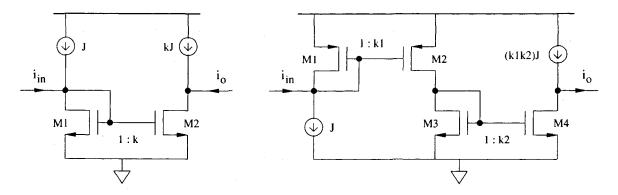

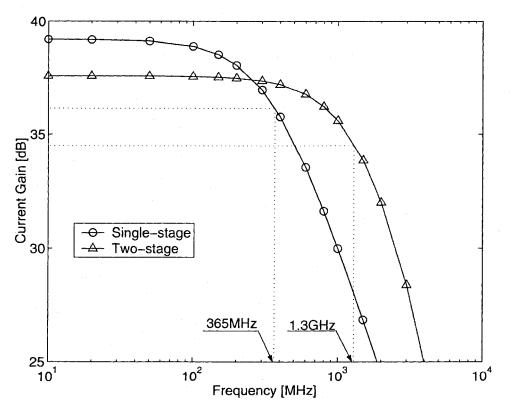

| 5.1  | Current amplifiers (a)Single-stage; (b)Two-stage                                 | 54 |  |  |  |

| 5.2  | Frequency response of single- and two-stage current amplifiers                   | 55 |  |  |  |

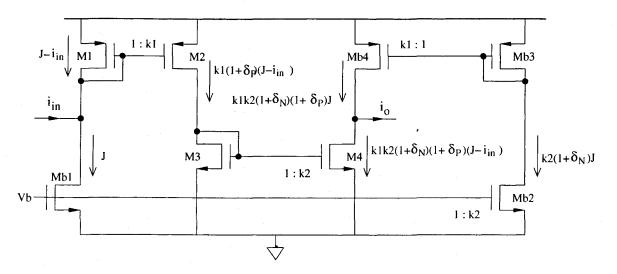

| 5.3  | Fully balanced two-stage current current amplifier                               | 59 |  |  |  |

| 5.4  | Two-stage current amplifier with current-branching                               | 60 |  |  |  |

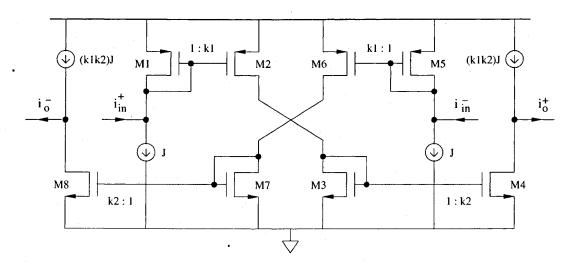

| 5.5  | Differential current amplifier                                                   | 62 |  |  |  |

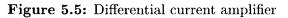

| 5.6  | Output current of non-differential and differential amplifiers with a noisy      |    |  |  |  |

|      | supply voltage                                                                   | 62 |  |  |  |

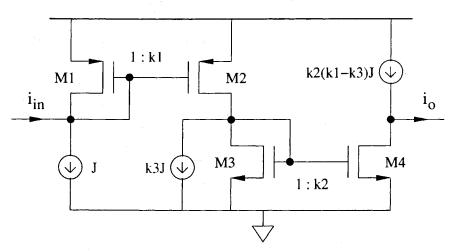

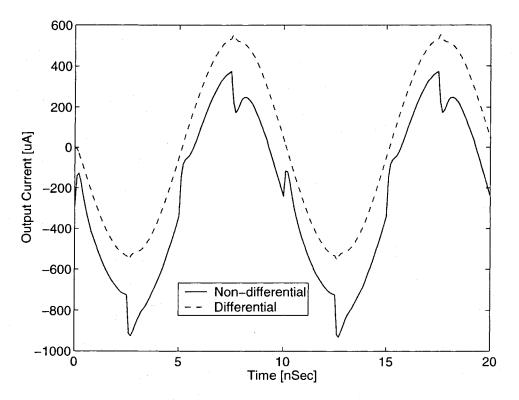

| 5.7  | Current amplifiers with current feedback (a)Single-stage; (b)Two-Stage $\ .$     | 63 |  |  |  |

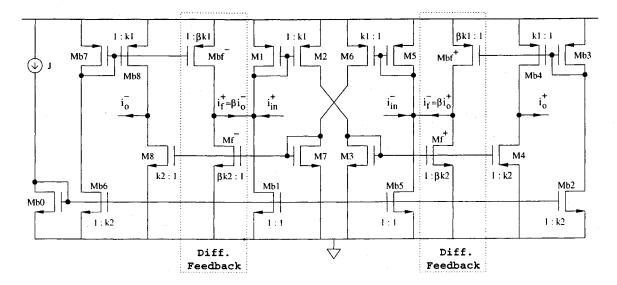

| 5.8  | Differential current amplifier with negative differential current feedback $\ .$ | 64 |  |  |  |

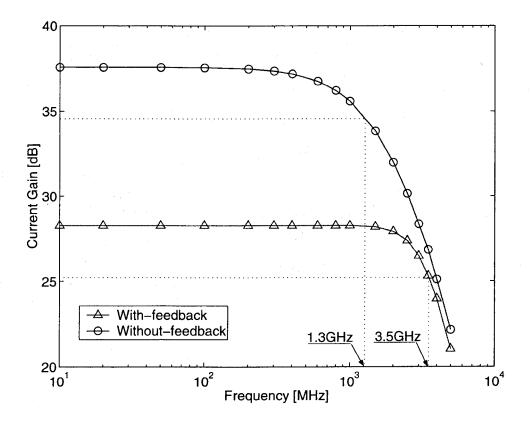

| 5.9  | Frequency response of differential current amplifier with and without feed-      |    |  |  |  |

|      | back                                                                             | 65 |  |  |  |

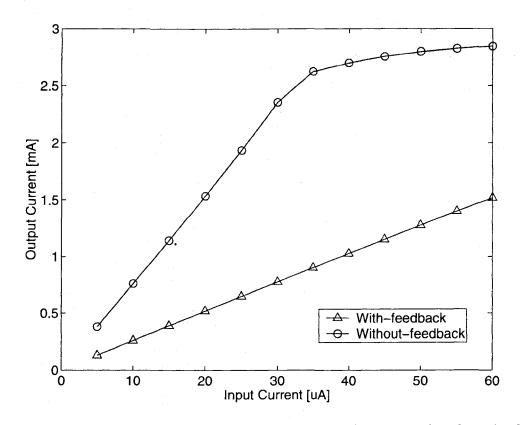

| 5.10 | Dynamic range of differential current amplifier with and without feedback        | 66 |  |  |  |

| 5.11 | Common-mode feedback                                                             | 67 |  |  |  |

| 6.1  | $ Differential \ optical \ front-end \ with \ differential \ transimpedance \ amplifier \ .$ | 70 |

|------|----------------------------------------------------------------------------------------------|----|

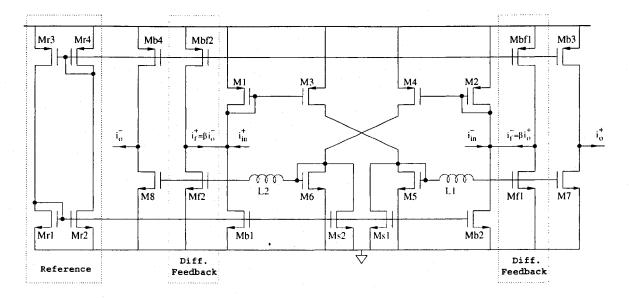

| 6.2  | Differential current-mode amplifier                                                          | 71 |

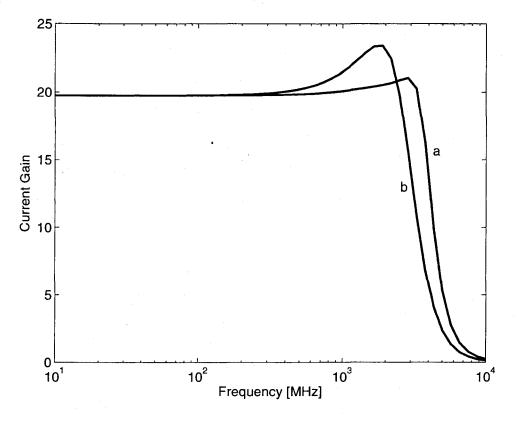

| 6.3  | Simulation with L at the 1st-stage input node                                                | 73 |

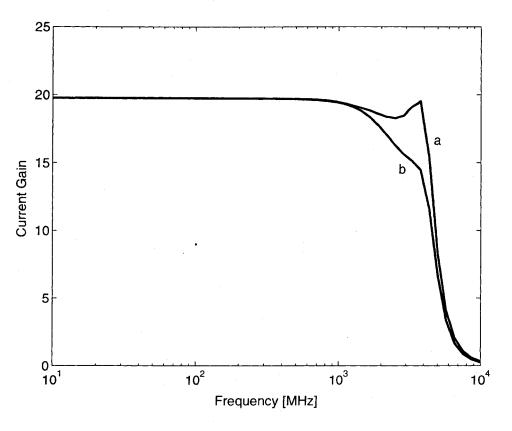

| 6.4  | Simulation with L at the 2nd-stage input node                                                | 74 |

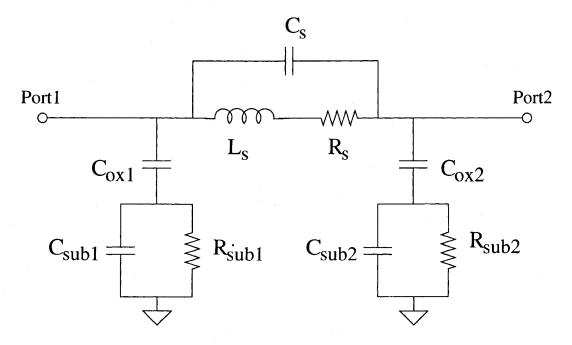

| 6.5  | Lumped model of on-chip inductors                                                            | 76 |

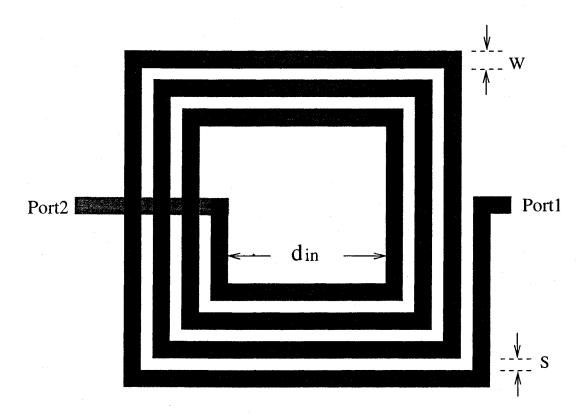

| 6.6  | Layout of on-chip planar inductor                                                            | 77 |

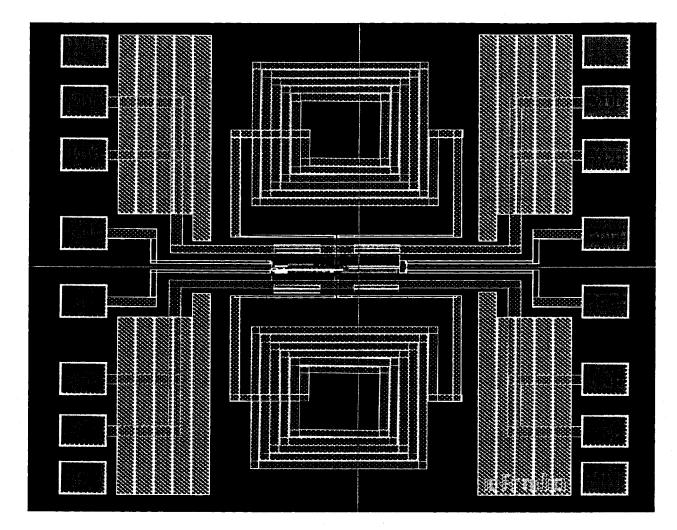

| 6.7  | Layout of the differential current-mode preamplifier                                         | 78 |

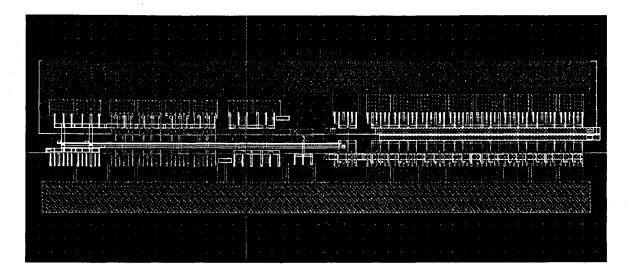

| 6.8  | Layout of the core circuits                                                                  | 79 |

| 6.9  | Frequency response of the differential preamplifier                                          | 79 |

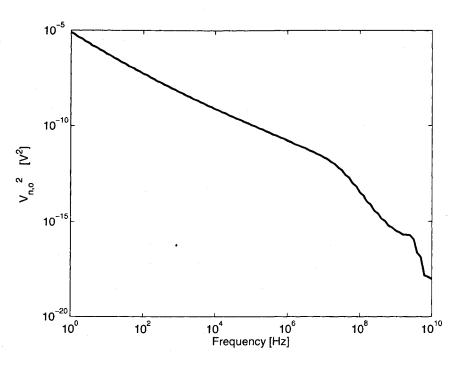

| 6.10 | Output noise voltage power                                                                   | 80 |

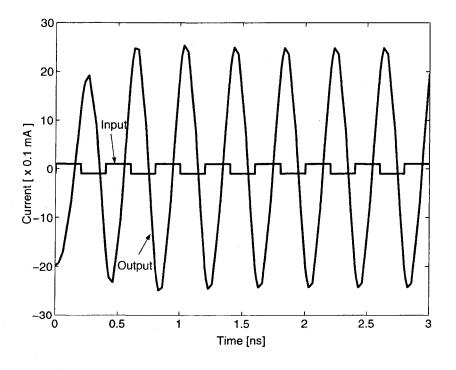

| 6.11 | Transient response of the differential preamplifier                                          | 81 |

# List of Tables

| 2.1 | Commonly used SONET and SDH transmission rates                                                                           | 8  |

|-----|--------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Minimum and maximum input power and their respective photocurrent                                                        |    |

|     | of OC-48 receivers                                                                                                       | 12 |

| 2.3 | The relationship between BER and SNR                                                                                     | 14 |

| 3.1 | Input and output impedances at low frequencies                                                                           | 25 |

| 3.2 | Channel width $(\mu m)$ of devices $\ldots \ldots \ldots$ | 27 |

| 3.3 | Input-referred noise generators                                                                                          | 32 |

| 4.1 | Damping characteristics                                                                                                  | 40 |

| 4.2 | Circuit parameters and bandwidth                                                                                         | 50 |

| 5.1 | Circuit parameters of single- and two-stage amplifiers                                                                   | 55 |

| 5.2 | Circuit parameters of differential amplifier                                                                             | 64 |

| 5.3 | Key performance parameters of differential amplifier                                                                     | 65 |

| 6.1 | Transistor sizes of the optical preamplifier                                                                             | 71 |

| 6.2 | Comparative performance of the preamplifiers                                                                             | 81 |

| A.1 | Three broad application categories in SONET physical layers                                                              | 85 |

| A.2 | Maximum and minimum power requirement at different speeds                                                                | 85 |

# Chapter 1 Introduction

#### 1.1 Overview

Optical fiber communication systems have been greatly developed with the blossom of Internet and Intranet networks. Optical communication systems are to carry a large volume of data across the networks. The primary application of such systems is in long distance telecommunication networks. For example, the telephone systems in Europe are connected to those in the North America through a fiber system installed across the Atlantic Ocean. Multimedia applications such as advanced graphics, audio, video conferences are driving the adoption of optical data links for short haul optical communications as well. The exchange of data using optical fiber communications gives a number of advantages over metal-wired cable systems. These are higher bandwidth, lower attenuation, smaller bit error rates (BERs), and less electromagnetic signal interface [1]. The cost of manufacturing and installing optical fiber cables is now less than that of metal cables for applications over 100 Mbps.

A transmitter and a receiver, connected by the fiber cable, constitute a generic optical communication system. The transmitter consists of a current drive circuit and an optical emitter, while the receiver consists of an optical detector and an amplifier circuit. The fiber cable is the transmission medium. The light experiences attenuation as it travels through long distance or low cost fibers. Thus, the receiver must exhibit wide bandwidth, high sensitivity and low noise. Our research is focused on the design of the front-end preamplifier which is the most challenging part in optical communication systems.

Currently, most high-speed optical receiver designs are using bipolar or GaAs MES-FET transistors [2], which give wider bandwidth. However, standard CMOS technology provides advantages such as low power and low cost. It also gives high degree of integration, which makes it possible to integrate the front-end preamplifier and the clock and data recovery circuits into a single chip. The  $f_T$  of MOS devices has also been improved significantly such that it is feasible to use CMOS for the optical front-end. The cost of an optical receiver built by GaAs is about 10 times that of a CMOS receiver. The rapid expansion of optical communication networks, especially the trend of "fiber-to-user" and "fiber-to-home", has brought more research interests on the design of low-cost, high-speed and low-noise optical receivers using standard CMOS technologies. In this thesis, a low-voltage current-mode CMOS preamplifier is designed using TSMC (Taiwan Semiconductor Manufacture Company) 0.18  $\mu$ m mixed-signal CMOS technology.

Transimpedance, high-impedance and low-impedance are three conventional configurations of preamplifiers of optical receivers. They convert the current from the photodetectors to a voltage signal. Intrinsically, all of the above configurations are based on voltage-mode operation. Recent advance in CMOS technology, mainly driven by low-power applications, has significantly lowered the supply voltage. The reduction in threshold voltages, however, is rather moderate in order to sustain needed noise margins. As a result, the performance of voltage-mode circuits is affected greatly. CMOS currentmode circuits offer many attractive advantages over their voltage-mode counterparts.

$\mathbf{2}$

The key performance feature of current-mode circuits is their inherent wide bandwidth. Transistor are used almost up to  $f_T$  in a current amplifier [3]. Other advantages include low supply voltage requirement, large dynamic range, and tunable input impedance [4]. These characteristics make the current-mode circuits particularly attractive for highspeed computer I/Os [5], and low-cost fiber communications [6].

The objective of this research is to design and build a current-mode front-end amplifier for optical receivers using standard CMOS technology. The aimed data rate is 5Gbps, which matches the rate of OC-96. The transimpednace gain is expected to reach 66dB $\Omega$  (2K $\Omega$ ) to sustain a large noise margin. The amplifier is intended to work with the minimum supply voltage requirement, and a differential configuration is adopted to minimize the switching noise caused by the clock and data recovery circuitry. The dynamic range of the amplifier must be large enough to accomodate different link distances. Other design objectives include minimum mismatch effects, and low power consumption.

TSMC 6-metal, 0.18  $\mu$ m, 1.8 V mixed-signal CMOS technology is used for the design. Spectre from Cadence Design Systems with BSIM3V3 device models [7] is the CAD tool used for analysis. The designed chip is currently being fabricated by TSMC via CMC (Canadian Microelectronics Corporation).

#### **1.2 Original Contributions**

This thesis designs a new low-voltage, wide-band, high gain, large dynamic range, and fully differential CMOS current-mode preamplifier for optical communications. Leading by a comprehensive analysis of the characteristics of current-mode circuits, several new topologies and design strategies are introduced to support the final circuit design.

The major contributions of the thesis are summarized as follows:

3

- An in-depth comparative analysis of the characteristics of various low-voltage CMOS current-mode configurations is conducted, and many useful insights are obtained.

- A new inductor series-peaking technique to boost the bandwidth of current amplifiers is developed and implemented in the design of the preamplifier.

- A new current feedback technique to lower the input impedance, boost the bandwidth, and reduce the value of the series-peaking inductance is developed and implemented in the design of the preamplifier.

- A two-stage fully balanced current amplifier to achieve a larger bandwidth with the same gain, and to minimize the mismatch effects of current mirrors is proposed.

A current-branching mechanism to reduce the power dissipation and increase the output impedance of current amplifiers is introduced.

- A differential current-mode configuration to minimize the effect of switching noise caused by the digital circuitry is proposed. A new negative differential current feedback to boost the bandwidth, and increase the dynamic range of the differential amplifier is implemented.

These original contributions have been published in one journal paper [8] and several conference proceedings [9] [10] [11] [12] [13].

#### 1.3 Thesis Organization

The thesis consists of 7 chapters and is organized as follows:

In chapter 2, we give a brief review of optical communication systems. The characteristics of photodetectors are depicted. The performance requirements and design challenges of optical receivers are described. Conventional structures of optical receivers are reviewed and analyzed. A primitive current-mode approach for optical front-end preamplifiers is proposed.

In chapter 3, we give a in-depth comparative study of the characteristics of various low-voltage current-mode circuits. Design issues, such as input impedance, bandwidth, dynamic range, and noise performance are examined both analytically and quantitatively. It reveals that most configurations fail to function properly at high frequencies. The current-mirror amplifier with current feedback offers the best performance.

Chapter 4 introduces two new bandwidth enhancement techniques for current-mode circuits. The inductor series-peaking technique boosts the bandwidth by utilizing the resonance characteristics of *LC* network formed by placing an inductor in series with the capacitor constituting the dominant pole. The technique is demonstrated in both of the current-mirror amplifier configuration and the optical preamplifier configuration. The current feedback increases the bandwidth by taking the advantage of negative feedback theory. A new sampling mechanism is introduced to acquire the feedback current. It shows that the employment of both the inductive peaking and current feedback further increases the bandwidth, and the current feedback can significantly reduces the value of the peaking inductor. Both the inductor series-peaking and the current feedback techniques do not affect the supply voltage and the DC biasing conditions.

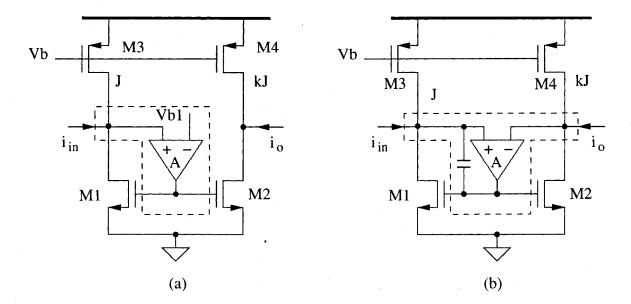

Chapter 5 introduces several topologies and design strategies to improve the performance of current-mode circuits. It shows that a two-stage amplifier configuration has a higher bandwidth than that of a single-stage one. The accuracy of current-mode circuits is severely affected by the errors caused by the mismatches of current mirrors. Analysis shows that a fully balanced configuration can minimize the DC bias-induced mismatch error, which is the dominant portion of the output offset current. A current-branching configuration is introduced to reduce the power consumption of the circuit, and to increase the output impedance. To minimize the effect of power and ground fluctuations caused by the switching of the digital portion of the receivers, we propose a fully differential current-mode configuration. Negative differential current feedback is employed to boost the bandwidth and improve the dynamic range of the differential amplifiers. A common-mode feedback configuration is proposed to increase CMRR and to stabilize the DC biasing condition.

Chapter 6 presents a new low-voltage fully differential CMOS current-mode preamplifier with the preceding circuit techniques implemented. It examines the design techniques, selection of circuit parameters, and the layout strategies. Simulation results are shown to demonstrate the performance of the preamplifier.

In chapter 7, the thesis is summarized and the directions of future research are discussed.

# Chapter 2 Background

This chapter gives an overview of the structure of optical communication systems, the characteristics of photodetectors, and the configuration of front-end amplifiers. It discusses the receiver design requirements, and reviews the principal structures of the preamplifiers. Followed by discussion on the challenges of the front-end design, we propose a current-mode approach.

#### 2.1 Generic Optical Communication Systems

Fig. 2.1 shows the basic elements of optical fiber communication systems. On the transmitter side, a drive circuitry accepts the modulated data and delivers large electrical current to the laser diode or light emitting diode (LED). Laser diodes or LEDs then convert the electrical signals into optical signals, and launch them into an optical fiber. The fiber, made from pure glass, is the high-speed propagating medium for optical signals. The device responsible for converting the optical signal back to an electrical signal is an optical receiver. A typical fiber optical receiver consists of an optical detector, a low-noise amplifier, and other circuitry used to recover the clock and data.

There are two widely adopted standards for synchronous fiber-optic transport systems. SONET (Synchronous Optical NETwork) is the North America standard, and

Transmitter

Receiver

#### Figure 2.1: Simple optical communication system

SDH (Synchronous Digital Hierarchy) is a similar standard used by the rest of the world [1]. Table 2.1 shows the data rates of SONET and SDH. Although the bandwidth of the fiber is capable of  $10^6$  Gbps with 1 Km communication distance, due to the speed limitation of the electrical devices, 2.5Gbps (OC-48) optical system was the state of the art design in the past few years and 10Gbps (OC-192) is emerging.

| SONET Level |        | SDH equivalent | Line rate (Mb/s) |  |

|-------------|--------|----------------|------------------|--|

| 1           | OC-1   | _              | 51.84            |  |

|             | OC-3   | STM-1          | 155.52           |  |

|             | OC-12  | STM-4          | 622.08           |  |

|             | OC-24  | STM-8          | 1244.16          |  |

|             | OC-48  | STM-16         | 2488.32          |  |

|             | OC-96  | STM-32         | 4976.64          |  |

|             | OC-192 | STM-64         | 9953.28          |  |

Table 2.1: Commonly used SONET and SDH transmission rates

There are three popular wavelengthes used in fiber communications. The firstgeneration links operated at around  $850 \ nm$ .  $1310 \ nm$  and  $1550 \ nm$  wavelengthes

8

were adopted with the development of optical sources and photodetectors because of their low attenuation in optical fibers as shown in Fig. 2.2 [2]. The launched optical signals will be progressively attenuated and distorted with increasing distance because of scattering, absorption, and dispersion in the glass material [2]. The attenuated and distorted signals have made the design of the front-end optical receivers to be the most challenging part of an optical communication system.

Figure 2.2: Attenuation in optical fibers

#### 2.2 Photodetectors

A photodetector is a transducer that converts the incident optical power into an electrical current. Semiconductor photodiodes are ideal for high-speed optical communications because of their superior frequency response, low dark currents and high quantum efficiency [14]. The principal photodiodes used in fiber optical systems include semiconductor positive-intrinsic-negative (PIN) photodiodes and avalanche photodiodes (APDs). A PIN photodiode is a semiconductor positive-negative (p-n) structure with an intrinsic region sandwiched between the other two regions. It is normally operated by applying a reverse-bias voltage. The magnitude of the reverse-bias voltage depends on the photodi-

ode application, but typically is less than a few volts. An avalanche photodiode (APD) is a photodiode that internally amplifies the photocurrent by an avalanche process. The sensitivity of APD detectors is usually higher than that of PIN detectors. However, a large reverse-bias voltage is needed to apply across the APD's active region.

The small-signal equivalent circuit of an PIN photodiode is shown in Fig. 2.4. The photodiode capacitance  $C_d$  consists mainly of the junction capacitance and parasitic capacitance of packaging. The series resistance  $R_s$  is very small comparing with the load resistance. Small  $C_d$  is needed to achieve high-speed response. A thick active area can lower the photodiode capacitance. However, a thick active region increases the transit time and decreases the responsivity of the photodiode. Practically, the photodiode capacitance is quite large (in the range of 100 to 500 fF) [15]. In general, the photodiode capacitance is the dominant factor of the frequency response of an optical receiver.

The photocurrent  $i_s$ , is generated through the creation of electron-hole pairs when photons from the incident light penetrate the diode. The relationship of the photocurrent and the incident optical power is given by

$$i_s = R_r P \qquad [A] \qquad (2.1)$$

1

1

ŀ

10

Figure 2.4: Small signal equivalent circuit of PIN photodiodes

where P is the average optical power incident on the photodiode and  $R_r$  is the responsivity of the photodiode and is given by

$$R_r = \frac{\eta q}{h\nu} \qquad [A/W] \qquad (2.2)$$

where  $\eta$  is the quantum efficiency (usually in the range of 0.6 to 0.9), q is the electron charge  $(1.69 \times 10^{-19} \text{ C})$ , and  $h\nu$  is the photon energy. The responsivity is a function of wavelength. As shown in Fig. 2.3 [2], the material of the photodiode must match the light wavelength to maximize the power efficiency. At a given wavelength (a given value of  $h\nu$ ), the responsivity is constant, so the photocurrent  $i_s$  is proportional to the optical power P. The typical value of  $R_r$  is around 0.85 A/W for InGaAs detectors at 1310 nm.. Table 2.2 shows the maximum and minimum input optical power and their respective photocurrent for SONET OC-48 receivers. The definition of long-distance (LR), intermediate-distance (IR) and short-distance (SR) optical links is given in Appendix A. It is seen that, in all the three type links, the photocurrent generated by the minimum input power is quite weak.

The photodiode also generates un-negligible noise power  $I_n^2$  into the downstream preamplifier. This noise consists of thermal noise, dark current noise, and quantum

Table 2.2: Minimum and maximum input power and their respective photocurrent of OC-48

receivers

| (with $R_r = 0.85 \text{ A/W}$ ) |                |       |       |  |  |  |  |  |

|----------------------------------|----------------|-------|-------|--|--|--|--|--|

|                                  | Short Distance |       |       |  |  |  |  |  |

| $P_{max}$ (dBm)                  | -10            | 0     | -3    |  |  |  |  |  |

| Current $(\mu A)$                | 85             | 850   | 426   |  |  |  |  |  |

| $P_{min}$ (dBm)                  | -26            | -18   | -18   |  |  |  |  |  |

| Current $(\mu A)$                | 2.14           | 13.47 | 13.47 |  |  |  |  |  |

noise [14]. Although low-noise photodiodes are essential for high-performance optical receivers, the noise of the preamplifier is usually the dominant contributor to the noise of the receiver.

#### 2.3 **Optical Preamplifiers**

#### 2.3.1 Preamplifier Performance Parameters

The front-end amplifies the photocurrent so that it can be used by following clock and data recovery circuits. It plays a crucial role in determining the overall performance of the receiver such as gain, bandwidth, noise, and dynamic range.

(i) **Gain** – Since the photocurrent generated by the photodiode is small, the gain of the preamplifier must be large enough. Large preamplifier gain helps to overcome the noise of the subsequent stage. Therefore, the design of the subsequent stage, typically a 50- $\Omega$  driver or a limiting post-amplifier, can be simplified [15]. The gain trades with bandwidth and dynamic range. The tendency of increasing data rate and decreasing power supply voltage have limited the transimpedance gain from several kilo-Ohms to a few hundred Ohms. (ii) **Bandwidth** – Due to the inevitable large photodiode capacitance, the total input capacitance of the preamplifier,  $C_{in}$ , consisting of the photodiode capacitance, pad capacitance, and input transistor parasitic capacitances, usually dominates the frequency response of the receiver. The bandwidth is determined by the time constant  $\tau = R_{in}C_{in}$ at the input. The rising time of the step response is given by  $t_r = 2.2R_{in}C_{in}$  [16]. SONET employs Non-Return-to-Zero (NRZ) as its data format. With  $t_r = \frac{1}{2}$ Bit-Time, it is given that

$$f_{-3dB} = \frac{1}{2\pi R_{in}C_{in}} = \frac{2.2}{2\pi t_r} = \frac{2.2}{2\pi \times \frac{1}{2}\text{Bit-Time}} = \frac{2.2}{\pi} \times \text{Bit-Rate}$$

(2.3)

For example, the data rate of SONET OC-96 is about 5 Gbps, the minimum bandwidth requirement of the optical receiver is 3.5 GHz.

(iii) Noise – The receiver sensitivity is the minimum amount of optical power required to achieve a specific receiver performance. For digital transmission at a given data rate, this performance is characterized by the maximum bit-error rate (BER) [2]. In analog systems, for a given modulation and bandwidth, it is described by the minimum signalto-noise ratio (SNR). The relationship between BER and SNR [15] [17] [18] is given by

$$BER = \frac{1}{\sqrt{2\pi}Q} \exp(-\frac{Q^2}{2})$$

(2.4)

where

$$Q = \frac{1}{2} \times \text{SNR} = \frac{1}{2} \times \frac{\text{Signal}_{pp}}{\text{Noise}_{rms}}$$

(2.5)

SONET standard requires the BER not less than  $1 \times 10^{-10}$ . From Table 2.2, -18dBm incident optical power generates a 13.47  $\mu A_{pp}$  photocurrent (with  $R_r=0.85$  A/W). Thus

to achieve a BER less than  $1 \times 10^{-10}$ , the input current noise, including the input referred current noise of the preamplifier and the noise of the photodiode, must be lower than 1.06  $\mu A_{rms}$ .

| <b>Table 2.3:</b> The relationship between BER and SNR |           |           |           |            |            |            |            |            |

|--------------------------------------------------------|-----------|-----------|-----------|------------|------------|------------|------------|------------|

| BER                                                    | $10^{-7}$ | $10^{-8}$ | $10^{-9}$ | $10^{-10}$ | $10^{-11}$ | $10^{-12}$ | $10^{-13}$ | $10^{-14}$ |

| SNR $(A/A)$                                            | 10.4      | 11.2      | 12.0      | 12.7       | 13.4       | 14.1       | 14.7       | 15.3       |

(iv) Dynamic Range – Dynamic range of the receiver refers to the range of optical power levels over which the receiver operates within the specification. Table 2.2 shows that the power specifications vary dramatically according to the transmission distance. Receivers that have large dynamic range are essential to the flexibility of variable-distance links. However, Recent advance in CMOS technology has significantly lowered the supply voltage, while the threshold voltages of MOS devices have only been reduced moderately. As a result, the input and output signal swings are strictly limited. Low-voltage amplifiers tolerating high signal swing are crucial in up-to-date optical receiver design.

#### 2.3.2**Conventional Preamplifier Structures**

Optical preamplifiers convert the current from photodiodes into a voltage signal. As depicted in Fig. 2.5 and 2.6, there are three typical preamplifier configurations, namely low-impedance, high-impedance, and transimpedance amplifiers. Low/high impedance preamplifiers have the same topology. Their transfer function is given by

$$\frac{V_o(s)}{I_{in}(s)} = -\frac{AR}{1 + sRC_{in}} \tag{2.6}$$

where R is the termination resistance,  $C_{in}$  is the total input capacitance consisting of

14

Figure 2.5: Low impedance and high impedance amplifiers

photodiode capacitance  $C_d$  and preamplifier parasitic input capacitance. The bandwidth is given by

$$f_{-3dB} = \frac{1}{2\pi R C_{in}}$$

(2.7)

As depicted in Section 2.2, the photodiode capacitance  $C_d$  is usually large. As a result, the total input capacitance usually dominates the frequency response of the preamplifier. Thus, low-impedance configuration exhibits a better high-speed performance. This configuration also has a good dynamic range. The noise performance of this configuration is poor. This is because the thermal noise of the termination resistor R is directly referred to the input, and its noise current power density is given by

$$\overline{i_{n,R}^2} = \frac{4kT}{R} \qquad [A^2/\text{Hz}] \qquad (2.8)$$

where k is the Boltzmann's constant  $(1.38 \times 10^{-23} J/K)$  and T is the absolute temperature degree in Kelvin. The smaller the value of R, the higher the noise current. High-

15

impedance amplifiers improve the noise performance at the expense of both the dynamic range and bandwidth. Usually, this configuration needs an equalizer to enlarge the bandwidth.

Figure 2.6: Transimpedance amplifier and its noise sources

Transimpedance amplifiers (TIAs) shown in Fig. 2.6 is a compromise of low-impedance and high-impedance approaches.  $R_f$  is a shunt-shunt feedback resistor [19], and the transfer function is given by

$$\frac{V_o(s)}{I_{in}(s)} = -\left(\frac{A}{A+1}\right) \frac{R_f}{1+s\frac{R_f C_{in}}{A+1}}$$

(2.9)

The bandwidth is given by

$$f_{-3dB} \approx \frac{A}{2\pi R_f C_{in}} \tag{2.10}$$

It is seen that the transimpedance gain is approximately equal to the resistance of  $R_f$ , and the bandwidth is boosted by the voltage gain.

From Fig. 2.6, the output noise voltage is given by

$$V_{n,out}(s) = \frac{V_{n,R_f} + (sR_fC_d + 1)V_{n,A}}{1 + \frac{sR_fC_d}{A}}$$

(2.11)

where  $V_{n,A}$  is the input referred noise voltage of the voltage amplifier,  $V_{n,R_f}$  is the noise voltage of the feedback resistor. It can be shown that if  $C_d = 0$ , then  $V_{n,out} = V_{n,R_f} + V_{n,A}$ , yielding the input referred noise current of the transimpedance amplifier

$$\overline{I_{n,in}^2} \coloneqq \frac{\overline{V_{n,R_f}^2} + \overline{V_{n,A}^2}}{R_f^2}$$

$$= \frac{4kT}{R_f} + \frac{\overline{V_{n,A}^2}}{R_f^2}$$

(2.12)

The input referred noise voltage of the voltage amplifier is divided by  $R_f$ , but the noise of  $R_f$  is directly referred to the input.

Much research has been done on CMOS transimpedance amplifiers. The commongate transimpedance amplifier [20] features large bandwidth, but its dynamic range is small and the input referred noise is high. Regulated cascode configuration [21] was introduced to increase the bandwidth and reduce the noise of the common-gate amplifiers, but this configuration has small gain and high power consumption. Most CMOS transimpedance amplifiers use the common-source configuration [22] as shown in Fig. 2.7(a).

As depicted in Section 2.3.1, the transimpedance gain ( $\approx R_f$ ) is about a few hundred Ohms to a few kilo-Ohms. Only poly resistors and diffusion n+/p+ resistors, whose sheet resistance is small, are suitable to be used to build such a relatively small feedback resistor. Unfortunately, CMOS passive resistors have very poor accuracy. For example, the error of the poly resistors is about  $\pm 20\%$ , and that of the diffusion n+/p+ resistors is about  $\pm 30\%$  [23]. Thus, the transimpedance gain is very difficult to be accurately specified, resulting in uncontrolled amplifying performance. It is even more challenging

**Figure 2.7:** CMOS transimpedance amplifiers (a)Common-source amplifier, (b)Invertor amplifier

in designing an analog signal processing system where accuracy is strictly required. Another disadvantage of the common-source transimpedance amplifier is that the output voltage has to be restrained to ensure that the transistor is working in the saturation region. Thus, the dynamic range of this configuration is small [24].

An invertor transimpedance amplifier as shown in Fig. 2.7(b) [25] was introduced recently. Active feedback is employed in this configuration. The feedback PMOS transistor  $M_f$  works in the linear region. The major disadvantage of this circuit is that the transistor  $M_f$  working in the linear region has a large drain-to-substrate parasitic capacitance [25]. It introduces a large loading capacitance at the output node.

#### 2.3.3 Current-Mode Approach

Voltage amplifiers are employed in the conventional preamplifiers. The gain-bandwidth product of the amplifiers limits the bandwidth of the voltage amplifiers as well as the

18

bandwidth of the whole preamplifier. The optimal voltage gain in the invertor transimpedance amplifier is only about 3 [25]. Thus, a small and accurate feedback resistor is critical for the high performance wide-band preamplifiers.

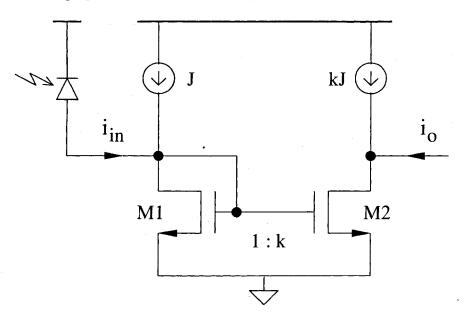

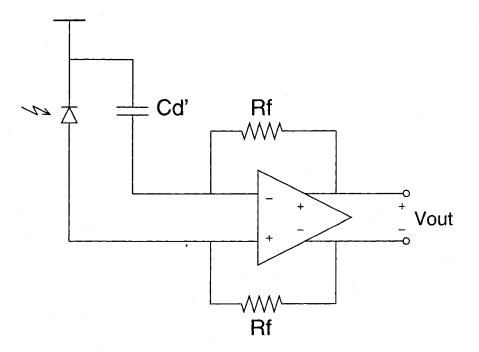

Figure 2.8: Current-mode approach of optical fron-end

The intrinsic advantages of current-mode circuits including large bandwidth, low supply voltage requirement, tunable input impedance, and large dynamic range [3] [4], make them particularly attractive for low-cost optical communications. Current-mirrors are the building blocks of current-mode circuits. Fig. 2.8 shows a primitive current-mode approach for an optical front-end. No necessary passive components are adopted. The current source may be implemented by PMOSs with a DC gate voltage. The minimum requirement of the supply voltage is about  $V_{T,n} + V_{sat,p}$ , where  $V_T$  is the threshold voltage and  $V_{sat}$  is the pinch-off voltage. The input impedance is given by

$$R_{in} \approx \frac{1}{g_{m1}} = \frac{1}{\sqrt{2\mu_n C'_{ox}(W/L)_1 J}},$$

(2.13)

where  $\mu_n$  is the surface mobility of the channel of NMOS,  $C'_{ox}$  is the gate oxide capaci-

tance density. A desired low impedance is achievable by increasing the biasing current J or by increasing the channel width of  $M_1$ .

The current gain at low frequencies is given by

$$k = \frac{(W/L)_2}{(W/L)_1} \left(\frac{v_{GS2} - V_{T2}}{v_{GS1} - V_{T1}}\right)^2 \frac{1 + \lambda v_{DS2}}{1 + \lambda v_{DS2}},\tag{2.14}$$

where  $\lambda$  is the channel length modulation parameter,  $v_{GS}$  and  $v_{DS}$  are the gate-source and drain-source voltages, respectively. Neglecting the mismatches, we obtain  $k = \frac{(W/L)_2}{(W/L)_1}$ . The current gain simply equals to the size ratio between the output and input transistors. The higher the current, the larger the size of output transistors, resulting in larger parasitic capacitances. As long as the parasitic capacitances of the transistors are much smaller than that of the photodiode, the increase in the current gain has a little effect on the bandwidth.

The input referred noise current power density of the current mirror amplifier is given by

$$\overline{I_{n,in}^{2}} = 4kT\gamma g_{m1} + \frac{4kT\gamma g_{m2}}{k^{2}}$$

$$= 4kT\gamma g_{m1}(1 + \frac{1}{k})$$

(2.15)

where  $\gamma$  equals 2/3 for long-channel transistors and may be larger for submicron MOS-FET [26]. If  $k \gg 1$ , the noise from  $M_2$  can be neglected.

It is seen that a low input impedance requires both a large biasing current and a large input transistor. To achieve a high current gain, both the biasing current and the transistor size at the output branch becomes extremely large, resulting in high power dissipation and large parasitic capacitances (maybe comparable to the photodiode capacitance). The performance of current-mode circuits deteriorates due to mismatches, and their dynamic range is limited by the biasing current. In the following chapters, we will give an in-depth analysis on CMOS current-mode circuits, and introduce several new topologies and design strategies to improve the performance of those circuits.

### Chapter 3

## Comparative Study of Low-Voltage CMOS Current-Mode Circuits

Current mirrors are the building blocks of CMOS current-mode circuits [4]. Due to the significantly lowered supply voltage by advance technology, the performance of many effective current-mode circuits, such as cascode [27] and class-AB current mirrors [28], is affected severely.

This chapter presents a comparative study of the characteristics of low-voltage CMOS current-mode circuits for optical communications both analytically and quantitatively. It examines design issues including input impedance, bandwidth, dynamic range, and noise performance for low-voltage CMOS current-mode circuits. A new current mirror with current feedback to lower the input impedance and increase the bandwidth is proposed (more discussions on this configuration are given in Section 4.3). The performance of these current mirrors is assessed using Cadence Spectre and the results are presented.

#### 3.1 Input Impedance

Low input impedance is essential for optical preamplifiers because the parasitic capacitance of photodiodes is usually much larger than the input capacitance of preamplifiers. As a result, the dominant pole of optical preamplifiers is usually determined by the par-

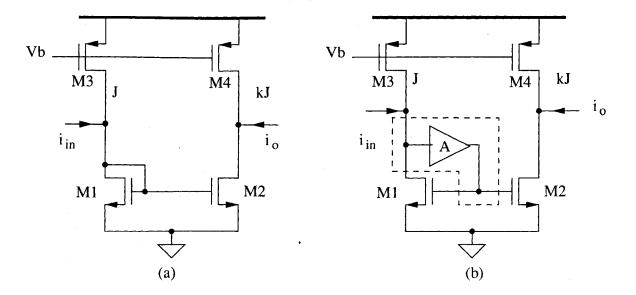

Figure 3.1: (a) Basic current mirror (BASIC); (b) Low input-impedance current mirror (LI-IMP)

Figure 3.2: Current mirrors with common-gate feedback (CGFB)

asitic capacitance of photodiodes and the input resistance of preamplifiers. The *basic* current mirror shown in Fig. 3.1(a) has the input impedance of

$$R_{in} = \frac{1}{g_{m1} + (1/r_{o1})} \approx \frac{1}{g_{m1}},$$

(3.1)

where  $g_m$  is the transconductance and  $r_o$  is the output resistance of the MOS transistors.

Figure 3.3: (a) Mirror with active feedback (ACTIVE). (b) Bootstrapped current mirror (BSTRP)

**Figure 3.4:** (a) Auxiliary differential-input single-output Opamp. (b) High bandwidth current mirror (HBW)

The input impedance can be reduced by inserting a voltage amplifier between the drain and gate of M1, as shown in Fig. 3.1(b), leading to the *low input-impedance current mirror*. The input impedance of the LI-IMP mirror at low frequencies is given by

$$R_{in} = \frac{1}{Ag_{m1} + (1/r_{o1})} \approx \frac{1}{Ag_{m1}}.$$

(3.2)

The voltage amplifier can be implemented using common-gate configuration to take the advantage of its immunity from Miller effect, as shown in Fig. 3.2. It can be shown that the input impedance of the CGFB mirrors at low frequencies is approximately given by

$$R_{in} \approx \frac{1}{g_{m1}(r_{o6}g_{m5})},\tag{3.3}$$

much smaller as compared with that of the basic mirror.

The amplifier can also be differentially configured as shown in Fig. 3.3(a) [29]. To achieve both a low input impedance and a high output impedance, the bootstrapped CMOS current mirror proposed in [30] and shown in Fig. 3.3(b) can be used. This configuration, however, suffers from poor stability at high frequencies. A compensation capacitor is needed as shown and the mirror becomes the basic mirror at high frequencies. The implementation of the auxiliary differential amplifier is shown in Fig. 3.4(a) with bandwidth approximately 692MHz. A drawback of the differential amplifier approach is that it requires a higher supply voltage.

| ~ |                      |                          |                         |  |  |

|---|----------------------|--------------------------|-------------------------|--|--|

|   | Mirror               | Input Impedance          | Output Impedance        |  |  |

|   | BASIC                | $1/g_{m1}$               | $r_{o2}  r_{o4} $       |  |  |

|   | CGFB                 | $1/(r_{o6}g_{m5}g_{m1})$ | $r_{o2}  r_{o4} $       |  |  |

|   | HBW                  | $1/g_{m1}$               | $r_{o2}  r_{o4}  $      |  |  |

|   | $\operatorname{RES}$ | $1/g_{m1}$               | $r_{o2}  r_{o4} $       |  |  |

|   | ACTIVE               | $1/(Ag_{m1})$            | $ r_{o2}  r_{o4} $      |  |  |

|   | BSTRP                | $1/(Ag_{m1})$            | $(Ag_{m1}r_{o1})r_{o2}$ |  |  |

|   | $\operatorname{CFB}$ | $1/[g_{m1}(1+k\beta)]$   | $r_{o2}  r_{o4}  $      |  |  |

**Table 3.1:** Input and output impedances at low frequencies(the output impedance of biasing current source is assumed to be infinite)

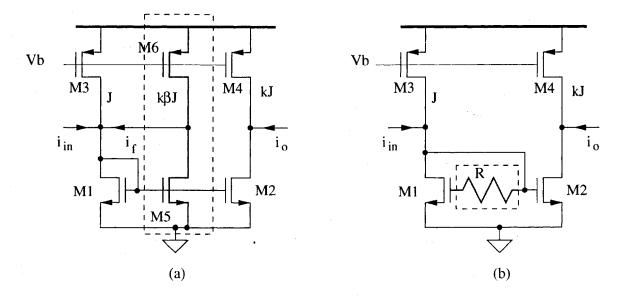

Figure 3.5: (a) Current mirror with current feedback (CCFB). (b) Current mirror with resistor (RES)

It is well known that current-current feedback is capable of reducing input impedance and increasing bandwidth. To sample the output current without adding more elements between  $V_{DD}$  and ground, an additional branch is added in parallel with the output transistor to sample the output current. The sampled output current is then fed back to the input, as shown in Fig. 3.5(a). It can be shown that the input impedance of the CCFB mirror is given by

$$R_{in} = \frac{1}{g_{m1}(1+k\beta)},\tag{3.4}$$

where k and  $\beta$  are the gain of the forward and feedback paths respectively.

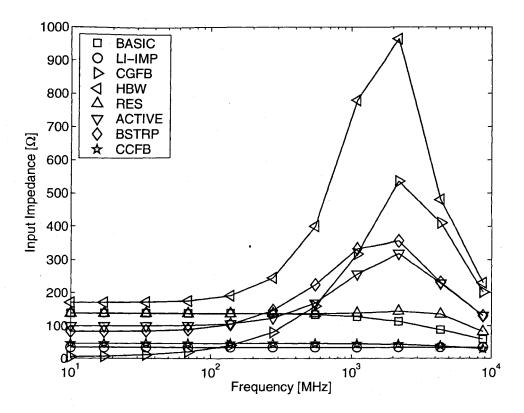

The input and output impedance of the mirrors are tabulated in Table 3.1. To quantify the input characteristics, these mirrors were implemented using TSMC  $0.18\mu$  CMOS technology with circuit parameters given in Table 3.2, and simulated using Spectre with BSIM3v3 device models. The amplifier in LI-IMP current mirror is implemented using an ideal VCVS with gain of 5. The results are plotted in Fig. 3.6. The impedance of the

Figure 3.6: Input impedance

| $(L_{min} = 0.18 \mu \text{m} \text{ is used for all devices})$ |    |     |    |     |    |    |

|-----------------------------------------------------------------|----|-----|----|-----|----|----|

| Mirror                                                          | M1 | M2  | M3 | M4  | M5 | M6 |

| BASIC                                                           | 25 | 100 | 25 | 100 | i  |    |

| CGFB                                                            | 25 | 100 | 25 | 100 | 40 |    |

| HBW                                                             | 25 | 100 | 25 | 100 | 20 |    |

| RES                                                             | 25 | 100 | 25 | 100 |    |    |

| ACTIVE                                                          | 25 | 100 | 25 | 100 |    |    |

| BSTRP                                                           | 25 | 100 | 25 | 100 |    |    |

| CFB                                                             | 25 | 100 | 25 | 100 | 50 | 50 |

| Opamp                                                           | 2  | 2   | 2  | 2   |    |    |

**Table 3.2:** Channel width  $(\mu m)$  of devices  $(L_{min} = 0.18 \mu m)$  is used for all devices)

basic mirror at low frequencies is  $137\Omega$ . LI-IMP mirror gives a lower and constant input impedance of  $35\Omega$ . The input impedance of CCFB mirror is  $46\Omega$  and decreases with frequency. CGFB mirror provides the lowest input impedance at low frequencies only.

At high frequencies the input impedance of CGFB, HBW, active and bootstrapped mirrors is significantly high, revealing that they are not suitable for optical communications where signal frequency is in the range of GHz.

## 3.2 Bandwidth

The bandwidth of the basic mirror is given by

$$\dot{\omega}_{-3dB} = \frac{g_{m1}}{C_{qs1} + C_{qs2}}.$$

(3.5)

It can be adjusted by changing the bias current. The bandwidth of CGFB mirror can be obtained from its transfer function

$$\frac{I_o(s)}{I_{in}(s)} = \frac{\frac{g_{m2}g_{m5}}{C_{gs5}(C_{gs1} + C_{gs2})}}{s^2 + s\frac{g_{m5}}{C_{gs5}} + \frac{g_{m1}g_{m5}}{C_{gs5}(C_{gs1} + C_{gs2})}}.$$

(3.6)

with the poles located at

$$p_{1,2} = \frac{g_{m5}}{2C_{gs5}} \left[ -1 \pm \sqrt{1 - 4\left(\frac{g_{m1}}{C_{gs1} + C_{gs2}}\right) \left(\frac{C_{gs5}}{g_{m5}}\right)} \right].$$

(3.7)

It is seen that under the condition  $\frac{g_{m1}}{C_{gs1} + C_{gs2}} = \frac{1}{4} \left( \frac{g_{m5}}{C_{gs5}} \right)$ , the circuit has two identical real poles. The bandwidth is given by  $\omega_{-3dB} = \frac{g_{m5}}{2C_{gs5}}$ , approximately 2 times that of the basic current mirror.

The mirror shown in Fig. 3.4(b) is derived from [31] and is called the *high-bandwidth* current mirror. The source follower is employed to suppress the capacitance at the input node. From the transfer function

$$\frac{I_o(s)}{I_{in}(s)} = \frac{\frac{g_{m2}g_{m5}}{C_{gs5}(C_{gs1} + C_{gs2})} \left(s\frac{C_{gs5}}{g_{m5}} + 1\right)}{s^2 + s\frac{g_{m1}}{C_{gs1} + C_{gs2}} + \frac{g_{m1}g_{m5}}{C_{gs5}(C_{gs1} + C_{gs2})}},$$

(3.8)

we obtain the two poles

$$p_{1,2} = \frac{g_{m1}}{2(C_{gs1} + C_{gs2})} \Big[ -1 \pm \sqrt{1 - 4\Big(\frac{g_{m5}}{C_{gs5}}\Big)\Big(\frac{C_{gs1} + C_{gs2}}{g_{m1}}\Big)} \Big].$$

(3.9)

Under the condition  $\frac{g_{m1}}{C_{gs1} + C_{gs2}} = \frac{1}{4} \left( \frac{g_{m5}}{C_{gs5}} \right)$ , two identical real poles are obtained. It is seen that the added transistor M5 introduces a zero and does not affect the real part of the poles. The bandwidth is given by  $\omega_{-3dB} = \frac{g_{m1}}{2(C_{gs1} + C_{gs2})}$  approximately, only half of the bandwidth of the basic mirror.

To avoid using active devices at the input, which may cause unwanted oscillation, a resistor can be inserted between the gates of the input and output transistors, as shown in Fig. 3.5(b) [32]. With the transfer function given by

$$\frac{I_o(s)}{I_{in}(s)} = \frac{g_{m2}(sRC_{gs1}+1)}{RC_{gs1}C_{gs2}\left(s^2 + s\frac{C_{gs1}+C_{gs2}}{RC_{gs1}C_{gs2}} + \frac{g_{m1}}{RC_{gs1}C_{gs2}}\right)},$$

(3.10)

it can be shown that when  $R = \frac{1}{g_{m1}}$ , the zero and one of the poles cancel out, resulting in a first-order system with the pole at  $s = -\frac{1}{RC_{gs2}}$ . The bandwidth of the circuit is much larger in this case. Further analysis in Section 3.4, however, reveals that the resistor increases the output noise of the circuit significantly. To increase the bandwidth without employing noisy resistors, CCFB mirror can be used. The current gain of the CCFB mirror is given by

$$\frac{I_o(s)}{I_{in}(s)} = \frac{\frac{g_{m2}}{g_{m1}(1+k\beta)}}{s\left[\frac{C_{gs1}+C_{gs2}+C_{gs5}}{g_{m1}(1+k\beta)}\right]+1},$$

(3.11)

from which we obtain the bandwidth

$$\omega_{-3dB} = \left(\frac{g_{m1}}{C_{gs1} + C_{gs2} + C_{gs5}}\right)(1 + k\beta).$$

(3.12)

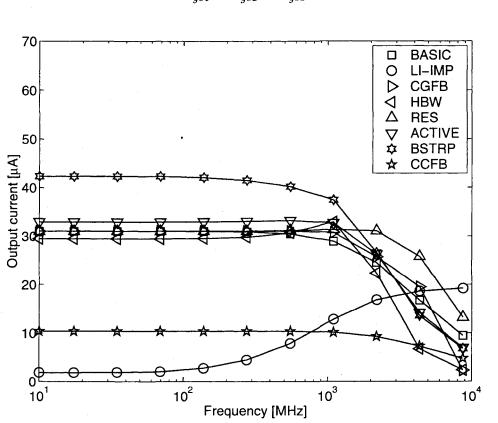

Figure 3.7: Output current (with  $I_{in} = 10\mu A$ )

It is seen that the bandwidth is increased by a factor of  $(1 + k\beta)$  approximately. The bandwidth of the active and bootstrapped current mirrors is the same as that of the basic mirror because the bandwidth of the differential amplifier is smaller. Fig. 3.7 shows the output current of these mirrors. The basic mirror has bandwidth of 2.7 GHz. The bandwidth of the mirror with common-gate feedback provides bandwidth of 2.65 GHz. The bandwidth of HBW-mirror is approximately 2.3 GHz. The bandwidth of the mirror with a 1k $\Omega$  resistor is approximately 5.43 GHz. The values of k and  $\beta$  of the mirror with CCFB are 4 and 0.5, respectively. Simulation results show that the CCFB mirror has the bandwidth of 4.3 GHz.

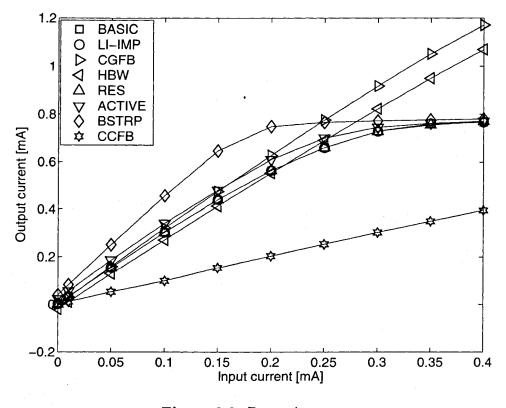

## 3.3 Dynamic Range

The dynamic range of the current mirrors are examined by varying the input current from 0 to 0.4 mA (55% of J) and measuring the corresponding output current. Active current mirrors are used as the output loads. The results are plotted in Fig. 3.8. It is seen that the dynamic range of BASIC current mirror is about 27% J. CCFB current mirror provides the largest dynamic range while bootstrapped current mirror has the smallest dynamic range.

## 3.4 Noise

Using small-signal analysis, the power of the input-referred noise voltage generator  $\overline{v_n^2}$  and that of the input-referred noise current generator  $\overline{i_n^2}$  of the current mirrors are derived and tabulated in Table 3.3. It is seen that (i) if the current gain of the mirror is large, both the contribution of the noise of M2 and the input-referred voltage noise generator are negligible. (ii) The effect of the noise of the feedback transistor M5 in both HBW and CGFB mirrors is marginal. (iii) The noise of the mirror with a compensation resistor is significantly larger as compared with that of other mirrors. (iv) The input-referred noise of CCFB mirror is higher than that of the basic current mirror due to the reduction of the current gain and the noise of the feedback device.

| Table 5.5: Input-relefied hoise generators |                                                                                                                                             |                                                                               |  |  |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|

| Mirror                                     | $i_n^2$                                                                                                                                     | $v_n^2$                                                                       |  |  |

| BASIC                                      | $\overline{i_{n1}^2} + \left(rac{g_{m1}}{g_{m2}} ight)^2 \overline{i_{n2}^2}$                                                              | $\frac{\overline{i_{n2}^2}}{g_{m2}^2}$                                        |  |  |

| CGFB                                       | $\overline{i_{n1}^2} + \left(rac{g_{m1}}{g_{m2}} ight)^2 \overline{i_{n2}^2}$                                                              | $\approx 0$                                                                   |  |  |

| HBW                                        | $\overline{i_{n1}^2} + \left(\frac{g_{m1}}{a_{m2}}\right)^2 \overline{i_{n2}^2} + \left(\frac{g_{m1}}{a_{m5}}\right)^2 \overline{i_{n5}^2}$ | $\frac{\overline{i_{n1}^2}}{g_{m1}^2} + \frac{\overline{i_{n2}^2}}{g_{m2}^2}$ |  |  |

| RES                                        | $\overline{i_{n1}^2} + \left(\frac{g_{m1}}{g_{m2}}\right)^2 \overline{i_{n2}^2} + (g_{m1}R)^2 \overline{i_{nR}^2}$                          | $\frac{\overline{i_{n2}^2}}{g_{m2}^2}$                                        |  |  |

| ACTIVE                                     | $\overline{i_{n1}^2} + \Big(rac{g_{m1}}{g_{m2}}\Big)^2 \overline{i_{n2}^2}$                                                                | $\overline{\hat{v}_n^2} + \frac{\overline{\hat{i}_{n2}^2}}{Ag_{m2}^2}$        |  |  |

| BSTRP                                      | $\overline{i_{n1}^2} + \left(\frac{g_{m1}}{a_{n2}}\right)^2 \overline{i_{n2}^2}$                                                            | $\overline{\hat{v}_n^2} + \frac{\overline{\hat{i}_{n2}^2}}{Ag_{m2}^2}$        |  |  |

| CCFB                                       | $\overline{i_{n1}^2} + \left[\frac{g_{m1}^2(1+k\beta)^2}{g_{m2}^2}\right]\overline{i_{n2}^2} + \overline{i_{n5}^2}$                         | $rac{\overline{i_{n2}^2}}{g_{m2}^2}$                                         |  |  |

Table 3.3: Input-referred noise generators

## 3.5 Summary

An in-depth investigation of the small and large-signal characteristics of low-voltage CMOS current mirrors has been presented. The ideal LI-IMP current mirror effectively lowers the input impedance. Practical implementation of LI-IMP current mirror, however, suffers from large input impedances at high frequencies. CCFB and RES current mirrors provide low and monotonically decreasing input impedances. Among the current mirrors investigated, only CCFB and RES give significant improvement in bandwidth. BASIC, CGFB, and HBW current mirrors offer low noise. RES has the highest noise, mainly due to the thermal noise of the added resistor. The noise of CCFB is higher than that of BASIC due to its reduced current gain. CCFB current mirror provides the largest dynamic range whereas bootstrapped current mirror has the lowest dynamic range.

## Chapter 4

# New Bandwidth Enhancement Techniques for CMOS Current-Mode Circuits

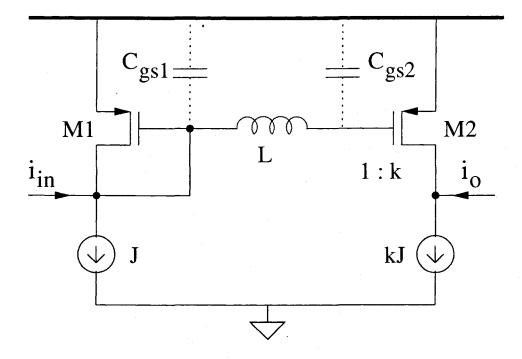

This chapter introduces two new bandwidth enhancement techniques, namely inductor series-peaking and negative current feedback, for low-voltage CMOS current-mode circuits.

Although inductors are commonly associated with narrow-band RF circuits, they are useful in broad-band circuits as well. The proposed inductor series-peaking technique boosts the bandwidth by utilizing the resonance characteristics of *LC* network formed by placing an inductor in series with the capacitor constituting the dominant pole. Two configurations are investigated. In the first configuration where the dominant pole is due to the gate-source capacitance of the output branch of current-mirror amplifiers. The peaking inductor is added between the gates of the input and output transistors. In the second configuration, the current amplifier is used as a pre-amplification stage of optical receivers. In this case, the parasitic capacitance of the photo diode and that of the packaging of the chip constitute the dominant pole. The peaking inductor is placed at the input node of the amplifier. Both the bond wire inductance and on-chip spiral inductance can be used to realize this inductor.

The current feedback increases the bandwidth by taking the advantage of negative feedback theory. A new sampling mechanism is introduced to acquire the feedback current. The employment of both the inductive peaking and current feedback further increases the bandwidth. Another notable advantage of the current feedback is that it significantly reduces the value of the peaking inductor, which is not only area-greedy but also has a strong interaction with the substrate. Both the inductor series-peaking and the current feedback techniques do not affect the supply voltage and DC biasing conditions.

Before introducing the new techniques, we begin with a brief review of two existing bandwidth enhancement techniques. The first is inductive shunt-peaking technique for voltage-mode circuits, and the second is resistive-compensation technique for currentmode circuits.

## 4.1 Inductive Shunt-Peaking and Resistive Compensation

Both inductive shunt-peaking and resistive-compensation techniques enhance the bandwidth by creating a zero to compensate the dominant pole.

As shown in Fig. 4.1, neglecting the parasitic capacitances, the transfer function of this simple common-source voltage amplifier (with L = 0) is given by

$$\frac{V_o(s)}{V_{in}(s)} = \frac{g_m R}{1 + sRC}.$$

(4.1)

The bandwidth is determined by a single dominant pole, which is determined by the output load resistance R and load capacitance C.

The inductive shunt-peaking technique introduces an inductor L in series with the load resistance and in parallel with the load capacitance. The transfer function is given

Figure 4.1: Inductive shunt-peaking technique

by

$$\frac{V_o(s)}{V_{in}(s)} = \frac{g_m(R+sL)}{1+sRC-s^2LC}.$$

(4.2)

The zero is solely determined by the L/R time constant and is primarily responsible for the bandwidth enhancement. The frequency response of this shunt peaked amplifier is characterized by the ratio of the L/R and RC constants [33]. This technique, however, is not particularly applicable to current-mode circuits, mainly due to the existence of high-impedance biasing current sources between AC ground and the dominant pole, and it will create mismatch problems (see Section 5.3) if the inductor is placed in series with the current source.

The resistive-compensation technique was introduced in [32] [34] to enhance the bandwidth of current mirrors. The basic current mirror is a single-pole system. The resistive-compensation generates an additional pole and a compensating zero by inserting

Figure 4.2: Resistive compensation technique

a passive resistor between the gates of the input and output transistors, as shown in Fig.4.2. The transfer function is given by

$$\frac{I_o(s)}{I_{in}(s)} = \left(\frac{g_{m2}}{C_{gs2}}\right) \frac{s + \frac{1}{RC_{gs1}}}{s^2 + \frac{C_{gs1} + C_{gs2}}{RC_{qs1}C_{qs2}} + \frac{g_{m1}}{RC_{gs1}C_{qs2}}}.$$

(4.3)

For the compensated current mirror, the frequency response is characterized by the value of resistor R. The effectiveness of compensation is somewhat uncertain due to the inaccurate CMOS resistors. Additionally, as revealed in Section 3.4 that the thermal noise of the added resistor deteriorates the noise performance because its noise is directly referred to the input. For applications such as preamplifiers of data transceivers, noiseless elements that provides comparable bandwidth enhancement are preferred.

## 4.2 Inductor Series-Peaking

#### 4.2.1 Current-Mirror Amplifiers

It is commonly said that the current-mode circuits possess large bandwidth [4] [3]. A main drawback of these circuits is their low current gain. To increase the current gain, the size of the transistor in the output branch of current-mirror amplifiers can be made large, however, at the expense of bandwidth.

Figure 4.3: Current-mirror amplifier with series-peaking inductor  $(J = 0.5 \text{mA}, W_1 = 10 \mu \text{m}, W_2 = 100 \mu \text{m})$

Neglecting the parasitic gate-drain capacitances, the basic current-mirror amplifier shown in Fig. 4.3 (with L = 0) has the first-order transfer function

$$\frac{I_o(s)}{I_{in}(s)} = \left(\frac{g_{m2}}{g_{m1}}\right) \frac{1}{s \frac{C_{gs1} + C_{gs2}}{g_{m1}} + 1},\tag{4.4}$$

with bandwidth

$$\omega_o = \frac{g_{m1}}{C_{gs1} + C_{gs2}},\tag{4.5}$$

where  $g_m$  is the transconductance and  $C_{gs}$  is the gate-source capacitance of transistors. Because the current gain  $k = \frac{(W/L)_2}{(W/L)_1}$  is usually large,  $C_{gs2} \gg C_{gs1}$  and dominates the frequency response. The bandwidth is therefore given by  $\omega_o \approx \frac{g_{m1}}{C_{gs2}}$ . To quantify the bandwidth, the amplifier is implemented in TSMC's  $0.18\mu$ m 1.8V CMOS technology and analyzed using Spectre from Cadence Design Systems with BSIM3V3 device models. Simulation results with the circuit parameters given in Table 4.2 are shown in Fig. 4.11.

Because the dominant pole of CMOS current-mirror amplifiers is attributed to the gate-source capacitance of the output transistor, a compensation inductor L can therefore be placed between the gates of the input and output transistors and is in series with  $C_{gs2}$ , as shown in Fig.4.3. Note that the added inductor has no effect on the DC characteristics. The amplifier has a third-order transfer function

$$\frac{I_o(s)}{I_{in}(s)} = \left(\frac{g_{m2}}{g_{m1}}\right) \frac{1}{s^3 \frac{LC_{gs1}C_{gs2}}{g_{m1}} + s^2 LC_{gs2} + s \frac{C_{gs1} + C_{gs2}}{g_{m1}} + 1}.$$

(4.6)

With the assumption  $C_{gs2} \gg C_{gs1}$ , the transfer function is simplified to

$$\frac{I_o(s)}{I_{in}(s)} \approx \left(\frac{g_{m2}}{g_{m1}}\right) \frac{\frac{1}{LC_{gs2}}}{s^2 + s\frac{1}{g_{m1}L} + \frac{1}{LC_{gs2}}},$$

(4.7)

with the poles given by

$$p_{1,2} = \frac{-1 \pm \sqrt{1 - \frac{4g_{m1}^2 L}{C_{gs2}}}}{2g_{m1}L}.$$

(4.8)

From the control theory, the transfer function of a stable, zeroless, second-order system can be expressed as

$$H(s) = \tilde{H} \frac{{\omega_n}^2}{s^2 + 2\xi \omega_n s + {\omega_n}^2},$$

(4.9)

where  $\tilde{H}$  is the DC gain,  $\omega_0$  is the undamped natural frequency, and  $\xi$  is the damping ratio. Three distinct cases are defined:

- the under-damped case, when  $0 < \xi < 1$ ,

- the critically damped case, when  $\xi = 1$ , and

- the over-damped case, when  $1 < \xi < \infty$ .

| L                               | Table 4.1: Damping characteristics           Poles         Damping characteristics |                   | Response                                                                         |  |

|---------------------------------|------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------|--|

| $L < \frac{C_{gs2}}{4q_{m1}^2}$ | Two distinct                                                                       | Over-damped       | 1) Small bandwidth                                                               |  |

| 5 111                           | negative real<br>poles                                                             |                   | <ol> <li>Large rise time</li> <li>No ringing</li> </ol>                          |  |

| $L = \frac{C_{gs2}}{4g_{m1}^2}$ | Two identical<br>negative real<br>poles                                            | Critically damped | <ol> <li>Large bandwidth</li> <li>Small rise time</li> <li>No ringing</li> </ol> |  |

| $L > \frac{C_{gs2}}{4g_{m1}^2}$ | Complex conjugate<br>poles with<br>negative real part                              | Under-damped      | <ol> <li>Large bandwidth</li> <li>Small rise time</li> <li>Ringing</li> </ol>    |  |

Table 4.1: Damping characteristics

For the current-mirror amplifier, the damping ratio  $\xi = \sqrt{\frac{C_{gs2}}{4g_{m1}^2L}}$ . It is seen that the characteristics of the current-mirror amplifier depend upon the value of the peaking

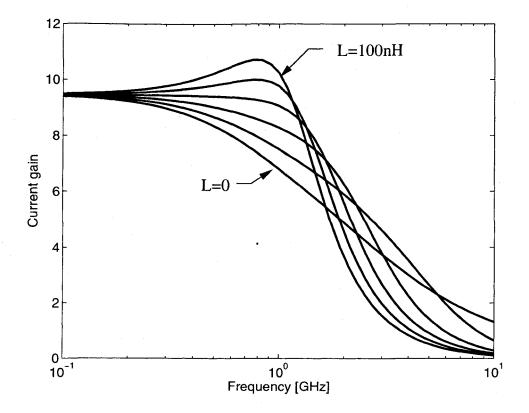

Figure 4.4: The effect of the peaking inductor on the bandwidth of current-mirror amplifier  $(\beta = 0, L \text{ is varied from } 0 \text{ to } 100 \text{ nH with step } 20 \text{ nH})$

inductor, as detailed in Table 4.1. To maximize the bandwidth and avoid ringing in time-domain response, the peaking inductor is sized based on the criterion of the critical damping where

$$L = \frac{C_{gs2}}{4g^2_{m1}L}.$$

(4.10)

The amplifier in this case has the bandwidth of

$$\omega_o = \frac{2g_{m1}}{C_{gs2}},\tag{4.11}$$

It is nearly twice that of the basic current-mirror amplifier. Simulation results with the circuit parameters given in Table 4.2 demonstrate that the inductor series-peaking technique increases the bandwidth of the circuit from 1.6 GHz (L = 0) to 2.7 GHz (L = 60nH), as shown in Fig.4.11. Fig. 4.4 shows the effect of the value of the peaking inductor on the bandwidth of the amplifier. It is seen that the critical damping occurs at  $L\approx 60nH$ .

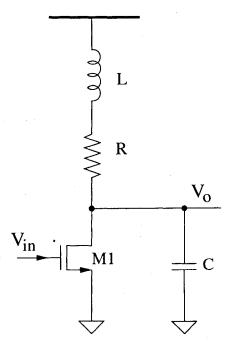

#### 4.2.2 Optical Preamplifiers

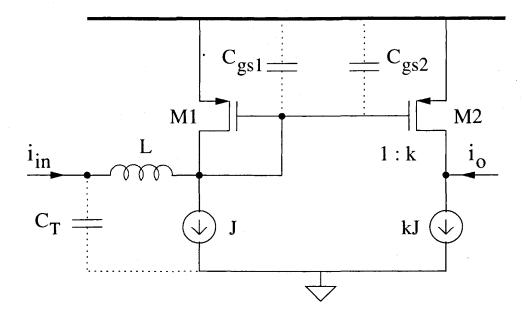

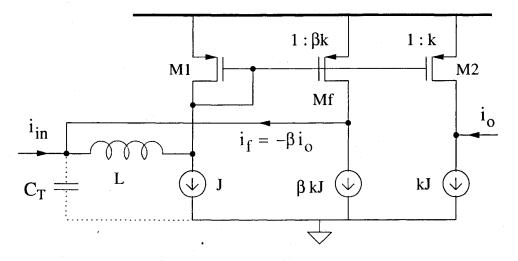

Figure 4.5: Optical preamplifier with series-peaking inductor  $(J = 0.5 \text{mA}, W_1 = 10 \mu \text{m}, W_2 = 100 \mu \text{m}, C_T = 0.5 \text{pF})$

In the preceding analysis, the parasitic input capacitance is neglected and the gatesource capacitance of the output transistor is assumed to constitute the dominant pole. However, in the design of preamplifiers for optical communications, due to the large parasitic capacitance of the photodiode and that of bonding pads of the chip, the input parasitic capacitance is usually much larger than the capacitance of the transistors. Fig. 4.5 shows a primitive current-mode preamplifier for optical communications (L = 0), where  $C_T$  equals the total parasitic capacitance of the photodiode and the packaging. The transfer function of the preamplifier is given by

$$\frac{I_o(s)}{I_{in}(s)} = \left(\frac{g_{m2}}{g_{m1}}\right) \frac{1}{s \frac{C_T + C_{gs}}{g_{m1}} + 1},\tag{4.12}$$

with bandwidth

$$\omega_o = \frac{g_{m1}}{C_T + C_{gs}},\tag{4.13}$$

where  $C_{gs} = C_{gs1} + C_{gs2}$ . Assuming  $C_T \gg C_{gs}$ , the bandwidth is given by  $\omega_o \approx \frac{g_{m1}}{C_T}$ . As shown in Fig. 4.12, the bandwidth of the preamplifier with  $C_T = 0.5$  pF is only 0.45 GHz. To implement the series-peaking technique, the peaking inductor is placed at the input node of the preamplifier, as shown in Fig. 4.5. Both the bond wire inductance and on-chip spiral inductors can be used to realize this inductor. The preamplifier with the peaking inductor has a third-order transfer function

$$\frac{I_o(s)}{I_{in}(s)} = \left(\frac{g_{m2}}{g_{m1}}\right) \frac{1}{s^3 \frac{LC_{gs}C_T}{g_{m1}} + s^2 LC_T + s \frac{C_{gs} + C_T}{g_{m1}} + 1}.$$

(4.14)

With the assumption  $C_T \gg C_{gs}$ , it can be simplified to a second-order function

$$\frac{I_o(s)}{I_{in}(s)} \approx \left(\frac{g_{m2}}{g_{m1}}\right) \frac{\frac{1}{LC_T}}{s^2 + s\frac{1}{g_{m1}L} + \frac{1}{LC_T}},$$

(4.15)

with a pair of poles

$$p_{1,2} = \frac{-1 \pm \sqrt{1 - \frac{4g_{m1}^2 L}{C_T}}}{2g_{m1}L},$$

(4.16)

These equations are similar to those of the current-mirror amplifier with a series peaking inductor. In the critically damped case where

$$L = \frac{C_T}{4g_{m1}^2},\tag{4.17}$$

the circuit has the bandwidth of

$$\omega_o = \frac{2g_{m1}}{C_T},\tag{4.18}$$

which is twice that of the basic preamplifier. Simulation results demonstrate that the inductor series-peaking technique increases the bandwidth of the preamplifier from 0.45 GHz (L = 0) to 1.0 GHz (L = 100 nH), as shown in Fig. 4.12. It should be noted that since the value of bond wire inductance is limited [33], a large on-chip spiral inductor is needed. On-chip inductors are very area consuming. Inductors greater than 100 nH are rarely used in practice [35].

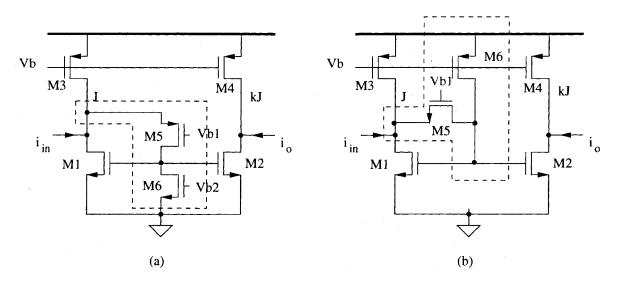

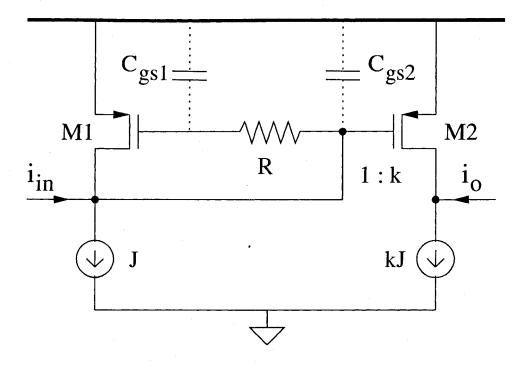

#### 4.3 Negative Current Feedback

It is well known that negative current-current feedback lowers the input impedance, improves the dynamic range, and boosts the bandwidth, however, at the expense of current gain.

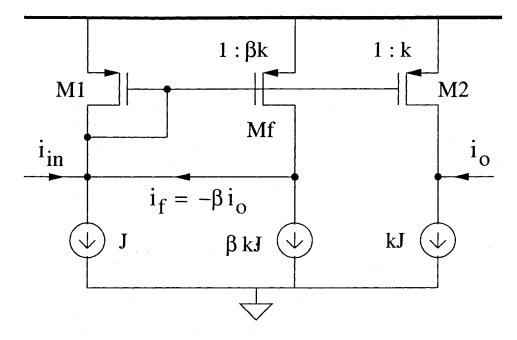

Conventionally, current-current feedback is a series-shunt feedback which means that the feedback current is acquired in series with the output current [26]. As mentioned in Section 3.2, to sample the output current without affecting both the DC biasing condition and the supply voltage, we introduce a new current feedback mechanism shown in Fig. 4.6. In the basic current-mirror amplifier, the feedback transistor  $M_f$  is simply a diodeconnected mirror of the input transistor  $M_1$ . It can be shown that the transfer function is given by

Figure 4.6: Current-mirror amplifier with current feedback  $(J = 0.5 \text{mA}, W_1 = 10 \mu \text{m}, W_2 = 100 \mu \text{m}, W_f = 10 \mu \text{m})$

$$\frac{I_o(s)}{I_{in}(s)} = \left[\frac{g_{m2}}{g_{m1}(1+k\beta)}\right] \frac{1}{s\frac{C_{gs1} + C_{gs2} + C_{gsf}}{g_{m1}(1+k\beta)} + 1},$$

(4.19)

with bandwidth

$$\omega_{o} = \frac{g_{m1}}{C_{gs1} + C_{gs2} + C_{gsf}} (1 + k\beta)$$

$$\approx \frac{g_{m1}}{C_{gs2}} (1 + k\beta)$$

(4.20)

where  $C_{gs2} \gg C_{gs1}$ ,  $C_{gsf}$  was assumed. It is seen that the feedback increases the bandwidth by the factor  $(1 + k\beta)$ . Two notable advantages of this configuration are (i) the feedback gain can be adjusted independent of that of the forward path, and (ii) no increase in the minimum supply voltage, which is given by  $V_T + V_{sat}$ , where  $V_{T,n} = |V_{T,p}| = V_T$  is the threshold voltage and  $V_{sat}$  is the pinch-off voltage. Simulation results with  $\beta = 0.1$ are shown in Fig. 4.11. It is seen that the feedback boosts the bandwidth from 1.6 GHz