### **Ryerson University** Digital Commons @ Ryerson

Theses and dissertations

1-1-2008

## The effect of multi-bit correlation on the design of routing resources in field programmable gate arrays

Ping Chen Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

Chen, Ping, "The effect of multi-bit correlation on the design of routing resources in field programmable gate arrays" (2008). Theses and dissertations. Paper 292.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

## THE EFFECT OF MULTI-BIT CORRELATION ON

## THE DESIGN OF ROUTING RESOURCES IN FIELD PROGRAMMABLE GATE ARRAYS

by

Ping Chen

Bachelor of Applied Science

Beijing University of Aeronautics and Astronautics, 1996

A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Applied Science

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2008

© (Ping Chen) 2008

I hereby declare that I am the sole author of this thesis or dissertation.

I authorize Ryerson University to lend this thesis or dissertation to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis or dissertation by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

# THE EFFECT OF MULTI-BIT CORRELATION ON THE DESIGN OF ROUTING RESOURCES OF FIELD PROGRAMMABLE GATE ARRAY

Master of Applied Science, 2009

Ping Chen

Electrical and Computer Engineering Ryerson University

#### **ABSTRACT**

The large arithmetic-intensive applications increasingly implemented on field-programmable gate arrays (FPGAs) challenge FPGA architects to design FPGAs that can efficiently transport large amount of multi-bit wide signals in the data-path circuits of these applications. In this work, we investigate the area efficiency of two FPGA multi-bit aware routing architectures – the sparse and the enhanced sparse architectures, and compare them with the conventional and the configuration memory sharing architectures. We found that the sparse and enhanced sparse architectures are 6-10% more area efficient than the conventional architecture. Our data also show that while the configuration memory sharing architecture can achieve the highest level of theoretical area savings for multi-bit transportation, it performs poorly for circuits with 50% or less multi-bit signals. These results suggest that FPGA architects should look beyond conventional architectures in order to create more efficient routing architectures for modern FPGAs.

#### **ACKNOWLEDGEMENTS**

Many people have helped and supported me in this long and intense endeavor that took to get here.

I would like to first address my thanks to my family in China. I would like to thank my father, whom I will always give credit for every achievement in my life even though he could not even witness my graduation from high school. I would like to thank my mother, who always offers unconditional help and support to every decision I have made even when the decision was to bring me to the other side of the earth from her. I would like to thank my sister, who is different from me in many ways but has influence on me in all the ways, in a good way.

I would like to express my gratitude to the many helpful suggestions, endless patience and great support from my supervisor, Dr. Andy Ye, who has given me the best career opportunity I've received so far in Canada. He is a bit "difficult" when it comes to writing, a skill I often overlooked in my research, but now when I look back, I really appreciate his push and enjoy the progress I have made.

The two year study in Ryerson would have been much more stressful than it was without my classmates, who shared pressure and happiness with me in the hall way of the engineering building during class breaks or in the subway on our way back home. I would like to thank all my classmates, in particular, Sebastian and Theepan.

I would like to thank my husband, Mark Stoodley, for his company to me during those tiring weekends when I struggled for deadlines in the lab, for the warm meals he prepared for me after I came home after night classes in cold winter nights, for the knowledge he shares with me on programming and research, and for his patience to wait for me to find my direction in this new continent. Running into him is my best luck.

Finally, I would also like to thank my parents in law, whose house is the warmest in Toronto, and my brother in law's family, who are always a lot of fun to stay with. I am grateful and happy to be the person I am today and I would like to thank all the people who make it happen.

## TABLE OF CONTENTS

| CHAPT | TER 1. INTRODUCTION                                               | 1  |

|-------|-------------------------------------------------------------------|----|

| 1.1.  | THESIS MOTIVATION                                                 | 5  |

| 1.2.  | THESIS CONTRIBUTION                                               | 5  |

| 1.3.  | THESIS ORGANIZATION                                               | 5  |

| CHAPT | TER 2. BACKGROUND                                                 | 7  |

| 2.1.  | GENERAL FPGA ARCHITECTURE                                         | 7  |

| 2.1.  | -, -, -, -, -, -, -, -, -, -, -, -, -, -                          |    |

| 2.1.  |                                                                   |    |

| 2.1.  | 3. Common Routing Architecture Structure                          | 10 |

| 2.2.  |                                                                   |    |

| 2.2.  | <b>3</b>                                                          |    |

| 2.2.  |                                                                   |    |

| 2.3.  |                                                                   |    |

| 2.3   |                                                                   |    |

| 2.3   | .2. Routing Resource Modeling in CAD Tool                         | 21 |

| CHAPT | TER 3. THE SPARSE AND ENHANCED SPARSE ARCHITECTURES               | 24 |

| 3.1.  | THE SPARSE ARCHITECTURE                                           | 24 |

| 3.2.  | THE ENHANCED SPARSE ARCHITECTURE                                  | 26 |

| 3.3.  | DESIGN SPACE ANALYSIS                                             | 34 |

|       | FER 4. TRADEOFFS BETWEEN ROUTING SWITCH DENSITY AND               |    |

| ROUT  | ING FLEXIBILITY                                                   | 39 |

| 4.1.  | CIRCUIT ASSUMPTIONS                                               | 39 |

| 4.2.  | ROUTING SWITCH DENSITY COMPARISON                                 | 41 |

| CHAP  | TER 5. ROUTING TOOL SELECTION                                     | 45 |

| CHAP  | ΓER 6. EXPERIMENTAL RESULTS                                       | 53 |

| 6.1.  | EFFECT OF CONFIGURATION MEMORY SHARING ON AREA EFFICIENCY         | 54 |

| 6.2.  | SHIFT AND CONTROL ENHANCED SPARSE ARCHITECTURES VS. CONFIGURATION |    |

| Мем   | ORY SHARING ARCHITECTURE                                          | 59 |

| 6.3.  | MULTI-BIT AWARE VS. CONVENTIONAL ARCHITECTURES                    |    |

| 6.4.  | PERFORMANCE COMPARISON                                            |    |

| CHAP' | ΓER 7. CONCLUSION                                                 | 67 |

| 7.1.  | THESIS SUMMARY                                                    | 67 |

| 7.2.  | SUGGESTIONS TO FUTURE WORK                                        |    |

| REFEI | RENCE                                                             | 71 |

## LIST OF TABLES

| TABLE 3.1 CONNECTION BLOCK DESIGN SPACE                                     | 38  |

|-----------------------------------------------------------------------------|-----|

| TABLE 4.1 SINGLE-BIT AND MULTI-BIT TRACK REDUCTION                          | 43  |

| TABLE 5.1 ROUTING AREA FOR THE SPARSE ARCHITECTURE                          | 45  |

| TABLE 5.2 ROUTING AREA FOR THE CONVENTIONAL ARCHITECTURE                    | 46  |

| TABLE 5.3 COMPARISON OF ROUTING AREA FOR THE CONVENTIONAL ARCHITECTURE      | 51  |

| TABLE 6.1 NOTATIONS FOR ARCHITECTURAL PARAMETERS                            | 53  |

| TABLE 6.2 PARAMETER SETTINGS FOR THE SPARSE AND THE CONFIGURATION MEMORY    |     |

| SHARING ROUTING ARCHITECTURES                                               | 54  |

| TABLE 6.3 PARAMETER SETTINGS FOR THE ENHANCED SPARSE AND THE CONFIGURATION  |     |

| MEMORY SHARING ROUTING ARCHITECTURES                                        | 59  |

| TABLE 6.4 ROUTING AREA VS. % OF MULTI-BIT SIGNALS PER CIRCUIT               | 62  |

| TABLE 6.5 PARAMETER SETTINGS FOR THE CONVENTIONAL, SPARSE, AND              |     |

| CONTROL-ENHANCED SPARSE ARCHITECTURES                                       | 63  |

| TABLE 6.6 ROUTING AREA VS. % OF MULTI-BIT SIGNALS PER CIRCUIT               | 65  |

| TABLE 6.7 ROUTING DELAYS OF 15 BENCHMARKS ROUTED ON THE 4 BEST ARCHITECTURE | s66 |

## LIST OF FIGURES

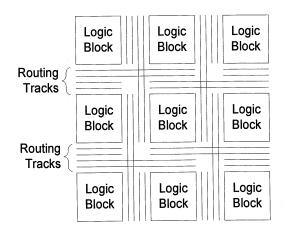

| FIG. 2.1 OVERVIEW OF THE GENERAL FPGA ARCHITECTURE                                        | 8          |

|-------------------------------------------------------------------------------------------|------------|

| FIG. 2.2 2-INPUT LUT (2-LUT)                                                              | 8          |

| FIG. 2.3 A BASIC LOGIC ELEMENT (BLE)                                                      | 9          |

| FIG. 2.4 A 3-INPUT 2-OUTPUT CLUSTER.                                                      | 10         |

| FIG. 2.5 ROUTING SEGMENTS OF LENGTH 2                                                     | 10         |

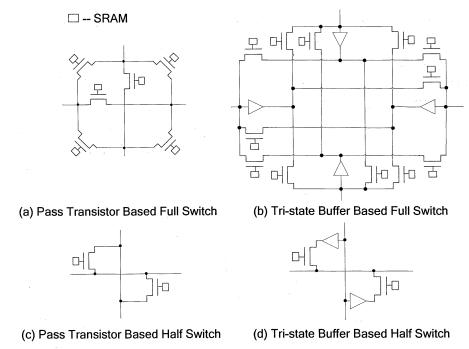

| FIG. 2.6 FULL SWITCHES AND HALF SWITCHES EMPLOYED IN SWITCH BLOCKS                        | 11         |

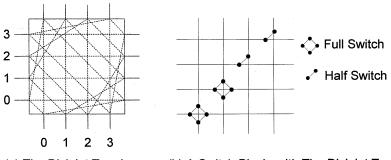

| FIG. 2.7 SWITCH BLOCK                                                                     | 12         |

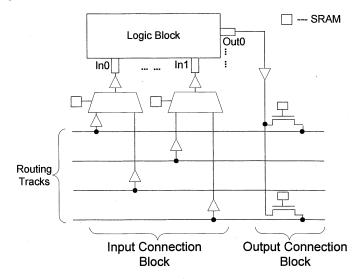

| FIG. 2.8 CONNECTION BLOCK.                                                                | 13         |

| FIG. 2.9. ALGORITHM TO GENERATE SWITCH PATTERNS IN CONNECTION BLOCKS.                     | 14         |

| FIG. 2.10 CONNECTION BLOCKS IN THE CONVENTIONAL ARCHITECTURES                             |            |

| FIG. 2.11 ROUTING RESOURCE GRAPH IN VPR                                                   | 15         |

| Fig. 2.12 FPGA with Configuration Memory Sharing Architecture                             | 16         |

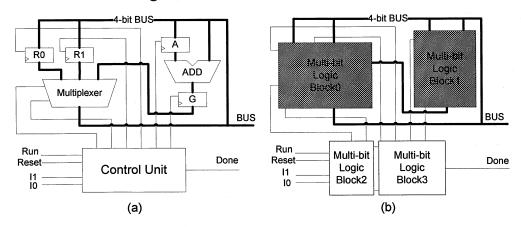

| Fig. 2.13 Map a 4 bit Wide Adder to a Multi-bit Logic Block                               | 17         |

| FIG. 2.14 A SIMPLE 4 BIT WIDE PROCESSOR                                                   | 18         |

| Fig. 2.15 A Processor Mapped Onto an FPGA with Multi-bit aware routing                    | NG         |

| ARCHITECTURE                                                                              | 19         |

| FIG. 2.16 MULTI-BIT SWITCH BLOCK IN THE CONFIGURATION MEMORY SHARING                      |            |

| Architecture                                                                              |            |

| FIG. 2.17 MULTI-BIT CONNECTION BLOCKS                                                     | 20         |

| Fig. 2.18 Connection Block in the Configuration Memory Sharing Archi                      | TECTURE21  |

| FIG. 2.19 ROUTING RESOURCE GRAPH FOR THE CONFIGURATION MEMORY SHARING                     | √G         |

| Architecture                                                                              | 22         |

| Fig. 3.1 Switch block on multi-bit tracks in the sparse architectures $\dots$             | 24         |

| FIG. 3.2 CONNECTION BLOCK IN THE SPARSE ARCHITECTURE                                      | 25         |

| Fig. 3.3 Configuration Memory Sharing Setting in the Architecture Fili                    | E25        |

| Fig. 3.4 Signals Routed in the Connection Blocks in the Sparse Architecture $\frac{1}{2}$ | TURE26     |

| Fig. 3.5 Signals Routed in the Connection Blocks in the Sparse Architecture $\frac{1}{2}$ | TURE WITH  |

| EXTRA ROUTING SWITCHES                                                                    | 27         |

| Fig. 3.6 The Enhanced Sparse Switch Patterns Investigated in the Resea                    | RCH28      |

| Fig. 3.7. The Algorithm Adding the Control Patterns to the Sparse Swit                    | CH PATTERN |

|                                                                                           | 29         |

| Fig. 3.8 The Control Enhanced Sparse Switch Patterns Described in an                      |            |

| ARCHITECTURE FILE                                                                         | 31         |

| FIG. 3.9 AN ENHANCED SPARSE SWITCH PATTERN                                                | 32         |

| FIG. 3.10 MERGED SWITCH PATTERNS                                                                      | 32  |

|-------------------------------------------------------------------------------------------------------|-----|

| FIG. 3.11 ROUTING RESOURCE GRAPH FOR THE ENHANCED SPARSE ARCHITECTURE                                 | 33  |

| FIG. 3.12 SWITCH PATTERNS GENERATED BY VPR                                                            | 34  |

| Fig. 3.13 Switch Patterns in The Configuration Memory Sharing Routing                                 |     |

| Architecture                                                                                          | 35  |

| FIG. 3.14 SWITCH PATTERNS IN THE CONTROL ENHANCED SPARSE ARCHITECTURE                                 | 36  |

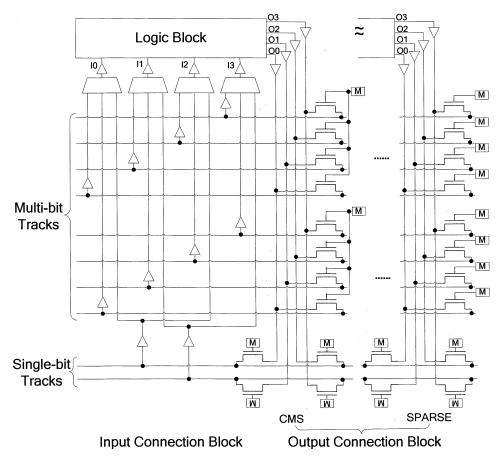

| FIG. 4.1 INPUT AND OUTPUT CONNECTION BLOCKS IN THE CONFIGURATION MEMORY SHARE                         | ING |

| AND SPARSE ARCHITECTURES                                                                              | 40  |

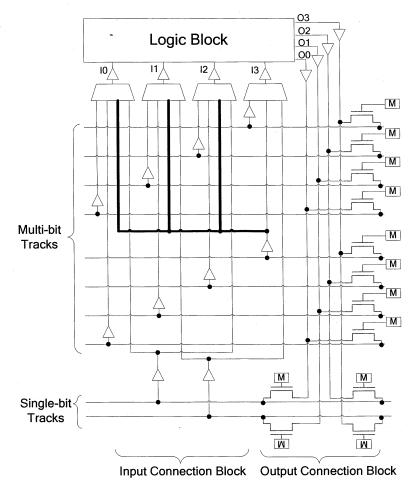

| FIG. 4.2 INPUT AND OUTPUT CONNECTION BLOCK IN THE ENHANCED SPARSE ARCHITECTUR                         | æ41 |

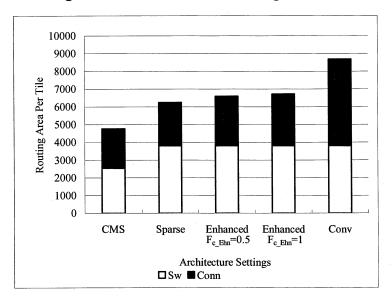

| Fig. 4.3 Routing Area Per Tile In Min Width Trans When $F_{c\_\text{IN}}/F_{c\_\text{out}}$ =0.4/0.25 | 42  |

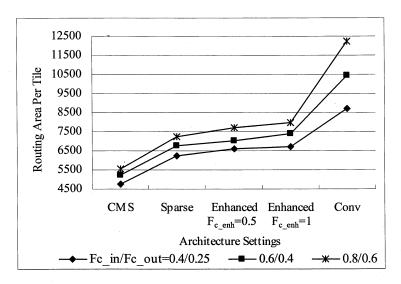

| Fig. 4.4 Routing Area per Tile in Minimum Width Transistors                                           | 43  |

| Fig. 5.1 A Routing Iteration in the Conventional Routing Tool                                         |     |

| Fig. 5.2 A Routing Iteration in the Multi-bit Aware Routing Tool                                      |     |

| Fig. 5.3 Experiment 1: Change the Routing Sequence in the Conventional Routing                        | 3   |

| Tool                                                                                                  | 49  |

| FIG. 5.4 EXPERIMENT 2: CHANGE THE WAY OF RIPPING UP NETS IN THE MULTI-BIT AWARE                       |     |

| ROUTING TOOL                                                                                          | 50  |

| Fig. 6.1 Number of Single-Bit and Multi-Bit Routing Tracks in the Configuration                       | N   |

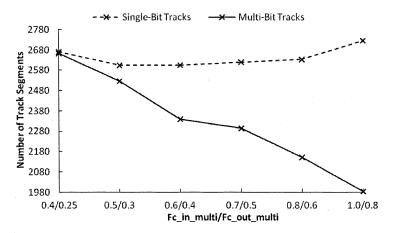

| MEMORY SHARING ROUTING ARCHITECTURE                                                                   | 55  |

| FIG. 6.2 NUMBER OF SINGLE-BIT AND MULTI-BIT ROUTING TRACKS IN THE SPARSE                              |     |

| ARCHITECTURE                                                                                          | 55  |

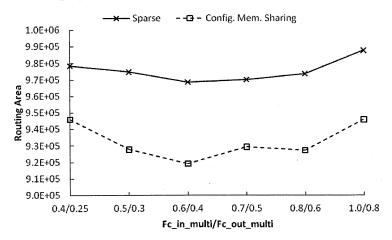

| FIG. 6.3 ROUTING AREA FOR SPARSE AND CONFIGURATION MEMORY SHARING ROUTING                             |     |

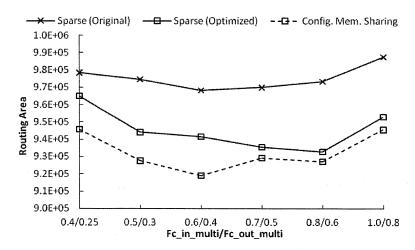

| Architectures                                                                                         | 56  |

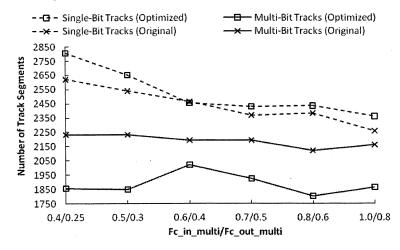

| FIG. 6.4 MULTI-BIT TRACK REDUCTION DUE TO ROUTING ALGORITHM OPTIMIZATION                              | 56  |

| Fig. 6.5 Reduction in Routing Area for the Sparse Architecture Due to Routing                         |     |

| ALGORITHM OPTIMIZATION                                                                                | 57  |

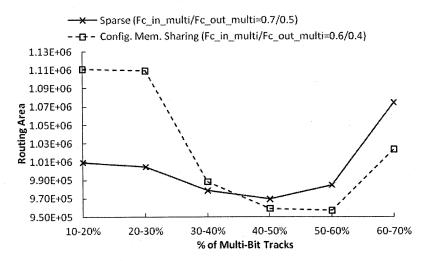

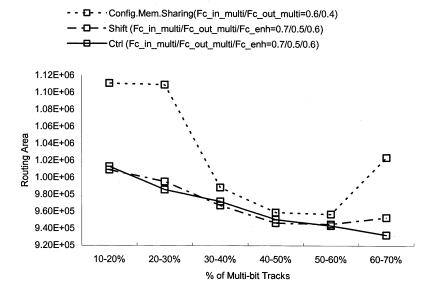

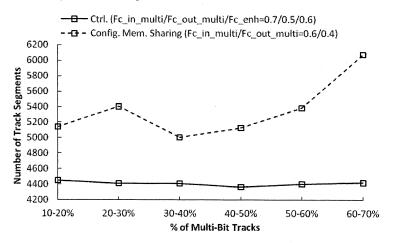

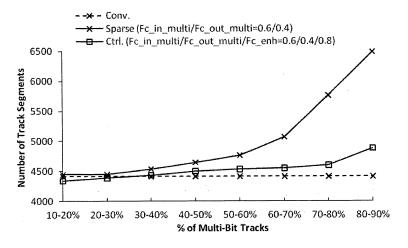

| FIG. 6.6 ROUTING AREA VS. % OF MULTI-BIT TRACKS                                                       | 58  |

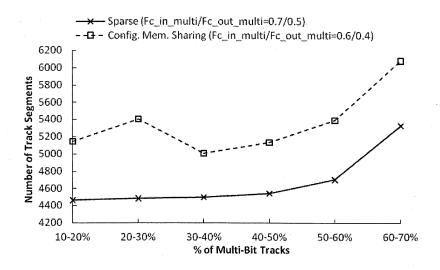

| FIG. 6.7 TRACK SEGMENTS VS. % OF MULTI-BIT TRACKS                                                     | 59  |

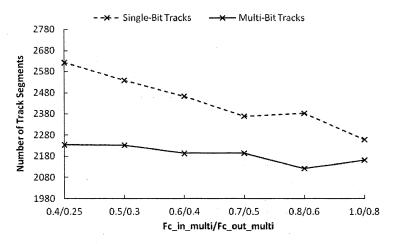

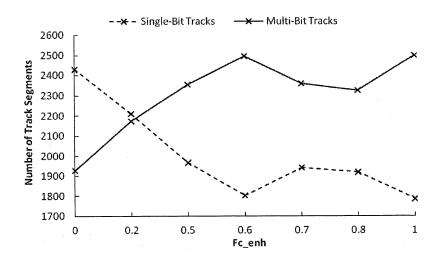

| Fig. 6.8 Number of Single-Bit and Multi-Bit Routing Tracks in the                                     |     |

| CONTROL-ENHANCED SPARSE ARCHITECTURE                                                                  | 60  |

| FIG. 6.9 ROUTING AREA VS. % OF MULTI-BIT TRACKS                                                       | 61  |

| FIG. 6.10 TRACK SEGMENTS VS. % OF MULTI-BIT TRACKS                                                    | 61  |

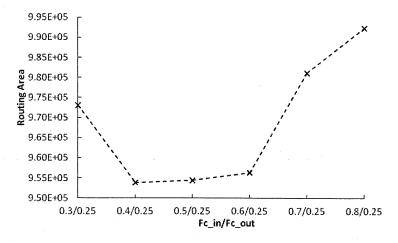

| Fig. 6.11 Most Area Efficient $F_{c\_IN}$ Values for the Conventional architecture                    | 63  |

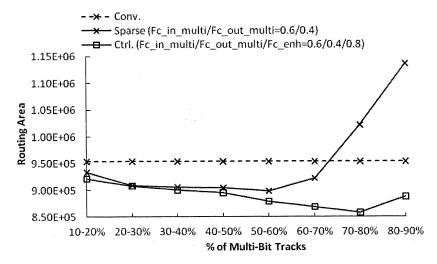

| FIG. 6.12 ROUTING AREA VS. % OF MULTI-BIT TRACKS                                                      | 64  |

| FIG. 6.13 TRACK SEGMENTS VS. % OF MULTI-BIT TRACKS                                                    | 64  |

#### **CHAPTER 1**

#### INTRODUCTION

Field programmable gate arrays (FPGAs) are integrated circuits that can be programmed to implement virtually any digital circuit. FPGAs were developed from mask-programmable gate arrays (MPGAs). MPGAs, however, are programmed using integrated circuit fabrication to form metal interconnections. FPGAs, on the other hand, are programmed via electrically programmable switches. FPGAs are similar to the traditional programmable logic devices (PLDs) but can achieve much higher level of integration than PLDs [1].

Over the years, FPGAs have developed rapidly to programmable logic devices that can accommodate more than a half million logic elements and tens of millions of memory bits. These devices can be clocked at over 600MHz to perform high speed tasks [2][3].

FPGAs are optimized for implementing digital hardware algorithms and have the added advantage of being able to change their functionalities in a fraction of second. Being both hardware-oriented and programmable, FPGAs provide a unique blend of performance and flexibility, which has proven essential in many applications. The programmability of FPGAs, however, has made their design particularly challenging. Typically, only 25% of FPGA area is actually used to perform computation while the remaining 75% is used for the *routing resources* which connect the computing elements together [1]. Due to their vast area consumption, the design of the routing resources is as important as the design of the computing elements.

As the logic capacity of FPGAs increases, more and more arithmetic-intensive applications are implemented on FPGAs. Consequently, there has been a corresponding increase in the variety of FPGA computing elements. From a mere collection of logic blocks, FPGAs now can include digital signal processors, multipliers, multi-bit addressable memory cells, and even processor cores [2][3]. One of the common characteristics of these new computing elements is their multi-bit design, where each element is designed to process several bits of data at a time.

While the input and output pins of a conventional logic block carry independent bits of information, the input and output pins of a multi-bit processing element are logically organized to represent multiple-bit wide data. In this organization, pins that represent a datum are often used at the same time. Similarly, routing resources are routinely used to transport multiple-bit wide data from a common source to a common destination.

To transport a multiple-bit wide datum (a *multi-bit signal*), one can either treat the datum as a set of independent signals (*single-bit signals*) and transport these signals individually through conventional routing resources, or view the entire datum as a single coherent unit and transport the unit collectively through a set of specialized routing resources.

Conventional routing tools treat signals independently and route them individually. In this thesis, we call routing architectures associated with the conventional routing tools as the *conventional architecture* and the routing tracks in these architectures the *single-bit routing tracks*. The conventional routing tools can be represented by the Versatile Place and Route (*VPR*) tool [4], a successful FPGA CAD tool widely used in academia. VPR assumes a routing architecture that distributes switches from logic block I/O pins to routing tracks as uniformly as possible such that each I/O pin has an equal chance to connect to any of the routing tracks. Consequently, a multi-bit signal is often broken into a sequence of single-bit signals – the correlation among these signals is ignored and the regularity of the multi-bit signal is destroyed.

To preserve the regularity of multi-bit signals, we can transport a multi-bit signal as a single unit on a set of specialized routing tracks. We call the specialized routing tracks *multi-bit routing tracks*. The routing architectures containing multi-bit tracks are called *multi-bit aware routing architectures*. The multi-bit tracks and logic block I/O pins are all grouped into buses. Within a bus, each routing track or a logic block I/O pin is assigned to a unique bit position. An I/O pin can only be connected to multi-bit tracks that are at the same bit position and vice versa. Compared to the routing tracks in the conventional architecture, a multi-bit track can connect to fewer logic block I/O pins. This reduced connectivity results in sparser switch patterns which consume less active area. At the same time, sparser switches also lower the flexibility of the routing tracks. As a result, more tracks might be needed to route a particular circuit. Therefore, the area efficiency of

multi-bit aware routing architectures compared to conventional architectures depends on the tradeoff between the sparseness of the routing switches and the utilization of the routing tracks. Investigation into the sparser switch pattern design may lead to more area efficient FPGA routing architectures, but we are not aware of any previous work in this direction.

Even though the commercially available general purpose FPGAs have included data-path oriented features such as processors and multipliers, these features are mainly aimed at improving the performance of specific arithmetic functions through heterogeneous architectures. Recent research on commercial FPGAs center on improving the performance or lowering the power consumption of FPGAs through more advanced logic block and routing circuitry design [5][6][7]. The routing architectures in that research, however, are still based on the conventional routing architectures. We are not aware of any industrial research to investigate either multi-bit aware routing architectures or the design of automated CAD tools that can capture and maintain data-path regularity.

Many academic researchers have studied data-path oriented field programmable architectures, which are typically designed for arithmetic-intensive applications. These studies, however, either have not empirically reported on the area efficiency of the routing architectures or have focused on substantially different logic and routing architectures from those found in conventional FPGAs. The field programmable architectures investigated in previous research can be classified into 4 classes: 1) processor-based architectures; 2) static Arithmetic Logic Unit (ALU)-based architectures; 3) dynamic ALU-based architectures, and 4) Look Up Table (LUT)-based architectures. Examples of the processor-based architectures include PADDI-1[8], PADDI-2 [9], RAW machine [10], and REMARC [11] architectures. Instead of processors, the static ALU-based architectures are built on arrays of arithmetic logic units. This class of architectures can be represented by Colt [12], DreAM [13], and PipeRench [14] architectures. Unlike the static ALU-based architectures, which can be only configured by configuration memory bits, the dynamic ALU-based architectures can also be configured by the data from the computation process in the architectures. Several dynamic ALU-based architectures are the RaPiD [15], MATRIX [16], and Chess [17] architectures.

The above 3 classes of architectures are constructed from arrays of processors or ALUs, which are considerably more complex than the conventional LUT-based logic blocks and therefore have very different routing demands and routing resources. This difference limits the researches on these architectures from benefiting from the current work on FPGA routing architectures. The fourth class of the architectures - the LUT-based architectures such as Garp [18], the mixed-grain FPGA [19], and DP-FPGA [20][21] architectures – is the closest to conventional FPGA architectures. In the Garp architecture, however, the track segments remain unconnected to each other instead of being connected through routing switches as in the conventional architectures. This feature severely limits the possible applications of this architecture. The mixed-grain FPGA architecture study defined the basics of its routing architecture, which is closer to conventional architectures than the Garp architecture, but this work didn't measure the area efficiency by actually placing and routing benchmark circuits on the architecture. Like the mixed-grain FPGA architecture, the DP-FPGA architecture study did not empirically report on the area efficiency of its routing architecture. In fact, this work did not define a complete set of its building blocks, so there is not yet a CAD flow for the DP-FPGA architecture.

Based on the DP-FPGA architecture, the work in [22] developed the MB-FPGA architecture. This work carefully defined the detailed routing architecture for the MB-FPGA architecture, and has designed a full CAD flow for the architecture. This work also routed a set of benchmark circuits on the MB-FPGA architectures and found 8% routing area saving over the conventional routing architectures. The MB-FPGA routing architecture is multi-bit aware routing architectures and has multi-bit tracks that can be grouped together for multi-bit transportation. The routing architecture, however, has configuration memory sharing among the switches within a bus, so the effect of the switch pattern design was mixed together with the effect of configuration memory sharing. From the experimental results of this work, therefore, we can not decide how much of the area savings can be attributed to the sparser switch pattern design on the multi-bit tracks and how much is from sharing configuration memory.

#### 1.1. Thesis Objectives

The motivation of this thesis is to investigate the sparser switch patterns independently. In this research, we first separate the sparser switch patterns from configuration memory sharing to generate a new routing architecture called the *sparse architecture*, and then we improve upon this routing architecture to produce the *enhanced sparse architecture*. The goal of this work is to look beyond the conventional architectures and search for more area efficient FPGA routing architectures that can be used to implement data-path oriented applications.

#### 1.2. Thesis Contribution

This thesis evaluates two new FPGA multi-bit aware routing architectures: the sparse and the enhanced sparse architectures. The research on these two routing architectures greatly expands the FPGA routing architecture design space previously explored by the conventional architecture. Our thesis shows that the conventional architecture only explored a very small fraction of the total design space.

In the research, we routed a set of benchmark circuits on these two new routing architectures and measured their area efficiency, track counts, and performance. We found that the sparse and the enhanced sparse architectures are more area efficient than the conventional architecture with only a slight increase in track count, and are as area efficient as the configuration memory sharing architecture with significant decrease in track count. We also found that the performance of these two new architectures is as good as that of the conventional and the configuration memory sharing architectures.

#### 1.3. Thesis Organization

The thesis is organized as follows. The general FPGA architecture and the two existing routing architectures – the conventional and the configuration memory sharing architectures will be described in Chapter 2. The two new routing architectures that this research targets – the sparse and the enhanced sparse architectures – are introduced in Chapter 3. To understand the tradeoffs between the routing density and the routing flexibility in these routing architectures, Chapter 4 then compares the routing resource density of all four routing architectures and estimates the routing flexibility required by

the sparse and the enhanced sparse architectures to maintain their area efficiency. Before we experimentally evaluate the area efficiency of these two routing architectures, we select, in Chapter 5, the routing tools for the evaluation. Chapter 6 presents the results of our evaluation. Finally, in Chapter 7, we summarize the thesis and propose future work.

#### **CHAPTER 2**

#### **BACKGROUND**

In this chapter, we describe the background material for the remainder of the thesis. Section 2.1 introduces the general FPGA architecture, including the structure of logic blocks and the routing architecture. We will then review two earlier routing architectures in Sections 2.2 and 2.3, respectively: 1) the conventional architecture generated by the VPR tool, and 2) the configuration memory sharing architecture. The first routing architecture acts as a baseline in our research, while the second one is the building block of the new routing architectures described later in this thesis.

#### 2.1. General FPGA Architecture

FPGA's programmability can be realized through various programming technologies such as: anti-fuses, erasable programmable read-only memories (EPROMs) and *static* random access memories (SRAMs). The FPGA logic blocks can be built on one or more of the followings: transistor pairs, basic gates, wide fan-in AND-OR structures, multiplexers and *Look Up Tables* (LUTs) [1]. SRAM based FPGAs whose logic blocks are built on LUTs are the main stream in the current FPGA market, and also the focus of our research. In this section, we will introduce the architecture of these FPGAs.

#### 2.1.1. Overview of the General FPGA architecture

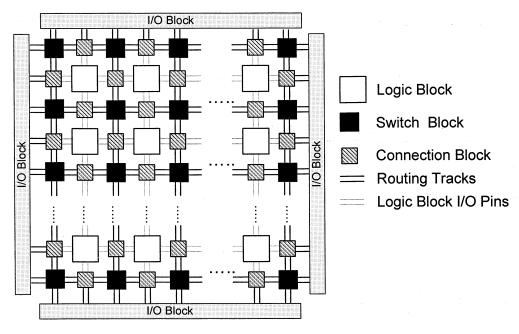

The general architecture of an FPGA is shown in Fig. 2.1. The *logic blocks* are the basic programmable computing elements in an FPGA. The input or output pins of the logic blocks are connected to the routing tracks through the *connection blocks* and the routing tracks are connected together through the *switch blocks*. The switch and the connection blocks are the two building blocks for the FPGA *routing architecture*. The I/O blocks exchange signals between the FPGA and external circuits. Since the remainder of the thesis does not deal with the I/O blocks, we do not describe them in detail here. In the remaining part of this section, we will give further details on the structures of the logic blocks and the routing architecture.

Fig. 2.1 Overview of the General FPGA Architecture

#### 2.1.2. Common Logic Block Structures.

The logic blocks are based on Look Up Tables (LUT). A LUT, paired with a register forms a *Basic Logic Element* (BLE). Several BLEs are then connected together to become a cluster. Finally, one or several clusters form a logic block. In this section, we will introduce the structure of the logic block in details, starting from its basic building blocks – LUTs.

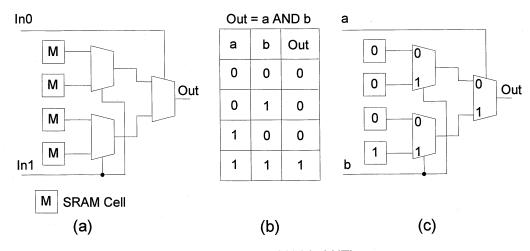

Fig. 2.2 2-Input LUT (2-LUT)

LUTs are combinational circuits consisting of K inputs, a set of multiplexers and SRAMs, through which LUTs can be programmed to realize any K input combinational

logic functions. An example of a 2-input LUT (2-LUT) is shown in Fig. 2.2. The structure of the LUT is illustrated in Fig. 2.2 (a) while Fig. 2.2 (b) and (c) show how the LUT works as an AND gate. To map a 2-input AND gate to a 2-LUT, we need to store all possible outputs of the AND gate in the SRAM cells of the 2-LUT. These outputs are shown in the  $3^{rd}$  column of the truth table shown in Fig. 2.2 (b). Correspondingly, the binary values "0 0 0 1" are stored in the SRAM cells of the 2-LUT as shown in Fig. 2.2 (c). In Fig. 2.2 (c), the digit "0" or "1" on each input line of multiplexers denotes the value of the selection signal that is needed for the corresponding input line to be selected to be the multiplexer output. For example, if the selection signal a is 1 and the selection signal b is 0, the lower input to the multiplexer in the second stage and the upper input to the multiplexer in the first stage are selected. As a result, the stored content in the  $3^{rd}$  SRAM is delivered to the output of the 2-LUT. This output matches the output in the  $4^{th}$  row of the truth table shown in Fig. 2.2 (b). The remaining 3 cases in the truth table can be verified in the same way.

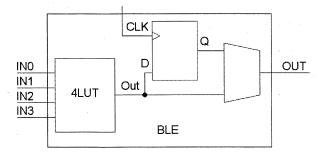

Fig. 2.3 A Basic Logic Element (BLE)

LUTs are the major programmable resources in FPGA logic blocks. A LUT is often paired with a sequential circuit to form a higher level logic unit. In a typical FPGA, a LUT and a register are wired together to form a Basic Logic Element (BLE) as shown in Fig. 2.3. In the figure, 4 BLE inputs are directly connected to a 4-input LUT and the output of the BLE can either be connected to the registered version of the 4-LUT output or be directly connected to the output of the 4-LUT.

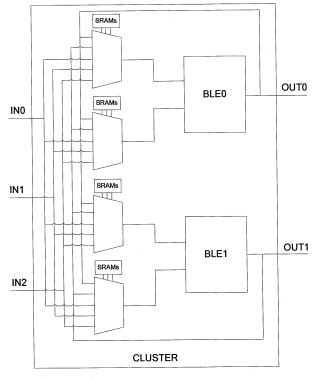

Several BLEs are then connected by a set of local routing resources to form a cluster. Fig. 2.4 shows a cluster with 3 inputs and 2 outputs. This cluster has two 2-input BLEs whose inputs can be connected to any of the inputs or outputs of the cluster through a set of multiplexers controlled by SRAM cells. These inputs to the cluster are therefore

logically equivalent and so are the outputs.

Fig. 2.4 A 3-Input 2-Output Cluster.

The conventional FPGAs assume that each cluster directly forms a logic block. The data-path oriented FPGAs, on the other hand, group a set of clusters into a logic block.

#### 2.1.3. Common Routing Architecture Structure

Fig. 2.5 Routing Segments of Length 2

The logic blocks are connected through programmable routing resources in an FPGA. FPGA routing resources include routing tracks and programmable routing switches, which are grouped into the switch and connection blocks.

The routing tracks are organized into *routing channels*, which run both horizontally and vertically between the logic blocks. A routing track is broken into *track segments*. A track segment with length N spans N logic blocks. Fig. 2.5 shows a simplified routing architecture with 2 horizontal and 2 vertical routing channels with the track segment length of 2. The track segments are connected together through switch blocks and to the logic block I/O pins through connection blocks. In the remainder of this section, we describe the structure of the switch blocks and the connection blocks respectively.

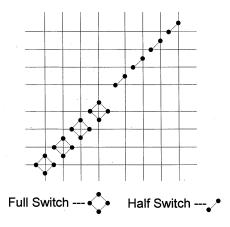

Fig. 2.6 Full Switches and Half Switches Employed in Switch Blocks

Fig. 2.6 shows two types of switches that are employed in a switch block – the full and the half switch. A full switch connects 2 horizontal routing track segments with 2 vertical routing track segments. The switch can be constructed out of pass transistors or tri-state buffers as shown in Fig. 2.6 (a) and (b). A half switch connects two perpendicular routing tracks that continue through a switch block. A pass transistor based half switch is illustrated in Fig. 2.6 (c) and a buffer based half switch is shown in Fig. 2.6 (d).

Using the full and half switches, a switch in a switch block connects an incoming track to a set of outgoing tracks. The topology of switch blocks decides the exact set of outgoing tracks that an incoming track can connect to. Among several common topologies used for switch blocks [23] [24] [25], we will describe the *disjoint topology* in

detail since the topology was shown to be one of the most efficient and is used in many studies on the conventional architecture [4] [23] [26] and the configuration memory sharing architecture [27].

(a) The Disjoint Topology

(b) A Switch Block with The Disjoint Topology

Fig. 2.7 Switch Block

Fig. 2.7 (a) shows the connections in a switch block that employs the disjoint topology. In this figure, a dashed line represents a connection between two track segments. An incoming track in the switch block is always connected to 3 outgoing tracks of the same index. For example, as shown in Fig. 2.7 (a), the horizontal track at index 1 entering the switch block from the left can connect to 1) the vertical track at index 1 leaving the switch block from the top, 2) the horizontal track at index 1 leaving the switch block from the bottom. Fig. 2.7 (b) shows actual construction of a switch block with the disjoint topology. The switch block connects two perpendicular channels that contain 4 tracks each. Two of these 4 tracks continue through the switch block while the other two end. To connect the ending tracks, we need two full switches shown in Fig. 2.6 (a) or (b). To connect the continuing tracks, two half switches shown in Fig. 2.6 (c) or (d) are used instead.

The other types of building blocks for the FPGA routing architecture are the connection blocks, which are used to connect either the routing tracks to the logic input pins (the *input connection blocks*), or the logic output pins to the routing tracks (the *output connection blocks*). The input connection blocks are built from multiplexers while output connection blocks are built from tri-state buffers. Fig. 2.8 shows a simple example of an input connection block and an output connection block. In the input connection block, the SRAMs connected to the select inputs of the multiplexers select the routing

track to be connected to a logic block input. In the output connection block, the SRAM cell on the base of a pass transistor turns on the pass transistor to connect a logic block output to a routing track.

Fig. 2.8 Connection Block.

More details about the connection and the switch block design will be described in the next two sections where we introduce the two routing architectures studied in previous research: the conventional and the configuration memory sharing architectures.

#### 2.2. Conventional Architectures

In the section, the conventional architecture generated by VPR is introduced. We will first describe the structure of the routing architecture, and then explain how the architecture is modeled in VPR.

#### 2.2.1. Structure of the Conventional Architecture

Similar to the general routing architecture introduced in Section 2.1.3, the building blocks of the conventional routing architecture are the switch blocks and the connection blocks. The switch blocks utilized by VPR are tri-state buffer based and employ the disjoint topology. The design of the switch blocks are described in Section 2.1.3.

The connection blocks are more complex than the switch blocks. The switch patterns in the connection blocks are generated by the algorithm shown in Fig. 2.9. In this figure,  $F_c$  is the fraction of routing tracks per channel that can be connected to a logic block input

or output (I/O) pin, P is the number of logic block I/O pins, and W is the number of routing tracks per channel. The algorithm generates a switch pattern matrix containing the index of a routing track that the jth connection of the ith logic block I/O pin connects to.

```

IF logic block I/O pins are output pins THEN

C = ceil (Fc * W)

ENDIF

IF logic block I/O pins are input pins THEN

C = floor (Fc * W)

ENDIF

step = W / P / C

increment = W / C

FOR (i = 0; i < P; i++)

FOR (j = 0; j < C; j++)

switch_pattern[i][j] = floor(step * i + increment * j)

ENDFOR

ENDFOR

```

Fig. 2.9. Algorithm to Generate Switch Patterns in Connection Blocks

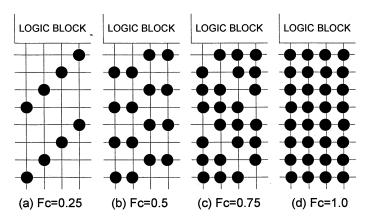

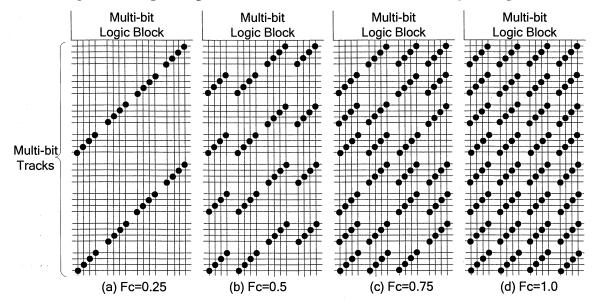

Fig. 2.10 shows 4 examples of the connection blocks that can be generated by the algorithm with varying  $F_c$  values. In the figure, a dot represents a switch in the connection blocks. A vertical line is a logic block I/O pin and a horizontal line is a routing track. There are a total of 4 I/O pins and 8 routing tracks in each of the switch patterns shown in the figure. When  $F_c$  is 0.25 as shown in Fig. 2.10 (a), two of the 8 tracks are connected to each logic block I/O pin via routing switches. When  $F_c$  is 1.0 as shown in Fig. 2.10 (d), all the tracks are connected to each logic block I/O pin.

$F_c$ , and P are described in the *architecture file* [28] and W can be either specified by a command line parameter input to VPR or decided by the routing process in VPR according to routing requirements. VPR generates the specified FPGA architecture according to the command line parameters and the architecture file.

Fig. 2.10 Connection Blocks in The Conventional architectures

#### 2.2.2. Routing Resource Modeling in VPR

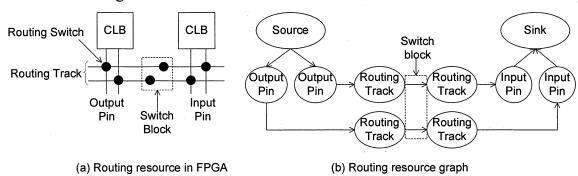

Routing resources in the conventional architecture include *sources*, *sinks*, input or output pins of logic blocks, routing tracks and routing switches. All output pins from a logic block are logically equivalent and originate from a common source. Similarly, all the input pins to a logic block are also logically equivalent and terminate to a common sink.

Routing resources in VPR are modeled as a directed graph called the *routing* resource graph, or rr-graph [4]. In an rr-graph, the nodes are used to represent sources, sinks, logic block I/O pins and routing tracks. Routing switches that connect logic block I/O pins to routing tracks or routing tracks together are modeled as edges in the rr-graph.

To generate an rr-graph, VPR first generates a switch pattern using the algorithm shown in Fig. 2.9. VPR then converts the pattern along with the assigned switch block topology into connections between the nodes of the graph. During the conversion, the specific circuit level details such as the buffer or pass-transistor based switches are also modeled according to the architecture file.

Fig. 2.11 Routing Resource Graph in VPR

Fig. 2.11 shows an example of the routing resource graph. The routing resources shown in Fig. 2.11 (a) are represented by the routing resource graph shown in Fig. 2.11 (b). In this figure, all the routing resources except routing switches are modeled as nodes that are represented by white circles, and the connection between two nodes is modeled as a directed edge.

#### 2.3. Configuration Memory Sharing Architecture

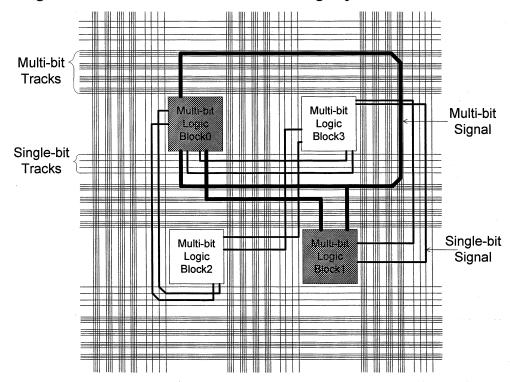

Fig. 2.12 FPGA with Configuration Memory Sharing Architecture

Another routing architecture we will describe in details is the configuration memory sharing architecture. This architecture is one of the multi-bit aware routing architectures, which are designed to take advantage of the large amount of multi-bit wide signals existing in data-path oriented applications. Most of the earlier studies on data-path oriented FPGAs have focused on the design of logic blocks [20][21]. The work in [22][27]

[29] investigated the design of the multi-bit aware routing architectures. This work, however, focused primarily on the configuration memory sharing aspect of the multi-bit aware routing architecture designs. In this section, we briefly review the configuration memory sharing architecture studied in his work because it forms the basis of this thesis.

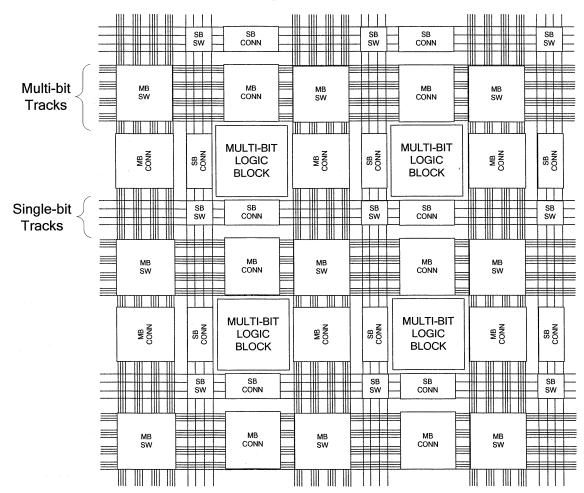

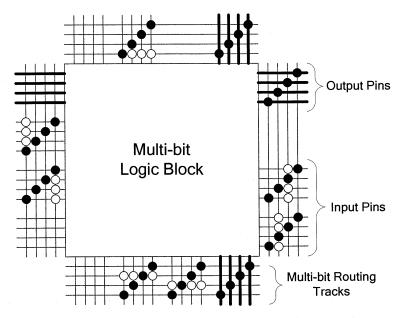

#### 2.3.1. FPGA with Configuration Memory Sharing Architecture

Fig. 2.13 Map a 4 bit Wide Adder to a Multi-bit Logic Block

Fig. 2.12 shows an FPGA with the configuration memory sharing architecture. The FPGA is constructed out of *multi-bit* logic blocks. These blocks are connected by two types of routing tracks – the single-bit and the multi-bit tracks. A set of single-bit tracks can be connected either to another set of single-bit tracks by a *single-bit switch block* (SBSW) or to a set of logic block I/O pins by a *single-bit connection block* (SBCONN). One major new feature of this routing architecture is the addition of multi-bit routing tracks specialized for transporting multi-bit signals. The multi-bit routing tracks are grouped into *routing buses*. A routing bus can be connected either to another routing bus by a *multi-bit switch block* (MBSW) or to a set of logic block I/O pins by a *multi-bit*

#### connection block (MBCONN).

In the remainder of the section, we will describe each of the building blocks – the multi-bit logic blocks, the switch blocks and the connection blocks. The switch blocks include both multi-bit and single-bit ones and so do the connection blocks.

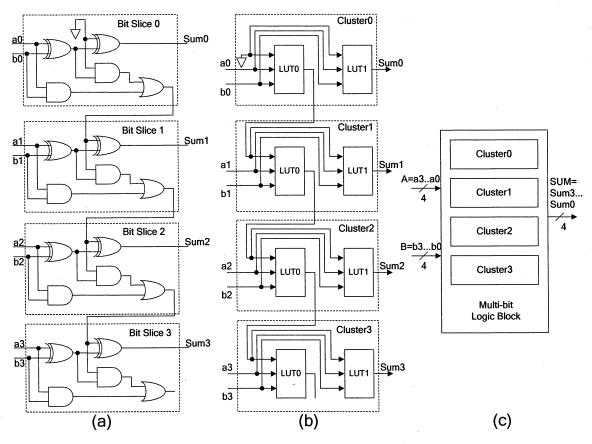

Fig. 2.14 A Simple 4 bit Wide Processor

Each multi-bit logic block contains *M* identical clusters and is designed to handle an *M*-bit computation. Fig. 2.13 shows an example of 4-bit adder mapped to a 4-bit wide multi-bit logic block. Fig. 2.13 (a) shows each individual bit slice of the 4-bit adder. Each of these slices can be implemented in a cluster as shown in Fig. 2.13 (b). Four of the clusters are grouped into a 4-bit wide multi-bit logic block that can perform a 4-bit addition as shown in Fig. 2.13 (c). In the 4-bit wide multi-bit logic block, every 4 input or output pins are grouped into an *input bus* or an *output bus*. In the example shown in Fig. 2.13 (c), there are two input buses used to input two 4-bit wide datum, A and B, to the adder and an output bus to output a 4-bit wide result, SUM, from the adder.

The multi-bit logic blocks are connected through both of the single-bit and multi-bit tracks. The multi-bit tracks are specialized for transporting multi-bit signals in data-path applications while single-bit tracks are specialized for single-bit signals. As an example, Fig. 2.14 shows a simple 4-bit wide processor. The data-path of the processor is shown in Fig. 2.14 (a). It contains an adder, a multiplexer, and several 4-bit wide buses. Besides the data-path, the processor also includes a control circuit. The control circuit sends out single-bit control signals to the data-path based on external commands. To map the processor onto an FPGA, we first mapped the processor into a set of multi-bit logic blocks as shown in Fig. 2.14 (b). These multi-bit logic blocks are then mapped onto a

4-bit wide FPGA with the configuration memory sharing architecture as shown in Fig. 2.15. In the example, the single-bit signals are routed on single-bit tracks while the multi-bit signals are routed on multi-bit tracks that are grouped into 4-bit wide buses.

Fig. 2.15 A Processor Mapped Onto an FPGA with Multi-bit aware routing architecture

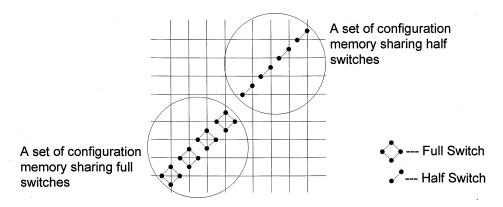

The multi-bit and single-bit tracks are connected together via the multi-bit and the single-bit switch blocks respectively. The single-bit switch blocks employ the same switch block design as described in section 2.2. The multi-bit switch blocks, on the other hand, is constructed out of a set of full and half switches that share configuration memory. A 4-bit wide switch block with the disjoint topology is shown in Fig. 2.16. Unlike the conventional switch blocks, however, switches in the multi-bit switch blocks are grouped into 4-bit wide groups and each group shares a single set of configuration memory. Note that without configuration memory sharing, each full switch would require 12 bits of configuration memory and each half switch would require 2 bits of configuration memory. With configuration memory sharing, 12 bits of configuration memory control the 4 full switches in this example. Only 2 bits of configuration memory control the 4 half-switches.

Fig. 2.16 Multi-bit Switch Block in the Configuration Memory Sharing Architecture

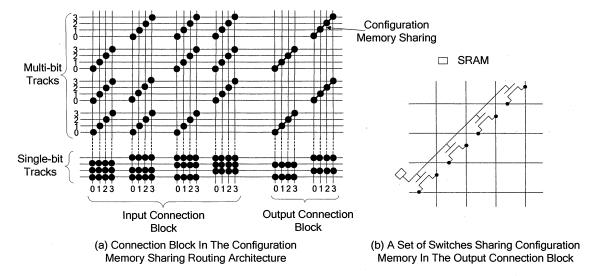

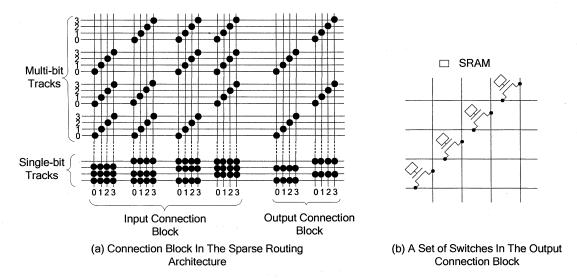

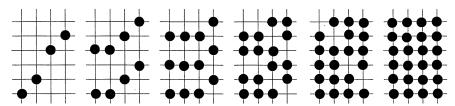

Similar to the switch blocks, the multi-bit aware routing architecture utilize two types of connection blocks – the single-bit and the multi-bit connection blocks. The single-bit connection blocks employ the same design methodology as described in section 2.2. The multi-bit connection blocks, on the other hand, is generated by operating the algorithm shown in Fig. 2.9 on buses instead of individual bits. In this case,  $F_c$  is the percentage of routing buses per channel that can be connected to a logic block input/output bus, P is the number logic block input/output buses, and W is the number of routing buses per channel.

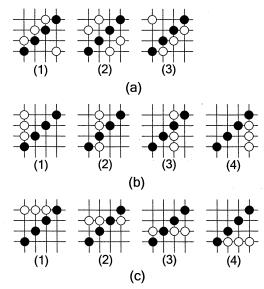

Fig. 2.17 Multi-bit Connection Blocks

Fig. 2.17 shows 4 examples of multi-bit connection blocks generated by the algorithm described above with varying  $F_c$  value. The bus width of these connection blocks is 4. In the figure, a black dot represents a routing switch. The vertical lines are I/O pins of multi-bit logic blocks and the horizontal lines are multi-bit tracks. Every 4

input or output pins are grouped into an input or output bus and every 4 routing tracks are grouped into a routing bus. When  $F_c$  is 0.25 as shown in Fig. 2.17 (a), each I/O bus connects to 2 of the 8 routing buses through two sets of switches. When  $F_c$  is 1.0 as shown in Fig. 2.17 (d), every I/O bus can connect to any of the routing buses.

Fig. 2.18 Connection Block in the Configuration Memory Sharing Architecture

Fig. 2.18 (a) shows a complete connection block in the configuration memory sharing architecture. This connection block contains the multi-bit input and output connection blocks as well as the single-bit input and output connection blocks. Each set of switches in the multi-bit output connection block share configuration memory as shown in Fig. 2.18 (b). Each switch in the multi-bit input connection block, on the other hand, is independently controlled by its own configuration memory cells because this switch is an input to a multiplexer which also takes inputs from single-bit tracks to a logic block input pin.

Fig. 2.18 (a) also shows an important feature of the connection block in the configuration memory sharing architecture: the switches in the multi-bit connection block are much sparser than those in the single-bit connection block. One of the goals of this research is to find out how much of the area efficiency of the configuration memory sharing architecture is attributed to the sparser switch pattern in the multi-bit connection block.

#### 2.3.2. Routing Resource Modeling in CAD Tool

The routing resources in the configuration memory sharing architecture are modeled

by the *multi-bit aware place and route tool* [22][27]. The tool models the routing resources with an rr-graph as well as several auxiliary data structures we describe later in this section.

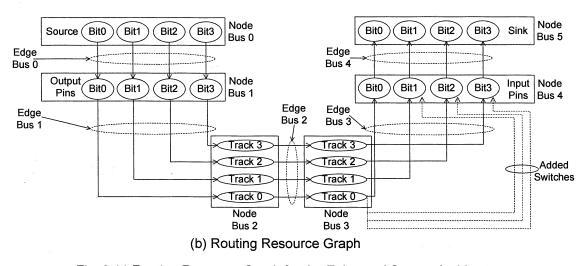

(a) Routing Resource in the Configuration Memory Sharing Architecture

(b) Routing Resource Graph

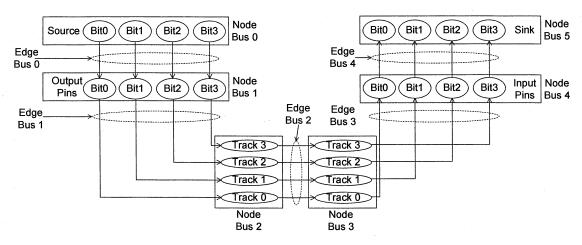

Fig. 2.19 Routing Resource Graph for the Configuration Memory Sharing Architecture

The rr-graph used in the multi-bit aware place and route tool can represent multi-bit as well as single-bit routing resources. Fig. 2.19 (a) shows a set of 4-bit wide multi-bit routing resources. In this figure, a logic block output bus is connected to a logic block input bus through routing buses and 3 sets of routing switches. These routing resources are modeled as an rr-graph by the multi-bit aware place and route tool as shown in Fig. 2.19 (b). Unlike the conventional architecture, each node representing a source, sink, logic block I/O pin, or multi-bit track in the rr-graph for the configuration memory sharing architecture belongs to a bus and has a bit position in that bus. These buses are marked as *node buses* in Fig. 2.19 (b). Similarly, each edge representing a switch that connects to sources, sinks or multi-bit tracks also belongs to a bus and has a bit position

in that edge bus. These buses are marked as edge buses in Fig. 2.19 (b).

The multi-bit aware place and route tool employs two sets of indices to record all the buses in the rr-graph corresponding to: 1) the node buses, and 2) the edge buses. Each node bus is assigned an index, numbered from zero, and the individual nodes comprising that bus are assigned bit positions in the bus. Similarly, each edge bus is assigned an index, also numbered from zero, and the individual edges comprising an edge bus are assigned bit positions in the bus. These indices are stored in the data structures representing the nodes and edges in the rr-graph.

Configuration memory sharing is not represented explicitly in the rr-graph. Instead, an array of integers is used to store whether each numbered edge bus index in the rr-graph uses configuration memory sharing. We call this array the *configuration memory sharing array*. When an integer in this array is one, the corresponding edge bus has configuration memory sharing; otherwise, there is no configuration memory sharing in the edge bus.

#### **CHAPTER 3**

#### The SPARSE AND ENHANCED SPARSE ARCHITECTURES

In this chapter, we introduce two multi-bit aware routing architectures that we investigate in this research: the sparse and enhanced sparse architectures. We developed the sparse architecture from the configuration memory sharing routing architecture and we enhanced the flexibility of the sparse architecture to create the enhanced sparse architecture. We describe the sparse architecture in Section 3.1 and the enhanced sparse architecture in Section 3.2.

#### 3.1. The Sparse Architecture

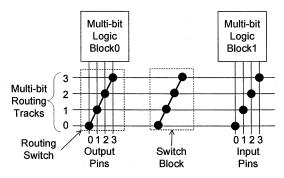

Compared to the conventional architectures, the configuration memory sharing routing architecture not only requires fewer configuration memory bits, but also employs sparser switch patterns in the multi-bit connection blocks. To isolate the effects of the sparser switch pattern in the multi-bit connection block from the effects of fewer configuration memory bits, we introduce the sparse architecture, which has the same arrangement of switches as the configuration memory sharing routing architecture but allows the switches to be individually controlled. Fig. 3.1 and Fig. 3.2 show the switch block and the connection block, respectively, in the sparse architecture.

Fig. 3.1 Switch block on multi-bit tracks in the sparse architectures

Fig. 3.2 Connection Block in the Sparse Architecture

We call the sparse architecture's switch pattern, which connects two buses using a set of switches in a diagonal arrangement, the *sparse switch pattern*. Similar to the switch patterns in the configuration memory sharing architecture, each switch in the sparse switch pattern only connects logic block I/O pins to the routing tracks at the same bit position. But unlike the configuration memory sharing routing architecture, each bit in a bus in the sparse architecture can be connected to the corresponding bit in another bus without affecting the connections in the other bits in the same bus.

We modeled the sparse architecture with the multi-bit aware place and route tool. To represent the sparse architecture in the tool, we need to use the rr-graph and the configuration memory sharing array. The rr-graph for the sparse architecture is the same with that for the configuration memory sharing. The members in the configuration memory sharing array, however, are not set to constants as in the original multi-bit aware place and route tool.

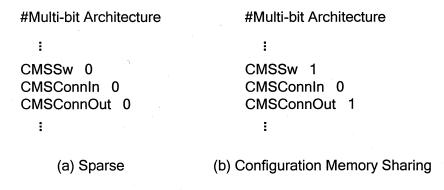

Fig. 3.3 Configuration Memory Sharing Setting in the Architecture File

We set the values of the configuration memory sharing array according to 3 variables representing whether there is configuration memory sharing in the switch blocks, the input connection blocks, and the output connection blocks. These 3 variables pick up their values from the architecture file, which can now include 3 new keywords, as shown in Fig. 3.3: *CMSSw*, *CMSConnIn*, and *CMSConnOut*. The parameter following the keyword *CMSSw* decides whether there is configuration memory sharing in the switch blocks. Value 1 or 0 for this parameter sets or clears, respectively, the configuration memory sharing in the switch blocks. The other two keywords work in the same way: *CMSConnIn* for configuration memory sharing in the input connection blocks and *CMSConnOut* for configuration memory sharing in the output connection blocks.

With the multi-bit aware place and route tool modified to handle these 3 new keywords in the architecture file, we can then model either the sparse architecture with the settings shown in Fig. 3.3 (a), or the configuration memory sharing routing architecture with the settings shown in Fig. 3.3 (b). These new keywords simplify exploring the multi-bit aware routing architectures.

## 3.2. The Enhanced Sparse Architecture

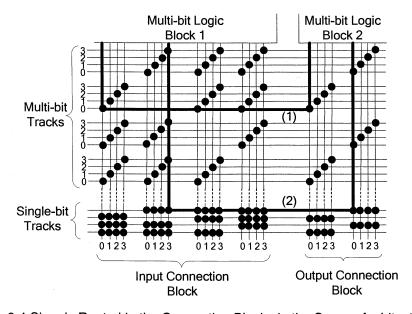

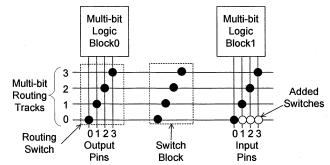

Fig. 3.4 Signals Routed in the Connection Blocks in the Sparse Architecture

In the sparse architecture, only signals from logic block output pins to the logic block input pins at the same bit position can be routed through the multi-bit tracks. For example,

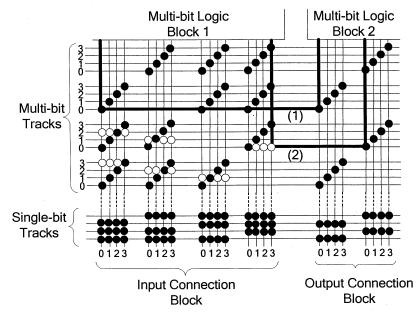

Fig. 3.4 shows an input and an output connection block in the sparse architecture. The thick lines in the figure represent signals routed through these connection blocks. As shown, the logic block I/O pins at bit position 0 can be only connected to the multi-bit tracks at bit position 0, so signal 1 from bit 0 to bit 0 can be routed on the multi-bit tracks. Signal 2, on the other hand, cannot be routed on the multi-bit tracks because this signal connects bit 0 to bit 3. In this case, single-bit routing tracks are needed even though there are empty multi-bit tracks.

Fig. 3.5 Signals Routed in the Connection Blocks in the Sparse Architecture with Extra Routing Switches

If we sparsely add switches to the multi-bit connection blocks to connect logic block I/O pins to routing tracks at different bit positions, as shown in Fig. 3.5, signal 2 can be routed on the multi-bit tracks. In this figure, a white dot represents one of these *added switches* on multi-bit tracks. With these added switches, the multi-bit connection blocks become more flexible. We call the sparse architecture with added switches on multi-bit tracks the *enhanced sparse architecture*.

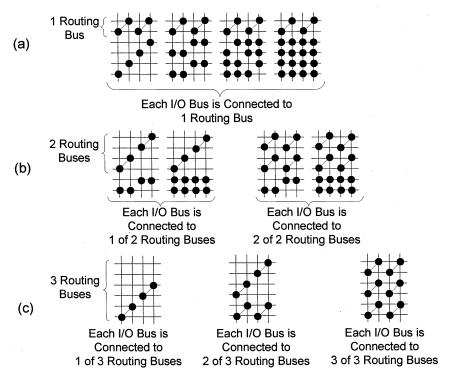

In this research, we selectively investigated several switch patterns to enhance the sparse switch pattern. We call these switch patterns enhanced sparse switch patterns, as shown in Fig. 3.6. To simplify the description, we use a bus width of 4, but the enhanced sparse switch patterns can be easily derived for other bus widths. In this figure, a set of black dots represents the sparse switch pattern. We call the set of switch patterns shown

in Fig. 3.6 (a) formed by the white dots, indicating the added switches, *shift patterns*. In the set, there are 3 shift patterns, indexed from 1 to 3. The added switch patterns shown in Fig. 3.6 (b) are called *vertical control* patterns and the ones in Fig. 3.6 (c) are called *control* patterns. Each set of vertical control patterns or control patterns contains 4 switch patterns indexed from 1 to 4. The sparse switch patterns with the shift patterns are called the *shift enhanced sparse* switch patterns. Similarly, we also define the *vertical control enhanced sparse* switch patterns and the *control enhanced sparse* switch patterns.

Fig. 3.6 The Enhanced Sparse Switch Patterns Investigated in the Research

Note that we do not add extra switches to every sparse switch pattern on multi-bit tracks. Instead, we introduce a new architectural parameter  $F_{c\_enh}$ , which is the fraction of routing buses that have enhanced switch patterns, so that the added density on the multi-bit tracks can be controlled. It is crucial to be able to balance the routing flexibility offered by the extra switches against the additional area those switches require. In Section 4.2, we investigate just where this balancing point lies.

To generate the enhanced sparse switch patterns, we first generate the sparse switch pattern as introduced in section 3.1. Then to the sparse switch pattern we add extra switches. We did not incorporate the process of generating the enhanced sparse switch patterns in the multi-bit aware place and route tool. Instead, we built an external program which can output the description of the enhanced sparse switch patterns to the architecture file. We then modified the multi-bit aware place and route tool to accept a description for any arbitrary switch pattern in the architecture file.

Fig. 3.7 shows the algorithm which adds the control patterns shown in Fig. 3.6 (c) to the sparse switch pattern to generate the control enhanced sparse switch patterns in the external program. As shown, we only show the algorithm for bus width 4, but the algorithm can be easily adapted to any bus width.

```

NumEnhancedBus=floor(NumMultiBitTracks × Fc Enh / BusWidth)

ControlPatternIndex= 1

FOR each side of a multi-bit logic block

SET the current routing bus to be the NumEnhancedBus from the last bus in the

multi-bit tracks

FOR each routing bus in the enhanced routing buses

FOR each input bus on the current side of a multi-bit logic block

IF there is a sparse switch pattern on the current intersection between the

routing bus and the input bus

Put a control pattern at ControlPatternIndex

Increase ControlPatternIndex by 1

IF ControlPatternIndex>4

ControlPosition=1

ENDIF

ENDIF

ENDFOR

ENDFOR

```

Fig. 3.7. The Algorithm Adding the Control Patterns to the Sparse Switch Pattern

**ENDFOR**

In Fig. 3.7, NumEnhancedBus represents the number of routing buses that have enhanced switch patterns. The number of routing buses that have enhanced switch patterns is a fraction of the total number of multi-bit tracks and the fraction is represented by  $F_{c\_enh}$ . BusWidth is the bus width of the multi-bit tracks. ControlPatternIndex is the index of a control pattern ranging from 1 to 4. The control patterns are added to the sparse switch patterns side by side with a multi-bit logic block. For each side of a multi-bit logic block, control patterns are added along the enhanced routing tracks to the

intersections of the input buses and the routing buses where there is the spare switch pattern. Every time a control pattern is added to the sparse switch patterns, *ControlPatternIndex* increments by one until the variable equals 4 and is then reset to 1. We can use the similar basic algorithm to generate the other two enhanced sparse switch patterns. Instead of putting control patterns on a sparse switch pattern, we put a shift pattern or a vertical pattern.

Note that we only put the added switches in the multi-bit input connection blocks. The switches in the input connection blocks are constructed with multiplexers, so adding a switch to an input connection block means adding an input pin to a multiplexer in the connection block. Adding a switch to an input connection block consumes less active area than adding a switch, which is a pass transistor, to the output connection block.

The algorithm outputs the description of the control enhanced sparse switch patterns to the architecture file. Fig. 3.8 shows an example of the output of the algorithm. First, the parameter following a keyword *coarseTracksInUserMatrix* declares the number of multi-bit tracks in the switch patterns: 4 in this example. The keyword *fineTracksInUserMatrix* declares the number of single-bit tracks in the switch pattern: it is 0 because the algorithm doesn't generate switch patterns for the single-bit tracks. The following lines describe the matrix itself. The matrix for input pins of a multi-bit logic block is described first and is followed by the matrix for output pins. For both the input and output pins, the matrix is shown side-by-side along the edge of the multi-bit logic block. For example, *inputUserMatrix top* means the matrix following the keyword is for the input pins on the top side of the multi-bit logic block. In the matrix, *c* indicates a switch in the sparse switch pattern, *I* represents an added switch and 0 means no switch. The set of switches denoted by *c* in a bus must form the sparse switch pattern or else these switches will be treated as added switches.

The control enhanced sparse switch patterns described in Fig. 3.8 is shown in Fig. 3.9. In this figure, a black dot represents a switch in the sparse switch pattern and a white dot denotes an added switch. A thin short line is a logic block input pin and a thick short line is a logic block output pin. The long lines represent multi-bit routing tracks. In the switch patterns shown, the bus width is 4. There are a total of 40 input and 16 output pins in the switch pattern shown, distributed on the 4 sides of a multi-bit logic block. Among

the 40 input pins, 8 input pins are located on both of the top and the right side and 12 are located on both of the bottom and the left side of the multi-bit logic block. The 16 output pins spread evenly on the 4 sides of the logic block. From left to right or from bottom to top, every 4 pins can be grouped together to form a bus.

coarseTracksInUserMatrix 4 fineTracksInUserMatrix 0 inputUserMatrix top: 0000c111n 00000c00n 00000c0n 000000cn inputUserMatrix bottom: 0000c000c000n 00001c110c00n 000000c011c1n 0.000000c000cn 0000c000c111n inputUserMatrix left: 00000c000c00n 000000c000c0n 0000111c000cn c000c000n inputUserMatrix right: 1c110c00n 00c011c1n 000c000cn outputUserMatrix top: c000n 0 c 0 0 n 00c0n000cn outputUserMatrix bottom: c000n 0c00n0.0c0n000cn 0000n outputUserMatrix left: 0000n 0000n 0000n c000n outputUserMatrix right: 0 c 0 0 n 00c0n000cn

Fig. 3.8 The Control Enhanced Sparse Switch Patterns Described in an Architecture File

Fig. 3.9 An enhanced sparse switch pattern

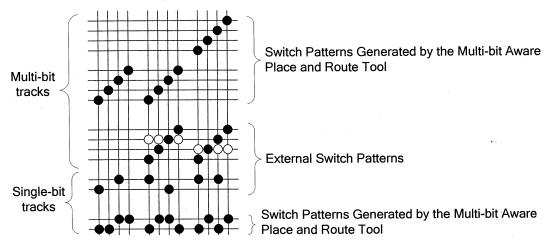

We call the switch patterns generated by an external program and described in the architecture file the *external switch patterns*. After the multi-bit aware place and route tool reads the external switch patterns, the tool compares the number of multi-bit tracks in these switch patterns with that required by the tool. If the tool requires less multi-bit tracks than those in the external switch patterns, the extra multi-bit tracks at the end of these switch patterns will be ignored. If the tool needs more multi-bit tracks than those in the external switch patterns, the tool will generate switch patterns on multi-bit tracks to fill in the blank. The same process is applied to the single-bit tracks as well.

Fig. 3.10 Merged Switch Patterns

When there are switch patterns generated by both an external program and the

multi-bit aware place and route tool, these switch patterns are merged in the way illustrated in Fig. 3.10. The external switch patterns are inserted into the switch patterns generated by the multi-bit aware place and route tool, between the multi-bit tracks and the single-bit tracks, so that multi-bit tracks can stay together and so do the single-bit tracks as shown in Fig. 3.10.

(a) Routing Resource in the Enhanced parse Architecture

Fig. 3.11 Routing Resource Graph for the Enhanced Sparse Architecture

To model the enhanced sparse switch patterns in the multi-bit aware place and route tool, we modified the rr-graph in the tool. Fig. 3.11 (a) shows an enhanced sparse switch pattern. The corresponding rr-graph is illustrated in Fig. 3.11 (b). In Fig. 3.11 (a), the white dots denote added switches that connect multi-bit tracks to logic block input pins. The edges representing these switches in the rr-graph are denoted by dashed lines as shown in Fig. 3.11 (b). Since the added switches do not connect any buses, the edges representing these switches do not belong to any edge bus. The existing multi-bit aware place and route tool, however, assigns an edge bus index and a bit position to every edge

that connects to multi-bit tracks. We modified the tool so that the modified tool only assigns edge bus indices and bit positions to the edges representing switches in the sparse switch pattern.

## 3.3. Design Space Analysis

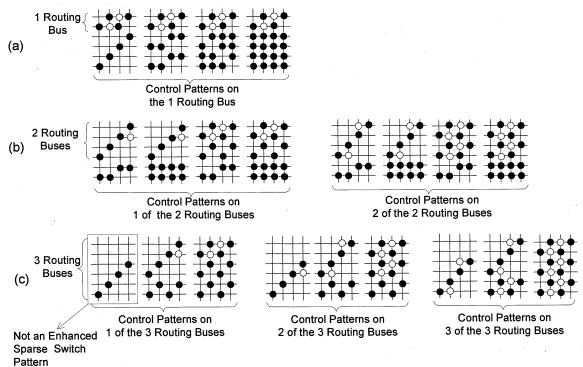

The major change in the sparse and enhanced sparse architectures introduced in this chapter compared to earlier architectures is the design of the connection block. In this section, we compare the number of switch patterns that are possible in the connection block designs for the sparse and enhanced sparse architectures with that for the conventional and configuration memory sharing routing architectures. Note that two switch patterns can be different in either: 1) the arrangement of the switches (switch arrangement), or 2) whether configuration memory sharing is used for these switches. In this section, we use the number of possible switch patterns in a connection block to quantify the design space available to a particular routing architecture.

To simplify the following description, we use three parameters to characterize a connection block: W for the number of routing tracks, P for the number of logic block I/O pins, and M for the bus width of multi-bit tracks. We also use an example 2-bit wide connection block containing 4 logic block I/O pins and 6 routing tracks (W=6, P=4, M=2).

Fig. 3.12 Switch Patterns Generated By VPR

For the conventional architectures, the number of connection block switch patterns VPR can generate only depends on the number of routing tracks in the connection block. In a connection block containing 6 tracks, VPR can generate 6 switch arrangements, as shown in Fig. 3.12. Since the conventional architecture does not employ configuration memory sharing, the number of switch patterns is the same as the number of switch arrangements. To generalize this result: in a connection block containing *W* tracks, VPR can generate *W* switch patterns.

The number of all the possible switch arrangements for a connection block can be calculated by the formula:  $\binom{W}{\Sigma} \binom{W}{i}^P$ . The example connection block in Fig. 3.12 has almost 16 million possible switch arrangements. The number of switch patterns in the conventional architecture is therefore only a tiny fraction of all possible switch patterns for a connection block.

Fig. 3.13 Switch Patterns in The Configuration Memory Sharing Routing Architecture

The configuration memory sharing routing architecture makes a step towards the wide open design space. The number of connection block switch patterns that can be created in the configuration memory sharing routing architecture depends on the number of tracks in the connection block and the bus width of the routing architecture. As shown in Fig. 3.13, when there are 6 routing tracks in a 2 bit wide connection block, 11 switch patterns can be generated. Fig. 3.13 (a) shows the switch patterns for the connection block with only 1 routing bus. In the case, there is only 1 switch pattern for the multi-bit connection block and 4 switch patterns for the single-bit connection block. When there are two routing buses in the connection block as shown in Fig. 3.13 (b), two switch patterns can be generated for the multi-bit connection block, and for each of the two

switch patterns, two switch patterns can be created for the single-bit connection block. When there are 3 routing buses in the connection block, 3 switch patterns can be generated for the multi-bit connection block and there is no single-bit connection block, as shown in Fig. 3.13 (c). For any M bit wide connection block with W tracks, there are  $\sum_{i=1}^{(W/M)} \left[ i \times \max(1, W - i \times M) \right]$  switch patterns that can be generated in the configuration memory sharing routing architecture.

The connection block switches in the sparse architecture are arranged in the same way as those in the configuration memory sharing routing architecture, but they are controlled differently. The number of connection block switch patterns in the sparse architecture, therefore, is the same as for configuration memory sharing routing architecture. The switch patterns are, however, distinct; the sparse architecture switch patterns are not the same as the configuration memory sharing routing architecture.

Fig. 3.14 Switch Patterns in the Control Enhanced Sparse architecture

The number of connection block switch patterns that can be produced in the enhanced sparse architecture depends on the number of routing tracks, the number of logic block I/O pins and the bus width of the connection block. Fig. 3.14 shows the possible switch patterns for the enhanced sparse architecture. The black dots in the switch patterns in Fig.

3.14 (a) are arranged in the same way as those in Fig. 3.13 (a), but there are control patterns (shown with white dots) on the multi-bit tracks in Fig. 3.14 (a). In Fig. 3.14 (b), the switch patterns are divided into two groups according to the number of routing buses that have control patterns. The black dots in each group are arranged in the same way as those shown in Fig. 3.13 (b). Similarly, the switch patterns in Fig. 3.14 (c) are divided into 3 groups. The black dot arrangements in each group are the same as those shown in Fig. 3.13 (c). The first switch pattern in the first group, however, is not an enhanced sparse switch pattern and should not be counted with the other patterns in this row of the figure. In this extra switch pattern, the control pattern can not be added to the top routing bus because this bus does not have any switches from the sparse switch pattern. This situation can only occur when the number of routing buses is larger than the number of logic block I/O buses. The amount by which the number of routing buses exceeds the number of logic block I/O buses determines how many switch patterns should be subtracted from the total number of possible switch patterns. As a result, we can generate 20 enhanced spare switch patterns in total for the connection block shown in Fig. 3.14. We can generalize for any M bit wide connection block that contains W routing tracks and P logic block I/O pins in the enhanced sparse architecture to compute the number of

switch patterns:

$$\sum_{i=1}^{(W/M)} \left[ i \times i \times \max(1, W - i \times M) - \sum_{j=1}^{\max(i - P/M, 0)} j \right].$$

Note that the control enhanced sparse architecture is only one of the 3 enhanced sparse architectures we investigate in this research. When the bus width of the enhanced sparse architecture is more than 2, we can have all 3 types of enhanced sparse switch patterns. Consequently, the number of the enhanced sparse switch patterns is 3 times of that of the control enhanced sparse switch patterns.

Table 3.1 shows the number of switch patterns that can be generated for 4 bit wide connection blocks with 8 logic block I/O pins and 8, 12, or 16 routing tracks. When there are 8 routing tracks in the connection block, 8 switch patterns can be generated in the conventional architecture, 6 in the configuration memory sharing and the sparse architecture respectively, and 24 in the enhanced sparse architectures. The sparse and the enhanced sparse architecture introduced in this research together more than double the design space that has been previously explored by the conventional and the configuration

memory sharing routing architectures. This design space expansion with the two new routing architectures is even more obvious when there are 12 or 16 routing tracks in the switch pattern.

Table 3.1 Connection Block Design Space

| W  | M | P | Conventional | Configuration<br>Memory<br>Sharing | Sparse | Enhanced<br>Sparse |

|----|---|---|--------------|------------------------------------|--------|--------------------|

| 8  | 4 | 8 | 8            | 6                                  | 6      | 24                 |

| 12 | 4 | 8 | 12           | 19                                 | 19     | 96                 |

| 16 | 4 | 8 | 16           | 44                                 | 44     | 276                |

In the remainder of the thesis, we compare these two new routing architectures to the earlier routing architectures in more detail, and empirically report on their area efficiency.

#### **CHAPTER 4**

# TRADEOFFS BETWEEN ROUTING SWITCH DENSITY AND ROUTING FLEXIBILITY

In this chapter, we compare the routing switch density in conventional and configuration memory sharing routing architectures to that of the new routing architectures introduced in this thesis: sparse and enhanced sparse architectures. From the extra routing switch density in the sparse and the enhanced sparse over the configuration memory sharing routing architecture, we then derive the extra routing flexibility needed to compensate for the density increase in the two new routing architectures. The evaluation covers a wide range of  $F_c$  values for all of these routing architectures. Section 4.1 describes the circuit assumptions for the evaluation presented in Section 4.2.

## 4.1. Circuit Assumptions

Our evaluation is based on the following circuit level assumptions. First, as in [4], we assume each SRAM cell is constructed out of six minimum width transistors. We also assume that two types of buffers are used in our architectures – a 4x buffer with four times the minimum driving strength and a 5x buffer with five times the minimum driving strength. Both buffers use a two-stage design with a stage ratio of four and five respectively.

The 5x buffers are used in constructing the two types of routing switches found in the switch blocks – a full switch and a half switch. Each track segment is assumed to have a segment length of 2. Bus width in our evaluation is 4. The general circuit design of switch blocks is described in section 2.1.3. The switch block design for the configuration memory sharing routing architecture is illustrated in section 2.3.1 and that for the sparse and the enhanced sparse architectures is in section 3.1

For the conventional, the configuration memory sharing, and the sparse architectures, we assume, as shown in Fig. 4.1, each logic block input pin is connected to its neighboring routing channel through a 4x buffer followed by a multiplexer. The multiplexer is constructed out of  $2I_m - 2$  pass transistors of minimum width and is