## FREQUENCY CALIBRATION OF THE SYSTEM CLOCK OF PASSIVE WIRELESS MICROSYSTEMS

by

Durand Jarrett-Amor

Bachelor of Engineering, Ryerson University, 2015

Bachelor of Science, University of Waterloo, 2009

A thesis

presented to Ryerson University in partial fulfillment of the requirements for the degree of Master of Applied Science in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2017 ©Durand Jarrett-Amor, 2017

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A THESIS

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public.

#### ABSTRACT

## FREQUENCY CALIBRATION OF THE SYSTEM CLOCK OF PASSIVE WIRELESS MICROSYSTEMS

#### Durand Jarrett-Amor

Master of Applied Science, Electrical and Computer Engineering, Ryerson University, 2017

This thesis presents a theoretical and simulated study of frequency calibration of the system clock of passive wireless microsystems.

The proposed frequency calibration technique achieves ultra-low power, high frequency accuracy, and fast calibration of the frequency of a local oscillator in a passive wireless microsystem using a frequency-locked loop (FLL). A new integrating frequency difference detector (iFDD) that senses the frequency difference between the local oscillator and a reference clock is also proposed. The iFDD is implemented using a switched-capacitor network with two integrating paths. The FLL is composed of a logic-control block for generation of clock signals, the iFDD, and a relaxation voltage-controlled oscillator. A detailed analysis of the characteristics of the iFDD in the time and frequency domains is presented. The loop dynamics of the FLL is also investigated. The proposed FLL is implemented in IBM 0.13- $\mu$ m, 1.2 V CMOS technology and is validated through simulations using Spectre APS.

#### ACKNOWLEDGMENTS

I am grateful to Professor Fei Yuan for his guidance, support, and invaluable feedback throughout my thesis.

I am also thankful for the financial support from the Ontario Graduate Scholarship program and the Faculty of Engineering and Architectural Science at Ryerson University. I also wish to thank CMC Microsystems for providing the computer-aided design tools.

I would also like to thank Professor Andy Ye, Professor Lev Kirischian, and Professor Gul Khan for being on my defense committee and for the useful feedback they provided.

Lastly, I am grateful for all of the continued understanding and loving support provided by my partner throughout the entirety of my studies.

## Contents

| Α            | utho  | r's Dec         | claration                                                             | ii           |

|--------------|-------|-----------------|-----------------------------------------------------------------------|--------------|

| A            | bstra | ct              |                                                                       | iii          |

| $\mathbf{A}$ | cknov | wledge          | ments                                                                 | iv           |

| $\mathbf{C}$ | onter | $\mathbf{nts}$  |                                                                       | $\mathbf{v}$ |

| Li           | st of | Tables          | S                                                                     | viii         |

| Li           | st of | Figure          | es                                                                    | ix           |

| Li           | st of | $\mathbf{Symb}$ | ols                                                                   | xii          |

| 1            | Intr  | oducti          | ion                                                                   | 1            |

|              | 1.1   | Chara           | cterization of Radio Frequency Identification (RFID) Systems $\ldots$ | 2            |

|              |       | 1.1.1           | Close-Coupling RFID Systems                                           | 2            |

|              |       | 1.1.2           | Remote-Coupling RFID Systems                                          | 2            |

|              |       | 1.1.3           | Long-Range RFID Systems                                               | 3            |

|              | 1.2   | Backg           | round on Passive Wireless Microsystems (PWMs)                         | 4            |

|              |       | 1.2.1           | Architecture                                                          | 4            |

|              |       | 1.2.2           | Applications                                                          | 6            |

|              | 1.3   | Motiva          | ation                                                                 | 6            |

|   |           | 1.3.1   | Challenges in the Design of the System Clock for PWMs $\ . \ . \ .$ .       | 6  |

|---|-----------|---------|-----------------------------------------------------------------------------|----|

|   | 1.4       | Object  | tive                                                                        | 9  |

|   | 1.5       | Contri  | butions                                                                     | 9  |

|   | 1.6       | Thesis  | Organization                                                                | 10 |

|   | 1.7       | Chapt   | er Summary                                                                  | 10 |

| 2 | A F<br>PW |         | of State-of-the-Art for Clock Generation and Calibration of                 | 12 |

|   | 2.1       | Clock   | Recovery Method                                                             | 12 |

|   |           | 2.1.1   | Clock Recovery from an ASK-Modulated Carrier                                | 12 |

|   |           | 2.1.2   | Clock Recovery using Injection-Locked Dividers                              | 13 |

|   |           | 2.1.3   | Clock Recovery from the Envelope of the Carrier                             | 14 |

|   | 2.2       | Remot   | e Frequency Calibration of a Local Oscillator                               | 15 |

|   |           | 2.2.1   | Remote Frequency Calibration using Digital Trimming                         | 16 |

|   |           | 2.2.2   | Remote Frequency Calibration using a Phase-Locked Loop $\ . \ . \ .$ .      | 16 |

|   |           | 2.2.3   | Remote Frequency Calibration using a Digital Frequency-Locked Loop          | 17 |

|   |           | 2.2.4   | Remote Frequency Calibration using an Injection-Locked Phase-Locked Loop    | 20 |

|   | 2.3       | Chapt   | er Summary                                                                  | 20 |

| 3 |           |         | owatts Integrating Frequency Difference Detector for Frequency<br>n of PWMs | 22 |

|   | 3.1       | Introd  | uction                                                                      | 22 |

|   | 3.2       | Integra | ating Frequency Difference Detector                                         | 23 |

|   |           | 3.2.1   | Concept of the iFDD                                                         | 23 |

|   |           | 3.2.2   | Time-Domain Behaviour of the iFDD                                           | 26 |

|   |           | 3.2.3   | Convergence                                                                 | 32 |

|    |       | 3.2.4  | Effect of Duty-Cycle Variation | 33 |

|----|-------|--------|--------------------------------|----|

|    |       | 3.2.5  | Maximum Frequency of Operation | 35 |

|    | 3.3   | Design | of the FLL                     | 36 |

|    |       | 3.3.1  | Model of the iFDD              | 36 |

|    |       | 3.3.2  | Model of the FLL               | 39 |

|    |       | 3.3.3  | Speed and Noise Considerations | 42 |

|    | 3.4   | Chapt  | er Summary                     | 42 |

| 4  | Res   | ults   |                                | 44 |

|    | 4.1   | Simula | ation Environment Set Up       | 44 |

|    | 4.2   | Simula | ation Results                  | 47 |

|    | 4.3   | Chapt  | er Summary                     | 53 |

| 5  | Con   | clusio | ns and Future Work             | 57 |

|    | 5.1   | Summ   | ary                            | 57 |

|    | 5.2   | Future | e Work                         | 58 |

| Bi | bliog | raphy  |                                | 59 |

## List of Tables

| 4.1 | Simulation Results of Power Consumption of FLL (Unit: $\mu$ W)                                                                                                                                                                       | 52 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | Simulation Results of Lock-time of FLL to a 1 MHz, 50% Duty-Cycle Reference Signal with $\alpha = 1. \ldots $ | 54 |

| 4.3 | Comparison with Prior Clock Recovery and Clock Calibration Technigues for PWMs <sup>*</sup>                                                                                                                                          | 55 |

## List of Figures

| 1.1 | Simplified block diagram of a typical UHF RFID transponder                                                                                                                                                                                                                                                                                                                                                                            | 4  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Simplified block diagram example of backscatter load modulation                                                                                                                                                                                                                                                                                                                                                                       | 7  |

| 1.3 | Spectrum of backscattered data signal from the transponder. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                              | 8  |

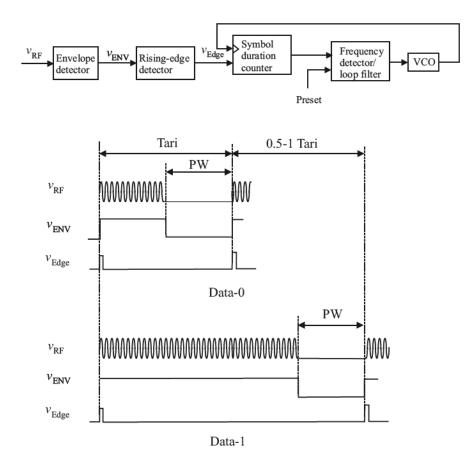

| 2.1 | Clock recovery from the ASK-modulated carrier wave [1]. $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                           | 13 |

| 2.2 | Clock recovery from the RF carrier wave using injection-locked dividers [1]                                                                                                                                                                                                                                                                                                                                                           | 14 |

| 2.3 | Clock generation from the envelope of the ASK-modulated carrier [1]                                                                                                                                                                                                                                                                                                                                                                   | 15 |

| 2.4 | Frequency calibration of a local oscillator by digital trimming $[1]$                                                                                                                                                                                                                                                                                                                                                                 | 17 |

| 2.5 | Frequency calibration of a VCO using a PLL $[1]$                                                                                                                                                                                                                                                                                                                                                                                      | 18 |

| 2.6 | Frequency calibration of a VCO using a DFLL [1]                                                                                                                                                                                                                                                                                                                                                                                       | 19 |

| 2.7 | Frequency calibration of a VCO using an IL-PLL [1]                                                                                                                                                                                                                                                                                                                                                                                    | 21 |

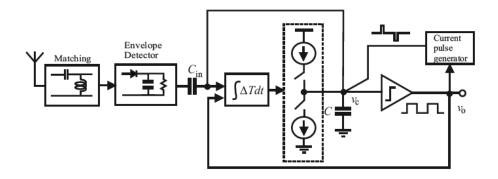

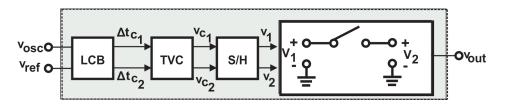

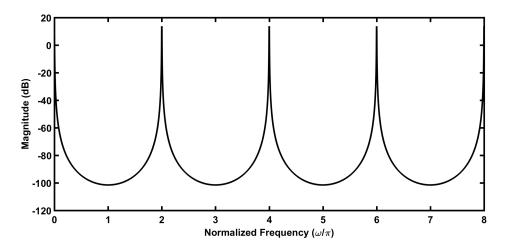

| 3.1 | Simplified block diagram of the proposed iFDD                                                                                                                                                                                                                                                                                                                                                                                         | 24 |

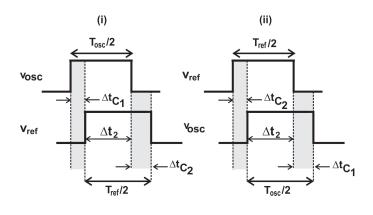

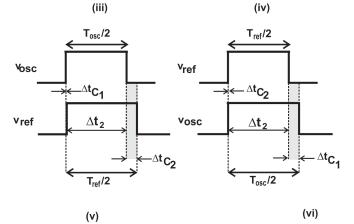

| 3.2 | Waveforms of $v_{osc}$ and $v_{ref}$ for fine frequency difference $(0 < f_{osc} < f_{ref}$ or $f_{ref} < f_{osc} < 2f_{ref}$ ) showing the definition of $\Delta t_{C_1}$ and $\Delta t_{C_2}$ , in addition to their intermediate and extreme values in (i)-(vi). This is for the ideal case that both waveforms are 50% duty-cycle signals.                                                                                        | 25 |

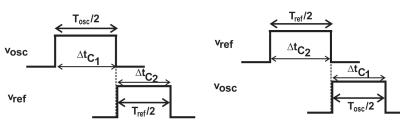

| 3.3 | Proposed iFDD and its logic control block (LCB) (left) and waveforms (right) of $v_{osc}$ , $v_{ref}$ , $\phi_{C_1}$ , $\phi_{sa1}$ , $\phi_{r1}$ , $\phi_{C_2}$ , $\phi_{sa2}$ , $\phi_{r2}$ , and $\phi_f$ . The order of operation of the switches are included in the waveform for ease of understanding. The number inside the brackets of $\Delta t_{C_1}(j)$ and $\Delta t_{C_2}(j)$ indicates their <i>j</i> th sample number | 27 |

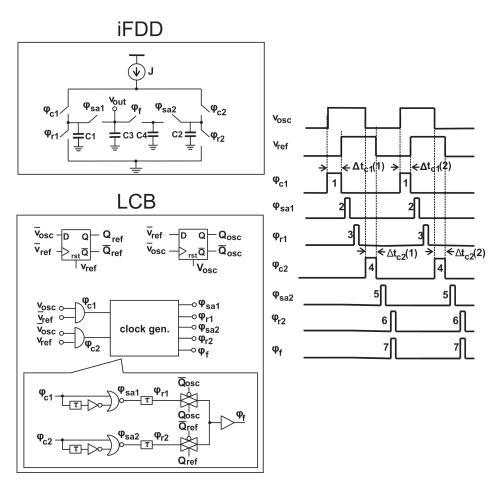

| 3.4 | Magnitude response of the iFDD with respect to normalized frequency                                                                                                                                                                                                                                                                                                                                                                   | 38 |

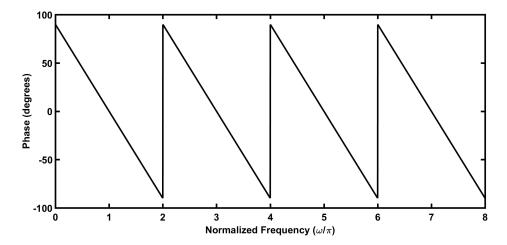

| 3.5 | Phase response of the iFDD with respect to normalized frequency.                                                                                                                                                                                                                                                                                                                                                                      | 38 |

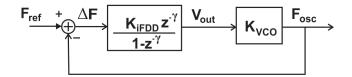

| 3.6  | Discrete-time model of the FLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 39 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

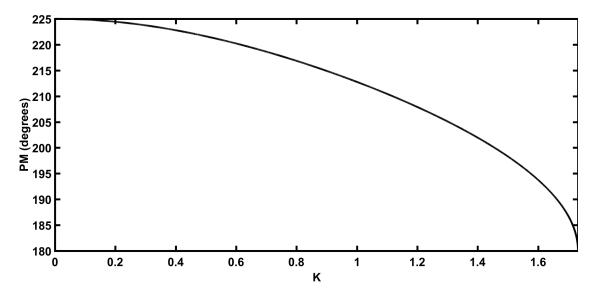

| 3.7  | Pot of phase margin $(PM)$ vs. loop gain factor, $K$                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41 |

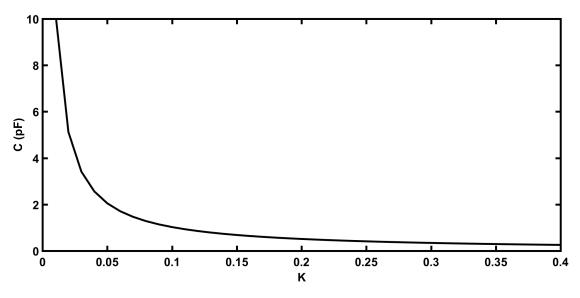

| 3.8  | Plot of C vs. loop gain factor, K, with $I = 100$ nA                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41 |

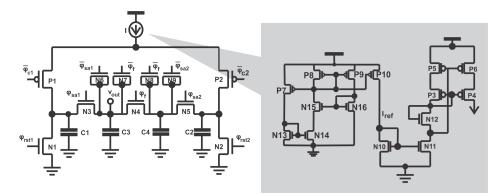

| 4.1  | Schematic of the iFDD. Transistor sizes are: $W_{N1,N2} = 0.320 \ \mu\text{m}, W_{N3-N5} = 1 \ \mu\text{m}, W_{P1,P2} = 0.640 \ \mu\text{m}, W_{N6-N9} = 0.5 \ \mu\text{m}, W_{N10-N12} = 0.480 \ \mu\text{m}, W_{P3,P5} = 0.960 \ \mu\text{m}, W_{P4,P6} = 1.55 \ \mu\text{m}, W_{N13-N16} = 0.480 \ \mu\text{m}, W_{P7-P9} = 0.960 \ \mu\text{m}, W_{P10} = 6 \ \mu\text{m}, L_{N1-N12,P1,P2,P3,P5} = 0.120 \ \mu\text{m}, L_{N13-N16} = 0.240 \ \mu\text{m}, \text{and } L_{P4,P6-P10} = 0.480 \ \mu\text{m}.$ | 44 |

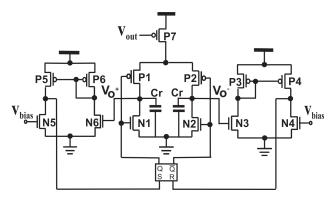

| 4.2  | Schematic of the relaxation VCO that was used to generate $v_{osc}$ . Transistor sizes are: $W_{N1-N6} = 0.350 \ \mu\text{m}, W_{P1-P7} = 0.700 \ \mu\text{m}, \text{ and } L_{N1-N6,P1-P7} = 0.120 \ \mu\text{m}.$<br>The value of the tuning capacitors, $C_r$ , was set 1.75 pF                                                                                                                                                                                                                                | 46 |

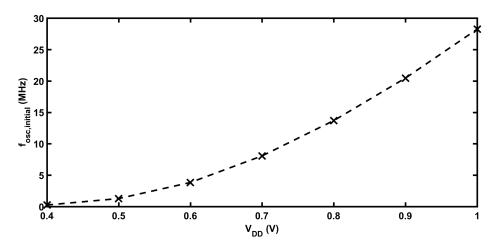

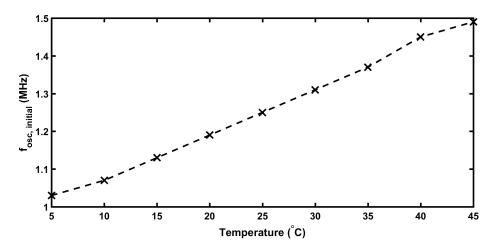

| 4.3  | Free-running frequency of VCO versus $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47 |

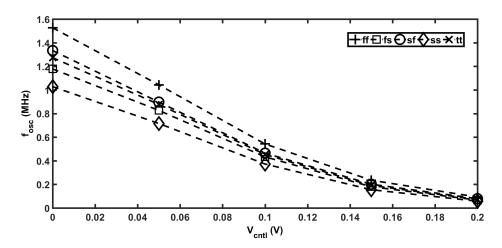

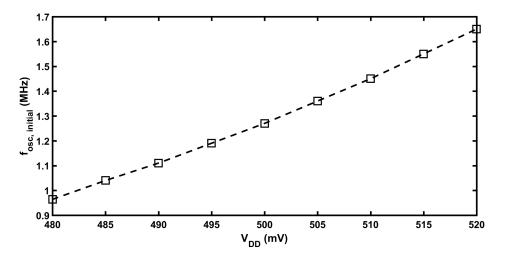

| 4.4  | VCO tuning curve across tt, ff, fs, sf, and ss process corners                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47 |

| 4.5  | Free-running VCO frequency $\sim$ temperature relation.                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48 |

| 4.6  | Free-running VCO frequency $\sim V_{DD}$ relation                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48 |

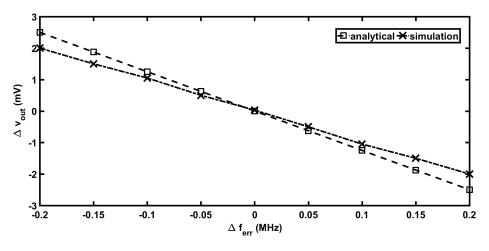

| 4.7  | $\Delta v_{out} \sim \Delta f_{err}$ relation                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49 |

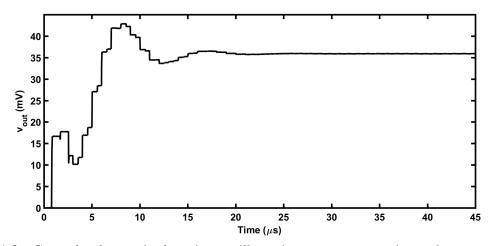

| 4.8  | Control voltage of relaxation oscillator in response to an input frequency step of 1 MHz with 50% duty-cycle.                                                                                                                                                                                                                                                                                                                                                                                                     | 51 |

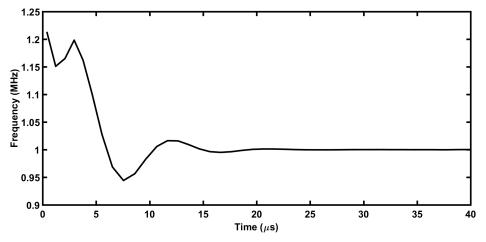

| 4.9  | Transient response of the frequency of the relaxation oscillator, $f_{osc}$ , with a 1 MHz, 50% duty-cycle reference clock input.                                                                                                                                                                                                                                                                                                                                                                                 | 51 |

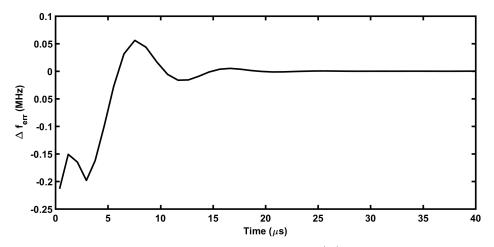

| 4.10 | Transient response of the frequency error, $\Delta f_{err}$ , in response to an input frequency step of 1 MHz with 50% duty-cycle.                                                                                                                                                                                                                                                                                                                                                                                | 52 |

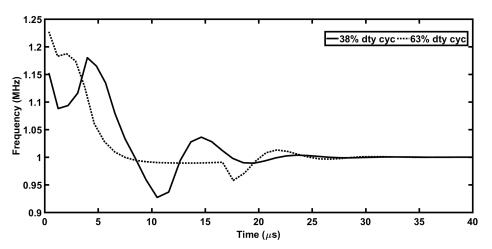

| 4.11 | Transient response of $f_{osc}$ to an input frequency step of 1 MHz with duty-cycles of 38% and 63%.                                                                                                                                                                                                                                                                                                                                                                                                              | 52 |

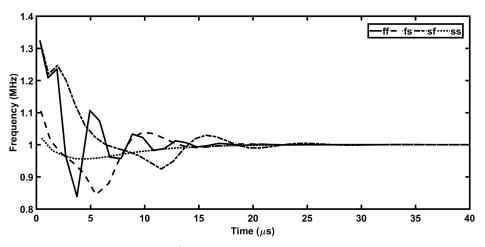

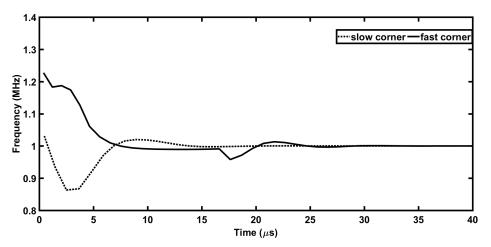

| 4.12 | Transient response of $f_{osc}$ to an input frequency step of 1 MHz with 50% duty-cycle across ff, fs, sf, and ss process corners.                                                                                                                                                                                                                                                                                                                                                                                | 53 |

| 4.13 | Transient response of $f_{osc}$ to an input frequency step of 1 MHz with 50% duty-cycle at fast ( $V_{DD} = 535 \text{ mV}$ , $T = -25^{\circ}\text{C}$ , ff process) and slow ( $V_{DD} = 465 \text{ mV}$ , $T = 85^{\circ}\text{C}$ , so process) corners.                                                                                                                                                                                                                                                      | 53 |

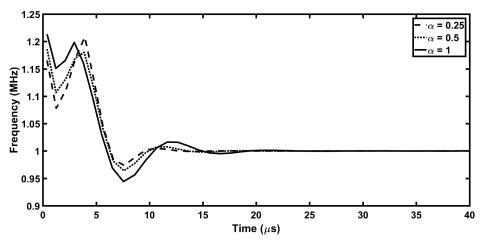

| 4.14 | Transient response of $f_{osc}$ to an input frequency step of 1 MHz with 50% duty-cycle<br>with $\alpha = \{0.25, 0.5, 1\}$ . Lock-time (within $\pm 1\%$ of $f_{ref}$ ) for $\alpha = \{0.25, 0.5, 1\}$ : 8.76 |    |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

|      | $\mu$ s, 9.27 $\mu$ s, and 13.53 $\mu$ s, respectively $\ldots \ldots \ldots$                   | 54 |  |

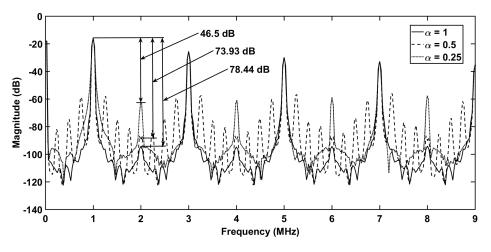

| 4.15 | Spectrum of VCO for $\alpha = \{0.25, 0.5, 1\}$                                                                                                                                                                 | 54 |  |

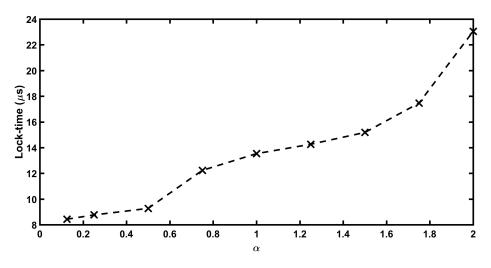

| 4.16 | Simulated lock-time (within $\pm 1\%$ of $f_{ref}$ ) versus $\alpha$ .                                                                                                                                          | 55 |  |

# List of Abbreviations

| CDS     | Cadence Design Systems                       |

|---------|----------------------------------------------|

| ADC     | Analog-to-Digital Converter                  |

| AND2    | 2-input AND logic gate                       |

| APS     | Accelerated Parallel Simulator               |

| ASK     | Amplitude-Shift Keying                       |

| BSIM4v4 | Berkeley Short-Channel IGFET Model 4 version |

| CMOS    | Complementary Metal-Oxide Semiconductor      |

| DAC     | Digital-to-Analog Converter                  |

| dBm     | Decidel power with respect to 1 Milliwatt    |

| DC      | Direct Current                               |

| DCO     | Digitally-Controlled Oscillator              |

| DFF     | Data (D) Flip-Flop                           |

| DFLL    | Digital Frequency-Locked Loop                |

| EPC     | Electronic Product Code                      |

| EPCC1G2 | Class-1 Generation-2 EPC standard            |

| ERP     | Equivalent Radiated Power                    |

| FF      | (NMOS)Fast-(PMOS)Fast                        |

| FLL     | Frequency-Locked Loop                        |

4

| FS        | (NMOS)Fast-(PMOS)Slow                     |

|-----------|-------------------------------------------|

| FVC       | Frequency-to-Voltage Converter            |

| iFDD      | Integrating Frequency Difference Detector |

| ILD       | Injection-Locked Divider                  |

| IL - PLL  | Injection-Locked Phase-Locked Loop        |

| IoT       | Internet-of-Things                        |

| LCB       | Logic-Control Block                       |

| IIR       | Infinite-Impulse-Response                 |

| MIM - cap | Metal-Insulator-Metal Capacitor           |

| 2:1MUX    | 2-input, 1-ouput Multiplexer              |

| NAND2/3   | 2/3 input Not-AND logic gate              |

| NMOS      | N-channel Metal-Oxide Semiconductor       |

| PFD       | Phase-Frequency Detector                  |

| PIE       | Pulse-Interval-Encoding                   |

| PLL       | Phase-Locked Loop                         |

| PMOS      | P-channel Metal-Oxide Semiconductor       |

| PVT       | Process, Voltage, and Temperature         |

| reltol    | Relative Tolerance                        |

| RF        | Radio Frequency                           |

| RFID      | Radio Frequency Identification System     |

| RT cal    | Read-to-Transponder calibration           |

| SAR       | ${\it Successive-Approximation-Register}$ |

| SF        | (NMOS)Slow-(PMOS)Fast                     |

| S/H      | Sample-and-Hold               |

|----------|-------------------------------|

| SNR      | Signal-to-Noise Ratio         |

| SR-latch | Set-Reset latch               |

| SS       | (NMOS)Slow-(PMOS)Slow         |

| TSPC     | True-Single-Phase-Clocking    |

| TT       | (NMOS)Typical-(PMOS)Typical   |

| TVC      | Time-to-Voltage Converter     |

| UHF      | Ultra High Frequency          |

| VCO      | Voltage-Controlled Oscillator |

# Chapter 1

## Introduction

Automatic identification procedures have become a popular method to supply information about animals, people, goods and products that are in transit and are now very important in the service, logistics, and manufacturing industries to name a few [2]. Although barcodes are stilled used to this day to provide information on products because they are very inexpensive, their low storage capacity and inability to be reprogrammed prevents them from being used in identification systems that require storage of large amounts of data and the ability to be reprogrammed [2].

Of the various types of identification systems-barcode, optical character recognition, voice recognition, smart card, and Biometry-radio frequency identification (RFID) systems are becoming popular alternatives because of their various distinct advantages, such as not being able to be interfered with while reading/writing data, their operation not being influenced by external objects like dust/dirt, and being able to have large distances ( $\gg 1$  m) between the reader and the data-carrying device [2]. Currently, they are finding extensive use in tap-to-pay systems for the goods and services industry as well as public transit payment systems. RFID systems consist of two intrinsic parts:

- the *transponder* (located on the item to be analyzed),

- the reader/interrogator.

The reader reads data from or writes data to the transponder and is usually composed of a transmitter/receiver module, a control block, and a coupling component to the transponder [2]. Similarly, the transponder also has a coupling element in addition to a microchip which processes and stores the data to be retrieved by the reader, provided it is within the reading distance of the reader [2].

# 1.1 Characterization of Radio Frequency Identification (RFID) Systems

RFID systems are typically characterized by the operating frequency of the reader, the coupling method between the reader and transponder, and the operating distance between the reader and transponder [2].

#### 1.1.1 Close-Coupling RFID Systems

RFID systems that have an operating range up to 1 cm are known as *close-coupling* systems [2]. Such systems have transmission frequencies in the range of 0-30 MHz and the coupling between the reader and transponder is achieved through both electric and magnetic fields, thus requiring the transponder to either be physically inserted into the reader or positioned on or very near to it [2]. Since close-coupling systems operate at very small distances, then their operating power can be greater than RFID systems that function at larger distances. Typically close-coupling RFID systems are used in applications that require rigid security between the reader and transponder as well as small operating distances between them, such as electronic door-locking systems and smart card systems with tap-to-pay functions [2].

#### 1.1.2 Remote-Coupling RFID Systems

RFID systems that operate at distances up to 1 m are termed *remote-coupling* systems [2]. Most remote-coupling systems use magnetic coupling between the reader and transponder, operate at frequencies less than 135 kHz or 13.56 MHz, and have applications in animal tracking and industrial automation [2].

#### 1.1.3 Long-Range RFID Systems

RFID systems with read-to-transponder ranges  $\gg 1$  m are collectively known as long-range systems [2]. These systems operate in the ultra-high frequency (UHF) range (860-960 MHz) and microwave region (2.5 GHz and 5.8 GHz) in Canada, use electromagnetic coupling between the reader and transponder (thus they require antennas for coupling) and the majority of such systems operate using the *backscattering* technique to communicate data from the transponder to the reader [2, 3, 4]. Long-range RFID systems are further distinguished by how their transponders are energized. Active long-range transponders have an on-board power supply/battery, whereas *passive* long-range transponders do not have a power supply but rather use the energy contained in the magnetic or electromagnetic field that is emitted by the reader when communicating with the transponder, provided the transponder is within the reader's interrogation zone [2]. In particular, if the transponder is in the interrogation zone of the reader, then it will provide the transponder with power through its emitted RF wave, which is stored on a large capacitor on the transponder [5]. The powerup procedure begins the reader-transponder communication process and it takes some time to complete, since the capacitor must be charged to a level that will allow the transponder to operate [2]. Another distinguishing factor between active and passive transponder is the field of the received RF wave from the reader. Since the magnetic or electromagnetic field of the emitted RF wave from the reader does not power active transponders, then it can be much weaker than the field that is emitted for passive transponders [2]. Passive transponders cannot generate enough power to create an RF signal on their own and, therefore, they rely on modulating the electromagnetic field that is emitted by the reader to be able to transmit data from the transponder to the reader [4]. In particular, passive transponders must be activated by the reader prior to communicating with it, whereas active transponders do not need to be activated by the reader prior to communication. Apart from the way active and passive transponders are powered, another major distinction between them is their operating distance. Active transponders have operating ranges of 15 m and above, while passive transponders typically have operating distances up to 3 m, although some authors haved reported operating distances of 9.25 m [2, 6].

## 1.2 Background on Passive Wireless Microsystems (PWMs)

RFID systems that operate using passive transponders are known as *passive wireless microsystems (PWMs)*. Attributive to their miniaturization, wireless accessibility, programmability, and maintenance-free operation, PWMs have found a broad range of emerging applications including implantable bio-MEMS pressure sensors [7], retinal prosthetic devices [8], multi-site pressure sensors for wireless arterial flow characterization [9], and wireless temperature sensors [10, 11, 12], to name just a few, and are the main focus of this thesis work.

#### 1.2.1 Architecture

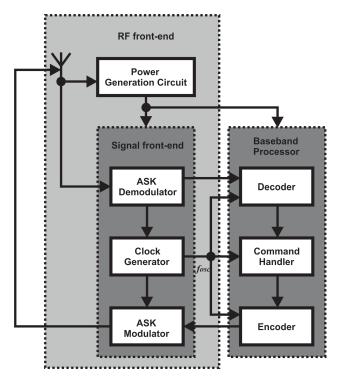

The architecture of an RF powered transponder consists of an antenna for receiving the RF signal, a power generation circuit, a signal front-end block, and a baseband processing block, as shown in Fig.1.1.

Figure 1.1: Simplified block diagram of a typical UHF RFID transponder.

#### **RF** Front-End

The first major layer of the transponder of the PWM is the RF front-end, which consists of an antenna for receiving the RF signal, a power generation circuit, an amplitudeshift-keying (ASK) demodulator for recovering the data, a clock generator for extracting the clock from the ASK demodulator, and an ASK modulator for transmitting the data from the transponder to the reader through backscattering. The RF front-end is thus responsible for supplying power to the transponder and interfacing with the reader.

Sub-components within the RF front-end that are critical to the correct operation of the transponder are the antenna matching network and the RF-to-DC converter. The antenna matching network is responsible for matching the impedance of the antenna to that of the transponder, in order to provide maximum power transfer from the RF signal to the chip [5]. The RF-to-DC converter is responsible for providing the required, stable DC voltage to power the transponder [5]. The efficiency of the matching network and the RF-to-DC converter are still major design challenges in these areas. However, the study of these important blocks are beyond the scope of this thesis and will not be discussed here.

#### **Baseband Block**

The baseband processing block consists of circuits that process, generate and/or store data, such as quantizing the sensor readings of the PWM through analog-to-digital converters (ADCs) or microprocessors for signal processing [5]. Since PWMs are powered by the incoming RF signal, then such signal processing units will have a very limited power budget. Consequently, the design of low power baseband processing circuits is the major challenge in this field, but is beyond the scope of this thesis and will not be discussed further.

#### System Clock

Another crucial element for PWMs is the clock signal itself. The operation of both the RF signal front-end and baseband processing blocks of a PWM is administered by its system clock, as seen in Fig.1.1. It is responsible for decoding the downlink data from the reader to the transponder, clocking the command handler, and encoding the uplink data from the transponder to the reader [13]. Further details on the requirements of the system clock and challenges in designing it will be explored in Section 1.3, followed by a review of the state-of-the art in clock generation and calibration for PWMs in Chapter 2.

#### 1.2.2 Applications

Passive wireless microsystems have applications in various areas that range from supply chain management for automation of the storing and distribution of goods, tracking items, and better inventory-control management; electronic access control into buildings and secure locations for storing equipment; tap-to-pay fare collection for transit systems; tracking livestock for animal health and disease control; and healthcare for tracking hospital equipment and supplies, to name a few [4]. Furthermore, the market for PWMs is expected to be worth \$14.9 billion by the year 2022, up from \$11.2 billion in 2017 [14]. Therefore, PWMs not only have applications in areas that either directly or indirectly affect our lives, but their economic impact is also very significant.

### 1.3 Motivation

The primary motivation of this thesis was overcoming the dominant challenges in the design of a clock generation technique for PWMs in UHF applications, which will be discussed next.

#### 1.3.1 Challenges in the Design of the System Clock for PWMs

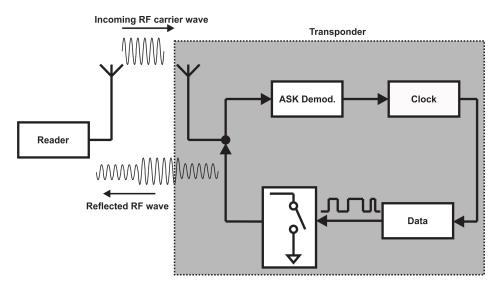

Due to the lack of a power source in PWMs, the transponder typically cannot allot any of its DC power to generate its own RF signal to communicate with the reader. Rather, PWMs communicate with the reader through backscatter load modulation, whereby a fraction of the received RF signal from the reader is reflected back to the reader by the transponder's antenna [2, 5]. The total power that is reflected back by the antenna is set by its input impedance. Therefore, by varying the impedance/load of the antenna, the amount of reflected power can be varied. The impedance of the antenna can be varied by modulating it with the data that is being transmitted by the transponder. The frequency of the data and, consequently, the frequency of the modulation of the antenna impedance is determined by the clock of the PWM. A diagram to illustrate the concept is presented in Fig.1.2. The switch varies the impedance of the antenna and is controlled by the baseband data, which controls the change in the antenna impedance. Backscatter load modulation significantly eases the power constraint on PWMs, since the transponder does not have to generate its own an RF signal thus greatly increasing its power budget.

Figure 1.2: Simplified block diagram example of backscatter load modulation.

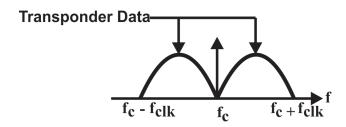

Modulating the data of the transponder by a carrier signal, namely the system clock of the PWM, generates sub-carriers which allows easier detection of the backscatterd signal by the reader [5]. This is shown in Fig.1.3. The reader can recover the carrier signal by filtering out the signal at the sub-carrier frequency  $f_c+f_{clk}$  using a low-pass filter. Fig.1.1 and Fig.1.3 show that the bandwidth of the backscattered transponder signal is set by the frequency of the transponder's clock signal. Therefore, a very accurate clock frequency is required to ensure proper transponder-to-reader communication. For the EPC radio-frequency class-1 generation-2 (EPC C1G2) UHF RFID protocol, the frequency variation of the uplink data must be bounded by  $\pm 2.5\%$  in environments that contain a single reader [3].

In addition to the frequency accuracy constraint, the power consumption of the clock generation technique must be low due to the limited power budget of a PWM. Additionally,

Figure 1.3: Spectrum of backscattered data signal from the transponder.

the larger the power consumption of a PWM the smaller the reader-to-transponder distance which limits the PWM to short-range applications [2]. Furthermore, the received power to a transponder decreases as its distance from the reader increases, further restricting the power budget of the PWM [2]. Therefore, for a PWM to operate at large ( $\gg 1$  m) reader-totransponder distances its power consumption must be ultra-low and the supply voltage it operates from should also be very low, since the amplitude of the received RF signal will be very small and its power decreases with increasing distance [2].

Including the power constraint and strict frequency accuracy requirement of the backscattered data, the calibration time of the reader-to-transponder can also be very strictly confined. For example, for EPC C1G2 UHF RFID protocol the reader-to-transponder calibration time can be as short as 56.25  $\mu$ s with a maximum calibration time of 300  $\mu$ s, depending on local radio regulations [3]. This places an extra constraint on the generation of the system clock.

To summarize, the following major challenges in the design of the system clock for PWMS are:

- 1. Ultra-low power clock generation due to the restricted power budget of the PWM.

- 2. Frequency variation of the backscattered data must be bounded by  $\pm 2.5\%$  for single reader environemnts.

- 3. Short calibration times ( $\leq 56.25 \ \mu s \text{ or } \leq 300 \ \mu s$ ).

- 4. Ability to operate at low supply voltages for large reader-to-transponder distances (>3 m) for UHF applications.

### 1.4 Objective

The objective of this thesis is the design of a frequency calibration technique that can meet the requirements described in Section 1.3.1. Our particular goal was to design a frequency calibration technique using a frequency difference detector that integrates the frequency difference between a reference clock that is provided by the reader and the local oscillator of a PWM, thereby providing zero steady-state frequency error for the system clock of the PWM after calibration, while also achieving very fast frequency calibration and an ultra-low power consumption so that the system can be used in long-range PWM applications, such as supply-chain management or healthcare.

### 1.5 Contributions

The following original contributions made by this thesis are outlined as follows:

- An ultra-low power, highly accurate, and fast frequency calibration method using a frequency-locked loop (FLL) that is embedded with frequency difference detector that integrates the frequency error between a reference clock sent by the reader and the local oscillator of the PWM, as discussed in Section 1.4. The calibration technique provides zero steady-state frequency error between a timing reference from the reader and the local oscillator of the transponder, while also achieving ultra-low power and a very short calibration time. Compared to previous clock generation techniques reported in [15, 16, 17, 18, 13, 19] our proposed design significantly improves on both the calibration time and the frequency accuracy of the system clock for PWMs.

- An ultra-low power integrating frequency difference detector (iFDD) that integrates the frequency difference between two signals and can operate at very low supply voltages. The iFDD provides fine frequency resolution and fast frequency calibration by detecting the duty-cycle and period difference between two signals through a switched-capacitor network. The importance of the iFDD design is that it uses only a single current source and switched-capacitor network to detect a frequency difference between two

signals, thereby reducing mismatch-induced frequency error present in dual-frequencyto-voltage (FVC) designs [20, 21].

### **1.6** Thesis Organization

This thesis is organized as follows:

- Chapter 1 provides an overview of the characterization of the various forms of RFID systems, background on the architecture of PWMs, and a brief discussion on the operation of each block within a PWM. This chapter also presents the challenges in designing the system clock for PWMs. The main objective of the thesis is derived from these design challenges. The contributions that the research presented in this thesis has achieved in realizing the main objective is also provided.

- Chapter 2 presents a literature review that examines and compares the state-of-theart in clock generation techniques for PWMs based on the major design challenges presented in Chapter 1.

- Chapter 3 introduces the proposed method for calibration of the system clock of PWMs. The proposed integrating frequency difference detector is presented and analyzed in detail in this chapter. The loop dynamics of the FLL embedded with the frequency difference detector is also investigated.

- Chapter 4 presents the simulation environment that was set up to test the performance of the FLL as well as the simulation results that were obtained from the set up. Comparison of our results to previous state-of-the-art works is also presented.

Chapter 5 summarizes the thesis and outlines possible directions for future work in this area.

## 1.7 Chapter Summary

This chapter presented a brief characterization of the difference types of RFID systems as well as basic background on PWMs. We acquainted ourselves with the basic architecture of a passive transponder and concisely discussed its critical circuit blocks, such as the RF front-end and baseband processing units. The specified tasks and design challenges of the signal front-end block, baseband block, and system clock of passive transponders were briefly discussed. Challenges with respect to the design of system clock for the transponder of PWMs were addressed in detail. From these challenges, it was concluded that the most pressing problems in the area of clock generation for PWMs are ultra-low power consumption, high frequency accuracy, and a fast calibration time. Motivated by these design challenges, the objective of this thesis was outlined and the contributions of a new frequency calibration technique using an integrating frequency difference detector were summarized.

## Chapter 2

## A Review of State-of-the-Art for Clock Generation and Calibration of PWMs

The operation of both the RF front-end and baseband processing blocks of PWMs is conducted by its system clock. As discussed in Chapter 1, there are demanding requirements on the system clock. A few methods have been developed to generate the clock for PWMs and they can be split into two categories:

- 1. Clock recovery from the incoming data sent by the reader.

- 2. Frequency calibration of a local oscillator in the PWM.

This chapter will review the advantages and disadvantages of previous works in each of these areas.

### 2.1 Clock Recovery Method

#### 2.1.1 Clock Recovery from an ASK-Modulated Carrier

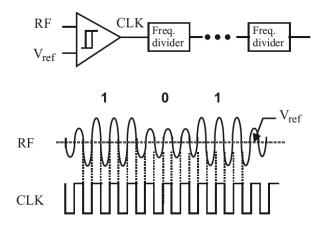

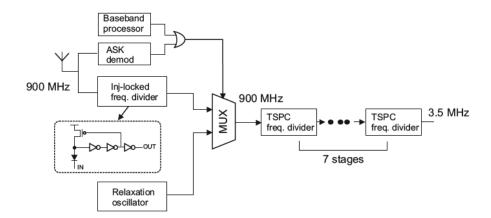

A PWM with ASK data links with its reader can directly extract the clock from the ASK-modulated carrier by using an ASK-demodulator, as shown in Fig.2.1 [22]. This approach yields a very simple design, since only a comparator and a chain of frequency dividers is needed. However, it suffers from a few notable drawbacks for UHF RFID systems. First, the high frequency of the carrier results in significant power consumption from the clock recovery circuit. This is because the baseband processors of PWMs operate in the high-kHz to low-MHz range, so frequency dividers are required to bring down the high frequency of the carrier to a baseband frequency [1]. Second, the clock signal is unavailable when the input RF signal is weak, which occurs when the read-to-transponder distance is large, or when transmitting a data-0 with a 100% modulation-index. Finally, a very stable voltage reference accross process, voltage, and temperature (PVT) variations is required to ensure reliable recovery of the clock signal from the RF carrier wave.

Figure 2.1: Clock recovery from the ASK-modulated carrier wave [1].

#### 2.1.2 Clock Recovery using Injection-Locked Dividers

To overcome the issue presented in Section 2.1.1, Leung and Luong proposed a method that uses an injection-locked divider (ILD) to reduce the power consumption of the frequency divider circuit as shown in Fig.2.2 [15]. The idea behind this approach is to first recover a clock at the frequency of the RF carrier when the RF signal is strong and then use low power injection-locked frequency dividers to bring the recovered clock frequency down further. True-Single-Phase-Clocking (TPSC) frequency dividers are used because of their low power consumption to further lower the frequency. This method resulted in a total average power consumption of 7  $\mu$ W from a power supply of 0.5 V and -12 dBm (63  $\mu$ W) input power to the transponder. Thus, the clock recovery circuit consumes 11% of the total received power. With this input power, a reading distance of around 3 m can be achieved (assuming a dipole antenna with 0 dB gain at 500 mW effective radiated power (ERP))[2]. However, as the reading distance increases and the amplitude of the received RF signal becomes smaller, the received input power decreases significantly [2]. Consequently, the majority of the power consumption of the transponder in this case would be from the clock generator circuit. Leung *et al.* resolve this issue by switching to a low-power oscillator circuit that consumes 1.5  $\mu$ W when the received RF signal is weak. However, the frequency accuracy of the local oscillator cannot be guaranteed because of PVT variations and since no frequency calibration of the local oscillator is done.

Figure 2.2: Clock recovery from the RF carrier wave using injection-locked dividers [1].

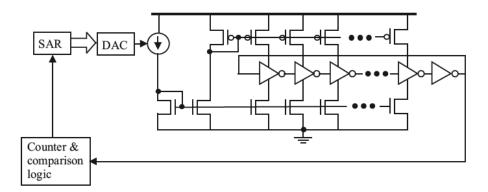

#### 2.1.3 Clock Recovery from the Envelope of the Carrier

The system clock of a PWM can also be extracted from the envelope of the received RF signal, as shown in Fig.2.3 [16, 23]. This method uses an envelope detection circuit to extract the envelope signal of the modulated RF carrier and a comparator to compare the amplitude of the recovered envelope signal with a reference value. The output of the comparator is then used to generate the clock signal. Compared with clock generation from the carrier, this method has a much lower power consumption because the clock that is extracted from the envelope is at a much lower frequency than the carrier signal and thus does not require frequency dividers, so it can be used for basedband operation of the transponder's processor. For example, Ma, Wu, Zhang, and Zhang achieved a static power consumption

for the clock generator circuit less than 1  $\mu$ W at a 1.8 V supply [16]. However, the dynamic power consumption of the clock generator circuit was 3.38  $\mu$ W. Another disadvantage of this approach is that a stable voltage reference across PVT is required for the comparator in order to accurately recover the clock signal. This increases the complexity and silicon area of the circuit, since compensation circuitry would be required for the reference voltage. Furthermore, any deviation in the reference voltage will result in reduced frequency accuracy of the recovered clock signal.

Figure 2.3: Clock generation from the envelope of the ASK-modulated carrier [1].

### 2.2 Remote Frequency Calibration of a Local Oscillator

The second method of creating the system clock for the transponder in a PWM involves generating the clock locally by tuning the frequency of a VCO. However, the impact of PVT uncertainty greatly affects the frequency accuracy of the local oscillator. For example, a VCOs free-running frequency can vary by as much as  $\pm 20\%$  owing to process, voltage, and temperature (PVT) effects [13]. Given the stringent frequency accuracy requirement of EPC C1G2 UHF RFID protocols of  $\pm 2.5\%$  for the backscattered data, the frequency of the VCO must be corrected prior to any operation of the PWM to reduce its frequency error.

Compensation circuitry can be used to offset the effect of supply voltage and temperature variations [24, 25]. However, such techniques become difficult to implement in PWMs because of their limited power budget [26, 27]. Furthermore, such techniques cannot mitigate the effect of process variations, so additional circuitry for process effects would be required. Another approach to correcting the VCO frequency prior to the commencement of the passive transponder's operations is to calibrate the VCO frequency with respect to a reference signal provided by the reader. This approach is termed *remote frequency calibration*.

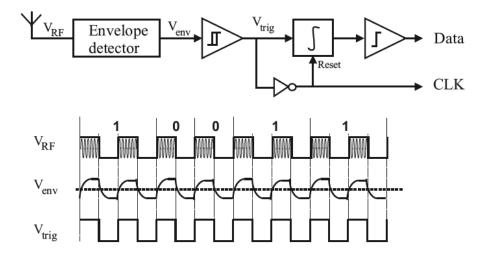

#### 2.2.1 Remote Frequency Calibration using Digital Trimming

The frequency of the local oscillator is often calibrated using digital trimming, shown in Fig.2.4 [17, 28, 29, 30, 31]. In this approach, the frequency of the local VCO is calibrated with respect to a calibrating signal sent from the reader in a calibration phase by using a counter to count the number of oscillation cycles of the oscillator during this phase. The value of the counter at the end of the calibration phase is then used as a threshold value for a successive-approximation-register (SAR), with which the frequency of the oscillator after the calibration phase is compared. Although this approach features a large frequency tuning range and excellent robustness in the presence of PVT variations, the need for a SAR, a digit-to-analog-converter (DAC), and other logic makes it rather difficult to lower the power consumption and shorten the calibration time. Additionally, since the frequency accuracy of digital trimming is set by the number of bits of the SAR, then improving the frequency accuracy will result in an increase in both the power consumption and the calibration time. For example, the power consumption of the frequency calibration block in [17] was 31  $\mu$ W while a calibration time of 928  $\mu$ s was required to set all of the bits of the 8-bit SAR.

#### 2.2.2 Remote Frequency Calibration using a Phase-Locked Loop

The local oscillator of a PWM can also be calibrated using a phase-locked loop (PLL), as shown in Fig.2.5 [18]. This approach uses a clock recovery and calibration circuit to calibrate the frequency of a VCO. An envelope detector detects the envelope of the received RF signal and a clock extractor generates a square wave clock signal with a frequency that is the same as the carrier frequency. Once the clock has been generated, a PLL is used to tune

Figure 2.4: Frequency calibration of a local oscillator by digital trimming [1].

the frequency of the VCO to the recovered clock signal. After the PLL has locked to the reference clock, a local system clock for the transponder of the PWM is generated. Fan, Dai, Zhang, and Lu implemented a PLL remote frequency calibration system that operated at a frequency of 13.56 MHz [18]. The total power consumption of Fan et. al's clock generation and calibration system was 17  $\mu$ W during the locking state and 3  $\mu$ W in the locked state. However, this is simply a result of the carrier frequency that was used in their design. For UHF carrier signals, the power consumption of this approach would be very large since the VCO would operate at a much higher frequency. Furthemore, when no carrier is available, which occurs when a large modulation index is used, the frequency of the local oscillator drifts since no reference clock is present. Fan et. al get around this problem by implementing a detector and logic block that turns the phase-frequency detector (PFD) off so that it holds it previous value, thus preventing the VCO frequency from differenting too much. However, the VCO frequency will drift by some amount due to stray capacitances in the loop filter of the PLL. Apart from the above drawbacks, since a PLL is used to calibrate the VCO, then the calibration time will be long since the PLL will lock the phase and frequency of the VCO to the recovered clock signal.

#### 2.2.3 Remote Frequency Calibration using a Digital Frequency-Locked Loop

Chan, Pun, Leung, Guo, Lincoln, and Choy proposed a remote frequency calibration technique that uses a digital frequency-locked loop (DFLL), as shown in Fig.2.6 [13]. This

Figure 2.5: Frequency calibration of a VCO using a PLL [1].

approach uses a counter that stores the number of oscillation cycles of a reference VCO during the transmission of a binary-0 or a binary-1, since in pulse-interval-encoding (PIE) a binary-0 and binary-1 have different pulse-widths [1]. A preset threshold value is used as a reference to compare the number of oscillation cycles of a digitally-controlled oscillator (DCO) that is stored in the counter. The threshold value is determined by the baseband processor of the transponder during the reader-to-transponder calibration (RTcal) phase. In particular, if the pulse-width of the transmitted symbol from the reader during RTcal is greater than RTcal/2, then the baseband processor decides that a binary-1 has been received. Otherwise, a binary-0 has been received. The DFLL compares the difference between the preset threshold value determined by the baseband processor and the value stored in the counter, such that their difference is used to control a DCO. Chan *et al.* were able to achieve a very low power consumption of 1.8  $\mu$ W and a frequency accuracy of -3.2~1.2% at a clock frequency of 2.56 MHz [13]. Another distinct advantage of this approach is that the DCO will be continuously calibrated so long as there is communication between the reader and transponder. However, a drawback of this approach is the limited frequency accuracy of the

local DCO, since a counter is used to store the number of oscillation cycles of the DCO. As a result, quantization error will always exist and fine frequency accuracy ( $\leq \pm 2.5\%$ ) cannot be achieved without increasing the power consumption of the transponder. A second drawback of this approach is that the reference value used to compare the number oscillation cycles of the DCO to is obtained from a second VCO that is not calibrated and thus is subject to PVT effects. Another limitation of this approach is its long calibration time of 16 PIE downlink data symbols in nominal conditions in the worst case and 6 PIE symbols in the best case [13]. Since a PIE symbol is determined by the length of a data-0 symbol plus a data-1 symbol, which can have pulse-widths between 25  $\mu$ s and 50  $\mu$ s and 6.25  $\mu$ s and 7.8125  $\mu$ s, respectively, then even in the best case scenario the calibration time of this technique is 84.375  $\mu$ s.

Figure 2.6: Frequency calibration of a VCO using a DFLL [1].

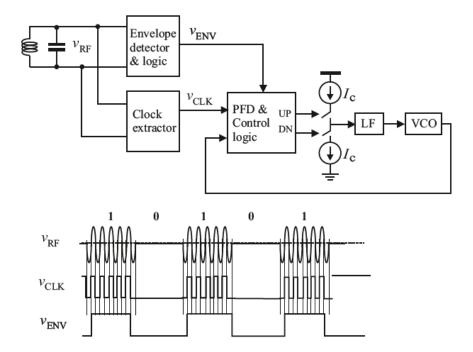

## 2.2.4 Remote Frequency Calibration using an Injection-Locked Phase-Locked Loop

A remote frequency calibration technique based on injection-locking to the envelope of the received RF input signal was proposed in [19] and is shown in Fig.2.7. This approach utilizes the fact that the baseband processor of passive transponders operates in the kHz-tolow-MHz range and that ASK-modulation schemes are often used for PWMs. Therefore, the envelope of the received RF signal can be extracted and then used as an injection-locking signal for the local oscillator that is embedded in a PLL. The injection-locked PLL (IL-PLL) utilizes integrating feedback to extend its lock range. This greatly reduces the power consumption of the remote frequency calibration system of the transponder by operating the local oscillator at a low frequency and by eliminating the need for frequency dividers. Furthermore, high frequency accuracy can be achieved through injection-locking of the local oscillator to the frequency of the envelope signal. Thus, this approach can achieve both a low power consumption and excellent frequency accuracy. The power consumption of this technique when using a 10-mV-amplitude injection signal at a frequency of 1 MHz was 0.96  $\mu W$  at a power supply of 1.2 V [19]. However, there are a few drawbacks to this technique. First, the lock range of the IL-PLL is limited to only 0.43 MHz, so if the VCO free-running frequency varies by more than this amount, the IL-PLL will be unable to lock the VCO to the injection signal. To increase the lock range, the charge-pump current in the integrating feedback loop has to be increased, thus increasing the power consumption. Second, the IL-PLL suffers from a relatively long calibration time of 150  $\mu$ s and 30  $\mu$ s in the worst and best cases, respectively, thus being unable to meet the EPC C1G2 RFID protocol for the calibation time in reader-to-transponder communication across PVT.

### 2.3 Chapter Summary

A review of the state-of-the-art in clock recovery and remote frequency calibration techniques for generating the system clock of the transponder in PWMs was presented. We found that clock recovery methods that extract the clock signal from either the carrier or envelope signal can suffer from high power consumption and are unable to operate correctly

Figure 2.7: Frequency calibration of a VCO using an IL-PLL [1].

when a large modulation index is used for the ASK-modulated carrier. This also limits the reading range of the PWM. Remote frequency calibration techniques that calibrate the frequency of a local oscillator through digital trimming, PLLs, DFLLs, and IL-PLLs were presented. The digital trimming technique was found to be the most popular calibration approach due to its large tuning range and robustness in the presence of PVT effects. However, it was determined that digital trimming suffers from long calibration times and significant power consumption. Remote frequency calibration using a PLL that locks to the carrier signal frequency was found to have a much lower power consumption than the digital trimming technique, but still experiences a large power consumption when a UHF carrier is used. A remote frequency calibration technique that uses a DFLL to compare the number of oscillation cycles of a reference VCO to that of a DCO was presented and found to have a very low power consumption, but long calibration times and a non-zero frequency error in steadystate. Finally, an IL-PLL that uses envelope injection-locking and integrating feedback to tune a VCO was presented. This method achieved both ultra-low power consumption and excellent frequency accuracy through injection-locking. However, noteable limitations to this design are its relatively long calibration time, high supply voltage, and small lock range.

## Chapter 3

## Sub-Microwatts Integrating Frequency Difference Detector for Frequency Calibration of PWMs

### 3.1 Introduction

The operation of both the RF front-end and baseband blocks of a PWM is controlled by its system clock. Successful communication between the reader and transponder of a PWM thus depends on the accuracy of its system clock, which is strongly dependent on changes in the local environment that the passive transponder is in. Variations in power supply, temperature, pressure, and the strength of the local electric/magnetic field can result in a subsequent deviation in the desired free-running frequency of the local oscillator that generates the system clock of the PWM. Regular calibration of the frequency of the local oscillator to a defined reference value can mitigate these effects and keep the oscillator's frequency at a constant, pre-defined value.

In this chapter, we propose a frequency calibration scheme that fine-tunes the frequency of the local oscillator of a PWM to a desired reference frequency using a frequencylocked loop (FLL). Additionally, a new ultra-low power integrating frequency difference detector (iFDD) that detects fine frequency differences is proposed. Similar to the dual frequency-to-voltage conversion (FVC) scheme in [20, 21], the iFDD uses a switched-capacitor network to sense and then integrate the difference between the frequency of the local oscillator and that of the reference. However, unlike the designs in [20, 21], the proposed iFDD does not use an error amplifier to amplify the frequency difference and uses only a single switched-capacitor network, thereby eliminating the need to design a low power and highgain error amplifier and the effect of FVC-mismatch-induced frequency error as a result of the use of two FVCs in [20, 21]. In addition, the stability of the FLL with the proposed iFDD does not depend on the stability of an error amplifier, unlike the designs in [20, 21]. Finally, the proposed iFDD is also capable of detecting duty-cycle error between the reference signal and the local oscillator, as opposed to the designs [20, 21] which require both signals to have the same duty-cycle.

The remainder of this chapter is organized as follows: Section 3.2 presents the basic concept of the the iFDD, including a time-domain and duty-cycle mismatch analysis. The frequency-domain behavior of the iFDD and FLL is explored in Section 3.3. Nonidealities such as duty-cycle variation and the effect of noise generated by the sampling capacitors on the operation of the FLL is also considered. The chapter is summarized in Section 3.4.

## 3.2 Integrating Frequency Difference Detector

To overcome the previously mentioned challenges in [20, 21], we propose a new integrating frequency difference detector that is capable of detecting fine frequency differences using a single FVC without an error amplifier. To develop an understanding of the iFDD, first a simple conceptual analysis of the iFDD is performed, followed by detailed derivations of its time-domain behaviour, an analysis of the effect of duty-cycle variation, and then finally an investigation into its maximum frequency of operation.

### 3.2.1 Concept of the iFDD

The simplified block diagram of the iFDD is shown in Fig.3.1. It consists of a logic control block (LCB), a time-to-voltage converter (TVC), a sample-and-hold (S/H) circuit, and a bridge circuit. The LCB converts the input frequencies,  $f_{ref}$  and  $f_{osc}$ , to two time intervals denoted by  $\Delta t_{C_1}$  and  $\Delta t_{C_2}$  for the charging intervals of two capacitors  $C_1$  and  $C_2$ , respectively, in addition to generating clocks for sampling and charge redistribution. A dual TVC that consists of a constant current source, I, and two capacitors,  $C_1$  and  $C_2$ , converts  $\Delta t_{C_1}$  and  $\Delta t_{C_2}$  to two voltages,  $v_{C_1}$  and  $v_{C_2}$ . The charging time intervals are obtained from the following equations

$$v_{\Delta t_{C_1}} = v_{osc} \wedge \overline{v_{ref}},\tag{3.1}$$

Figure 3.1: Simplified block diagram of the proposed iFDD.

$$v_{\Delta t_{C_2}} = \overline{v_{osc}} \wedge v_{ref}, \tag{3.2}$$

where  $v_{\Delta t_{C_1}}$  and  $v_{\Delta t_{C_2}}$  are the voltage waveforms of  $\Delta t_{C_1}$  and  $\Delta t_{C_2}$ , respectively. Expressions (3.1) and (3.2) show that the time intervals  $\Delta t_{C_1}$  and  $\Delta t_{C_2}$  determine the length of time for which  $v_{osc}$  is high and  $v_{ref}$  is low and  $v_{osc}$  is low while  $v_{ref}$  is high, respectively, as shown in Fig.3.2. In addition, Fig.3.2 shows that the iFDD senses fine frequency differences by measuring the time intervals formed by the rising and falling edges of  $v_{osc}$  and  $v_{ref}$ . As a result,  $\Delta t_{C_1}$  and  $\Delta t_{C_2}$  are related to the frequencies of the oscillator and reference signals via

$$0 \le \Delta t_{C_1} \le d_{osc} T_{osc},\tag{3.3}$$

$$0 \le \Delta t_{C_2} \le d_{ref} T_{ref},\tag{3.4}$$

where  $d_{osc}$  and  $d_{ref}$  represent the duty-cycle factors for the oscillator and reference signal, respectively. In the case that both waveforms are 50% duty-cycle, then  $d_{osc}=d_{ref}=2$ . From (3.3) and (3.4), a 1:1 mapping between  $T_{osc}$  and  $T_{ref}$  and  $v_{C_1}$  and  $v_{C_2}$  of the TVC exists and is given by

$$0 \le v_{C_1} \le \left(\frac{I}{C_1}\right) d_{osc} T_{osc},\tag{3.5}$$

$$0 \le v_{C_2} \le \left(\frac{I}{C_2}\right) d_{ref} T_{ref}.$$

(3.6)

Cases (i)-(vi) in Fig.3.2 show that the time intervals  $\Delta t_{C_1}$  and  $\Delta t_{C_2}$  determine which signal is operating at a higher frequency. In particular, if  $\Delta t_{C_1} > \Delta t_{C_2}$  (cases (ii), (iv),

**Figure 3.2:** Waveforms of  $v_{osc}$  and  $v_{ref}$  for fine frequency difference  $(0 < f_{osc} < f_{ref}$  or  $f_{ref} < f_{osc} < 2f_{ref}$ ) showing the definition of  $\Delta t_{C_1}$  and  $\Delta t_{C_2}$ , in addition to their intermediate and extreme values in (i)-(vi). This is for the ideal case that both waveforms are 50% duty-cycle signals.

and (v)) then  $f_{osc} < f_{ref}$ , and if  $\Delta t_{C_1} < \Delta t_{C_2}$  (cases (i), (iii), and (vi)) then  $f_{osc} > f_{ref}$ . Furthermore, assuming both waveforms are 50% duty-cycle, then we can write

$$\Delta t_{C_1} + \Delta t_2 = \frac{T_{osc}}{2},\tag{3.7}$$

$$\Delta t_2 + \Delta t_{C_2} = \frac{T_{ref}}{2}.\tag{3.8}$$

Notice in (3.8) that since  $\frac{T_{ref}}{2}$  is constant, then  $\Delta t_2 + \Delta t_{C_2}$  is constant in every cycle which implies that if  $\Delta t_2$  is increasing, then  $\Delta t_{C_2}$  must be decreasing and vice-versa. Subtracting (3.8) from (3.7) and defining the period error as  $\Delta T_{err} = T_{osc} - T_{ref}$ , we have

$$\Delta t_{C_1} - \Delta t_{C_2} = \frac{\Delta T_{err}}{2}.$$

(3.9)

Equation (3.9) shows that both the magnitude and sign of the frequency error between  $v_{osc}$  and  $v_{ref}$  is contained in the time intervals  $\Delta t_{C_1}$  and  $\Delta t_{C_2}$ . If  $\Delta t_{C_1} > \Delta t_{C_2}$ , then from (3.9)  $\Delta T_{err} > 0$  and thus the frequency of the oscillator must increase. Otherwise,  $\Delta T_{err} < 0$  and the frequency of the oscillator must decrease. Finally, If  $\Delta t_{C_1} = \Delta t_{C_2}$ , then  $\Delta T_{err} = 0$ . This implies that  $v_{C_1} = v_{C_2}$  so that  $v_1 = v_2$  after the S/H circuit. Consequently, the bridge is balanced when  $\Delta t_{C_1} = \Delta t_{C_2}$  (when both waveforms are 50% duty-cycle) so that  $T_{osc} = T_{ref}$ . Otherwise, the bridge isn't balanced and the circuit will continue to operate until the bridge is balanced, assuming the iFDD is in a closed-loop system with negative feedback.

#### 3.2.2 Time-Domain Behaviour of the iFDD

To develop a quantitative understanding of the iFDD, the circuit will be analyzed very close to steady-state conditions, so as to develop time-domain (and later on z-domain) equations of the output of the iFDD. Since the iFDD circuit contains switched-capacitors, then we can treat the output voltage of the iFDD as as a discrete-time signal, where the sampling rate in steady-state is set by the reference clock. Fig.3.3 shows the schematic of the proposed iFDD on the left and the waveforms of  $v_{osc}$ ,  $v_{ref}$ , and the clocks that control switches  $\phi_{C_1}$ ,  $\phi_{sa1}$ ,  $\phi_{r1}$ ,  $\phi_{C_2}$ ,  $\phi_{sa2}$ ,  $\phi_{r2}$ , and  $\phi_f$  on the right. Clock signals  $\phi_{sa1}$ ,  $\phi_{r1}$ ,  $\phi_{sa2}$ , and  $\phi_{rst2}$  are generated from signals  $\phi_{C_1}$  and  $\phi_{C_2}$ , respectively, whereas clock signal  $\phi_f$  is the delayed version of either  $\phi_{r1}$  or  $\phi_{r2}$  depending on if the falling edge of  $v_{osc}$  lags or leads the the falling edge of  $v_{ref}$ , as shown on the right of Fig.3.3. The falling edges of both  $v_{osc}$  and  $v_{ref}$  are detected by two rising edge DFFs, as shown on the left in Fig.3.3. If the falling edge of  $v_{osc}$  leads the falling edge of  $v_{ref}$ , then  $Q_{ref}$  goes high and  $\phi_{r2}$  is selected by the wired-OR 2:1 MUX so that  $\phi_f = \phi_{r2}$ . On the other hand, if the falling edge of  $v_{osc}$  lags  $v_{ref}$ , then  $Q_{osc}$ goes high and  $\phi_{r1}$  is selected by the wired-OR 2:1 MUX so that  $\phi_f = \phi_{r1}$ . The delay  $\tau$  that is used to create clock signals  $\phi_{sa1}$ ,  $\phi_{sa2}$ ,  $\phi_{r1}$  and  $\phi_{r2}$  is generated by a chain of inverters. Note that the order of operation of the switches varies when the circuit is not operating in or near steady-state or is not operating in a closed-loop system. In particular, the order of  $\phi_{C_1}$  and  $\phi_{C_2}$  will vary so that either  $\phi_{C_1}$  or  $\phi_{C_2}$  occurs first, and, consequently, the order of switches  $\phi_{sa1}$ ,  $\phi_{r1}$ ,  $\phi_{sa2}$ , and  $\phi_{r2}$  will vary. However, clock signal  $\phi_f$  will always occur after either  $\phi_{r1}$  or  $\phi_{r2}$ . The start and end of each cycle is defined when the rising edge of  $\phi_{C_1}$  or  $\phi_{C_2}$  occurs first and when the falling edge of  $\phi_f$  occurs, respectively. A buffer is added after the wired-OR so as to restore  $\phi_f$  to  $V_{DD}$ .

Figure 3.3: Proposed iFDD and its logic control block (LCB) (left) and waveforms (right) of  $v_{osc}$ ,  $v_{ref}$ ,  $\phi_{C_1}$ ,  $\phi_{sa1}$ ,  $\phi_{r1}$ ,  $\phi_{C_2}$ ,  $\phi_{sa2}$ ,  $\phi_{r2}$ , and  $\phi_f$ . The order of operation of the switches are included in the waveform for ease of understanding. The number inside the brackets of  $\Delta t_{C_1}(j)$  and  $\Delta t_{C_2}(j)$  indicates their *j*th sample number.

Consider the first cycle of operation, as shown in the waveform on the right of Fig.3.3, and assume that all capacitors are initially at rest, so that  $v_{C_{1,2,3,4}}(t = 0^-) = v_{C_{1,2,3,4}}(t = 0^+) = 0$ . The first operation in this cycle of the iFDD will be time-to-voltage conversion. Since time interval  $\Delta t_{C_1}(1)$  occurs first, then switch  $\phi_{C_1}$  will close and capacitor  $C_1$  will be charged so that  $\Delta t_{C_1}(1)$  is converted to a voltage, given by

$$v_{C_1}(1) = \left(\frac{I}{C_1}\right) \Delta t_{C_1}(1), \qquad (3.10)$$

where  $v_{C_1}(1)$  represents the first sample of  $v_{C_1}$ . After switch  $\phi_{C_1}$  opens, the second operation of the iFDD, sampling-and-holding, will occur. In this particular case, switch  $\phi_{sa1}$  closes so that charge redistribution between  $C_1$  and  $C_3$  occurs. Assuming that charge redistribution between  $C_1$  and  $C_3$  completes before switch  $\phi_{sa1}$  opens, then by the principle of conservation of charge we have

$$(C_1 + C_3)v_{C_3}(1) = C_3 v_{C_3}(0) + C1v_{C_1}(1), (3.11)$$

where  $v_{C_3}(1)$  represents the first sample value of the voltage across  $C_3$  and  $v_{C_3}(0)$  is the initial voltage across  $C_3$ . Since  $v_{C_3}(0) = 0$  and  $v_{C_3} = v_{out}$ , then solving for  $v_{C_3}(1)$  yields

$$v_{out}(1) = \left(\frac{C_1}{C_1 + C_3}\right) v_{C_1}(1).$$

(3.12)

Define  $\alpha_1 = \frac{C_3}{C_1}$ , then substituting  $\alpha_1$  and (3.10) into (3.12) yields

$$v_{out}(1) = \left(\frac{I}{C_1} + \alpha_1\right) \Delta t_{C_1}(1).$$

(3.13)

The third operation of the iFDD will be resetting capacitor  $C_1$  by discharging it to ground when  $\phi_{r1}$  closes so that  $v_{C_1} = 0$ . Next, switch  $\phi_{C_2}$  will close so that the fourth operation of the iFDD will be time-to-voltage conversion of  $\Delta t_{C_2}(1)$  to a voltage given by

$$v_{C_2}(1) = \left(\frac{I}{C_2}\right) \Delta t_{C_2}(1),$$

(3.14)

where  $v_{C_2}(1)$  represents the first sample of  $v_{C_2}$ . After switch  $\phi_{C_2}$  opens, switch  $\phi_{sa2}$  closes to commence the fifth operation, which is sampling-and-holding of the voltage  $v_{C_2}(1)$ . Assuming

that charge redistribution between  $C_2$  and  $C_4$  completes before switch  $\phi_{sa2}$  opens, then by the principle of conservation of charge we have

$$(C_2 + C_4)v_{C_4}(1) = C4v_{C_4}(0) + C2v_{C_2}(1), \qquad (3.15)$$

where  $v_{C_4}(0)$  is the initial voltage across capacitor  $C_4$ . Since  $v_{C_4}(0) = 0$  then solving for  $v_{C_4}(1)$  in (3.15) yields

$$v_{C_4}(1) = \left(\frac{C_2}{C_2 + C_4}\right) v_{C_2}(1).$$

(3.16)

Define  $\alpha_2 = \frac{C_4}{C_2}$ , then substituting  $\alpha_2$  and (3.14) into (3.16) yields

$$v_{C_4}(1) = \left(\frac{\frac{I}{C_2}}{1+\alpha_2}\right) \Delta t_{C_2}(1).$$

(3.17)

In order to compare  $v_{out}$  and  $v_{C_4}$  equally, we must have  $\frac{I}{C_1} = \frac{I}{C_2}$ . Therefore, let  $C_1 = C_2 = C$  and define  $K_{TVC} = I/C$  as the gain of the TVC. Then equations (3.13) and (3.17) become